1 20 419 F

A Publication Especially Covering VHF UHF and Microwaves

# communications

Volume No. 21 · Spring · 1/1989

Radio Astronomy &F VIF Tes

## communications

A Publication for the Radio Amateur Especially Covering VHF, UHF, and Microwaves

Volume No. 21 · Spring · Edition 1/1989

Published by:

TERRY BITTAN OHG, P.O.Box 80.

Jahnstraße 14, D-8523 BAIERSDORF

Fed. Rep. of Germany

Telephone (9133) 47-0 Telex 629 887

Telefax 0 91 33-47 18 Postgiro Nbg. 30455-858

Publishers:

TERRY BITTAN OHG

Editors:

Corrie Bittan

Colin J. Brock (Assistant)

Translator:

Colin J. Brock, G 3 ISB / DJ Ø OK

The international edition of the

Advertising

manager:

Corrie Bittan

VHF

COMMUNICATIONS

German publication UKW-BERICHTE is a quarterly amateur radio magazine especially catering for the VHF / UHF / SHF technology. It is published in Spring, Summer, Autumn and Winter. The 1988 subscription price is DM 25.00 or national equivalent per year. Individual copies are available at DM 7.50 or equivalent each. Subscriptions, orders of individual copies, purchase of PC-boards and advertised special components, advertisements and contributions to the magazine should be addressed to the national representative, or - if not possible - directly to the publishers.

©Verlag UKW-BERICHTE All rights reserved. Reprints, translations, or extracts only with the written approval of the publisher.

Printed in the Fed. Rep. of Germany by R. Reichenbach KG Krelingstr. 39 - 8500 Nuernberg.

We would be grateful if you would address your orders and gueries to your representative.

#### Representatives

Austria

Verlag UKW-BERICHTE, Terry D. Bittan POB 80, D-8523 Baiersdorf / W. Germany PSchKto WIEN 1.169.146

W.I.A. P.O. Box 300, South Cauffield, 3162 VIC, Phone 5285962

HAM INTERNATIONAL, Brusselsesteenweg 428, B-9218 GENT, PCR 000-1014257-25.

Tel. 00-32-91-312111

Denmark

Halskov Electronic, OZ 7 LX, Sigersted gamle Skole DK-4100 RINGSTED, Tel. 03-616162, Giro 7 29 68 00

Christiane Michel, F.5 SM, SM Electronic 20 bis, Avenue des Clairlons, F-89000 AUXERRE

Tel. (86) 46 96 59

Peter Lytz, OH 2 AVP, Gesterbystingen 14 E 49 SF- 02410 Kyrkslätt, Tel 358/0/2 98 17 61

SRAT, PL 44 SF-00441 Helsinki, Tel. 358/0/5625973

DOEVEN-ELEKTRONIKA, J. Doeven, Schutstraat 58. NL-7901 EE HOOGEVEEN, Tel. 05280-69679

Doron Jacobi 4Z4RG, P.O. Box 6382 HAIFA, Israel 31063

Franco Armenghi, I 4 LCK, Via Sigonio 2, I-40137 BOLOGNA, Tel. (051) 34 56 97

Luxembourg

TELECO, Jos. Faber, LX 1 DE, 5 - 9, Rue de la fontaine,

ESCH-SUR-ALZETTE, Tel. 53752

E. M. Zimmermann, Zl. 1 AGQ, P. O. Box 31-261 Milford, AUCKLAND 9, Phone 492-744

Henning Theg, LA 4 YG, Postboks 70, N-1324 LYSAKER, Postgirokonto 3 16 00 09

South Africa

HI-TECH BOOKS, P. O. Box 1142, RANDBURG, Transvaal 2125, Tel. (011) 886-2020

Spain + Portugal

Julio A. Prieto Alonso, EA 4 CJ, MADRID-15,

Donoso Cortes 58 5"-B, Tel. 243.83.84

Lars Pettersson, SM 4 IVE, Pt. 1254, Smegården Taiby, S-71500 ODENSBACKEN, Tel. 19-50223, Pg. 914379-3

Terry Bittan, Schweiz, Kreditanstalt ZURICH, Kto. 469.253-41; PSchKto. ZURICH 80-54.849 Leo Kälin, HB 9 CKL, Funktechnik Alte Landstr. 175, CH 8708 Männedorf

Tel. 01-9203535

**United Kingdom** Mike Wooding, G 6 IQM, 5 Ware Orchard Barby, nr. Rugby, Warks CV23 8UF, Tel. 0788 890365

Timekit, P. O. Box 22277, Cleveland, Ohio 44122, Phone: (216) 464-3820

ISSN 0177-7505

## Contents

| Matjaž Vidmar<br>YT 3 MV            | Digital Signal Processing Techniques for<br>Radio Amateurs<br>Part 2: Design of a DSP Computer for Radio-<br>Amateur Applications | 2 - 24  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------|

| Wolfgang Schneider,<br>DD 2 EK      | FM-ATV in the GHz Range<br>Part 1: 23 cm Transmitter                                                                              | 25 - 30 |

| Editors                             | Index of Volume 20 (1988)                                                                                                         | 31 - 34 |

| Andrew Bell,<br>GW 4 JJW            | Morse Code Generator for Microwave Applications                                                                                   | 35 - 38 |

| Carsten Vieland,<br>DJ 4 GC         | UHF and SHF Broadband Mixers                                                                                                      | 39 - 45 |

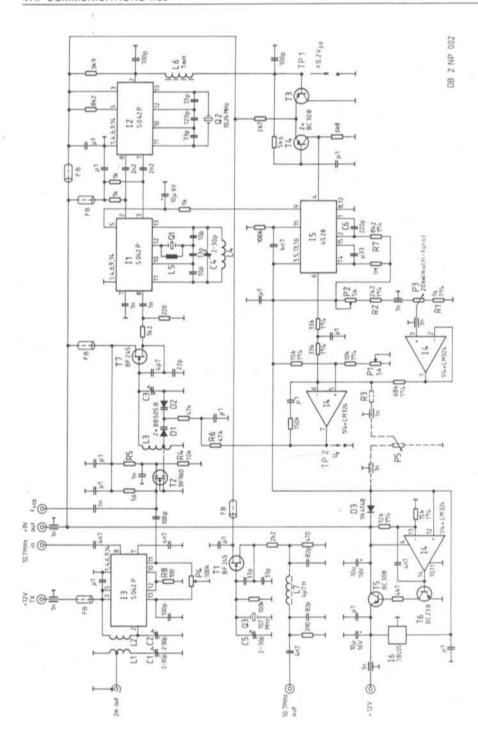

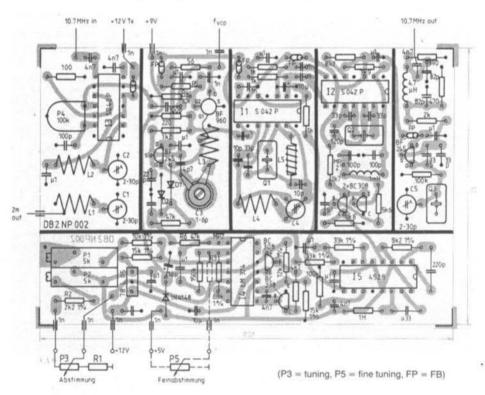

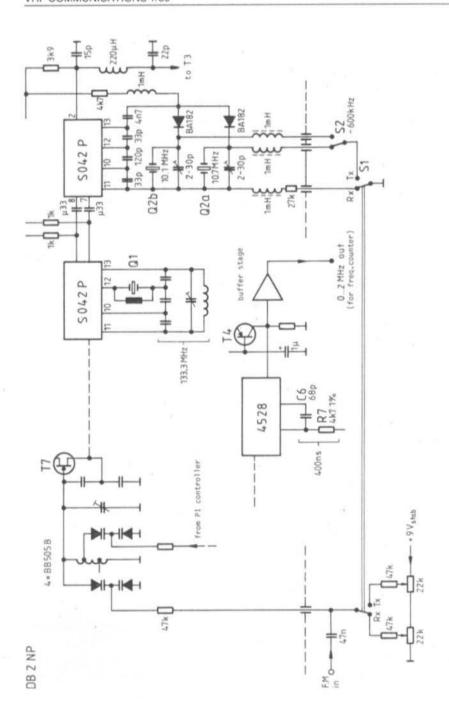

| Dr. (Eng.) Ralph Oppelt,<br>DB 2 NP | Stabilizing the VCO Frequency by Means of Monostables Part 2: A Continuously Tunable VCO for the 2 m SSB Band                     | 46 - 56 |

| Wolfgang Schneider,<br>DD 2 EK      | FM-ATV in the GHz Range<br>Part 2: Sound-Carrier Circuits and Tuning-<br>Voltage DC Converter                                     | 57 - 60 |

Matjaž Vidmar, YT 3 MV

## Digital Signal Processing Techniques for Radio Amateurs Part 2: Design of a DSP Computer for Radio-Amateur Applications

As already explained in the theoretical part of the article (VHF COMMUNICATIONS 2/1988), I decided to design a computer with DSP capabilities around a standard 16 bit microprocessor, in particular the Motorola MC 68010. An additional requirement was to design the hardware such that it does not slow down the CPU in any way due to the speed requirements of DSP algorithms.

#### 2.1. GENERAL DESIGN

The practical hardware design of a 16 bit microprocessor imposes many constraints. In comparison to an 8 bit microprocessor system, the number of connections is more than doubled. Further, 16 bit microprocessors have an order of magnitude faster bus than 8 bit microprocessors. Bus ringing and crosstalk, which are seldom a problem in a well-designed 8 bit microcomputer, usually cause troubles in 16 bit designs. Professional computer designers generally solve the problem by using a better printed-circuit-board technology, namely multilayer printed circuit boards. The latter are prohibitively priced if a small quantity is only required and this technology is therefore out of reach for amateur experimental work.

For experimental work a modular design with a common bus board, carrying just several multipole connectors with all the pins connected in parallel, is necessary. After a careful analysis of the MC 68010 bus signals, I found out that a bus with 64 pole connectors could be sufficient. The selection fell on the well-proven and reliable, but easily available and reasonably priced "Eurocard" connectors. A 64 pole "Eurocard" connector has two rows of 32 gold-plated contacts. The required parallel connections can be made all on one side of a double-sided printed circuit board

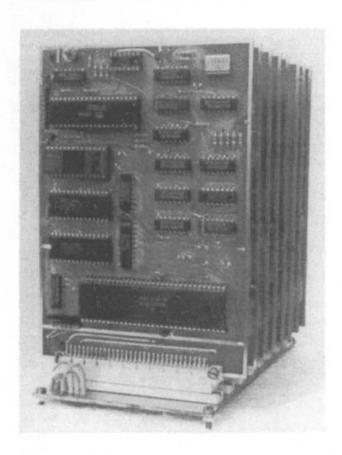

Fig. 2.0.: The DSP computer with 1 Mbyte SRAM, without power supply unit and housing.

so that the other side can be used as an almost continuous ground plane to significantly reduce crosstalk between the signal lines.

Considering the technology I had available for the printed circuit boards — simple double-sided boards with not too fine line geometry and not too many feedthrough holes — the modules had to be made slightly larger than the standard "Eurocard" format. All the modules developed are 120 mm wide and 170 mm long. The modules represent functional units and all the connections among the modules themselves are made through the computer bus with "Eurocard" connectors (fig. 2.0.).

Of course, the hardware design of a computer also depends on the application and software used. Since I decided right from the beginning to use nonvolatile RAM as the main program and data storage, the computer bus also carries a continuous supply voltage obtained from a single NiCd battery in the power supply module. The latter supplies all the computer memory and the real-time-clock circuit. Even more important, a nonvolatile RAM requires a very reliable RESET circuit. The latter should also be able to prevent the destruction of the data during any power-up or power-down sequence by inhibiting the access to the RAM unless the supply voltage is within the specified tolerances. The RESET signal is therefore generated by the power supply module and made available to all computer modules through the bus.

Since I planned little use of magnetic media, I made no special arrangements for quick data

transfer to or from the computer memory. The computer has no DMA capability and the MC 68010 is hardwired to be the bus master all the time. In any case, the MC 68010 is fast enough to handle the data stream to or from a floppy-disk controller on its own, without the aid of a DMA controller. In the case of a DSP application with a typical 10 kHz sampling frequency, not using a DMA controller brings a penalty of only 10 % or less in terms of CPU time. Finally, for memory-to-memory transfers, the MC 68010 loop-mode instructions are almost as fast as a DMA controller.

In a 16 bit microcomputer design it is frequently convenient to use standard 8 bit peripheral devices because they are inexpesive and widely available. Since these are usually too slow to interface directly with a high-speed 16 bit microprocessor bus, additional interface circuits are required. The latter are placed on the peripheral modules where required due to the limited number of conductors available on the computer bus.

#### 2.2. MC 68010 OPERATION

Before describing the various computer modules, a brief description of the MC 68010 CPU operation will be made. This introduction is intended for the reader that has a basic knowledge about the operation of a microcomputer, in particular of an 8 bit microprocessor, but has little or no experience with 16 bit microprocessors.

The MC 68010 has a 16 bit data bus and 32 bit internal registers. All addresses are internally 32 bits long and are referred to 8 bit bytes, corresponding to an addressing range of 2<sup>32</sup> or 4 terabytes. However, the upper 8 address bits are not available externally (there are not enough pins on the package), and the addressing range is limited to 2<sup>24</sup> or 16 megabytes. There are only 23 address lines, A1 to A23, since the 16 bit wide bus can access two bytes at a time. In the case of a single byte access, only half of the available

data lines are used, either the lower 8 data lines D0 to D7 (odd address) or the upper 8 data lines D8 to D15 (even address).

16 bit data words are always addressed by an even address (LSB = 0). A word access on an odd address (LSB = 1) would require two separate bus cycles. The MC 680xx series of microprocessors do not tolerate word accesses on odd addresses, in contrast with some other 16 bit microprocessors, and a call to the address error handling routine is generated. All MC 68010 instruction codes are either one or an integer number of 16 bit words and the program counter is always incremented in steps of 2, 4, 6 or other even numbers.

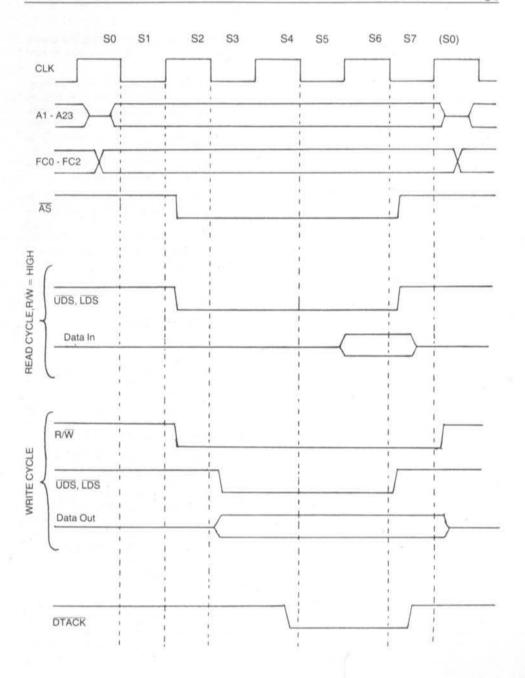

A typical memory access (read or write) cycle is shown on fig. 2.1. The address lines A1 to A23 are set first, followed by the Address Strobe (AS) signal going low. Two data strobe lines, Upper Data Strobe (UDS) and Lower Data Strobe (LDS) select the byte to be accessed. In the case of a word access, both UDS and LDS are asserted going low simultaneously. In the case of a write cycle, the Read/Write (R/W) signal goes low before the data strobes. The microprocessor now waits for the read or write operation to be completed. When the operation is completed, the memory signals this to the microprocessor by pulling the Data Transfer ACKnowledge (DTACK) line low. If no memory is available at the specified address, an external logic is usually used to activate the Bus ERRor line (BERR).

The MC 68010 supplies three additional signals, named function codes FC0, FC1 and FC2, to better describe the type of the bus cycle performed: instruction fetch, data read or write in both user and supervisor modes or interrupt acknowledge. Function code signals have to be decoded together with the address lines A1 to A23 to select devices tied on the bus.

The MC 68010 accepts seven different interrupts with differing priorities. The highest priority interrupt is not maskable (NMI) while the other interrupt levels can be inhibited by setting bits in the status register. The seven interrupt requests are decoded from three input lines: IPL0, IPL1 and IPL2, to reduce the number of pins on

Fig. 2.1.: MC 68010 bus cycle timing

| С      |    | A     |

|--------|----|-------|

| GND    | 1  | GND   |

| D4     | 2  | D 5   |

| D3     | 3  | D 6   |

| D2     | 4  | D 7   |

| D1     | 5  | D 8   |

| DO     | 6  | D 9   |

| AS     | 7  | D10   |

| UDS    | 8  | D11   |

| LDS    | 9  | D12   |

| R/W    | 10 | D13   |

| DTACK  | 11 | D14   |

| D15    | 12 | A23   |

| A22    | 13 | A21   |

| CLK    | 14 | A20   |

| HALT   | 15 | A19   |

| RESET  | 16 | A18   |

| A17    | 17 | A16   |

| VPA    | 18 | A15   |

| FC2    | 19 | A14   |

| FC1    | 20 | A13   |

| FC0    | 21 | A12   |

| A1     | 22 | A11   |

| A2     | 23 | A10   |

| A3     | 24 | A 9   |

| A8     | 25 | A 7   |

| A6     | 26 | A 5   |

| A4     | 27 | INT7  |

| NT6    | 28 | INT5  |

| NT4    | 29 | INT1  |

| MR     | 30 | INT2  |

| + CMOS | 31 | INT3  |

| + 5 V  | 32 | + 5 V |

the microprocessor package. An external priority encoder (usually 74LS148) is required in most applications.

CLOCK is obviously required by the micro-processor itself. RESET and HALT are both inputs: to reset the microprocessor, and outputs: to reset the peripherals under program control and signal a double bus error. Additional control lines include an interface for the slow 6800 series peripherals (VPA, E, VMA) and bus request lines for DMA (BR, BG, BGACK).

Most of the microprocessor signals are brought to the computer bus without using bufffers. The latter are placed on the inputs of the various modules to reduce bus loading. The actual bus connections on a 64 pole "Eurocard" connector are shown in fig. 2.2.

#### 2.3. PROCESSOR BOARD

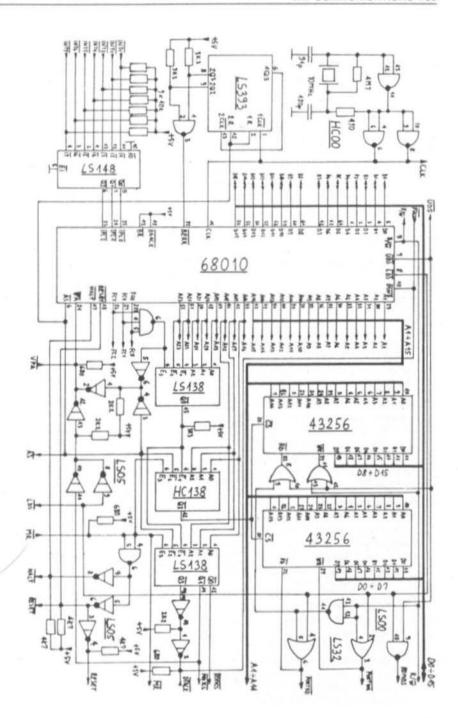

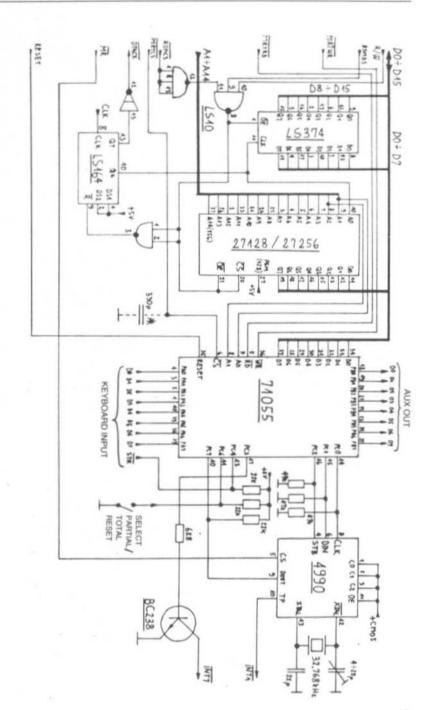

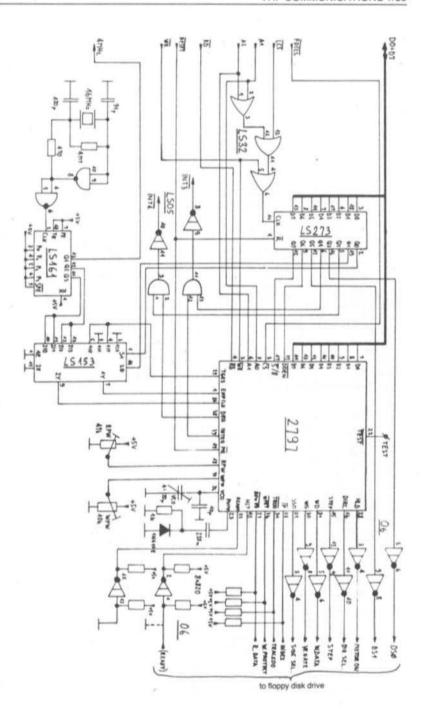

The processor board includes the MC 68010 chip and corresponding support circuitry, up to 32 kbytes of EPROM containing the operating system, 64 kbytes of nonvolatile RAM and the real-time calender/clock. The corresponding circuit diagram is shown in figs. 2.3. and 2.4.

The microprocessor support circuits include a clock generator, a bus-error timer, an interrupt-request priority encoder, an interrupt autovector logic, a reset logic and an address decoder for the remaining on-board devices. The clock generator is a simple crystal oscillator built around a CMOS (HC) gate, since there are no special requirements regarding its accuracy. The nominal clock frequency is 10 MHz. Additional HC gates are used to buffer the oscillator output.

The bus-error timer monitors the  $\overline{AS}$  signal. In the case of a bus-error no device will answer with a  $\overline{DTACK}$  or  $\overline{VPA}$  to terminate the bus cycle and the  $\overline{AS}$  could remain low indefinitely. However, the  $\overline{AS}$  is also used to reset the bus-error timer. If the  $\overline{AS}$  remains low for more than 192

Fig. 2.2.: Bus connections on a Eurocard connector

clock cycles, the bus-error timeout counter (LS 393) will assert the BERR signal commanding the MC 68010 to call the bus-error handling routine.

The interrupt-request priority encoder is simply a LS 148 with pull-up resistors on its active-low inputs, so that more devices requesting the same level interrupt can be simply wired-on. The MC 68010 is used in the autovector mode. The latter is invoked by decoding the interrupt-acknowledge function code (all three FC outputs at logical high) and asserting the VPA signal.

The MC 68010 microprocessor is reset when both RESET and HALT lines are pulled low simultaneously for a sufficiently long period of time — at least 10 clock cycles during normal operation but at least 100 milliseconds after power-up. The reason for this long power-up reset time is easily explained since the MC 68010 is a dynamic NMOS circuit internally. The delay of 100 ms is required for the internal on-chip substrate bias-generator to achieve its full output voltage of about — 3 V. The Main Reset signal (MR), supplied from the power-supply module, is applied through open-collector gates to both RESET and HALT.

The MC 68010 RESET pin can also be an opendrain output, activated when executing the RESET instruction. The latter will not reset the microprocessor but will drive the RESET pin low for 124 clock cycles. This signal is made available on the computer bus and is used to reset all peripheral devices.

On the other hand, the HALT pin is driven low when a double bus-error is detected after a soft-ware crash or hardware failure. A double bus-error blocks the MC 68010 to avoid damaging the memory content allowing subsequent trouble-shooting. After a double bus-error a reset is required to restart the MC 68010.

The address decoder is used to select the onboard memories and peripherals, decoding the most significant address lines and to answer with a DTACK or a VPA signal. The nonvolatile CMOS RAM requires an additional decoder chip (HC 138) which receives the same batterybacked supply voltage as the RAM itself. The decoder is inhibited by the MR signal to protect the RAM content during power-up or powerdown.

A single 8 bit wide EPROM is used to store the operating system software. An 8 bit latch (LS 374) and a sequence generator (LS 164) are used to generate a 16 bit data word for the MC 68010. Since this sequential 8 + 8 bit read operation is slow, the software is copied into the on-board system RAM immediately after reset. Once in the RAM, the software can be executed at full speed with no processor wait states.

The lower 16 kbytes of the on-board system RAM are assigned to the stack by the present software. In the case of a software crash it is usual for the stack to grow in an uncontrolled way. Therefore the locations immediately below the stack area are not assigned to any device so that an uncontrolled stack growth ends in a double bus-error safely blocking the MC 68010.

A 71055 parallel I/O port (fast CMOS version of the popular 8255) is used to interface the keyboard and the real-time clock chip. The parallel keyboard output is connected to port A, configured as a strobed input. Port B is a spare output. The remaining bits of port C are used both as inputs and as outputs to interface the 4990 real-time clock chip. The latter has serial inputs and outputs. Clocks and other signals are generated by software.

The 4990 Chip Select (CS) input is driven by the MR signal to protect the clock count during power-up or power-down for the same reason as the nonvolatile RAM. The 4990 has an on-chip opendrain interrupt output, while the keyboard interrupt, generated inside the 71055, requires an additional transistor. Current software requires the clock interrupt on INT1 and the keyboard interrupt on INT7, selectable through jumpers on the printed circuit board.

#### 2.4. VIDEO BOARD

The video board includes 128 kbytes of special, dual-port video RAM, video D/A converter and

timing and interface circuits. The circuit diagram of the video board is shown in figs. 2.5. and 2.6.

The memory used in a video interface is being read continuously to update the picture displayed on a CRT several times per second. If a microprocessor has to access the same memory, for example to update the picture, it can either wait for the horizontal or vertical retrace period or interrupt the display read operation disturbing the picture. General purpose dynamic or static memories are usually not fast enough to provide data for a high resolution video signal generation and be accessed by a fast 16 bit microprocessor at the same time. On the other hand, true dual-port memories with two completely independent access ports are both difficult to manufacture and expensive.

A few years ago, semiconductor manufacturers invented an alternative solution to increase the data rate from a dynamic memory built using only conventional DRAM chip technology. During any random access read or write operation, inside a dynamic RAM, a whole row of data (1024 bits in a 256 kbit RAM) is transferred from its storage cells to as many refresh amplifiers. This data can not be transferred quickly only because it is completely impractical to build an IC housing with so many pins. However, this data can be transferred to another circuit efficiently if the latter is located on the same semiconductor chip.

Dual-port dynamic memories include on-chip an additional shift register. A whole row of bits can be transferred from the main memory array to the auxiliary shift register in one single operation, called a data-transfer cycle and lasting no more than an ordinary data-access cycle. After such a data-transfer cycle the dynamic memory circuits and the shift register are completely independent: the microprocessor can randomly access the data in the main memory array (with no timing penalties) while other data is shifted out of the auxiliary register to generate the video signal.

Since dual-port video memories are only slightly more expensive than conventional dynamic RAMs, they are very attractive for any new video memory design. A data-transfer cycle usually has to be performed once every television line, i.e. once every 64 microseconds and it takes less than 1 % of this time. The memory is therefore available to the microprocessor for more than 99 % of the total time with no delays or disturbs to the generated video.

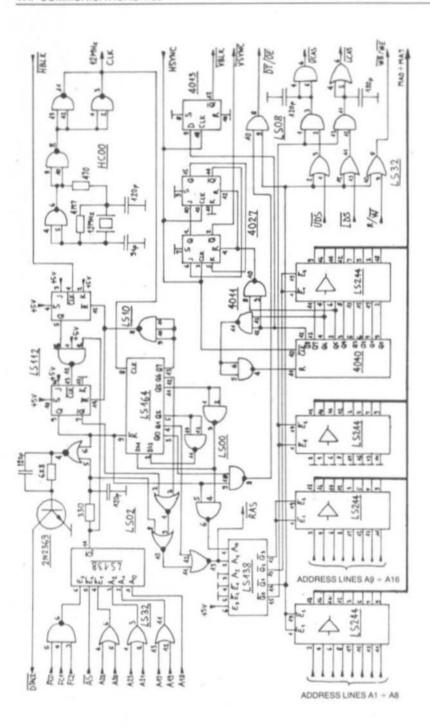

The described video board uses four 41264 chips which are organized as 64 k by 4 bits each. From the microprocessor side the video memory is organized as 64 k 16 bit words, from the video side there are 128 k pixels, arranged in 256 lines of 512 pixels each and the intensity of each pixel is described with 8 bits or 256 possible grey levels. Each 41264 chip also has four 256 bit shift registers that are all loaded in a single data-transfer cycle occurring during the horizontal retrace period. During the active scanning period, data is retrived alternately from two shift register groups so that the position of the 512 pixels obtained matches the microprocessor byte address ennumeration, simplifying and speeding-up the software.

All the timing of the generated video signal is derived from an on-board 12 MHz crystal oscillator, which drives a divider chain. The line period matches the standard TV line period (64  $\mu$ s). One TV line consists of 768 pixels; two thirds (512 pixels) represent the useful scan and the remaining third (256 pixels) is left for the horizontal retrace and black edges at both picture sides. The number of lines in a TV frame is slightly larger than standard — a frame of 320 lines was selected for simplicity. To avoid flicker the scanning is not interlaced.

At the end of each useful scan period the video timing logic issues a request for a data-transfer cycle to obtain the data for the next television line. The request can not be granted immediately since the microprocessor may be using the memory at the same time. All dynamic memories are very sensitive to correct timing — any incorrect timing acces cycle disturbs the refresh operation and destroys immediately at least one whole row of data!

The data-transfer cycle request is therefore passed to an arbitration logic, built around a double JK-FF (LS 112). The arbitration circuit decides who has priority to access the memory, allowing the device currently accessing the

memory to complete the cycle in a regular way. In the worst case, the microprocessor has to wait for one complete data-transfer cycle or the video timing logic has to wait for one microprocessor bus cycle.

The data-transfer cycle timing is generated by a sequential logic with an 8 bit shift-register (LS 164) and corresponding gates. Like all dynamic memories, the 41264 require RAS and CAS clocks and address multiplexing. LS 244 tri-state buffers are used for both row and column address multiplexing and for switching the address lines between the microprocessor and the video timing logic. Since the microprocessor may want to access a single byte at a time, separate CAS clocks are derived from UDS and LDS.

The 41264 video RAM serial outputs have tristate capability and are simply tied in parallel for multiplexing. A fast 8 bit D-FF (S374) is however required to "clean" the data in front of the video D/A converter. During both horizontal and vertical retrace periods, all the 8 data lines are held low (black level) by a tri-state buffer (LS 244).

Sync pulses are added to the output of the D/A converter. The horizontal sync pulse is generated by a dual monostable and its position can be adjusted to match the monitor used. The vertical sync pulse is generated by a dual FF, it is two line periods long and occurs 32 lines after the end of the useful picture scan.

A 733 video amp is used to boost the generated video signal level. Both polarities are available to drive any type of standard-scan TV monitor. Both the D/A converter and the video amplifier require a negative supply voltage of about — 4 V that is generated on-board. All supply voltages of the analog part of the circuit are to be well-filtered to avoid disturbs in the video signal.

#### 2.5. MEMORY

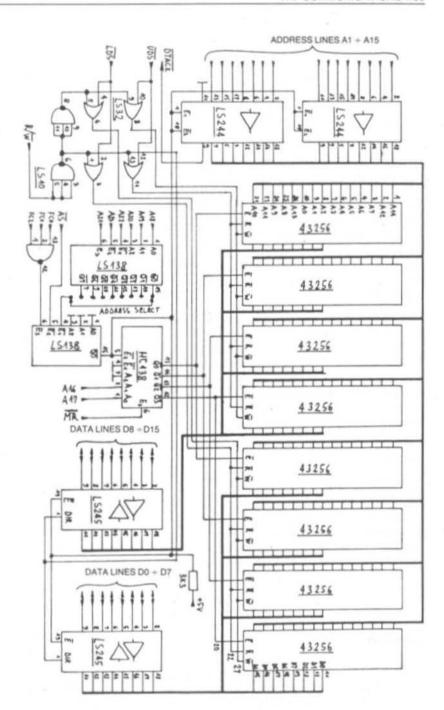

For most application programs, especially those handling pictures, the computer requires much more memory than the 64 kbytes provided on the processor board. Out of the MC 68010 16 Mbyte addressing range the current operating system uses the first megabyte for various system functions: start-up ROM, stack, video memory and I/O port addresses. The remaining 15 Mbytes are intended for memory expansion.

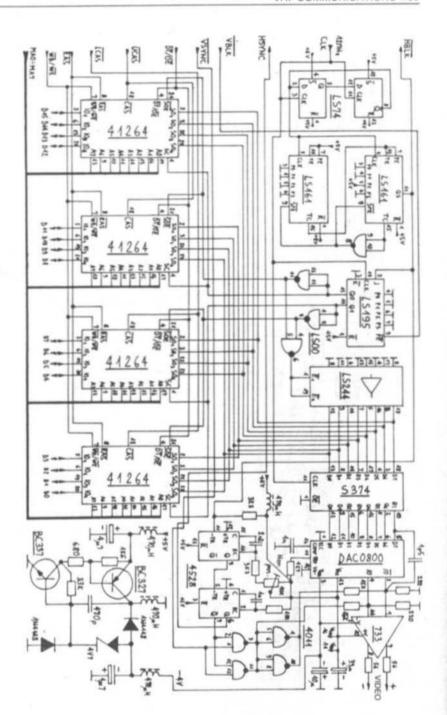

The circuit diagram of a 256 kbyte nonvolatile memory board is shown in fig. 2.7. The circuit includes eight 256 kbit CMOS RAMs 43256, address and data buffers to decrease the capacitive loading of the computer bus and an address decoder. The start address of the 256 kbyte block can be selected to start anywhere from address 200000H to 3C0000H positioning an on-board jumper.

The 43256 memory chips only have an active-low chip-enable input. To preserve the memory content when the computer is switched off, the chip-enables have to be kept high. This requirement can be met easily using a CMOS (HC) address decoder (HC 138) supplied from the same rail as the memory chips. The address decoder has an active-high input tied to MR to protect the memory content.

In a typical system, 4 such memory boards are used for a total 1 Mbyte nonvolatile memory. The latter is enough for most DSP applications and for some simple image processing. Due to bus loading problems it is difficult to connect more than 4 memory boards without sacrifying the operating speed. Of course as soon as higher-density memory chips become available, the described memory boards will be replaced by a higher capacity memory.

#### 2.6. ANALOG I/O

An important part of any DSP computer is its interface to the analog world. As already described in the theoretical part, I decided to use a telephone CODEC IC as the A/D and D/A converter, since its performances match those of voice grade communications receivers and transmitters, including radio-

amateur receivers and transmitters. Since all CODECs have on-chip a serial data interface, a UART is required to interface a CODEC to a microprocessor. Programmable counters are used to generate the A/D and D/A sampling rates.

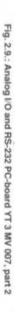

The analog I/O board also includes an independent RS-232 interface. The circuit diagram is shown in figs. 2.8. and 2.9. The RS-232 UART (71051), the programmable counters (71054) and the UART to interface the CODEC (another 71051) are all standard 8 bit microprocessor peripherals. To interface the faster MC 68010 bus, a timing logic built around a 4 bit shift register (LS 195) is required. The logic is started whenever any of the three on-board peripheral chips are selected by the address decoder (two LS 138), generating a longer Read (R) or Write (W) pulse and finally terminating the bus cycle by issuing a DTACK to the MC 68010. All three peripherals are connected to the lower byte (D0 to D7) of the 16 bit data bus through a bidirectional buffer (LS 245) to reduce the capacitive bus loading.

The RS-232 UART is equipped with a standard RS-232 receiver (75154). A 4053 CMOS multiplexer is used to generate RS-232 compatible transmit signal levels out of the + 5 V and - 5 V supplies available on-board. The RS-232 UART generates both receive (RX buffer full) and transmit (TX buffer empty) interrupts, connected through jumpers to INT3 and INT2 respectively. Both RX and TX clocks of the RS-232 UART are connected to a common programmable counter. The TX baud rate therefore can not be programmed different from the RX baud rate.

The CODEC UART has two separate programmable counters to generate the A/D and D/A sampling rates independently. Some additional logic, two 4029 counters and a few gates, are required to interface the MK 5156 CODEC. The A/D generated interrupt (new data available) is connected to  $\overline{\text{INT6}}$ , and the D/A interrupt (new data required) is connected to  $\overline{\text{INT5}}$ .

All the timing is derived from an on-board crystal oscillator at 6144 kHz. Some DSP programs, like the weather-satellite-picture receiving program, require a very accurate sampling frequency. The

6144 kHz clock is used by the UARTs, divided by 3 to obtain 2048 kHz required by the CODEC and switched-capacitor filter, divided by 2 to obtain 3072 kHz for the timing logic and divided by 4 to obtain 1536 kHz as the input to the programmable dividers. The divider-by-3 is a little more complex to obtain a nearly 50 % duty cycle at 2048 kHz.

To interface directly with analog circuits, receivers or transmitters, the CODEC analog input and output are connected to a switched-capacitor filter (TP 3040). The input audio signal is applied to a bandpass filter with a lower cut-off frequency of 300 Hz and an upper cut-off frequency of 3400 Hz before reaching the A/D converter. The D/A output signal is applied to a lowpass with a cut-off frequency of 3400 Hz.

Additional command lines are also provided, one input and two outputs. Their function is software programmable. The input is usually used as a squelch input (high means valid analog signal). The outputs are used as PTT and CW KEY commands to a transmitter. These two outputs are open-collector and active-low as required by most transmitters. The 75452 driver can handle 300 mA and 30 V on each of these outputs.

The CODEC, the switched-capacitor filter and the RS-232 driver require a negative voltage of -5 V. The latter is obtained on-board with a simple two-transistor flyback inverter similar to that on the video board. The supply voltages of the analog circuits have to be further filtered to avoid any interference from the noisy computer bus +5 V supply rail or inverter. The CODEC also requires two reference voltages. The positive reference is obtained from a red LED providing a stable voltage drop of about 1.8 V. The negative reference tracks the positive reference to avoid distortion using an op-amp (741).

#### 2.7. FLOPPY DISK DRIVE

Although the operating system developed for my DSP computer does not require a mass memory like magnetic disks for its operation, it is very

comfortable to have available a floppy drive. For example, applications programs can be loaded conveniently from a floppy disk for the first time, when initializing the system. Floppy disks are also useful for backup copies and to store large amounts of data for longer periods of time (pictures).

Building the mechanical part of a high-performance floppy drive is probably out-of-reach for an amateur. Available floppy drives come already with some electronics like write and read head amplifiers and motor drivers. Most of the recent floppy drives come with a 34 pole connector carrying TTL level signals in both directions. These signals are standardized. There are also many special purpose chips available, called Floppy Disk Controllers (FDC), to interface the standard "34 pole connector" signals to any microprocessor or DMA controller.

I selected to use 3.5" double-sided floppy disks on a 300 rpm drive at a recording speed of 250 kbps MFM. An 80 track double-sided disk has a raw capacity of 1 Mbyte. Each track has a raw capacity of 6.25 kbytes and the current software formats it into 5 sectors of 1024 bytes each, resulting in a formatted capacity of 800 kbytes per disk.

Floppy disk controllers come either in one chip or as a set of chips. The Western Digital 2797 is a single-chip FDC with an analog data separation PLL. New FDCs have digital PLLs that do not require adjustments, but the 2797 is cheap and easily available. To interface a standard 3.5" floppy drive, it only requires a few open-collector, high-current-sink TTL buffers.

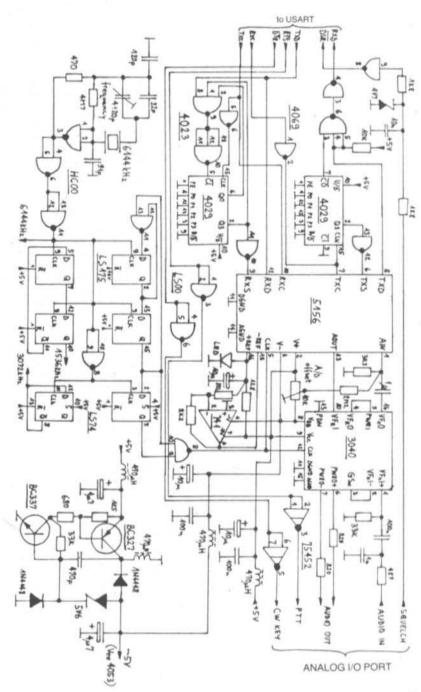

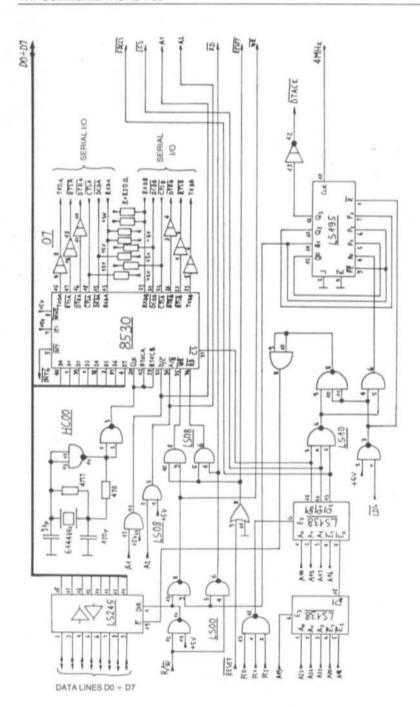

The circuit shown in figs. 2.10. and 2.11. also includes some additional logic to make all of the 2797 functions selectable by software. The circuit to interface the slow 2797 to the fast MC 68010 bus is identical to that used on the analog I/O board. A simple high-speed serial interface, based on a 8530 Serial Communications Controller (SCC), is located on the same board.

The timing for the FDC and bus interface logic is derived from a 16 MHz crystal oscillator. Its frequency is divided down to either 1 or 2 MHz to drive the 2797 clock input in the write mode. In the read mode, the 2797 derives its clocks from an on-chip PLL with a VCO running at 4 MHz.

To maintain software compatibility with its predecessors, the designers of the 2797 chip could not implement all of its functions as control register bits. The corresponding selection pins have to be driven by an additional output port, in this case a LS 273 latch. Two outputs of the LS 273 are used to select the floppy drive directly, bypassing the 2797 chip.

3.5" floppy drives do not have a head load solenoid - the read/write heads are loaded immediately after the disk is inserted into the drive. To avoid unnecessary wear of the disk and heads, it is necessary to stop the spindle motor after read or write operations are completed. In the case of the 2797 FDC, its Head LoaD (HLD) signal has to be used as a Motor On (MO) signal for a 3.5" floppy drive. Correspondingly, the READY input of the 2797 can not be used and the READY output from the drive, if available, should be tied to the Head Load Timing of the 2797. The HLD output of the 2797 has an interesting feature: if not disabled by software it will be disabled automatically after 15 disk revolutions (3 seconds) following the last read or write operation. A software crash or a careless programmer will not destroy the disk nor damage the heads!

Some of the connections between the FDC and the 34 pole connector are brought to a jumper plug to adapt for small differences in the connections of different drives. The two 2797 interrupts, DRQ and INTRQ, are also connected through jumpers to INT4 and INT3 respectively.

The serial communications controller chip (8530) obtains all its timing from a 6144 kHz crystal oscillator, since this frequency can be divided to obtain standard baud rates. The serial port uses the same signal levels as the floppy drive interface: drivers are open-collector, high-current-sink TTL and receivers are simple TTL inputs with pull-up resistors. INT6 is assigned to the SCC, again through a jumper, to handle the high data rates expected.

Fig. 2.10.: Serial I/O and floppy interface board circuit diagram (YT 3 MV 008), part 1

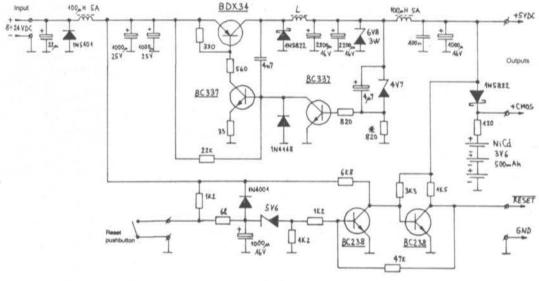

Fig. 2.12.: Power supply board circuit diagram (YT 3 MV 009)

#### 2.8. POWER SUPPLY

Although the design of a power supply is not considered very important by most design engineers, power supplies are usually a major source of troubles in practical electronic circuits, especially computers! Overheating, electrical interferences and unreliable resetting are common problems associated with poorly designed computer power supplies.

A DSP computer is intended to operate together with other analog equipment including sensitive receivers and powerful transmitters. Efficient shielding is a must to avoid interferences in both directions. However, an efficient shielding enclosure is normally very poor from the thermal design point of view since computer chips dissipate most of the heat produced by convection cooling. While it may not be possible to influence the amount of heat produced in the computer chips, other heat sources can be avoided in a

careful design. A good efficiency, switching power supply is a must!

The circuit diagram of the recommended power supply for the DSP computer is shown in fig. 2.12. The power supply is intended to operate from a non-regulated DC supply of nominally 12 V DC, negative grounded, like most other radio-amateur equipment. The efficiency of the simple series switching regulator is above 80 %. Chokes at both input and output are used to suppress both interferences generated by the computer and by the switching regulator itself.

The power supply module includes a 3.6 V, 500 mAh NiCd battery for clock and memory back-up.

The reset circuit is an integral part of the power supply, since it is very difficult to derive the information to operate a reset circuit just from the + 5 V rail on the computer bus. The RESET signal will be applied immediately after the input voltage falls below about 6.5 V. The series regulator is still operating correctly at this input voltage and the RESET signal will effectively protect the vulnerable content of the non-volatile RAM. If the

input voltage falls down to zero, the RESET signal remains active, since it is active-low.

When the input voltage is applied again, the RESET will only be removed after the input voltage goes above about 7 V (hysteresis of about 0.5 V) and after the delay introduced by the 1000  $\mu\text{F}/1.2\,\text{k}\Omega$  time constant. Everyday practical use confirmed that this resetting/protection scheme is failure-proof regardless of the kind of transients on the power line, in severe contrast to what happens with commercial computers, packet-radio TNCs or other equipment using microprocessors!

Since there are just four wires connecting the power supply module to the computer bus: + 5 V, + CMOS, MR and GND, the module is not equipped with an "Eurocard" connector to avoid capacitive loading of the computer bus.

#### 2.9. ANTENNA ROTATOR INTERFACE

Automatic satellite tracking with a steerable antenna system is usually required together with many DSP applications. The described DSP computer is able to generate the required tracking information as a background task to the main DSP task with a minimum additional loading of the CPU. Even in the case of up-dating the antenna pointing direction every second, only about 2 % of the total CPU time is required for the tracking program.

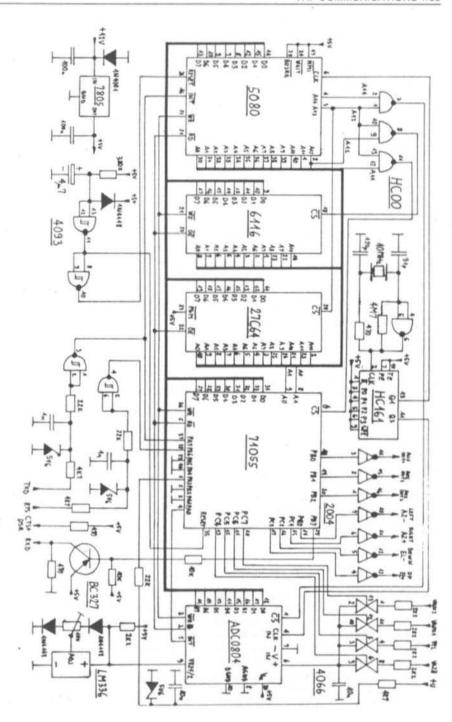

Due to the variety of different antenne rotator systems, I decided not to build any rotator interface inside the computer itself. The rotator interface, shown in fig. 2.13., accepts data from the computer RS-232 port and interfaces to a KR-5600 rotator control unit. It includes an 8 bit microprocessor 5080 (CMOS version of the Z80CPU) with an EPROM (27C64) and a RAM (6116), an A/D converter (ADC0804), darlington relay drivers (2004) and a simplified RS-232 port. Only a very small part of both the EPROM and the RAM are actually used since the software is very simple.

The rotator interface receives the desired antenna azimuth and elevation from the DSP computer. These values are compared with the actual values measured by the position-sensing potentiometers installed on the rotators. The interface microcomputer then decides to activate the motors in the appropriate direction. The software also corrects for the inertia of the rotator and antenna system. The damping coefficients are also up-loaded from the DSP computer. The interface also transmits a complete status report on request from the main computer.

All of the microcomputer components are CMOS versions to keep the current drain low. The overall current consumption of the interface is only about 35 mA. The latter can be derived from the multipole connector on the KR-5600 control unit thus saving the expense of an additional power supply. The interface requires just + 5 V obtained from a three-terminal voltage regulator. The A/D converter has its own 2.5 V reference LM 336. Since the computer memory content is lost after power-down, no special reset circuit is required, an RC network and a Schmitt-trigger gate are sufficient.

The RS-232 serial/parallel and parallel/serial conversions are done in software. Therefore, all the clocks are derived from a single crystal oscillator at 10 MHz — divided by 4 to obtain 2.5 MHz for the CPU and divided by 16 to obtain 625 kHz for the A/D converter.

A parallel I/O port (71055) controls the relay drivers, the analog multiplexer (4066) for the A/D converter and the RS-232 signals. The latter are not completely to the RS-232 specifications, since the output logical-low is only zero volts, but are accepted by most RS-232 receivers. With suitable software the interface could be used with any computer equipped with a RS-232 port.

#### 2.10. FUTURE PLANS

A construction article is planned to follow, discussing also hardware check-out, soft-

ware installation and use of the DSP computer. Some information, like the operating system manual, can not be published since they would take far too much space in the magazine copies will be made available separately. Software will probably be made available on floppy disks, including source files, their corresponding compiled versions and "manual" files describing how to use them.

There will certainly be many upgrades of both the hardware and especially the software. A very successful upgrade was the replacement of all LS-series TTL integrated circuits with the new HC-series. The HC-series integrated circuits. now available at the same price as the older LSs, offer a much lower current consumption (power dissipation!) and a lower bus loading. In addition, their constant, resistive output impedance efficiently suppresses bus ringing, allowing up to 30 % higher CPU clock frequencies.

The next imminent hardware upgrade is certainly a higher capacity memory board. Other peripherals could be built as well, including "intelligent" ones carrying maybe an even more powerful processor than the MC 68010 or a dedicated DSP chip. On the other hand, future antenna rotators will probably include an RS-232 interface and the described rotator interface board will probably become unnecessary.

Of course, most upgrades can be expected in the software. Several algorithms, including the Fast Fourier Transform, have not even been tried vet, although it is known they are possible on the described hardware.

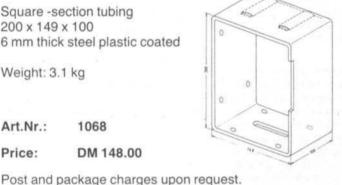

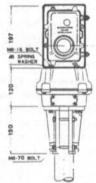

### **Heavy-Duty Support Housing** for KR 5400/KR 5600 Satellite Rotators

This heavy-duty, stable profile replaces the L-bracket which forms part of the KR 5400 or KR 5600 rotator systems. The use of this component ensures a much higher degree of antenna-installation stability.

#### Material:

Square -section tubing 200 x 149 x 100 6 mm thick steel plastic coated

Weight: 3.1 kg

Art.Nr.:

1068

Price:

DM 148.00

Telecommunications, VHF-Communications - UKW-Technik Terry D. Bittan Jahnstraße 14, D-8523 Baiersdorf, Telefon (09133) 470, Telex 629887

Wolfgang Schneider, DD 2 EK

## FM-ATV in the GHz Range Part 1: 23 cm Transmitter

Owing to the advancing developments in the field of satellite television techniques, FM-ATV is becoming of increasing importance to the radio amateur. In addition to the use of ready-made industrial units, the modern semi conductors allow the home construction of

complete FM-ATV transmitters and receivers, well into the GHz range, with the minimum effort. The following multipart article describes the construction of a transmitter/receiver for FM-ATV in the 23 cm band.

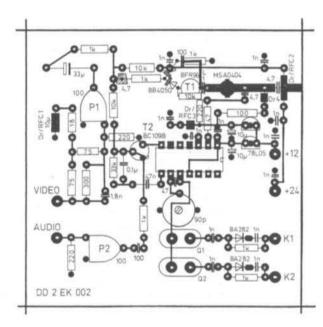

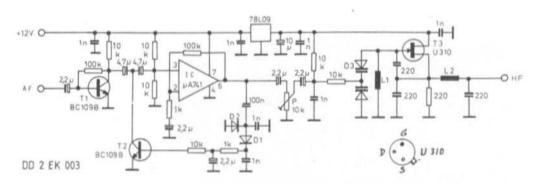

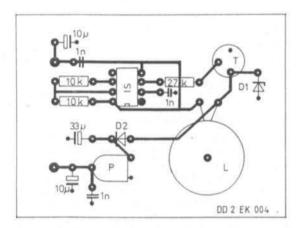

Fig. 1: 23 cm band FM-ATV transmitter

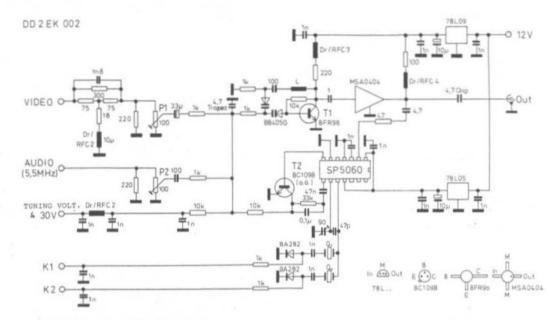

#### 1. CIRCUIT DESCRIPTION

As may be seen from fig. 1, the 23 cm ATV transmitter displays no particular peculiarities. As may be expected, the heart of the transmitter may be regarded as the voltage-controlled oscillator (VCO) included in a phase-locked looped (PLL). This will now be examined in detail.

#### 1.1. The Voltage-Controlled Oscillator (VCO)

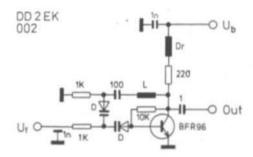

The VCO (fig. 2) was developed using economical, but readily obtainable components. The varicap diodes are normal UHF types and the transistor is also a standard type.

The series resonant circuit comprises an inductor and two varicap diodes (BB405G) connected between the collector and the base of the oscillator transistor. A 100 pF capacitor serves to isolate the varicaps from the DC collector voltage but at the same time its connecting lead forms the series tuning-inductance. Other connections are kept as short as possible in order to prevent the introduction of uncontrolled reactances into the circuit.

The control of the transistor's working point and its quiescent current is achieved by the 10  $k\Omega$  resistor between collector and base and the 220  $\Omega$  resistor in the collector. A small inductance in series with the collector resistor prevents the tuned circuit from being loaded and ensures complete decoupling from the supply voltage.

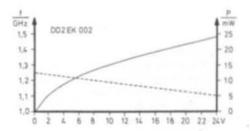

The VCO, as described, is capable of working at 2.2 GHz. The inductor formed from the lead of the 100 pF capacitor determines the resonant frequency of this circuit. In the interesting frequency range around 1.2 GHz, a 0 - 24 volt tuning voltage will enable a spectrum of 500 MHz to be covered! An output power of about 12 mW is obtained at 1 GHz and 5 mW at 1.5 GHz (fig. 3).

#### 1.2. The Phase-Locked Loop

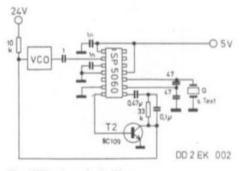

The SP 5060 forms, together with the VCO, a complete PLL frequency synthesizer (fig. 4) which is usable over the range 300 MHz to 2 GHz.

Fig. 2: The voltage-controlled oscillator

Fig. 3: The VCO frequency and the output power (dotted line) as a function of the tuning voltage

Fig. 4: The phase-locked loop

The integrated circuit contains a pre-scaler together with a pre-amplifier and a frequency divider. The latter has a fixed division factor, the ratio between the synthesizer and the reference frequency being 256:1.

The phase comparator is supplied with an external, quartz-derived, reference frequency. The output of the comparator controls the varicap diode in the VCO via an external transistor (BC 109 or equiv.).

Owing to the fixed division factor in the SP 5060's divider, the reference frequency is obliged to be exactly a 256th of the synthesizer frequency. This means that for a desired output frequency, say 1270 MHz, a reference frequency of 1270/256 = 4.9609375 MHz is required.

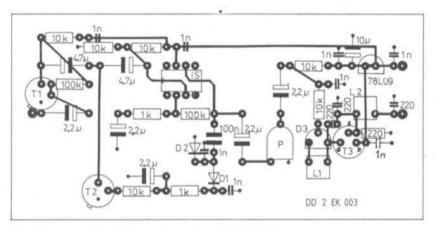

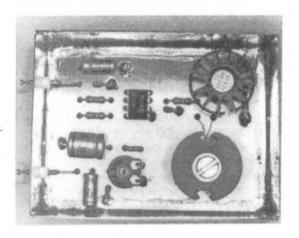

## 2. CONSTRUCTION

The printed circuit board for the circuit described above, is constructed on a double-sided, 1.5 mm thick, epoxy-glass material and of dimensions

$72 \times 72$  mm (see fig. 5). It fits into a proprietary tinplate box  $74 \times 74 \times 30$  mm.

After trimming the board to size, it is cleaned and coated with rub-on silver plating — although this is not absolutely necessary. Then it is drilled. The broadband amplifier is fitted into a suitably cut hole in the board. Also, a slot (1 x 8 mm) is provided, at the appropriate place at the edge of the board, in order to accommodate the BNC socket inner connector spigot.

The board is then drilled for the other components; resistors, capacitors, the crystal etc. Care must then be taken to provide a countersink (using a 2.5 mm drill) around the ungrounded leads on the ground-plane, i.e. component side of the board, in order that the component leads are not inadvertently shorted to earth.

After this work is finished, the board can be treated with flux solution.

Fig. 5: The tracks and components of the double-sided PCB DD 2 EK 002 for the circuit diagram of fig. 1

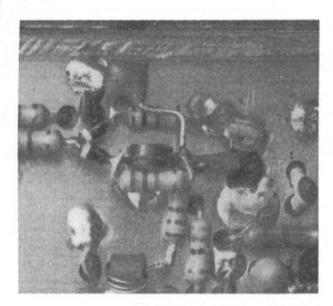

Fig. 6: The VCO showing the selfsupporting-in-air component mounting

When the board is dry, the through-plating contacts can be installed for the broadband amplifier IC. The BNC socket must be installed so that its flange fits to the appropriate place on the frame with its inner spigot in the slot provided on the PCB. The teflon shoulder on the socket may be removed with a sharp knife before mounting. Also, see to it that the module lid is not prevented from fitting when the crystal has been installed (think about this when the board is being soldered into its frame).

Following the correct soldering of the PCB into the box frame, the equipping of the board is carried out. The VCO is wired together "in air" (see fig. 6), the component leads being made as short as possible in order to minimize stray inductance effects. The series inductor in the VCO is formed from the collector-side lead of the 100 pF capacitor connected between base and collector of T 1. For the frequency of interest, about 1.2 GHz, this lead is trimmed to 9 mm and bent through 90°. This may be clearly seen in the photograph of fig. 6.

#### 2.1. Components

- 1 BC109B, BC 413, BC 550 or equiv. low-noise NF types

- 1 BFR96

- 1 MSA0404 (Avantek)

- 1 SP5060 (Plessey)

- 1 78 L 09

- 1 78 L 05

- 2 Diode BB405G

- 2 Diode BA282

- 1 RFC 10 µH (Neosid)

- 1 6-hole ferrite core (Valvo)

- 2 RFC 4 turns 0.3 mm Cu/lac. wire on 3 mm ferrite bead

- 1 90 pF foil trimmer (red)

- 1 4.7 pF trapez, cap.

- 1 4.7 pF chip cap.

- 1 0.47 µF cap. (7.5 mm grid)

- 1 0.1 µF cap. (7.5 mm grid)

- 1 33 µF/35 V elko. (10 mm grid)

- 2 10 µF/16 V tant.

- 2 100  $\Omega$  preset pot. (10 mm grid)

- 1 100 Ω/0.3 W resistor

- 1 Tin-plate box 74 x 74 x 30 mm

- 1 BNC panel mounting socket UG290A/U

- 6 teflon feed-thro insulators

Ceramic disc capacitors (2.5 mm grid)

- 1 1 pF

- 1 4.7 pF

- 1 47 pF

- 2 100 pF

- 12 1 nF

- 1 1.8 nF

Resistors (fixed, 10 mm grid)

- 1 18 Ω

- 1  $47\Omega$

- 2 75 Ω

- 1 100 Ω

- 3 220 Ω

- 1 300  $\Omega$

- 6 1 kΩ

- 3 10 kΩ 1 33 kΩ

Inductors see text.

Crystal

HC-18U or HC-25U (see text)

#### 3. COMMISSIONING

The following test instruments should be available:

- Multi-purpose meter

- Frequency counter (to 1.3 GHz)

- Power meter (to 1.3 GHz)

Following the application of the 12 V supply voltage, the unit should immediately start

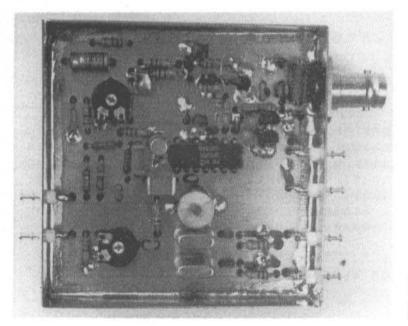

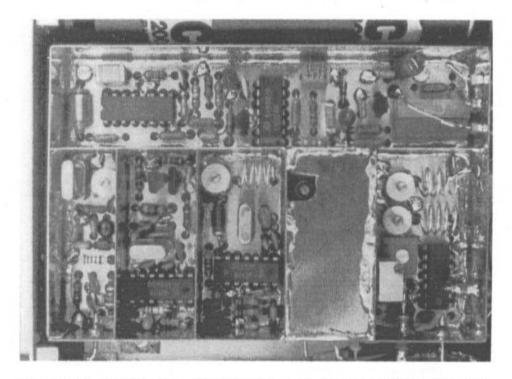

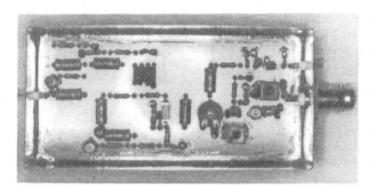

Fig. 7: The completed FM-ATV transmitter module

working, delivering some 20 mW to the power meter. The VCO, however, is not yet locked on to one of the two crystal-determined frequencies but is oscillating at its lowest frequency. The tuning voltage (max. 30 V) is now connected and one of the two crystals put into operation by applying 12 V to the appropriate point. The oscillator is now oscillating, locked at the desired frequency, and if not, it is working outside of the PLL's capture range. This may be corrected either by altering the inductance L or by an adjustment of the control voltage. A small test circuit, which will be described in the second part of the article, will produce an adjustable control voltage from the available 12 V supply voltage.

After the synthesizer has been set-up correctly, the video camera and a frequency-modulated, 5.5 MHz sound carrier can be connected and the unit put into operation. It only remains now to set the frequency deviation with the two preset resistors.

#### 4. LITERATURE

- (1) Grimm, J., DJ 6 PI: Frequency Modulated Amateur Television (ATV) VHF COMMUNICATIONS 18 (1986), Edition 3, P. 165 - 176

- (2) Sattler, Günter: Baugruppen für FM-ATV Sender in den GHz-Bereichen 32. Weinheimer UKW-Tagung (Weinheimer meeting)

- (3) Hirschelmann, Klaus: Gedanken zum Aufbau von einfachen Sendern für FM-ATV 32. Weinheimer UKW-Tagung (Weinheimer meeting)

- (4) Plessey: Data sheet SP 5060

#### Interested in AMATEUR TV ?

....then you need CQ - TV Magazine

CQ - TV Magazine is the quarterly journal of the British Amateur Television Club. The club caters for all aspects of television including amateur transmissions, broadcast reception, video techniques, satellites, SSTV etc.

Details of membership may be obtained by sending

a stamped addressed envelope to:

"BATC", 'Grenehurst', Pinewood Road High Wycombe, Bucks HP12 4DD, U.K.

## Index of Volume 20 (1988)

| Article                                                                       | Author                                                | Edition | Pages     |

|-------------------------------------------------------------------------------|-------------------------------------------------------|---------|-----------|

| ANTENNA TECHNOLOGY                                                            |                                                       |         |           |

| Rear-Feed Dish Radiator with Corrugated Horn                                  | Dr. med. Hans Schlüter,<br>DJ 7 GK                    | 1988/1  | 8- 9      |

| Receiving METEOSAT with Yagis                                                 | Andreas Schaumburg,<br>DF 7 ZW                        | 1988/1  | 15 - 18   |

| A 2 m/70 cm Antenna Splitting Filter                                          | Jochim Kestler,<br>DK 1 OF                            | 1988/1  | 26 - 30   |

| A Compact Hybrid Antenna for 2 m, 70 cm and 23 cm                             | Hannes Fasching,<br>OE 5 JFL                          | 1988/4  | 212 - 217 |

| An Introduction to Moonbounce (EME)                                           | Willi Rass,<br>DF 4 NW                                | 1988/4  | 218 - 232 |

| FUNDAMENTALS · NEW TECHNOLOGY                                                 |                                                       |         |           |

| Wideband Power-Divider/Combiner for the 2 m and 70 cm Bands                   | Konrad Hupfer,<br>DJ 1 EE                             | 1988/1  | 2- 7      |

| Digital Signal Processing Techniques for<br>Radio Amateurs — Theoretical Part | Matjaž Vidmar,<br>YT 3 MV                             | 1988/2  | 76 - 97   |

| Stabilizing the VCO Frequency by Means of<br>Monostables – Part 1             | Dr. (Eng.) Ralph Oppelt,<br>DB 2 NP                   | 1988/4  | 238 - 245 |

| POWER SUPPLIES                                                                |                                                       |         |           |

| A 12 Volt to 12 Volt Converter                                                | Dr. Eng. Jochen Jirmann,<br>DB 1 NV                   | 1988/1  | 19 - 25   |

| A Stabilized Power Supply for Valved PAs                                      | Wilfried Hercher, DL 8 MX/<br>Jochen Jirmann, DB 1 NV | 1988/4  | 246 - 251 |

|                                                                               |                                                       |         | 31        |

| Article                                                            | Author                                | Edition | Pages     |

|--------------------------------------------------------------------|---------------------------------------|---------|-----------|

|                                                                    |                                       |         |           |

| MEASURING TECHNOLOGY                                               |                                       |         |           |

| A Thermal Power Mount                                              | Dr. Eng. Jochen Jirmann,<br>DB 1 NV   | 1988/2  | 98 - 102  |

| 50 $\Omega$ Wideband Detectors                                     | Carsten Vieland,<br>DJ 4 GC           | 1988/2  | 111 - 125 |

| A 1,5 GHz Plug-In for the DL Ø HV Frequency Counter                | Dieter Schwarzenau/<br>Bernhard Kokot | 1988/3  | 130 - 137 |

| Digital Storage Interface for the SWOB-2 Sweep Generator           | Ralph Berres,<br>DF 6 WU              | 1988/3  | 138 - 140 |

| Providing a Frequency Counter for the SWOB                         | Ralph Berres,<br>DF 6 WU              | 1988/3  | 142 - 146 |

| AMATEUR TELEVISION                                                 |                                       |         |           |

| Improved AFC Unit for the DJ 4 LB<br>ATV-Transmitter Sound Carrier | Ralph Berres,<br>DF 6 WU              | 1988/1  | 35 - 38   |

| ATV-FM Driver for the 13 cm Band                                   | Hubertus Rathke,<br>DC 1 OP           | 1988/1  | '39 - 49  |

| 70 cm Converter using GaAs-FET CF 300                              | Wolfgang Schneider,<br>DD 2 EK        | 1988/1  | 50 - 53   |

| FM Television for the Amateur                                      | John Wood,<br>G 3 YQC                 | 1988/4  | 194 - 211 |

|                                                                    |                                       |         |           |

| TV SATELLITE RECEPTION                                             |                                       |         |           |

| Receiving Converter for 4-GHz-Band Satellite                       | Matjaž Vidmar,<br>YT 3 MV             | 1988/2  | 103 - 110 |

| WEATHER SATELLITE RECEPTION                                        |                                       |         |           |

| Receiving METEOSAT with Yagis                                      | Andreas Schaumburg,<br>DF 7 ZW        | 1988/1  | 15 - 18   |

| Timer/Zoom Unit for the YU 3 UMV/DL 6 NAD Image Storage            | Klaus Gottwaldt/<br>Editorial Staff   | 1988/3  | 147 - 151 |

| A Digital Multi-Image Storage for WEFAX<br>Images – Part 2         | Harald Hufenbecher,<br>DL 6 NAD       | 1988/3  | 152 - 157 |

| More on the PC Interface for the<br>YU 3 UMV Weather Picture Store | Hans Oppermann,<br>Quickborn          | 1988/3  | 179 - 180 |

| 32                                                                 |                                       |         |           |

| Article                                                                     | Author                              | Edition | Pages     |

|-----------------------------------------------------------------------------|-------------------------------------|---------|-----------|

| OCCUL ATORS                                                                 |                                     |         |           |

| OSCILLATORS Improved AFC Unit for the DJ 4 LB ATV-Transmitter Sound Carrier | Ralph Berres,<br>DF 6 WU            | 1988/1  | 35 - 38   |

| FILTERS                                                                     |                                     |         |           |

| A 2 m/70 cm Antenna Splitting Filter                                        | Joachim Kestler<br>DK 1 OF          | 1988/1  | 26 - 30   |

| INTERESTING COMPONENTS                                                      |                                     |         |           |

| Microwave Power Transistors                                                 | Editors                             | 1988/1  | 10 - 12   |

| The SDA 4212 - the 4211's Successor                                         | Armin Meier,<br>DC 7 MA             | 1988/1  | 13 - 14   |

| SHORTWAVE, IF-MODULES                                                       |                                     |         |           |

| Short-Wave Pre-Selector/Amplifier                                           | Wolfgang Guenther,<br>DF 4 UW       | 1988/3  | 181 - 185 |

| 2 m BAND                                                                    |                                     |         |           |

| Wideband Power-Divider/Combiner for the 2 m and 70 cm Bands                 | Konrad Hupfer,<br>DJ 1 EE           | 1988/1  | 2- 7      |

| A 2 m/70 cm Antenna Splitting Filter                                        | Joachim Kestler,<br>DK 1 OF         | 1988/1  | 26 - 30   |

| A Super Power Amplifier for 144 MHz EME                                     | Dragoslav Dobričić,<br>YU 1 AW      | 1988/3  | 158 - 170 |

| A Compact Hybrid Antenna for 2 m, 70 cm and 23 cm                           | Hannes Fasching,<br>OE 5 JFL        | 1988/4  | 212 - 217 |

| An Introduction to Moonbounce (EME)                                         | Willi Rass,<br>DF 4 NW              | 1988/4  | 218 - 232 |

| Stabilizing the VCO Frequency by Means of<br>Monostables – Part 1           | Dr. (Eng.) Ralph Oppelt,<br>DB 2 NP | 1988/4  | 238 - 245 |

| 70 cm BAND                                                                  |                                     |         |           |

| Wideband Power-Divider/Combiner<br>for the 2 m and 70 cm Bands              | Konrad Hupfer, DJ 1 EE              | 1988/1  | 2- 7      |

| A 2 m/70 cm Antenna Splitting Filter                                        | Joachim Kestler,<br>DK 1 OF         | 1988/1  | 26 - 30   |

| Article                                                                                                                    | Author                                          | Edition | Pages     |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------|-----------|

|                                                                                                                            |                                                 |         |           |

| 70 cm Converter using GaAs-FET CF 300                                                                                      | Wolfgang Schneider,<br>DD 2 EK                  | 1988/1  | 50 - 53   |

| A Compact Hybrid Antenna for 2 m, 70 cm and 23 cm                                                                          | Hannes Fasching,<br>OE 5 JFL                    | 1988/4  | 212 - 217 |

| 432 MHz Linear PA using 3 x 2C39BA                                                                                         | Dragoslav Dobričić,<br>YU 1 AW                  | 1988/4  | 233 - 237 |

| 23 cm BAND                                                                                                                 |                                                 |         |           |

| A 1296 MHz, 200 mW Driver using<br>SMD Technology                                                                          | Armin Roesch,<br>HB 9 MFL                       | 1988/1  | 54 - 59   |

| A Compact Hybrid Antenna for 2 m, 70 cm and 23 cm                                                                          | Hannes Fasching,<br>OE 5 JFL                    | 1988/4  | 212 - 217 |

| 13 cm BAND                                                                                                                 |                                                 |         |           |

| ATV-FM Driver for the 13 cm Band                                                                                           | Hubertus Rathke,<br>DC 1 OP                     | 1988/1  | 39 - 49   |

| 3 cm BAND                                                                                                                  |                                                 |         |           |

| Rear-Feed Dish Radiator with Corrugated Horn                                                                               | Dr. med. Hans Schlüter,<br>DJ 7 GK              | 1988/1  | 8- 9      |

| MISCELLANEOUS                                                                                                              |                                                 |         |           |

| GrafTrak and Mirage Interface (MTI) —<br>Something Really Good for the Radio Amateur!                                      | Klaus Eichel, DC 6 HY/<br>Hans-L. Rath, DL 6 KG | 1988/2  | 66 - 74   |

| GrafTrak and Mirage Tracking Interface (MTI) —<br>Something Really good for the Radio Amateur!<br>Second (concluding) Part | Klaus Eichel, DC 6 HY/<br>Hans-L. Rath, DL 6 KG | 1988/3  | 171 - 178 |

Andrew Bell, GW 4 JJW

# Morse Code Generator for Microwave Applications

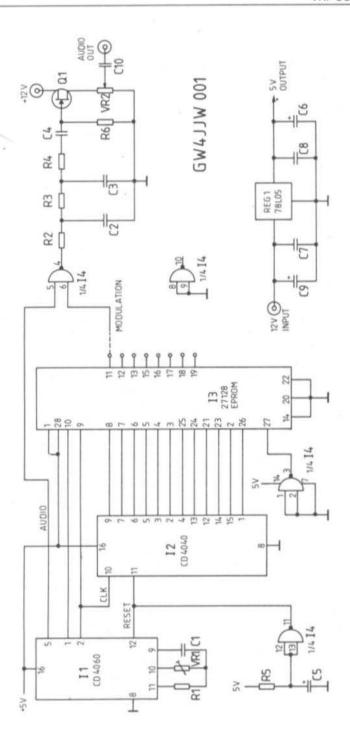

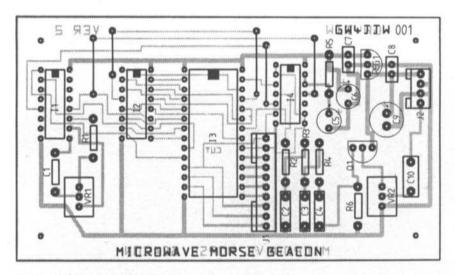

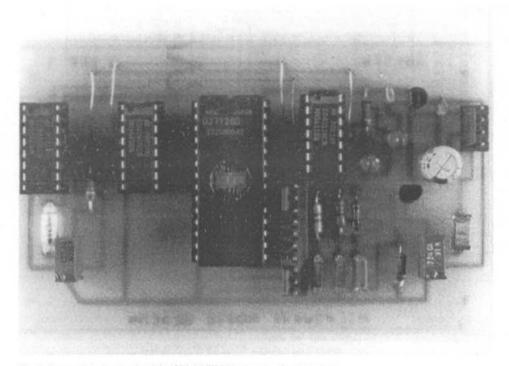

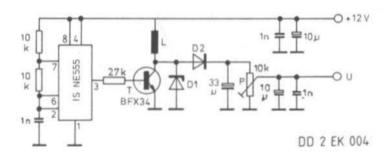

This single-sided PCB (fig. 2) generates a morse code modulated tone which can be fed into the modulator of a microwave transmitter. The morse code is stored in an EPROM and it takes about 20 minutes to scan through the entire EPROM at about 15 wpm. When the end is reached, scanning is restarted from the beginning of the EPROM. The theory is that periods of continuous tone or silence may be interspersed with morse code at will. The input to the board is  $\pm$  12 volt and the output is a low-pass-filtered, morse code modulated audio tone.

## CIRCUIT DESCRIPTION

I1, a 12-stage CMOS oscillator and divider, is set to oscillate at about 28 kHz by means of C 1 and VR 1 (fig. 1). Square wave audio is taken from pin 5 after a division by 32 to yield a frequency of about 880 Hz. After division of the original signal by 8192, the signal is passed on to the I2, a CD 4040, for 12 more stages of division. The results of the last 14 stages of division are taken

from the counters and passed to the EPROM on its address lines. The EPROM will then step through about 14 addresses per second which represents a morse code speed of about 15 wpm. At any specific address if a data bit is found to be logical-one, a tone will be generated, otherwise a period of silence will follow. On the prototype (fig. 3) only bit-zero was used although provision has been made via a ten-way molex connector, J 1, to select any one of the 8-bits which emerge from the EPROM by means of a switch. The EPROM data bit, which is really a 'tone-enable' signal, is passed to I4, a CD 4011 NAND gate, where it is combined with the square-wave tone signal. The output is audible morse code. This is passed through a two-stage R/C filter to remove many harmonics and glitches caused by the slow propagation time of the counters. It then goes to a common drain JFET amplifier to convert the high output impedance of the filter to a much lower value. The function of R 4 is to reduce the amplitude of the audio signal. Finally VR 2 serves to vary the amplitude of the morse modulated audio signal which is AC-connected to the 4-way molex connector.

A power-on reset comprising R 5 and C 5 ensures that on power-up the EPROM address is set to zero.

Fig. 1: Beacon circuit diagram

Fig. 2: PC-board GW 4 JJW 001

#### 1.1. Connection

In the prototype the audio output was left continuously connected to the Gunn diode modulator and the 12 V supply was switched on when required. (In this way the EPROM does not consume power when its function is not required.) The morse code speed, and therefore the frequency of the tone, are adjusted by VR 1. The amplitude of the signal is adjusted by VR 2.

#### 1.2. EPROM Programming

The EPROM contains a time image of the morse code to be sent out over the twenty minute period. Every address in the EPROM dictates whether a tone should be output or not. This state lasts for the period of a morse code dot before the EPROM address is incremented.

The author wrote a small BASIC program on a BBC microcomputer which translated ASCII text into morse code \*. If a tone was required the byte was set to 255, but otherwise it was set to

254. (The author only used bit-0 and unused bits were set to 1 to speed up programming, but later the program was enhanced and is now able to generate each of the 8-bits of the EPROM separately so that 8 different "messages" may be stored in the EPROM). A morse code 'dash' would therefore be programmed as 3 consecutive addresses set to 255. These results were written to a disc file and later used to program the EPROM. If more than a single bit is used, it may be useful to dedicate one bit to a continuous tone. A ground connection is provided on the ten-way molex plug for 'no tone'.

#### 2. CONCLUSION

The author combined this board with a simple Gunn oscillator and modulator and the resulting 'beacon' has proved most valuable in setting up

<sup>\*</sup> A paper listing of the program will be sent upon request against C.R.I. (coupon-réponse international).

Fig. 3: A completed example of the GW 4 JJW 001 morse code generator

microwave receivers. In particular, one can be sure that the receiver is being aligned on the correct signal and not a spurious one.

#### 3. COMPONENTS

11 CD 4060 12 CD 4040 13 27128 EPROM 14 CD 4011 REG 1 78L05 Q1 J 310/MPF 102

38

R 1 100 K R2 8 K 2 R3 68 K R4 1 M R5 33 K R6 100 K VR 1 100 K (multiturn) VR 2 1 K (multiturn) C1 470 pF polystyrene C2 18 nF layer C3 2 n 2 layer C4 10 nF layer C 5/C 6 10 µF 16 V tantalum C 7/C 8 10 nF plate ceramic C9 100 μF 25 V can electrolytic C 10 0.1 µF layer

J 1 10-pin vertical molex (optional) J 2 4-pin vertical molex

Carsten Vieland, DJ 4 GC

## UHF and SHF Broadband Mixers

For frequencies higher than the 70 cm band, the overwhelming majority of amateur mixers are singly-balanced, narrow-band types. However, the positive qualities of symmetrical passive mixers with 50  $\Omega$  ports such as, inter-port isolation, suppression of an undesirable mixer product or freedom from self-oscillation tendencies, are available at frequencies above 1 GHz.

The definite qualities of broadband 50  $\Omega$  mixers are evident not only in transmit and receive techniques but also in measurement techniques. The low-cost region of industrially manufactured mixers have, in the meantime, reached the 13 cm band (e.g. SRA-11H or LMX-123) and as a result, these mixers have become too expensive for most amateurs. The present technology strives for a band from 2 to 26 GHz.

This article describes broadband mixers which, because of their use of printed circuit boards, are easily and reliably reproducible, demand the use of no expensive components and by means of the well-tried mixer-attenuation, achieves the multi-octave bandwidth of 2 - 11 GHz.

Stimulated by a publication in a Germanlanguage, microwave magazine (1), the mixer described here, represents a translation of the published high-tech version into one using readily obtainable materials and components. The astonishing bandwidth specification proved extremely independent of component tolerances and diode characteristics. Practical experiments have shown that despite the use of not so favourably specified diodes or incorrect di-

mensioning, e.g. of the slotted lines, the characteristics of the mixer circuit are, in the main, well preserved.

#### 1. CONSTRUCTION

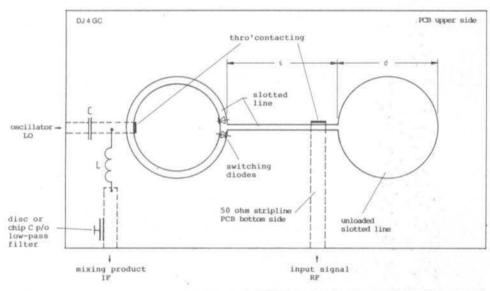

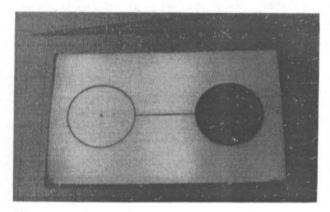

The ring mixers which have long been popular e.g. SRA-1, IE-500 or HPF-505, contain two wideband, ferrite transformers and a ring mixer consisting of four Schottky diodes. Ferrite transformers exhibit sharp hysterisis losses above about 3 GHz, thus forming a natural barrier for this technology. Using powdered-iron cores has the disadvantage of narrower bandwidths. In the SHF region therefore, circuits are preferred which utilize the phase relationships of transformer tuned lines, Wilkinson combiners or symmetrical lines to produce the necessary diode phasing. In the following construction, a combination of strip and slotted lines (fig. 1) is used in order to achieve symmetry over a wide band.

#### 1.1. PCB Material

The important circuit components are located on a double-sided PCB. As there can be no resonant structures in such a circuit, epoxy-glass base material can be used up to about 3 GHz. RT/ Duroid in 0.79 mm thickness and Keene teflon substrate are usable up to about the X-band

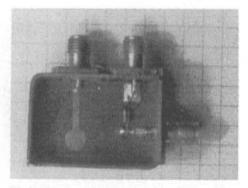

Fig. 1: The constructed details of a wideband, microwave mixer on a two-sided PCB

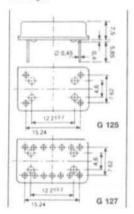

| Mixer | d     | S     |  |

|-------|-------|-------|--|

| SHF   | 5 mm  | 7 mm  |  |

| UHF   | 18 mm | 16 mm |  |

(10.3 GHz). Ceramic substrates, owing to their high relative permittivity (9.7) and small loss-angle, appear at first to be ideal candidates. However, the difficulty of obtaining them and also the subtle methods attending the machining of this brittle material at an amateur level, forced

higher losses to be tolerated by the use of more pliable and obtainable materials.

Besides that, however, there are new PCB materials appearing in the trade which impregnate the teflon carrier material with pulverized

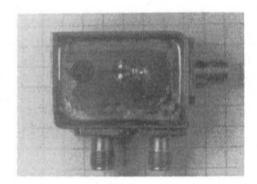

Fig. 2: Etched mixer board with two BA 481

ceramic (e.g. RT/Duroid 6010 from Mauritz in Hamburg). The consequence of a high permittivity of over 9, is a reduced stripline width for 50  $\Omega$  to 0.65 mm (substrate thickness 0.635 mm). The realizable slot width of 0.2 mm results in a better wideband match to the diodes than can be obtained with the "normal" base materials having permittivities of around 2.34. Narrow striplines are therefore to be preferred to wide ones because of the lower energy loss by radiation and the resulting insensitivity to the fitting of covers on the instrument's specifications.

#### 1.2. UHF Mixer

In this construction (fig. 2) the local-oscillator signal is fed in from the stripline via a through-contact into a circular formed slotted line. From the feed-in point of view, this arrangement appears like a parallel circuit consisting of two carrier lines. The L.O. signal is fed in-phase to the back-to-back diodes (fig. 3). The two diodes will conduct according to the momentary polarity of the oscillator signal. As in all passive mixers, the local oscillator has the function of opening

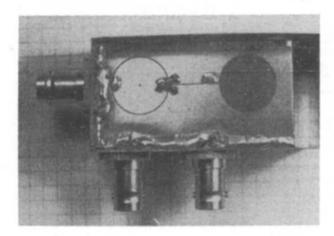

Fig. 3: A complete UHF mixer in its metal box (slotted-line side)

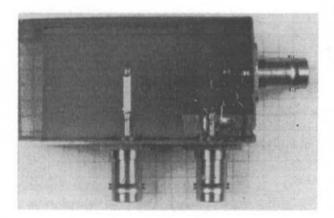

Fig. 4: Stripline side of the UHF mixer showing the IF low-pass filter, the inductor of which is fashioned from bent wire (grid = 5 mm)

and shutting the diodes at a pre-determined rate. This role could be fulfilled by a relay contact if it were fast enough.

The mixing products are taken from the slotted-line island. The lower difference-signal is selected by a low-pass filter (fig. 4) and taken to a coaxial socket. In order to avoid connecting losses, an isolating capacitor (of e.g. 10 pF) is placed in the oscillator's stripline lead-in, which acts as a high-pass filter. As, normally, the IF and the L.O. signals lie very far apart in frequency, no formal diplexer is required for this purpose.

The HF input signal is, either capacitively or via a through-contact, (fig. 4), fed into the slotted line. On the one side, it goes to a circular-formed expansion (unloaded slotted-line) which acts as an impedance discontinuity point. The input signal is reflected from this point and taken to the L.O.-controlled diode switch. From here, and at a clock speed determined by the L.O., energy is transferred to the slotted-line island, first from one diode and then from the other oppositely-phased diode. The multiplexed signal contains both the sum and the difference frequenicies. This arrangement is representative of a simple balanced mixer circuit.

The dimensioning of the slotted line poses many problems. As opposed to striplines, the characteristic impedance of slotted lines is considerably more frequency-dependent. As only the opposite copper edges of the slot are involved in the transport of energy, there is a higher additional loss due to skin-effect which increases with frequency. The various line lengths can never be terminated at every frequency with its nominal impedance. This inevitably, not only leads to both an increasing attenuation with frequency but also to a pronounced ripple across the working band of the mixer.

The prototype used photo-resist PCB material (e.g. RT/Duroid 5870). Both striplines are 2.4 mm wide and are located on the underside of the board. They are made by adhering black strips directly to the photo-resist. Then an exposure is made, followed by developing and etching.

The slotted-line structure can be made quite easily by the use of a pair of divider scribers to scratch a circle in the photo-resist. During the

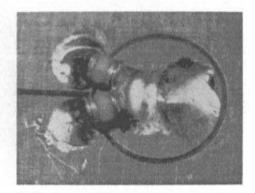

Fig. 5: SHF mixer (slotted-line side) showing both diodes (BAT 14-093). All connectors are SMA (grid = 5 mm)

Fig. 5a: Close-up of the mixer diodes

Fig. 6: The mixer of 5 above from the stripline side.

The cross-shaped structure is the printed

RF input capacitor

X

following etching process, a 0.25 mm wide slot is formed in the copper-clad surface (fig. 2). The production of a suitable exposure mask is much too time-consuming for a one-off job.

housings. By using a large L.O. input power (+ 13 dBm), the characteristics of these diodes allow a particularly good intercept point (IP) to be achieved.

#### 1.3. SHF Mixer

The SHF mixer is shown in **figs. 5 and 6**. The RF input signal is coupled-in capacitively from the stripline to the slotted line by means of a printed structure. In the UHF version, this structure would have been too large, which is why the throughcontacting was used. The function is not, however, greatly influenced by the type of input coupling.

The lower limit frequency of this mixer type is reached when the line length of the circular slotted line presents little or no diversion length for the RF signals.

The isolating capacitor in the oscillator branch should be of the "chip" construction (e.g. ATC). Also, the switching diodes (fig. 5a) could be chosen in the first instance, according to their form of construction — the smallest form of any particular type being selected. Glass diodes (BA 481) exhibit good characteristics well into the S band. For use in the X band, a microwave diode housing must be employed. The favourably-priced GaAs diodes MGF 3000 can be used in spite of the somewhat large size of their

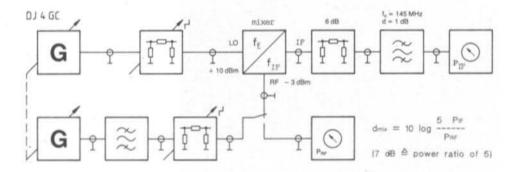

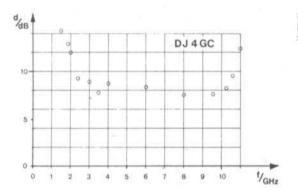

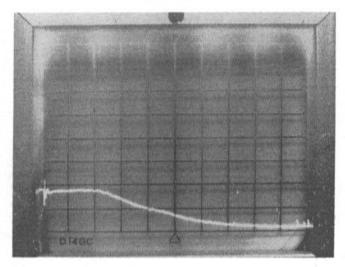

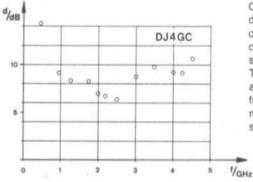

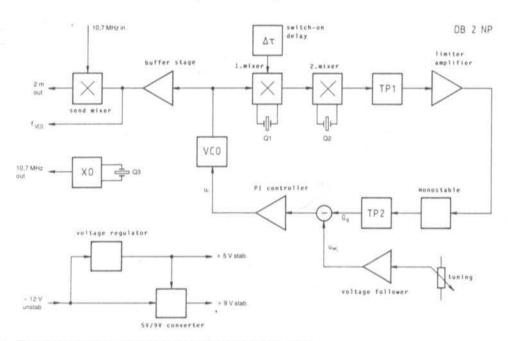

#### 2. MEASURED RESULTS