# Electronic Vol. 7, No components & applications

198

## Electronic components & applications

Volume 7, No.2

1985

## Contents

| 66  |

|-----|

| 73  |

| 77  |

| 81  |

| 89  |

| 95  |

| 106 |

| 112 |

| 116 |

| 119 |

| 122 |

| 125 |

| 128 |

|     |

All information in Electronic Components and Applications is published in good faith, but the publishers assume no flability for any consequence of its use, its publication does not imply a licence under any patent. Specifications and availability of goods mentioned in it are subject to change without notice.

Editors Ian L. A. Crick Michael J. Prescott Design and production Cees J. M. Gladdines Bernard W. van Reenen Jacob Romeijn Michael J. Rose Design consultant Theo Kentie

When Christopher Columbus set sail for the Indies in 1492, all he had to guide him were his compass, his knowledge of the heavens and his sailor's insight. In those days there were no official charts to aid him, no chronometers to help him calculate longitude, and the sextant was more than 100 years in the futurel Contrast that with the host of electronic navigation aids available to the sailors of today. Like the crew of The Philips Innovator currently competing in the Whitbread Round the World Race. To help them on their voyage they have a Philips 'ap navigator' for coastal navigation, a Magnavox MX 4102 satellite navigator, and a facsimile receiver for supplying them with weather charts. For communication they have the latest Mariphone equipment plus telex facilities. No doubt all this would have greatly impressed Columbus. But if he'd possessed it, maybe he would have found his route to the Indies after all — and who knows, maybe America would still be undiscovered!

## Astable multivibrators using HCMOS ICs

#### **R. VOLGERS**

74HC/HCT/HCU high-speed CMOS (HCMOS) logic ICs dissipate little power, have a wide operating voltage and temperature range and a low temperature coefficient of the input switching threshold voltage. This makes them ideal for constructing simple yet reliable astable multivibrators in which the operating frequency is determined by a single RC network. What's more, the high impedance of HCMOS inputs allows a wide range of switching time-constants (wide frequency range) to be selected without using high value capacitors which would increase the dynamic power dissipation. This article describes a basic astable circuit using two 74HC/HCU or two 74HCT inverting gates or buffers and derives simple formulae for accurately determining its operating frequency. It then develops the formulae to show how adding one resistor to the circuit makes the operating frequency and duty factor more independent of supply voltage variations and input switching threshold voltage spreads, and limits the input current. The article concludes by discussing the effect of temperature variations, the dynamic power dissipation and the range of external component values and supply voltage that can be used for the circuit.

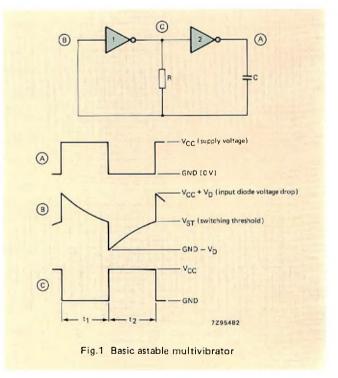

#### **BASIC ASTABLE MULTIVIBRATORS**

Figure 1 illustrates the circuit arrangement and waveforms for a basic astable multivibrator using two HCMOS inverters. When the supply voltage (V<sub>CC</sub>) is applied to the circuit, the potential at points A and B will be of opposite polarity to that at point C (e.g. points A and B LOW, point C high). The capacitor then begins to charge and the potential at point B approaches the switching threshold voltage (V<sub>ST</sub>) of inverter 1. When the voltage at point B reaches V<sub>ST</sub>, the output of inverter 1 (point C) goes LOW, and the output of inverter 2 (point A) goes HIGH. Because the level change at point B is clamped within the limits V<sub>CC</sub> + V<sub>D</sub> and  $GND - V_D$  by the input protection network of inverter 1. The potential at point B now approaches  $V_{ST}$  again and, when it reaches that level, the circuit again changes state and the cycle repeats. The equations for switching periods t<sub>1</sub> and t<sub>2</sub> are:

$$t_1 = -RC \ln \frac{V_{ST}}{V_{CC} + V_D}$$

(1)

$$t_2 = -RC \ln \frac{V_{CC} - V_{ST}}{V_{CC} + V_D}$$

(2)

$$t_1 + t_2 = -RC \ln \frac{V_{ST} (V_{CC} - V_{ST})}{(V_{CC} + V_D)^2}$$

(3)

### Influence of supply and switching threshold voltage variation

For a circuit using a 74HC/HCU IC with VST = 0.5 V<sub>CC</sub> and V<sub>D</sub> = 0.7 V, the switching period varies by +9% and -2.5% around the value at V<sub>CC</sub> = 5 V over the supply voltage range 3 V to 6 V. This variation is due to the influence of the forward voltage drop across the input protection diodes of inverter 1 (V<sub>D</sub> = 0.7 V) which causes the value

$$\ln \frac{V_{\rm ST}}{V_{\rm CC} + V_{\rm D}}$$

to vary with supply voltage variations even though VST is a constant percentage of V<sub>CC</sub>. Since V<sub>ST nom</sub> is 0,5 V<sub>CC</sub> for 74HC and 74HCU ICs, the peaks of the voltage at point B in Fig.1 are symmetrical around V<sub>ST</sub>, resulting in a duty factor of 0,5 which is independent of supply voltage variations. However, the nominal switching threshold voltage is subject to a spread (0,3 V<sub>CC</sub> to 0,7 V<sub>CC</sub> for 74HC ICs and 0,2 V<sub>CC</sub> to 0,8 V<sub>CC</sub> for 74HCU ICs). This causes the total switching period to increase by a maximum of 10,5% for a circuit using a 74HC IC and 27% for a circuit using a 74HCU IC. The switching threshold voltage spread also causes the duty factor to spread between the limits 0,7 to 0,3 for a circuit using a 74HC IC, and 0,8 to 0,2 for a circuit using a 74HCU IC.

For a circuit using a 74HCT IC, the nominal V<sub>ST</sub> is 1,3 V at V<sub>CC</sub> = 4,5 V, 1,415 V at V<sub>CC</sub> = 5 V and 1,53 V at V<sub>CC</sub> = 5,5 V. The switching threshold voltage is therefore always below the midpoint of the total voltage swing at point B in Fig.1, and is not a constant percentage of the supply voltage. Because the supply voltage range for 74HCT ICs is only 4,5 V to 5,5 V, the value

$$\ln \frac{V_{ST}}{V_{CC} + V_D}$$

varies less over the supply voltage range than it does for a circuit using a 74HC/HCU IC, resulting in a switching period variation of  $\pm 0.8\%$  around the value at V<sub>CC</sub> = 5 V over the supply voltage range. However, because the voltage swing at point B in Fig.1 is asymmetrical around V<sub>ST</sub>, the periods calculated with equations (1) and (2) are unequal, resulting in duty factors of 0.74 at V<sub>CC</sub> = 4.5 V, 0.75 at V<sub>CC</sub> = 5 V and 0.76 at V<sub>CC</sub> = 5.5 V. Furthermore, the nominal V<sub>ST</sub> of 74HCT ICs is subject to a spread of about  $\pm 0.5$  V. With a 5 V supply, this causes a maximum switching period increase of 16% above the nominal value, and a duty factor spread from 0.8 to 0.6.

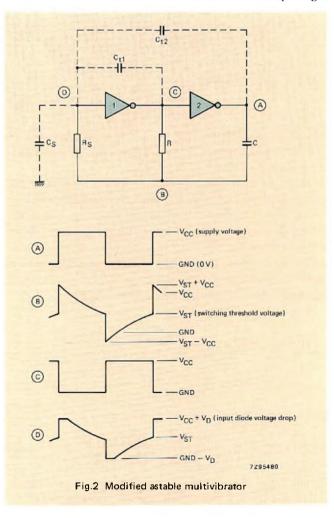

#### CIRCUIT MODIFICATION TO REDUCE SWITCHING PARAMETER VARIATIONS

Figure 2 shows the astable multivibrator circuit modified by the addition of resistor  $R_S$  in series with the input to inverter 1. This resistor increases the resistance between point B and the input to inverter I, and thereby prolongs the discharge of capacitor C via the input protection network of inverter 1 each time the polarity of the charge on capacitor C reverses. If the value of Rs is high enough, the voltage at point B will reach the limits VCC+VST and  $V_{ST} - V_{CC}$  before the voltage at point D reaches the switching threshold voltage. Since the waveform at point B now swings by  $\pm V_{CC}$  around VST, it is always symmetrical about VST regardless of the value of VST or VCC. If the value of RS is too low, the peaks of the waveform at point B will be clipped; if it is too high and a buffered 74HC IC is being used, spurious oscillations or glitches may occur due to stray capacitance Ct1 causing phase-shifted feedback around inverter 1. It is therefore preferable to use the unbuffered Hex Inverter 74HCU04 for this circuit. The optimum value for RS is 2R. It will be shown later that increasing the value of RS beyond 2R doesn't result in any further improvement of the performance of the circuit. The waveform at the input to inverter 1 (point D) is clamped by the input protection diodes to V<sub>CC</sub> + V<sub>D</sub> for positive-going swings, and to  $-V_D$  for negative-going swings, but resistor RS limts the current flow through the input protection network during these periods. The presence of RS therefore also reduces crosstalk to other inverters in the same package.

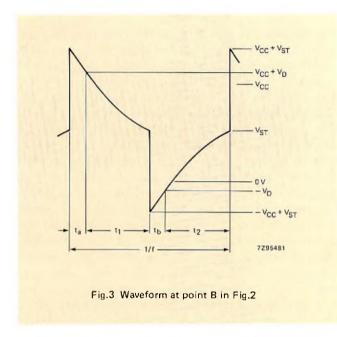

#### ASTABLE MULTIVIBRATORS WITH HCMOS

Figure 3 is a more detailed version of the waveform at point B in Fig.2. Period  $t_1$  is still defined by equation (1), and period  $t_2$  is still defined by equation (2). The equations for additional periods  $t_a$  and  $t_b$  are:

$$t_{a} = -\frac{K}{K+1} RC \ln \frac{K(V_{CC} + V_{D})}{K(V_{CC} + V_{ST}) + V_{ST} - V_{D}}$$

(4)

$$t_{b} = -\frac{K}{K+1} RC \ln \frac{K(V_{CC} + V_{D})}{K(2V_{CC} - V_{ST}) + V_{CC} - V_{ST} - V_{D}}$$

(5)

where  $K = (R_S + R_I)/R$ , and  $R_I$  is the input resistance of inverter 1 when one of the input protection diodes is conducting (about 125  $\Omega$ ).

Since periods  $t_a$  and  $t_b$  increase with increasing supply voltage, and periods  $t_1$  and  $t_2$  decrease, the total switching period and duty factor of the waveform at point B in the modified circuit tends to be stabilized against supply voltage variations. Since  $t_a$  and  $t_2$  increase with increasing switching threshold voltage, and  $t_1$  and  $t_b$  decrease, the total switching period and duty factor also tend to be stabilized against spread of the switching threshold voltage.

If  $K \ge 2$ , periods  $t_1 + t_a$  and  $t_2 + t_b$  are:

$$t_1 + t_a = -RC \ln \frac{V_{ST}}{V_{CC} + V_{ST}}$$

$$t_2 + t_b = -RC \ln \frac{V_{CC} - V_{ST}}{2V_{CC} - V_{ST}}$$

The total switching period is therefore:

$$T = -RC \ln \frac{V_{ST} (V_{CC} - V_{ST})}{(V_{CC} + V_{ST}) (2V_{CC} - V_{ST})}$$

(6)

Equation (6) shows that the switching period is no longer influenced by the forward voltage drops across the input protection diodes of inverter 1. For a circuit using a 74HC or 74HCU IC in which the nominal value of  $V_{ST}$  is 0,5V<sub>CC</sub> for all supply voltages, equation (6) can be simplified to:

$$T = 2,2RC \tag{7}$$

For a circuit using a 74HCT IC in which the nominal VST is 1.3 V for V<sub>CC</sub> = 4.5 V, 1.415 V for V<sub>CC</sub> = 5 V and 1.53 V for V<sub>CC</sub> = 5.5 V, equation (6) can be approximated by:

$$\Gamma = 2,4RC \tag{8}$$

Tables 1 and 2 verify the accuracy of equations (7) and (8) by comparing their results with calculations made with equations (1), (2), (4) and (5), and with measured results for a circuit in which  $V_{CC} = 5 V$  and  $K = 2 (R_S = 2R)$ .

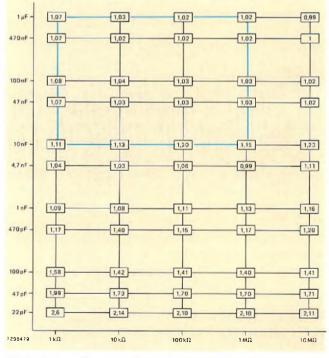

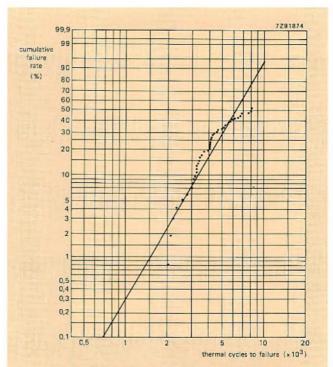

For a circuit using a 74HC IC, Fig.4 indicates the ratio of measured switching periods to those calculated with equations (1), (2), (4) and (5) for various combinations of R and C and with K=2. The component value limits which will maintain the ratio acceptably close to unity are also shown.

#### Influence of supply voltage variations

Table 3 (74HC/HCU) and Table 4 (74HCT) compare the results of switching period and duty factor calculations made with equations (1), (2), (4) and (5) for  $K = 10^{-3}$  (Rs short-circuit), K = 2 (Rs = 2R) and K = 10 (Rs = 10R), with supply voltage as a parameter. The Tables show that the influence of supply voltage variation on the switching period and duty factor of a circuit using a 7HC/HCU or 74HCT IC is almost eliminated when K = 2.

Fig.4 Ratios of measured to calculated switching periods, for a circuit using a 74HC IC, to indicate the validity of equations (1), (2), (4) and (5)

#### ASTABLE MULTIVIBRATORS WITH HCMOS

| TABLE 1Accuracy of formulae for 74HC/HCU ICs withVCC = 5 V, VST = 2,5 V and K = 2 (all times in $\mu$ s) |                            |            |                 |                |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------------|------------|-----------------|----------------|--|--|

| RC                                                                                                       | T calculated from formulae | T = 2,2 RC | measu<br>(74HC) | red T<br>74HCU |  |  |

| 1000                                                                                                     | 2174                       | 2200       | 2177            | 2147           |  |  |

| 100                                                                                                      | 217                        | 220        | 218             | 214            |  |  |

| 10                                                                                                       | 21,7                       | 22         | 22,6            | 21,7           |  |  |

| 1                                                                                                        | 2,17                       | 2,2        | 2,4             | 2,4            |  |  |

| 0,1                                                                                                      | 0,217                      | 0,22       | 0,3             | 0,3            |  |  |

| Accuracy of formulae for 74HCT ICs with                                |

|------------------------------------------------------------------------|

|                                                                        |

| $V_{CC} = 5 V$ , $V_{ST} = 1,415 V$ and $K = 2$ (all times in $\mu$ s) |

| RC   | T calculated from formulae | T = 2,4 RC | measured T |

|------|----------------------------|------------|------------|

| 1000 | 2348                       | 2400       | 2362       |

| 100  | 235                        | 240        | 236        |

| 10   | 23,5                       | 24         | 24,4       |

| 1    | 2,35                       | 2,4        | 2,6        |

| 0,1  | 0,235                      | 0,24       | 0,3        |

|      |                            |            |            |

|                             | (131 0  | $0,5 V_{\rm CC}, RC =$ | 100 µ3)  |         |         |

|-----------------------------|---------|------------------------|----------|---------|---------|

|                             |         | $K = 10^{-3}$          |          |         |         |

| V <sub>CC</sub>             | 3 V     | 4,5 V                  | 5 V      | 5,5 V   | 6 V     |

| total switching period (µs) | 181,645 | 168,685                | 165,986  | 163,749 | 161,866 |

| deviation from value at 5 V | +9%     | +1,6%                  | 0        | -1,3%   | -2,5%   |

| switching duty factor       | 0,5     | 0,5                    | 0,5      | 0,5     | 0,5     |

|                             | 1       | K = 2                  |          |         |         |

| V <sub>CC</sub>             | 3 V     | 4,5 V                  | 5 V      | 5,5 V   | 6 V     |

| total switching period (µs) | 218,027 | 216,822                | 216,537  | 216,293 | 216,081 |

| deviation from value at 5 V | +0,7%   | +0,1%                  | 0        | -0,1%   | -0,2%   |

| switching duty factor       | 0,5     | 0,5                    | 0,5      | 0,5     | 0,5     |

|                             | CELON   | K = 10                 | 1. 1. 1. |         |         |

| total switching period (µs) | 219,367 | 219,107                | 219,045  | 218,991 | 218,945 |

| deviation from value at 5 V | +0,1%   | +0,03%                 | 0        | 0,02%   | -0,05%  |

| switching duty factor       | 0,5     | 0,5                    | 0,5      | 0,5     | 0,5     |

#### Influence of switching threshold voltage spread

Table 5 (74HC), Table 6 (74HCU) and Table 7 (74HCT) compare the results of switching period and duty factor calculations made with equations (1), (2), (4) and (5) for  $K = 10^{-3}$  (RS short-circuit), K = 2 (RS = 2R) and K = 10 (RS = 10R), with switching threshold voltage as a parameter. For a circuit using a 74HC IC, Table 5 shows that the influence of the switching threshold voltage spread on the

switching period is reduced by 33% when K = 2, and the duty factor spread is reduced by 43%. For a circuit using a 74HCU IC, Table 6 shows a 33% reduction of the switching period deviation and a 40% reduction of duty factor spread with K = 2. For a circuit using a 74HCT IC, Table 7 shows a 29% reduction of switching period deviation and a 25% reduction of duty factor spread when K = 2.

#### ASTABLE MULTIVIBRATORS WITH HCMOS

| voltage with K as a j                                  | $= 100 \mu s$ ) | or 74HCT | ICs          |

|--------------------------------------------------------|-----------------|----------|--------------|

|                                                        | $K = 10^{-3}$   |          | Called State |

| V <sub>CC</sub>                                        | 4,5 V           | 5 V      | 5,5 V        |

| V <sub>ST</sub>                                        | 1,3 V           | 1,415 V  | 1,53 V       |

| total switching period (µs)<br>deviation from value at | 188,273         | 186,810  | 185,623      |

| $V_{\rm CC} = 5 \text{ V}$                             | +0,8%           | 0        | -0,6%        |

| switching duty factor                                  | 0,74            | 0,75     | 0,76         |

| A CONTRACTOR OF STREET                                 | K = 2           |          | Nilley       |

| V <sub>CC</sub>                                        | 4.5 V           | 5 V      | 5,5 V        |

| V <sub>ST</sub>                                        | 1,3 V           | 1,415 V  | 1,53 V       |

| total switching period (µs)<br>deviation from value at | 234,022         | 234,855  | 235,562      |

| $V_{CC} = 5 V$                                         | -0,3%           | 0        | +0,3%        |

| switching duty factor                                  | 0,64            | 0,64     | 0,65         |

| 1997日4月1日                                              |                 | Line ber |              |

|                                                        | K = 10          |          | and the      |

| V <sub>CC</sub>                                        | 4,5 V           | 5 V      | 5,5 V        |

| VST                                                    | 1,3 V           | 1,415 V  | 1,53 V       |

| total switching period (µs)<br>deviation from value at | 236,635         | 237,692  | 238,588      |

| $V_{CC} = 5 V$                                         | -0,4%           | 0        | +0,4%        |

| switching duty factor                                  | 0,63            | 0,64     | 0,64         |

#### Influence of temperature on switching period

Temperature variations have little influence on the switching period, and hence the operating frequency of astable multivibrators using 74HCMOS ICs. This is because the switching threshold voltage varies by only  $\pm 60 \text{ mV}$  from its nominal value at 25 °C over the temperature range -40 °C to  $\pm 125$ °C. This is far less than the  $\pm 200 \text{ mV}$  variation for LSTTL JCs. The effect of the variation in switching threshold voltage is a spread of the total switching period. For a circuit using a 74HC/HCU IC with a 5 V supply and K=2, the switching period increases by 0,02% at the two temperature extremes. For a circuit using a 74HCT IC, the switching period varies by  $\pm 1\%$ .

TABLE 5

Switching period and duty factor as functions of switching

| Switching Pointer and and Switching Statements       |

|------------------------------------------------------|

| thread old voltage with V as a momentar for 74UC ICa |

| threshold voltage with K as a parameter for 74HC ICs |

|                                                      |

| $(V_{CC} = 5 V, RC = 100 \mu s)$                     |

|                                                      |

|                                   | $K = 10^{-3}$ |              | The start   |

|-----------------------------------|---------------|--------------|-------------|

| V <sub>ST</sub>                   | 1,5 V         | 2,5 V        | 3,5 V       |

| total switching period (µs)       | 183,384       | 165,986      | 183,384     |

| deviation from value at           | +10,5%        | 0            | +10,5%      |

| VST nom.<br>switching duty factor | 0,73          | 0,5          | 0,27        |

|                                   |               | - 10         |             |

| The second second                 | K = 2         | the state of | and the     |

| V <sub>ST</sub>                   | 1,5 V         | 2,5 V        | 3,5 V       |

| total switching period (µs)       | 231,812       | 216,537      | 231,812     |

| deviation from value at           |               |              |             |

| VST nom.<br>switching duty factor | +7%<br>0,63   | 0<br>0,5     | +7%<br>0,37 |

|                                   |               |              | 1           |

| - Street gate in the              | K = 10        |              | a de la com |

| V <sub>ST</sub>                   | 1,5 V         | 2,5 V        | 3,5 V       |

| total switching period (µs)       | 234,596       | 219,045      | 234,596     |

| deviation from value at           | . 7.01        | 0            |             |

| VST nom.<br>switching duty factor | +7%<br>0,62   | 0<br>0,5     | +7%         |

| structure duty factor             | 0,02          | 0,5          | 0,37        |

#### Dynamic power dissipation

The average dynamic power dissipation of an entire IC package of inverters (or inverting gates), only two of which are used for an astable multivibrator is the sum of the following five terms. The first two terms apply to the inverters in the package which don't form part of the multivibrator. The sum of the last three terms is the dynamic power dissipation of the two inverters of the multivibrator.

$CPDVCC^2 f_i$  in which CPD is the load imposed by internal capacitance and switching transient currents, and  $f_i$  is the frequency at the input.

TABLE 6Switching period and duty factor as functions of switchingthreshold voltage with K as a parameter for 74HCU ICs(VCC = 5 V. RC = 100 µs)

| (VCC = 5                    | $\mathbf{V}, \mathbf{RC} = 100$ | <b>σμ</b> ε) |         |

|-----------------------------|---------------------------------|--------------|---------|

|                             | $K = 10^{-3}$                   |              |         |

| V <sub>ST</sub>             | 1 V                             | 2,5 V        | 4 V     |

| total switching period (µs) | 210,497                         | 165,986      | 210,497 |

| deviation from value at     |                                 |              |         |

| V <sub>ST</sub> nom.        | +27%                            | 0            | +27%    |

| switching duty factor       | 0.83                            | 0,5          | 0,17    |

|                             |                                 |              |         |

|                             | K = 2                           | - 16         |         |

| V <sub>ST</sub>             | 1 V                             | 2.5 V        | 4 V     |

| total switching period (µs) | 256,202                         | 216,537      | 256,202 |

| deviation from value at     |                                 |              |         |

| V <sub>ST</sub> nom.        | +18%                            | 0            | +18%    |

| switching duty factor       | 0.7                             | 0,5          | 0,3     |

|                             |                                 |              |         |

| and a second dependent      | K = 10                          | The second   |         |

| V <sub>ST</sub>             | 1 V                             | 2,5 V        | 4 V     |

| total switching period (us) | 259,377                         | 219,045      | 259,377 |

| deviation from value at     |                                 |              |         |

| VST nom.                    | +18%                            | 0            | +18%    |

| switching duty factor       | 0,7                             | 0,5          | 0,3     |

- $\Sigma(CLV_{CC}^2 f_0)$  in which CL is the load capacitance at the output, and  $f_0$  is the frequency at the output.

- $(CPDVCC^2)/T$  in which CPD is defined for the first term, and T is the total switching period for the multivibrator.

- $(2CV_{CC}^2)/T$  in which C is the timing capacitance of the multivibrator, and T is its total switching period.

- XV<sub>CC</sub> in which X is the average through-current from Table 8 and 9. This through current depends on the size of the input transistors of the particular IC and varies from one type of IC to another.

It is obvious from the fourth term that the dynamic power dissipation can be reduced by using a lower value for timing capacitor C, and therefore, higher values for R and  $R_S$ .

| TABLE 7 |  |

|---------|--|

|---------|--|

Switching period and duty factor as functions of switching threshold voltage with K as a parameter for 74HCT ICs  $(V_{CC} = 5 V, RC = 100 \mu s)$

| $K = 10^{-3}$                                          |         |         |         |  |

|--------------------------------------------------------|---------|---------|---------|--|

| V <sub>ST</sub>                                        | 0,93 V  | 1,415 V | 1,9 V   |  |

| total switching period (µs)                            | 215,996 | 186,810 | 171,907 |  |

| deviation from value at<br>VST nom.                    | +16%    | 0       | -8%     |  |

| switching duty factor                                  | 0,84    | 0,75    | 0,64    |  |

|                                                        | K = 2   |         |         |  |

| V <sub>ST</sub>                                        | 0,93 V  | 1,415 V | 1,9 V   |  |

| total switching period (µs)<br>deviation from value at | 261,231 | 234,856 | 221,700 |  |

| V <sub>ST</sub> nom.                                   | +11%    | 0       | -5,6%   |  |

| switching duty factor                                  | 0,71    | 0,64    | 0,58    |  |

|                                                        | K = 10         |         |         |

|--------------------------------------------------------|----------------|---------|---------|

| V <sub>ST</sub>                                        | 0, <b>93 V</b> | 1,415 V | 1,9 V   |

| total switching period (µs)<br>deviation from value at | 264,478        | 237,692 | 224,303 |

| V <sub>ST</sub> nom.                                   | +11%           | 0       | -5,6%   |

| switching duty factor                                  | 0,70           | 0,63    | 0,57    |

The last term is the additional average dynamic power dissipation of the first inverter used for the multivibrator. It occurs because the near-triangular waveform at the input to inverter 1 (point D in Fig.2) slowly approaches  $V_{ST}$  and causes the through-current indicated in Tables 8 and 9. Because of the shape of the waveform, inverter 1 is always operating in its linear region so that this term is independent of the operating frequency.

#### Component value and supply voltage limits

The astable multivibrator shown in Fig.2 will operate correctly as long as C is a bipolar capacitor with a value greater than 100 pF, and the value of R is between  $470 \Omega$  and 1 M $\Omega$ . The lower limit for the value of R ensure that R is much higher than the output impedance of the inverters (typically  $40 \Omega$  with a 4,5 V supply) so that output impedance spreads don't influence the switching period. However,

due to the influence of parasitic capacitances  $C_{11}$  and  $C_{t2}$ , equations (7) and (8) will only remain valid when C is 10 nF or greater, and R is between 1 k $\Omega$  and 1 M $\Omega$ .

The previously mentioned spurious oscillations or glitches which can occur if the value of RS is too large will have a frequency of  $1/(2t_p)$  where  $t_p$  is the propagation delay of inverter 1. The impedance at the input to inverter 1 is then very high and sensitive to crosstalk. The spurious oscillations can be suppressed by using careful board layout to decrease parasitic capacitance Ct1, decreasing RS, or increasing C<sub>12</sub> by connecting a low-value capacitor between point A and D. However, the best solution is to use the unbuffered Hex Inverter 74HCU04 which is specially made for linear applications and will make the oscillator less sensitive to spurious oscillations because it has lower gain than the HC04 or HCT04. Parasitic capacitance CS is formed by board tracks and should be kept as low as possible to avoid any additional delay due to time-constant RSCS.

Although 74HC/HCU ICs can operate from a supply voltage as low as 2 V, it is recommended that a supply of at least 3 V be used for an astable multivibrator. This is because the threshold voltages of the input transistors can be as high as 0.9 V which would leave insufficient margin to operate in the linear region with a 2 V supply. The supply voltage range for astable circuits using 74HC/HCU ICs is therefore 3 V to 6 V. For circuits using a 74HCT ICs it is 4,5 V to 5,5 V.

|         | TABLE 8                                         |

|---------|-------------------------------------------------|

| Average | through-current for two inverters in an astable |

|         | multivibrator using 74HC/HCU ICs                |

| 74HC00 | 74HC04             | 74HCU04                                        |

|--------|--------------------|------------------------------------------------|

| t      | hrough-curi        | ent (µA)                                       |

| 150    | 130                | 600                                            |

| 700    | 450                | 2600                                           |

| 1050   | 650                | 3500                                           |

| 1800   | 1050               | 5600                                           |

|        | 150<br>700<br>1050 | through-curr<br>150 130<br>700 450<br>1050 650 |

TABLE 9Average through-current for two inverters in an astablemultivibrator using 74HCT ICs

|                 | 74HCT0  | 0 74HCT04    |

|-----------------|---------|--------------|

| V <sub>CC</sub> | through | current (µA) |

| 4,5 V           | 700     | 450          |

| 5 V             | 1050    | 650          |

| 5,5V            | 1350    | 800          |

#### ACKNOWLEDGEMENT

The author wishes to acknowledge the assistance of J. Exalto of the Central Applications Laboratory, Eindhoven who made measurements of the performance of astable circuits to verify the information contained in this article.

## **Crystal oscillators using HCMOS ICs**

#### J. EXALTO

Crystal-controlled oscillators are widely used in clock pulse generators because of their excellent frequency stability and their wide operating frequency range. If they use an HCMOS IC as the active element, they have the additional advantages of low power dissipation and stable operation over a wide range of supply voltages and temperature. This article describes the design of several types of crystalcontrolled oscillators based on the unbuffered HCMOS Hex Inverter 74HCU04.

The terms and definitions for crystal-controlled oscillators as specified by the IEC in their publication IEC 122-11 are listed in the Table.

#### **CRYSTAL CHARACTERISTICS**

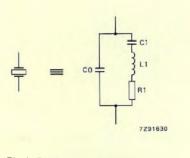

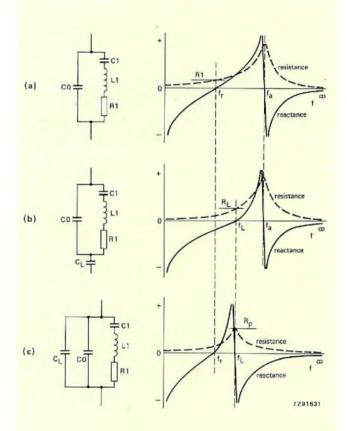

Figure 1 is the equivalent circuit of a quartz crystal. The reactive and resistive components of the impedance of the crystal alone, and of the crystal with a series and a parallel capacitive load are shown in Fig.2.

Figure 2 shows that, with a specified value of load capacitance ( $C_L$ ), the load resonance frequency ( $f_L$ ) is the

Fig.1 Equivalent circuit of a crystal

same for a circuit with either a parallel or series capacitive load. It is therefore very important to use this value of load capacitance in the design of a crystal oscillator. However,

Fig.2 Reactance and resistance characteristics of a crystal, (a) resonance, (b) anti-resonance, (c) load resonance

#### CRYSTAL OSCILLATORS WITH HCMOS

the preferred load capacitance should be partially adjustable so that compensation can be made for spurious capacitances caused by the pcb and the pins of the IC. Preferred values of load capacitance specified for fundamental frequency operation of various crystals at parallel resonance are 20 pF, 30 pF, 50 pF and 100 pF. Some countries still use 32 pF, but, since this is not a preferred value, its use is not recommended. The preferred values of load capacitance for overtone operation at series resonance are 8 pF, 12 pF, 15 pF, 20 pF and 30 pF.

The power dissipated in a crystal is called the "level of drive". Since the crystal characteristics become highly dependent on the level of drive if it is outside the range 1 pW to 1 mW, the crystal characteristics are usually specified at 0,5 mW. With a very low level of drive, as can occur during oscillator start-up, the characteristics can vary slightly, in particular, the resonance resistance  $R_{\rm I}$  will increase about threefold. To overcome this, the loop gain of the oscillator circuit should be sufficient to prevent start-up problems, but not enough to overdrive the crystal.

#### HCMOS HEX INVERTER 74HCU04 IN CRYSTAL-CONTROLLED OSCILLATORS

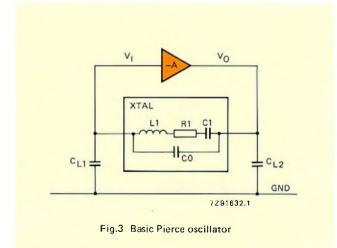

The Pierce oscillator in which the crystal has a parallel load capacitance is the type most widely used in digital systems. As shown in Fig.3, it is basically a Colpitts oscillator in which the inductor has been replaced by a crystal. The advantages of this configuration are:

- good suppression of the third overtone (9x)

- lower power dissipation (level of drive) in the crystal than in a series-resonant oscillator due to the high ohmic loading

- the amplifier must provide  $180^{\circ}$  phase shift, so a simple inverter can be used.

The high input impedance of the 74HCU04 Hex Inverter makes it ideal for use in a Pierce oscillator. However, good power supply decoupling is necessary (see "Power supply decoupling" in the user guide of Data Handbook IC06N).

Although the 74HCU04 can operate from a supply voltage as low as 2 V, it is recommended that a supply of at least 3 V be used for a crystal-controlled oscillator. This is because the threshold voltages of the input transistors can be as high as 0.9 V which would leave insufficient margin to operate in the linear region with a 2 V supply. The supply voltage range for crystal oscillators using the 74HCU04 is therefore 3 V to 6 V.

Unfortunately, the output impedance of the 74HCU04 is too low to drive the crystal directly. The simple expedient of adding a resistor in series with the output causes additional phase shift resulting in an increase of loop gain and a decrease of the level of drive in proportion to the square of the frequency. This arrangement is therefore only suitable for lower frequencies (up to about 4 MHz). For higher frequency oscillators, the output impedance of the inverter must be increased with a series capacitor instead of a series resistor.

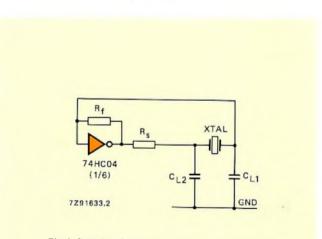

#### A 4 MHz crystal oscillator using the 74HCU04

Figure 4 illustrates a practical 4 MHz Pierce oscillator in which the crystal is operating at its fundamental frequency and is tuned by a parallel load capacitance consisting of  $C_{L1}$  and  $C_{L2}$  in series, together with stray capacitances.  $C_{L1}$  should be adjustable so that the capacitive load can be accurately set to the preferred load capacitance specified for the particular crystal being used. The loop gain of the circuit is:

$$\frac{V_{O}}{V_{I}} = \frac{C_{L2}}{C_{L1}}$$

Fig.4 Practical Pierce oscillator using unbuffered inverter 74HCU04

For an economy range 4 MHz crystal ( $4322 \ 143/144 \ 04091$ ), the specified C<sub>L</sub> (C<sub>L1</sub> and C<sub>L2</sub> in series) is 30 pF and the specified resonance resistance (**R**<sub>r</sub>) of the crystal is 75  $\Omega$ . At 4 MHz, a loop gain (C<sub>L2</sub>/C<sub>L1</sub>) of about unity is adequate, and so if there is no stray capacitance.

$$C_{L1} = C_{L2} = 60 \, \text{pF}.$$

However, since there will always be some stray capacitance 56 pF capacitors should be used for  $C_{L1}$  and  $C_{L2}$ . Since  $C_{L1}$  and  $C_{L2}$  are equal, the total impedance as seen from the output of the inverter can be simplified to:

$$Z_{L} = \frac{X_{CL}^{2}}{R_{f}}$$

where  $X_{CL} = -j/\omega C_{L2}$  and  $R_r$  is the specified resonance resistance of the crystal (75  $\Omega$ ).

For optimal operation of a Pierce oscillator, the output impedance of the inverter should be the same as the total load impedance. The output impedance of the inverter should therefore be  $5,9 \,\mathrm{k}\Omega$ . Since the output impedance of the 74HCU04 with a 5V supply is only about  $40 \,\Omega$ , the preferred value for  $R_s$  in series with the output of the inverter is  $5,6 \,\mathrm{k}\Omega$ . However, this value would cause too much phase shift, so a compromise value of  $2,2 \,\mathrm{k}\Omega$  is used. Any value between  $1 \,\mathrm{M}\Omega$  and  $10 \,\mathrm{M}\Omega$  is suitable for  $R_f$ which provides d.c. bias for the output of the inverter.

### Higher frequency crystal oscillators using the 74HCU074

In addition to the phase shift introduced by  $R_s$  in series with the inverter output, the inverter's propagation delay  $(t_p)$  also causes phase shift which can be expressed as:

Phase shift =

$$f_{osc} \times t_p \times 360^\circ$$

.

With a maximum propagation delay of 14 ns, a 4,5 V supply for the 74HCU04, and an oscillator frequency of 6 MHz, a further 30° phase shift would occur. This means that the Pierce oscillator circuit shown in Fig.4 is unsuitable for operation at high frequencies. Modifying the circuit by replacing  $R_s$  with a capacitor ( $C_s$ ) of about the same value as  $C_L$  (half the value of  $C_{L1}$  or  $C_{L2}$ ), allows the circuit to be used at a higher frequency.

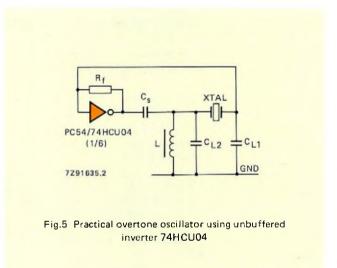

#### An overtone crystal oscillator using the 74HCU04

Most crystal manufacturers supply crystals for operation at fundamental frequencies, third overtone crystals for operation in the frequency range 10 MHz to 75 MHz, and fifth overtone crystals for operation in the frequency range 50 MHz to 125 MHz. Due to the high maximum operating frequency of HCMOS logic systems, it may be necessary to use a third overtone oscillator with parallel load capacitance as shown in Fig.5. A critical requirement for this type of oscillator is suppression of the fundamental frequency of the crystal. Two methods of suppression are used in the circuit of Fig.5.

- capacitor  $C_s$ , which should have a value close to that of  $C_L$ , presents a higher impedance to the fundamental frequency of the crystal than it does to the third overtone

- C<sub>s</sub>/L resonates at slightly below the third overtone and traps the fundamental frequency.

Tuning L for maximum output voltage may affect the oscillator frequency slightly, but adjustment of  $C_{L1}$  will usually compensate for this.

#### Checking a prototype crystal oscillator design

The following simple checks will verify the quality of the design of a crystal-controlled oscillator using a 74HCU04 IC:

- 1. Test the oscillator under worst-case conditions (lowest supply voltage, worst-case crystal and highest operating temperature). A worst-case crystal can be simulated by adding series and parallel resistors.

- 2. Ensure that the circuit doesn't oscillate without the crystal.

- 3. Check the frequency stability of the oscillator over a supply voltage range greater than that which is likely to occur during normal operation.

#### TERMS AND DEFINITIONS FOR CRYSTAL OSCILLATORS (IN ACCORDANCE WITH IEC 122-1)

| Adjustment<br>tolerance                       | The permissible deviation from the nominal frequency at the reference temperature under specified conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ageing (long-<br>term parameter<br>variation) | The relation which exists between any param-<br>eter (e.g. resonance frequency) and time.<br>Note: such parameter variation is due to long-<br>term changes in the crystal unit and is usually<br>expressed in fractional parts per period of time.                                                                                                                                                                                                                                                                                                             |

| Ageing tolerance                              | The permissible deviation due to time under specified conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Anti-resonance<br>frequency f <sub>s</sub>    | The higher of the two frequencies of a crystal<br>unit alone, under specified conditions, at which<br>the electrical impedance of the crystal unit is<br>resistive.                                                                                                                                                                                                                                                                                                                                                                                             |

| Level of drive                                | A measure of the conditions imposed upon the crystal unit expressed in terms of power dissipated.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                               | Note: in special cases, the level of drive may be specified in terms of crystal current or voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Load capacitance<br>CL                        | The effective external capacitance associated with the crystal unit which ddetermine the load resonance frequency $f_{L}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Load resonance<br>frequency fL                | One of the two frequencies of a crystal unit in association with a series or with a parallel load capacitance, under specified conditions, at which the electrical impedance of the combination is resistive. This frequency is the lower of the two frequencies when the load capacitance is in series and the higher when it is in parallel (see Fig.2). For a given value of load capacitance (CL), these frequencies are identical for all practical purposes and are given by:<br>$\frac{1}{t_L} = 2\pi  \sqrt{\frac{L_1C_1(C_0 + C_L)}{C_1 + C_0 + C_L}}$ |

resistance RL

Load resonance The resistance of the crystal unit in series with a stated external capacitance at the load resonance frequency fL. Note: the value of RL is related to the value of

$R_r$  by the following expression:

## $R_{L} = R_{r} \left(1 + \frac{C_{0}}{C_{L}}\right)^{2}$

| Motional<br>capacitance C <sub>1</sub>          | The capacitance of the motional (series) arm of the equivalent circuit.                                                                                                                                                                                         |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Motional<br>inductance L <sub>1</sub>           | The inductance of the motional (series) arm of the equivalent circuit.                                                                                                                                                                                          |

| Nominal<br>frequency f <sub>n</sub>             | The frequency assigned by the specification of the crystal unit.                                                                                                                                                                                                |

| Operable<br>temperature<br>range                | The range of temperatures as measured on the<br>enclosure over which the crystal unit must<br>function though not necessarily within the<br>specified tolerances.                                                                                               |

| Operating<br>temperature                        | The range of temperatures as measured on the enclosure over which the crystal unit must function within the specified tolerances.                                                                                                                               |

| Reference<br>temperature                        | The temperature at which certain crystal measurements are made. For controlled temperature units, the reference temperature is the mid-point of the controlled temperature range. For non-controlled units the reference temperature is normally $25 \pm 2$ °C. |

| Resonance<br>frequency f <sub>r</sub>           | The lower of the two frequencies of the crystal<br>unit alone, under specified conditions, at which<br>the electrical impedance of the crystal unit is<br>resistive.                                                                                            |

| Resonance<br>resistance R <sub>r</sub>          | The resonance of the crystal unit alone at the resonance frequency ${\rm f}_{\rm r}.$                                                                                                                                                                           |

| Tolerance due to<br>level of drive<br>variation | The permissible deviation due to the variation of level of drive.                                                                                                                                                                                               |

| Tolerance over<br>temperature<br>range          | The permissible deviation over the temperature range with respect to the frequency at the specified reference temperature.                                                                                                                                      |

| Unwanted<br>response                            | A state of resonance of a crystal vibrator other than that associated with the working frequency.                                                                                                                                                               |

| Working<br>frequency f <sub>w</sub>             | The operational frequency of the crystal unit together with its associated circuits.                                                                                                                                                                            |

#### REFERENCE

Data Handbook C9; "Piezoelectric quartz devices"; ordering code 9398 124 90011.

## Automatic placement machine for hybridcircuit assembly

Answering the needs of large-scale manufacturers of hybrid circuits, MCM IV is the latest addition to the versatile MCM family of automatic placement machines for SMDs (surface-mount devices). Working an 80 hour week, the first of the new machines to be delivered is currently assembling hybrids at a rate of 1,2 million a year.

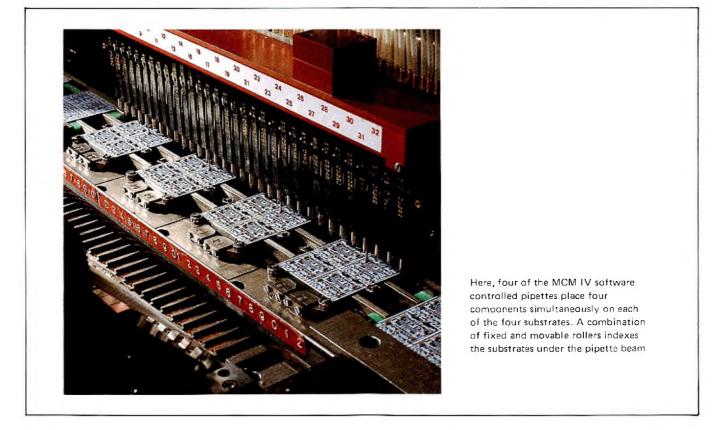

Developed in response to a customer's requirement to double hybrid-circuit production without taking up additional factory floor space, the MCM IV is based largely on concepts pioneered and proved in the MCM II, a machine which combines simultaneous and sequential placement under software control to attain high throughput. Unlike the MCM II, however, which is primarily for printed-circuitboard assembly, the MCM IV is designed specifically to work with standard ceramic substrates. Standard versions of the machine can have up to eight placement heads, each of which can place up to 1024 components in one machine cycle.

#### VERSATILE PLACEMENT HEAD

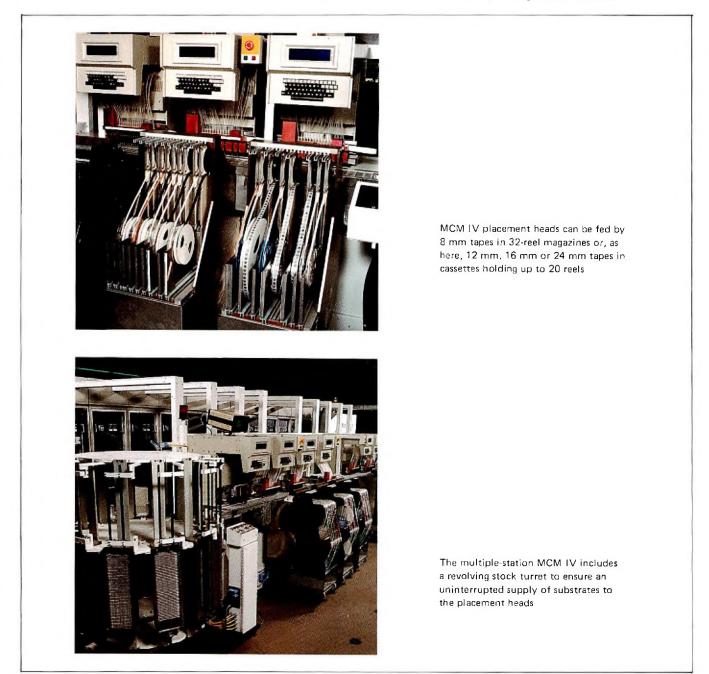

Central to each placement head is a movable beam carrying 32 pipettes that can pick up 32 components simultaneously and place them on substrates either simultaneously or sequentially. depending on the substrate layout and corresponding control software. The pipettes extract tapepackaged components fed from supply reels (also controlled by software), and transport them to their programmed positions on the substrates, rotate them to required alignments, and press them down onto solder-paste footprints screened in advance onto the substrates.

Four standard substrates at a time fit under the pipette beam, each served by a group of eight pipettes drawing from their own supply recls in a 32-reel, quick-change magazine. The beam moves under servo control so that any one of the pipettes in a group can place its component anywhere on the substrate it serves, with an accuracy of 0.2 mm in both x and y directions. The machine imposes no artificial grid restrictions.

The pipettes are spaced at a pitch of 10 mm and the walking-beam substrate transport mechanism can be programmed to advance the substrates 80, 160 or 320 mm at a time. For substrates having only one circuit each, the transport mechanism is programmed to advance 80 mm at a time so that successive groups of pipettes, working sequentially, can place up to 32 different component types. On substrates supporting two identical circuits, pipettes working simultaneously in pairs can place up to 16 component types. And on four-circuit substrates, pipettes working together in fours can place up to eight component types. The transport mechanism would then be programmed to advance 320 mm at a time so that all four substrates would move as a unit into and out of the placement-head working area.

In one machine cycle the pipettes can be charged up to 32 times. After that, all four of the substrates operated upon in that cycle must give way to four new ones. If two placement heads are fitted, the transport mechanism will then automatically position the first four substrates under the second head.

To avoid unnecessary constraints on substrate layout, any component can be rotated from its pick-up alignment by 90°, 180° or 270°, with an accuracy of 2°. Since selective rotation of individual pipettes would be unduly complicated mechanically, all are rotated together by the amount required for a given component, but only those actually placing that component are lowered to the substrate. After that, all 32 are again rotated together to the next alignment required.

#### **MULTIFUNCTION PIPETTES**

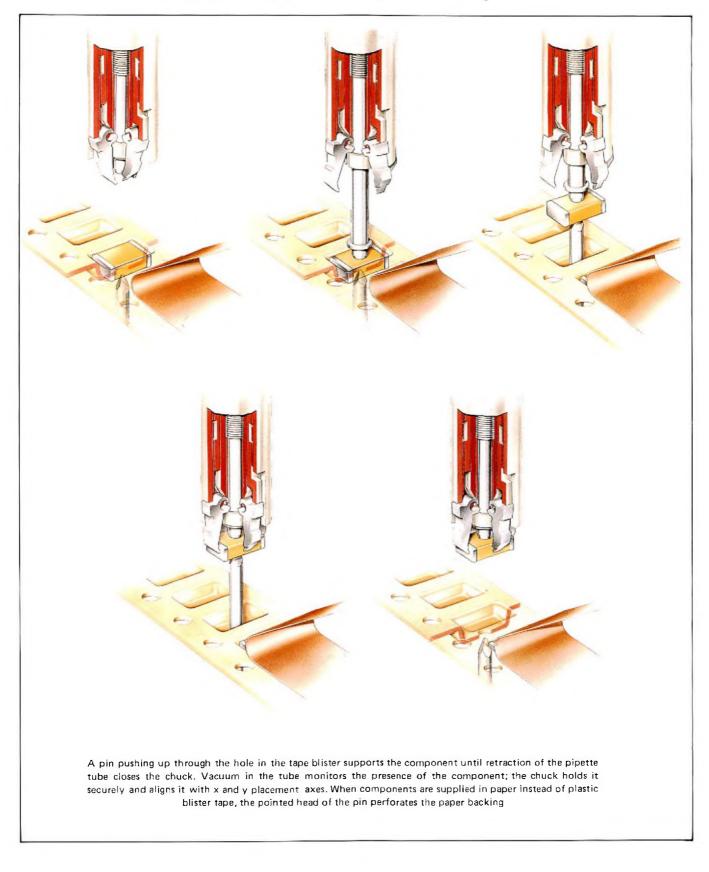

The basic design of the pick-and-place pipettes is an important feature that MCM IV shares with other members of the MCM family. It combines a central tube with an outer, mechanical chuck. The function of the tube is threefold: to monitor the presence of the component throughout the pick-and-place action, to hold it by vacuum during the last phase of that action, and to press it firmly onto its solderpaste footprint on the substrate. The chuck has equally important functions: it aligns the component with the x and y placement axes, regardless of tolerances in the original angle of presentation; and it exercises a positive, mechanical grip during transport of the component from the pick-up to the placement position.

A pin rising from beneath the tape lifts the component out of its blister and presents it to the central tube of the pipette, which at this stage is under vacuum. The pin continuous to support the component until the jaws of the chuck, descending along the outside of the tube, close on it. The pin then retracts and the pipette carries the component to its placement position on the substrate.

Microphones mounted in turbulence chambers in each of the 32 vacuum lines monitor the presence of the components in the pipettes. If the initial presentation of any component is unsuccessful, the monitoring system triggers the corresponding tape feed to advance a new component into position so that the pipette can try again to pick it up. If, after two such "refires", pick-up is still unsuccessful, the machine cycle stops and the control panel alerts the operator and reports the pipette position at which the fault has occurred so that he can take remedial action. Likewise, if a component becomes dislodged before placement, the machine stops and notifies the operator of the fault and its position.

An important respect in which the MCM IV pipettes differ from those of other members of the MCM family is their action during the very last phase of component placement. MCM IV is designed to place components on solderpaste footprints whose limited adhesiveness must be relied upon to hold them securely in place until the solder paste is reflowed. The components must therefore be pressed firmly enough onto the footprints to give them reasonable assurance of sticking, yet gently enough not to risk damaging the comparatively brittle ceramic substrate. MCM IV pipettes meet this requirement by cushioning the final placement with air.

When a pipette reaches the position at which its component is to be placed, its central tube starts to descend and the chuck opens so that the component is held solely by vacuum. Then, as soon as the component touches the substrate, a valve in the placement head momentarily switches the connection of the tube from the vacuum to the pressure manifold, pushing the component down onto its footprint with a pulse of compressed air.

Reconnected to the vacuum manifold, the tube then retracts. If the microphone does not detect noise in the turbulence chamber, the control system interprets that as an indication that the component has not in fact been successfully placed and is still attached to the tube instead of the substrate — as may happen, for example, if solder paste has not been properly screened onto the footprint. In this event too, the control system interrupts the machine cycle and alerts the operator.

#### AUTOMATIC PLACEMENT MACHINE

#### SUPPORT MODULES

In addition to the placement and transport modules, tapereel magazines, and control electronics, MCM IV includes loading and unloading modules also under software control. The loading module, with a capacity of 600 substrates stored in quick-change cassettes, feeds substrates to the transport module in step with the action of the walking beam. In the event of feeding errors, sensors incorporated in the transport module detect vacant positions and signal the control electronics to adjust the placement program accordingly. At the far end of the transport module, the unloading module restacks the assembled substrates in cassettes in which they can then progress to reflow soldering. A reflow soldering station also may be initiated in the MCM IV-line.

Depending on the layout of the substrates, one MCM IV, requiring the attention of only one operator, can place from 25 000 to 200 000 components an hour.

#### ACKNOWLEDGEMENT

This article is based on one that originally appeared in the May issue of Electronic Packaging & Production, copyright 1985, Cahners Publishing Co.; permission to publish is gratefully acknowledged.

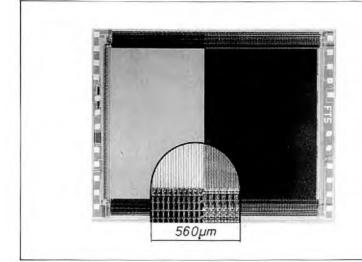

# MOS-XY, interline and frame-transfer sensors compared

#### M. COLLET

It wasn't so long ago that the solid-state imager was regarded as little more than a curiosity, something to be played with in the research labs of the world's big electronics companies, but no real threat to the tv camera tube. In those days the best that could be realized were relatively simple linear arrays that could do little more than display still images on a tv screen, good for a slide show but not much else. Two-dimensional high-resolution displays were just pie in the sky. But like the old adage of acorns and oaks, those early imagers have now grown into something really big. So big, in fact, that camera tubes are now under serious threat, and many types could well be completely supplanted within the next five years.

Already we find two-dimensional solid-state imagers replacing vidicons in CCTV installations and home video systems, and it won't be long before they hit the broadcasting market in the latest ENG tv cameras.

But the real future of the solid-state imager lies not merely as a replacement for the camera tube. It lies in applications for which camera tubes have never even been considered, and in a host of applications generated by its very existence. Character-recognition systems for computers and word processors are a prime example, as are home security systems, which thanks to the relatively low cost of the solid-state imager when in volume production, are likely to increase dramatically over the next few years. Then there are robot-vision systems, remote measuring systems and video slide-scanners, and in the slightly more distant future, home and office videophones and electronic *still-picture* cameras. So let's take a closer look at the solid-state imager, and see if we can predict which of the many systems currently on the market is likely to be the major one of the future.

Solid-state tv cameras are much smaller than their tube-based counterparts. This camera contains Philips' NXA1010 frametransfer sensor and is no more than 60 × 65 × 100 mm (excluding lens)

#### THREE SYSTEMS

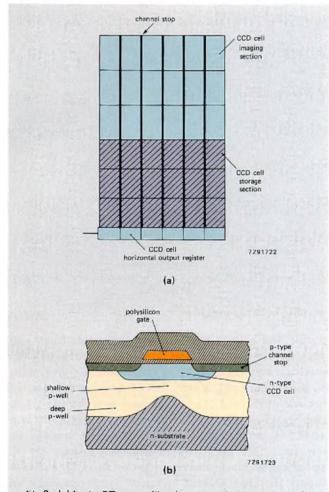

If we neglect some less important examples, we find that there are three major systems jockeying for the lion's share of the market. These are the interline-transfer (IL) sensor, the x/y-addressed MOS sensor (MOS-XY), and the frametransfer (FT) sensor. Let's look at each in turn.

#### SENSORS COMPARED

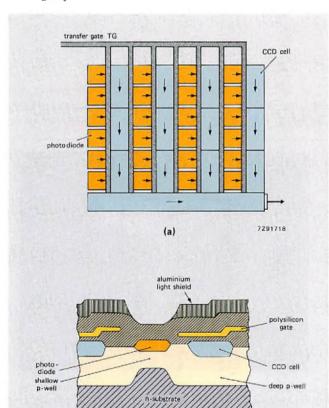

#### Interline-transfer (IL) sensor

The IL sensor (Fig.1), currently promoted mainly by NEC and Sony, was the first charge-coupled area image sensor to become commercially available. Basically it consists of a series of vertical arrays of integration sites, each array connected via a polysilicon transfer gate (TG) to a twophase vertical CCD shift register. The number of transfer cells in each shift register is equal to the number of display lines in each field, and to half the number of integration sites. So the transfer cells are shared between the two fields and, by appropriate biasing of either one or the other set of gates controlling the vertical shift registers, each field can be read out separately to produce an interlaced picture frame.

The IL sensor has the advantage of requiring only half as many vertical transfer cells as there are pixels in the final tv picture, but it does require the same number of integration sites. The total integration time is thus a full-frame period and this can result in a somewhat poor response to fast moving objects.

(b)

7291719

#### X/Y-addressed MOS sensor (MOS-XY)

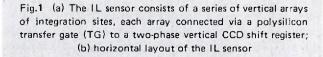

The MOS-XY promoted by Hitachi (Fig.2) consists of an x/y-addressed matrix of photodiodes with a MOSFET at each crossing point. The transistor gates in each row are connected via a polysilicon horizontal address line whose voltage is controlled by a vertical scan register. The transistor drains in each column are connected to aluminium sense lines, in turn connected to the video output via a series of MOSFETS controlled by a horizontal scan register.

Fig.2 (a) The MOS-XY consists of an x/y- addressed matrix of photodiodes with a MOSFET at each crossing point. The transistor gates in each row are connected via a polysilicon horizontal address line whose voltage is controlled by a vertical scan register. The transistor drains in each column are connected to aluminium sense lines, in turn connected to the video output via a series of MOSFETS controlled by a horizontal scan register; (b) horizontal layout of the MOS-XY sensor The vertical scan register selects the tv line to be read out by generating a positive pulse on the horizontal address line corresponding to that line, so raising the gate voltage of the MOS transistors and allowing the photocharge to pass to the aluminium sense lines. The horizontal scan register then sequentially connects each sense line to the video output to form the video signal. The outputs of each line are interlaced by the vertical scan register.

As with the IL sensor the MOS-XY requires as many photosensitive elements as there are pixels in the final tv picture. From a production point of view, however, it does have one advantage, it lends itself readily to manufacture using CMOS processes already established by Hitachi for its DRAMs, and this, of course, can provide significant cost savings.

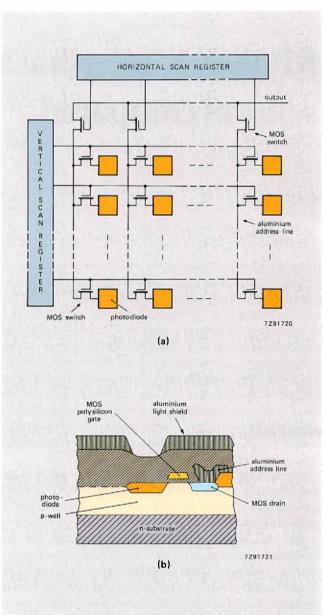

Fig.3 (a) In the FT sensor, illuminated vertical charge-transfer channels are operated with common electrodes to form a two-dimensional imaging area. During vertical blanking, charge generated in the imaging area over a field integration period is rapidly transferred into a shielded storage area located below the imaging area. During the horizontal blanking periods, this charge is shifted down a line at a time into a horizontal shift register where it is clocked out during each line period to form the video signal; (b) horizontal layout of the FT sensor

#### Frame-transfer (FT) sensor

In the FT sensor (promoted by Philips, Fig.3), chargetransfer channels are placed vertically side-by-side and operated with common electrodes to form a two-dimensional imaging area. During vertical blanking, charge generated in the imaging area over a field integration period is rapidly transferred into a shielded storage area located below the imaging area. During the horizontal blanking periods, this charge is shifted down a line at a time into a horizontal shift register where it is clocked out during each line period to form the video signal.

Since all the integrated charge is completely removed in each field, the FT sensor needs only half as many photosensitive cells as there are pixels in a complete frame, and the number of rows need equal only the number of display lines within a single field. The video information for the second interlaced field is obtained by electronically shifting the centre of each integration site by half a cell. In the latest four-phase devices (such as the NXA1010/1020), this is done by integrating the first field under, say, gates 2, 3 and 4, and the second field under gates 4, 1 and 2.

#### HOW DO THEY COMPARE?

When comparing these three systems, all of which are currently in use and enthusiastically promoted by their respective manufacturers, it's important to know on what basis we're talking. Should we, for example, consider devices of equal image area, and compare their sensitivity, resolution, cost. There are, after all, some arguments for this approach since the current most popular tv camera size is 2/3 inch, and it would be reasonable to expect the new cameras based on solid-state imagers to fall into line with this.

On the other hand, it may be argued that with a completely new technology at our disposal, we should optimize it to the full. After all, what's the point of having such potential for miniaturization, with all its accompanying advantages, if we allow ourselves to be constrained by limitations of the past.

Whatever the basis for comparison, a look at the factors governing size, cost and performance should provide some clear indications for the future.

#### Sensor layout and potential for miniaturization

The sensor layouts are shown in Figs 1, 2 and 3. In all cases the number of pixels has been chosen to be compatible with PAL and VCR (video cassette recorders). IL and MOS-XY sensors currently have 400 pixels per line and 600 photodiodes per column, the FT sensor has 600 pixels per line and 300 CCD cells per column in both the imaging and storage sections, which through interlacing yield 600 tv lines. The basic cells in all devices use a vertical anti-blooming

#### SENSORS COMPARED

structure in which boron is diffused into the n-type substrate to produce p wells that allow excess-charge diffusion from the photosensitive areas into the substrate.

Looking at the horizontal layout of each device in turn, we find that for each column of pixels the IL sensor requires a channel stop, a photodiode, a transfer gate and a CCD shift register. The MOS-XY requires a channel stop, a photodiode, a MOS polysilicon gate and drain, and an aluminium address line. The FT sensor, on the other hand, requires only a channel stop and a CCD shift register, and so makes far more efficient use of the area available for imaging. And on the basis of size alone, using the same degree of miniaturization in all devices, it would appear that the FT sensor comes out a clear winner by a factor of at least two.

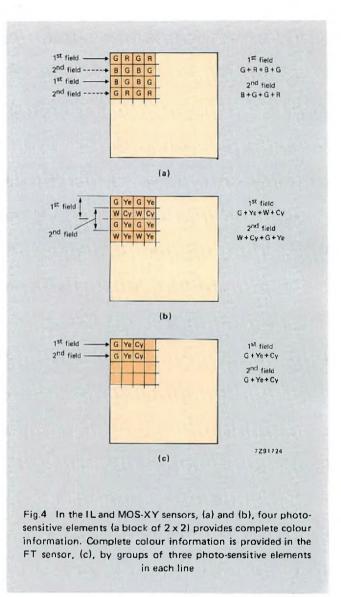

Things aren't quite that simple, however, and to understand why we must look at the way the three sensors generate the composite video signal. As we've seen, the FT sensor has the advantage of a narrow pitch, and the IL and MOS-XY sensors have the advantage of a separate site for each pixel. This has led to the use of mosaic colour filters for IL and MOS-XY sensors, and to vertical stripe colour filters for the FT sensor.

In the IL and MOS-XY sensors, four photo-sensitive elements (a block of  $2 \times 2$ , Figs 4(a) and 4(b)) provides complete colour information. The same is provided in the FT sensor by groups of three photo-sensitive elements in each line (Fig.4(c)). So the FT sensor needs 1,5 times as many photo-sensitive elements per line to produce the same number of colour pixels as the IL and MOS-XY sensors. This means that current devices referred to above (i.e.  $400 \times 600$  elements for IL and MOS-XY sensors,  $600 \times 300$  for the FT sensor) all produce lines of 200 colour pixels, so on this basis alone, all devices have the same horizontal resolution.

However, the narrower pitch of the FT sensor means for say an 8 mm image diagonal, these 200 pixels can be realized in  $4 \mu m$  technology, rather than the  $2 \mu m$  technology needed for current IL and MOS-XY sensors with 11 mm image diagonals. So an FT sensor of equivalent resolution to an IL or MOS-XY sensor is not only easier to manufacture, it also has a much smaller imaging area, and since it makes more efficient use of this area, its sensitivity is significantly higher.

If instead the FT sensor is manufactured in  $2 \mu m$  technology, we can either halve the size of the chip yet still produce an FT sensor of equivalent performance to current IL or MOS-XY sensors, or we can double horizontal resolution.

So even allowing for the fact that the FT sensor requires more columns to produce the same colour video information as the IL and MOS-XY sensors, it comes out a clear winner on the basis of sensitivity-resolution-miniaturization.

What's more, if we're only interested in black/white imaging, the resolution of the IL and MOS-XY sensors will

double, but that of the FT sensor will treble (since each photosensitive element then forms a complete pixel), thus making it even more attractive than it is for colour imaging.

A common criticism of the FT sensor has been that, because of its need of a storage section, it requires greater chip area than IL or MOS-XY sensors for equivalent image areas. As we've seen above, however, this neglects the important fact that for *equivalent performance* the FT sensor can be much smaller. To give an example: a state-ofthe-art IL sensor realized in 1,5 to  $2 \mu m$  technology will have a total chip area of around 39 mm<sup>2</sup>, whilst an equivalent FT sensor (also realized in 1,5 to  $2 \mu m$  technology) will have a total area (including storage section) of only  $22 mm^2$ .

If on the other hand we manufacture the FT sensor in  $3 \mu m$  technology, we'll end up with a sensor of around  $38 \text{ mm}^2$ , roughly the same as the 1,5 to  $2 \mu m$  IL sensor. But we'll also have a sensor with roughly twice the sensitivity and, moreover, one that's much easier to manufacture.

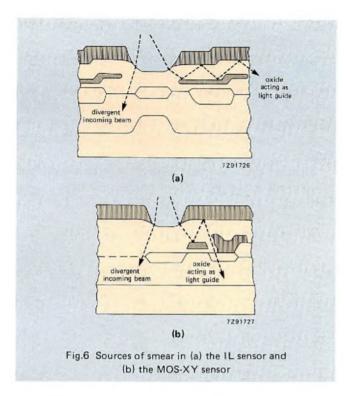

#### Vertical resolution

Modern MOS-XY sensors use two address lines per column, thus allowing the use of neighbouring lines to construct the composite video signal for each tv line. This would only be possible in the IL sensor by including two CCD registers per column – requiring much greater packing density. The IL sensor therefore uses non-neighbouring lines to construct the composite video signal and so has poorer vertical resolution than the MOS-XY sensor. It does, however, have a lower noise level since the charges, being read out via CCD registers, are kept separate throughhout the signal path, in contrast to the MOS-XY, in which some charge mixing can occur within the aluminium address lines.

In these respects the FT sensor combines the advantages of both sensors since it uses neighbouring lines to construct the composite video signal, so its vertical resolution is comparable to the MOS-XY, and it reads out the charge via CCD registers and so its noise level is comparable to the IL sensor.

#### Sensitivity

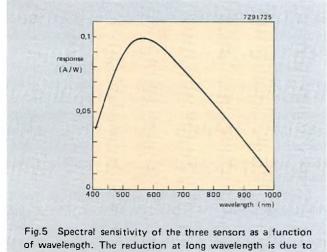

Besides the effects of technology referred to above (i.e.  $2 \mu m$  versus  $4 \mu m$  technology), many other factors influence the sensitivity of the three sensors. For example, all three sensors use silicon for the photo-conversion process. If the correct dopant profiles and annealing treatments are used, silicon has a quantum efficiency of 1 for wavelengths between 300 and 1000 nm.

With a vertical anti-blooming structure, only electrons generated in the upper half of the p-well are collected, and for all sensors this causes quantum efficiency to decrease beyond 550 nm (Fig.5).

Furthermore, the refractive index step between silicon dioxide (n = 1,45) and silicon (n = 3) causes reflection losses, which can be limited by the proper choice of oxide thickness but only for a restricted wavelength range (450 to 500 nm).

the p-well anti-blooming structure

Any parts of the imaging area covered with polysilicon suffer further losses due to reflection (which again can be optimized to some extent by proper choice of layer thickness) and absorption of short wavelengths (40% absorption at 450 nm, 80% at 400 nm). And of course, all regions covered by aluminium light shields will have zero sensitivity.

Combining all the above factors for equivalent sensors (i.e. realized in the same technology), we arrive at the quantum efficiencies given in Table 1. From this table you can deduce that for all visible wavelengths the IL sensor is less efficient than the MOS-XY and FT sensors.

| Quantum efficiencies | fable 1<br>of IL, M | OS-XY and | FT sensors |

|----------------------|---------------------|-----------|------------|

| wavelength (nm)      | IL                  | MOS-XY    | FT         |

| 450                  | 0,2                 | 0,3       | 0,3        |

| 550                  | 0,3                 | 0,5       | 0,5        |

| 650                  | 0,2                 | 0,3       | 0,3        |

#### Noise

The noise produced by a sensor is just as important as quantum efficiency in determining its sensitivity. Here *noise* encompasses all factors contributing to spurious signals.

#### Thermal noise

Modern technology limits dark current to about  $10 \text{ nA/cm}^2$  at 60 °C. This is equivalent to  $7 \times 10^3$  electrons per charge packet in IL and MOS-XY sensors (2/3-inch camera format, 400 pixels per line), leading to a shot noise in the dark current of 80 electrons, and to  $2 \times 10^3$  electrons per charge packet in the FT sensor (½-inch camera format, 600 pixels per line) leading to a shot noise of 40 electrons.

A second contribution to thermal noise is the noise introduced on resetting the CCD output node, which varies inversely with the square root of the output capacitance. For the IL and FT sensors, which currently have output capacitances of around 50 fF, this equals 90 electrons, and this number is likely to fall with improving design rules. For the MOS-XY sensor, the capacitance of the sense lines (around 1 pF) will always be the limiting factor and leads to a reset noise of around 400 electrons.

Since the output capacitance of both the IL and FT sensors is lower than that of the MOS-XY sensor, they are more susceptible to interference caused by spurious signals (frequency interference due to clock feed-through), but with proper camera design this will present no problem.

Finally, since most imagers use double source followers as output amplifiers, the thermal noise contributed by the amplifier should be the same for all. For an optimized amplifier design this lies at around 100 electrons.

#### SENSORS COMPARED

#### Fixed-pattern noise

In silicon, the dark current is generated through transitions between localized energy levels between valence and conduction bands. These are known as recombination-generation centres and they're produced by impurities or crystal defects in the bulk of the material, or by what are known as interface states (imperfections at the interface between the silicon and the gate oxide). Because these are statistically distributed throughout the material, neighbouring pixels contain different numbers of them. The leakage current they produce gives rise to fixed-pattern noise. With current technology, this is dominated by interface states. which reach a concentration of around 10<sup>9</sup>/(cm eV). For minimum fixed-pattern noise, these interface states should be distributed as evenly as possible over the pixel area, which means that the standard deviation in the number of electron/hole pairs generated by these states should be a minimum.

In the IL sensor, roughly 1/3 of the pixel area contributes to fixed-pattern noise (the remainder of the area being covered by channel stops and CCD transfer cells whose contributions are averaged over each column). For 2/3-inch camera format and 400 pixels/line, the standard deviation in the number of electron/hole pairs generated is 660.

The MOS-XY sensor has roughly half the pixel area contributing to fixed-pattern noise, and for a 2/3-inch camera format and 400 pixels/line this gives a standard deviation of 800 in the number of electron/hole pairs generated.

Finally, in the FT sensor with 70% of the pixel area contribution to fixed-pattern noise, a ½-inch camera format and 600 pixels/line gives a standard deviation of 750.

Although on this basis the IL sensors appears to come out best, in reality the difference in these figure is insignificant and, for the dark current at least, there's no discernable difference in the fixed-pattern noise between the three sensors.

#### Shading

Shading is a gradual *long-range* change in sensitivity from one end of the sensor to the other due to dopant inhomogeneities, variations in RC times of gate electrodes and changes in the amplitude of the read-out register clocks after each line blanking period. Because all three sensors use similar dopant profiles (p-wells in high-ohmic n-substrates), none has a clear advantage in this respect, and as far as the other causes of shading are concerned, present state-of-the-art VLSI technology has virtually eliminated them.

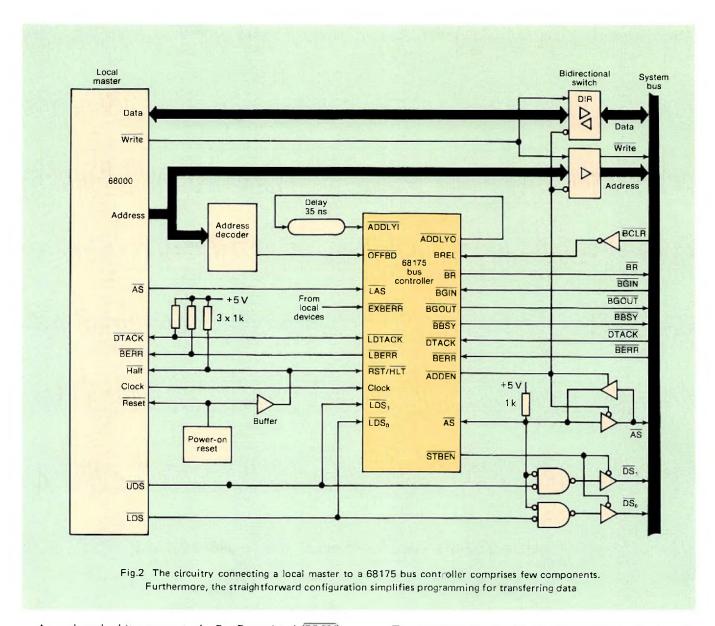

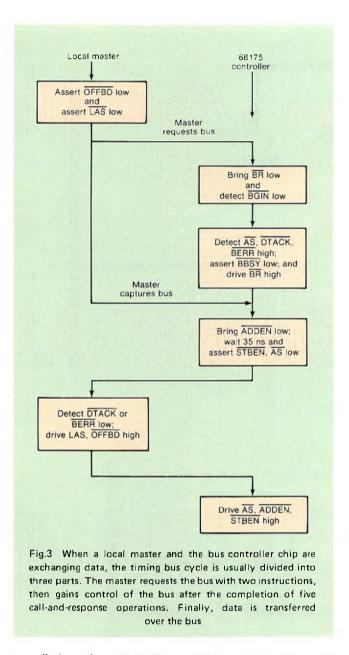

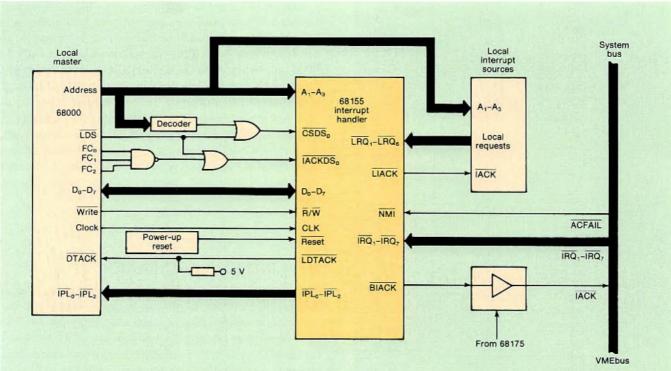

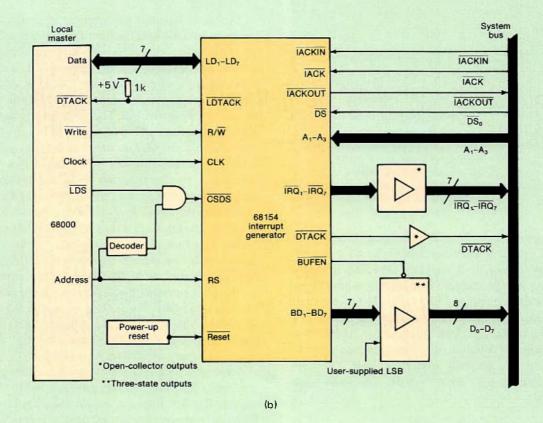

#### Blooming