# The PLL Synthesizer Cookbook

**Harold Kinley**

If you own a modern radio transceiver—ham, marine, CB or commercial rig—here's your chance to pick up valuable info on modern synthesizers and how they work. Learn all about how PLL synthesizers differ, their many and varied applications, and all the latest practical applications of these devices...and how to make them work for you. For the first time, you can get all this, and much more, in one fact-packed, fully illustrated source book.

There's plenty of hard data to satisfy any experimenter, hobbyist, or technician . . . anyone who wants to get in-the-know about PLL synthesizers and what makes them tick. After a thorough intro to modern synthesizers, you'll find all the facts about every PLL chip used in popular transceivers like the Fanon Fanfare 190 DF, Midland 77-830, Realistic TRC 424, Sharp CB-2260, and many, many others. More than a data source, this is a genuine cookbook . . . designed and tailored so you can get hands-on practice with all the information, PLUS find your own practical applications for the PLL synthesizers described. This volume covers ALL the common applications and variations of each chip, VHF and UHF bands, marine, ham, CB, commercial . . . it's all here!

You'll get sound advice on every feature of PLL, and why some chips are really unnecessary, expensive frills. Troubleshooting gets the full treatment, too, for the technician and for the do-it-yourself experimenter.

With more and more equipment coming on the market every day, especially on VHF and UHF bands, this is an excellent guide book for anyone interested in transceivers. So if a dozen questions run through your mind every time you see a PLL chip, this must-read manual has all the answers!

Harold Kinley is an experienced CB and amateur radio technician who has conducted extensive research in the field of PLL devices. He lives in Kingtree, SC.

# OTHER POPULAR TAB BOOKS OF INTEREST

Towers' International D Amp Linear-IC Selector (No. 12:6—\$7.95 paper; \$12.95 leatherefte)

- How To Design and Build Audio Amplifiers, including digital circuits—2nd Edition (No 1206— \$9.95 paper; \$15.95 hard)

- The Master IC Cookbook (No. 1199-\$9.95 paper; \$15.95 hard)

- The Master Guide To Electronic Circuits (No. 1184—\$12.95 paper; \$19.95 hard)

- 84 Practical IC Projects You Can Build (No. 1142—\$4.95 paper; \$8.95 hard)

- The Practical Handbook of Amateur Radio FM & Repeaters (No. 1212—\$9.95 paper, \$15.95 hard)

- How To Troubleshowt & Repair Amateur Radio Equipment (No. 1194—\$9.95 papes; \$14.95 hard)

- The 2-Meter FM Repeater Circuits Handbook— Using FM for Amateur Radio (No. 621—\$6.95 paper; \$9.95 hard)

- Home-Brew HF/VHF Antenna Handbook (No. 963—\$6.95 paper; \$8.95 hard)

TAB TAB BOOKS Inc.

Blue Ridge Summit, Pa. 17214

Send for FREE TAB Catalog describing over 750 current titles in print. ISBN 0-8306-1243-2 Prices higher in Canada

World Radio History

#### **FIRST EDITION**

#### FIRST PRINTING—SEPTEMBER 1980

Copyright C 1980 by TAB BOOKS Inc.

Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

#### Library of Congress Cataloging in Publication Data

Kinley, Harold The PLL synthesizer cookbook.

Includes index. 1. Citizens band radio—Equipment and supplies. 2. Phase-locked loops. I. Title. TK6570.C5K56 621.3846 80-19966 ISBN 0-8306-9707-1 ISBN 0-8306-1243-2 (pbk.)

World Radio History

The first time I was faced with repairing a phased-lock loop (PLL) circuit in a radio I realized just how little I knew about PLL synthesizers. With a little luck and a lot of time, I managed to get the thing repaired though. But we technicians and hobbyists cannot always depend on luck and we certainly cannot afford to spend lots of time on one repair job. Besides, I had always prided myself on using logical troubleshooting procedures based on an understanding of the particular circuit at hand. Troubleshooting by the "hit or miss" method never suited my style.

While I was involved in my first PLL encounter, I decided then and there that I would do everything possible to learn all I could about these new PLL synthesizers. After much searching for books on the subject, I was disappointed at finding practically nothing written on the subject. So I turned to the manufacturers of the PLL ICs for data sheets, application notes or whatever information they could supply on these IC products. I spent quite some time pouring over this technical data. I also experimented on PLL circuits for that "hands on" experience. With all this researching, I finally reached a point where I was comfortable with PLL synthesizers. I no longer had to regard the PLL circuit as a *black box*. I could now apply my logical troubleshooting method to these circuits too.

The thought then occurred to me: There must be thousands of technicians like myself who want to learn how PLL synthesizers work. I then decided to put the results of my research of PLL synthesizers into a book.

The first chapter is an introduction to the basic PLL synthesizer circuit. The rest of the book covers specific PLL ICs and circuits in detail. The appendices give information on still more PLL ICs.

Several semiconductor and CB manufacturers supplied information and material for the book. I therefore wish to express my appreciation to the following companies for their assistance:

Cobra Communications (Dynascan Corp.)—Bruce Diamond E. F. Johnson Co.—Robert Cervenka Fairchild Camera & Instrument Co. Faron/Courier (Resdel Industries)—Miguel Santana Melco (Mitsubishi Electric Corp.) Midland International Corp. National Semiconductor Corp. NEC (National Electric Co.) OKI Semiconductor Panasonic (Matsushita Electronics Corp.) Pearce—Simpson(Division of Gladding Corp.)—Earle Smith President Electronics/American Radio—Rex Trobridge Radio Shack Store, Kingstree, SC (Haigler Hardware) Toshiba America

Harold Kinley

.

- 2 The μPD2816C Digital Synthesizer ......24 Special Features—Internal Structure—A Typical Application— Cobra 1000 GTL CB Synthesizer

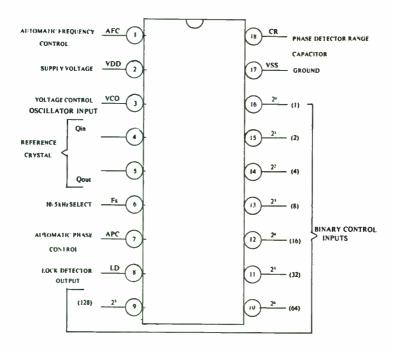

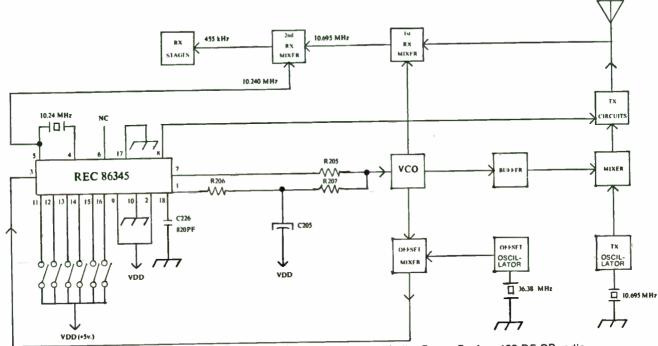

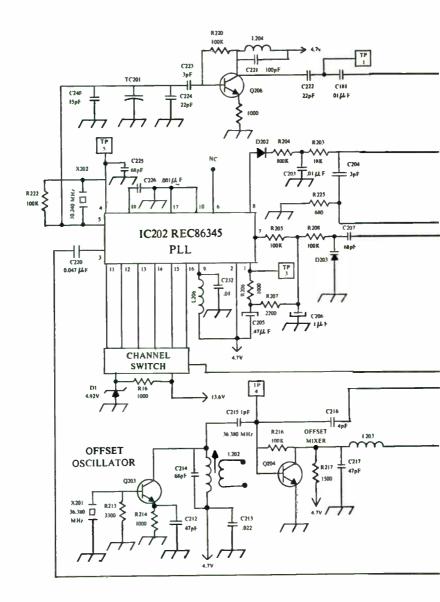

- 4 The REC86345 Digital Synthesizer IC......63 Special Features—Internal Structure—Fanfare 190 DF PLL Synthesizer

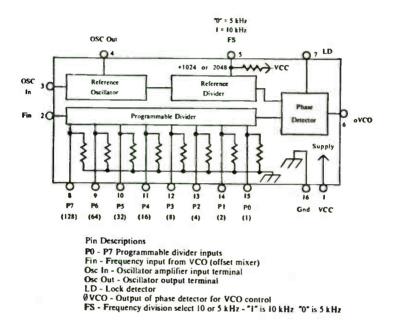

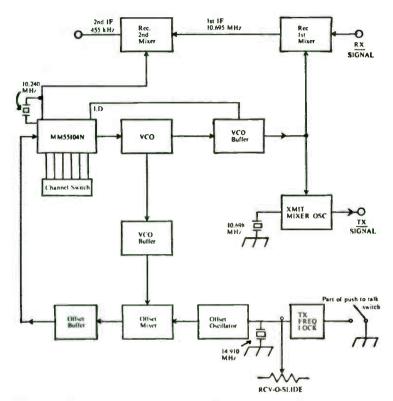

- 6 The MM55104N PLL IC......101 Reference Oscillator—Reference Divider—Programmable Divider—Phase Detector—Practical Application—Pearce— Simpson Super Tiger 40A PLL Synthesizer

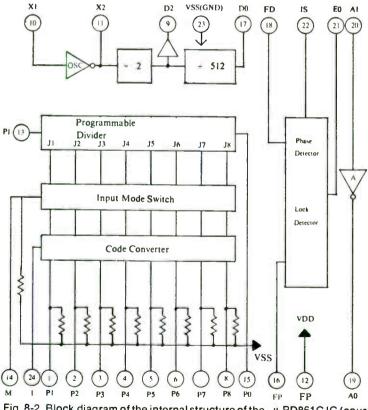

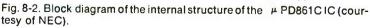

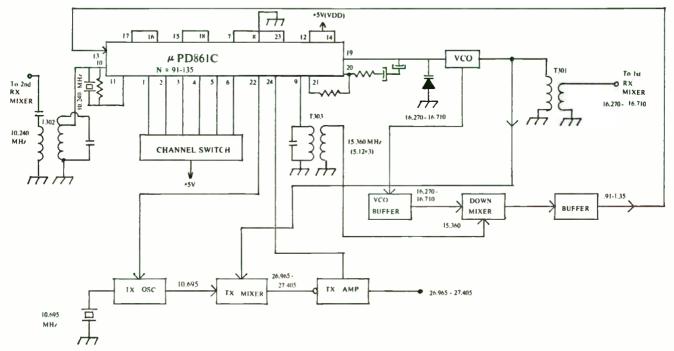

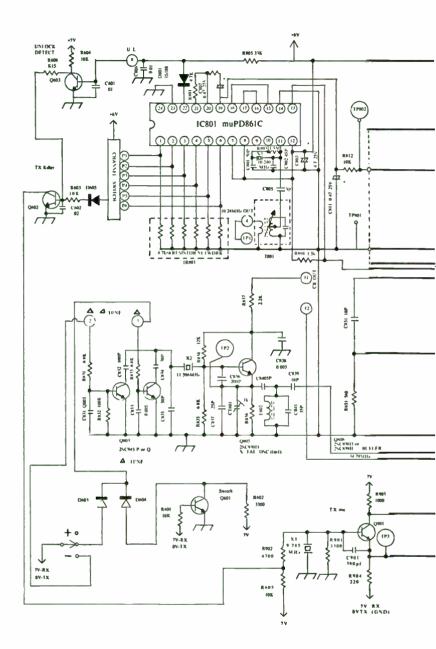

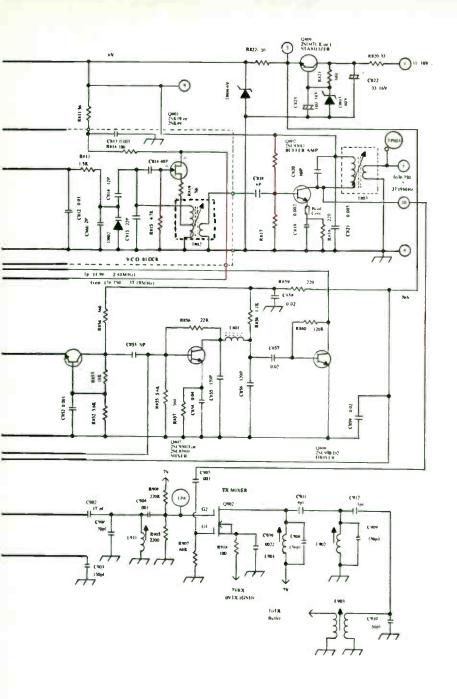

| 8     | The μPD861C PLL IC                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------|

| 9     | The MM55106 PLL IC                                                                                  |

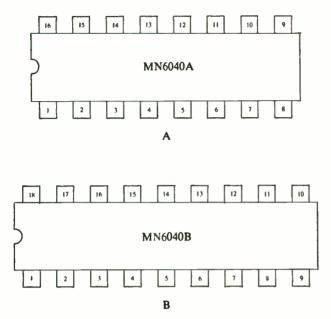

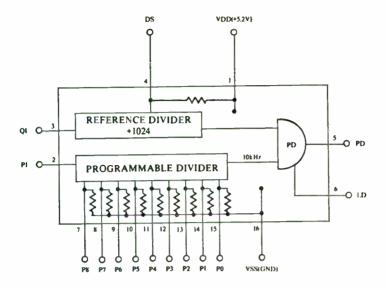

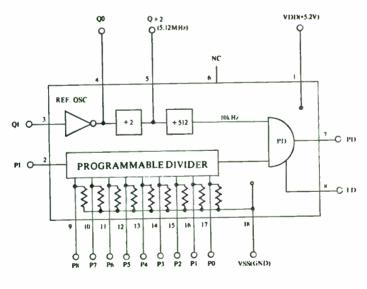

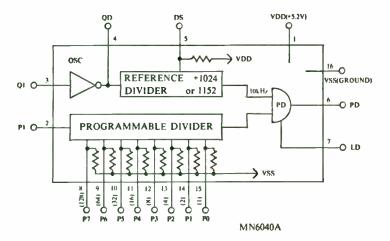

| 10    | The MN6040 PLL IC Series201<br>Special Features—Internal Structure—Robyn SX-402D PLL<br>Synthesizer |

| 11    | Toshiba PLL ICs                                                                                     |

| Appen | dices                                                                                               |

| ••    | The PLLO3A PLL IC240<br>Pin Functions—Application                                                   |

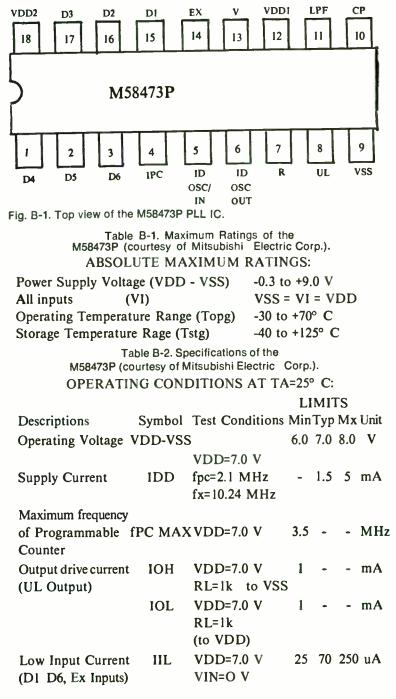

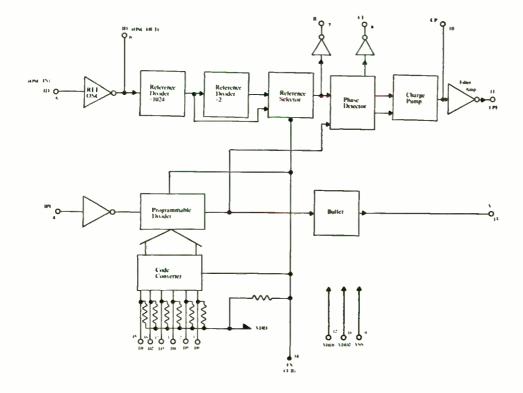

| B     | The M58473P PLL IC243<br>Pin Functions—Application                                                  |

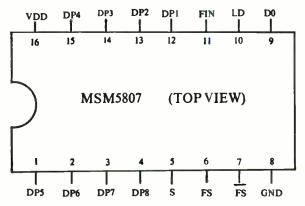

| C     | The MSM5807 PLL IC247<br>Pin Functions—Application                                                  |

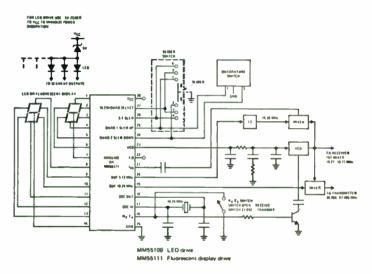

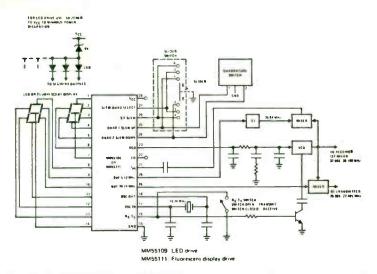

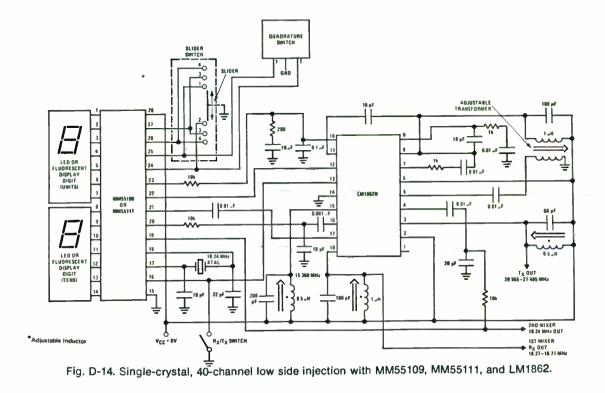

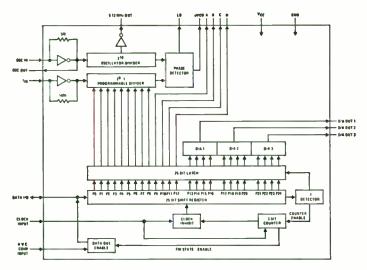

| D     | National Semiconductor PLL ICs                                                                      |

| E     | Fairchild 11C84 PLL IC                                                                              |

|       | Index278                                                                                            |

World Radio History

# Chapter 1 Introduction to PLL Synthesizers

In this chapter you'll learn what various stages make up a typical PLL synthesizer. Then after all stages are discussed, a complete PLL synthesizer will be analyzed. The basic stages which make up a PLL synthesizer are:

- □ Programmable divider

- □ Fixed divider

- □ Phase detector

- □ Charge pump and filter

- □ Voltage-controlled oscillator

- Crystal-controlled oscillator

- □ Mixers

# **PROGRAMMABLE DIVIDERS**

The programmable divider is defined as a frequency divider that can be programmed to divide its input frequency by a certain divisor (N). The actual divisor is determined by the application of proper voltage levels to the various *program* pins on the IC device. There are two voltage levels used on the program pins, the HIGH level (usually near the IC supply voltage) and the LOW level (at or near ground potential). The HIGH level is usually referred to as binary 1 and the LOW level as binary 0. This will be fully explained shortly.

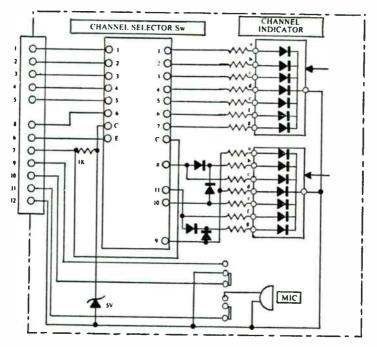

The proper voltage levels are usually applied to the program pins through the channel selector switch directly. Hence, the various positions of the channel selector switch apply HIGH and LOW levels to the program pins in various combinations. Each different combination or code programs the divider to divide the input frequency by a certain divisor, N. In order to understand how this programming is achieved, you will need a basic understanding of the binary numbering system.

# **Pure Binary System**

The binary number system uses only two different digits to represent any decimal number. The two digits are binary l and binary 0. Because only two different digits are used, the system is said to have a base of 2. For comparison, the decimal system uses 10 different digits. It therefore has a base of 10. Both the decimal system and the binary system are weighted systems. This simply means that the relative positions occupied by the digits determine the weight the digit carries. In the decimal system the weights are units, tens, hundreds, thousands, ten thousands, and so on for whole numbers. For example, in decimal number 5,362, the weight of the position occupied by the 2 is units, the weight of the position occupied by 6 is tens, the weight of the position occupied by the 3 is hundreds, and the weight of the position occupied by the 5 is thousands. The weight of each position is 10 times the weight of the position to its right.

The binary system uses only two different digits, 0 and 1, so the weight of each position or bit of a binary number is twice the weight of the bit to its right. For example, in the positions, ..., ..., ..., 256, 128, 64, 32, 16, 8, 4, 2, 1, each bit position has a weight which is twice that of the bit position to its right. The bits increase in weight from the right to the left by a factor of 2. The bit to the far right is called the least significant bit (LSB) and the bit to the far left is called the most significant bit (MSB). Here is a typical binary expression: 10010111. Unless otherwise noted, assume that the bit to the far right is the least significant (LSB) and the bit to the far left is the most significant (MSB). How do you determine the decimal number represented by this binary expression? Here's how: Simply write down the weights of the positions occupied by the binary 1 and then add them together to find the decimal equivalent. If necessary, write down the weights of the various positions above the binary digits like this: 10010111. Then simply add the weights of the bit positions where the binary 1 appears. In this example, this would be 128 + 16 + 4 + 2 + 1, or 151. So the binary expression 10010111 is the equivalent of decimal number 151. The number of bit positions required to conver from decimal to binary

form varies with the value of the decimal number. For instance, the binary equivalent of 2 could be written as simply binary 1 0. The decimal number 9 would be binary  $1 \ 0 \ 0 \ 1$ .

In converting a decimal number to binary, the following procedure will work: Write out the various weights of the bit positions as follows; ..., ..., 256, 128, 64, 32, 16, 8, 4, 2, 1. You need only expand out to a weight position that is equal to or smaller than the number to be represented. For example, to represent decimal number 249, you need only to expand the positions out to 128, because the next position (256) is larger than the decimal quantity to be represented. At this point, there will be eight bits required to represent decimal number 249. Each bit will be represented by either binary 1 or binary 0. All you need to do now is find out what the state of each position will be. Here is the procedure: From 249, subtract the weight of the largest bit position to be used. It has already been determined that the largest bit position is 128, so 249-128=121. Place binary 1 over position 128. Repeating this procedure, the largest bit position that doesn't exceed 121 is 64, so place binary 1 over 64 and subtract 64 from 127. This yields 121-64, or 57. The largest remaining bit position that doesn't exceed 57 is 32, so place binary 1 over 32 and subtract 32 from 57. This yields 57-32, or 25. The largest remaining bit position that doesn't exceed 25 is 16, so place binary 1 over 16 and subtract 16 from 25. This yields 25-16, or 9. The largest remaining bit position that doesn't exceed 9 is 8, so place binary 1 over the 8 and subtract 8 from 9 to yield 9-8, or 1. Place a binary 1 over the 1. Then over the unused positions, place binary 0. The expression would look like this:

1 1 1 1 1 0 0 1 128-64-32-16-8-4-2-1.

In the calculations, we used 128, 64, 32, 16, 8, and 1. All these have binary 1 over them. The only two positions not used are the 4 and 2 positions, so they would have a binary 0 over them to indicate that they are not used. The final binary expression is 11111001. This is the equivalent of 249. This system of binary numbering is called the *pure binary system*. This system is used extensively in programming the programmable dividers used in PLL synthesizers.

# **Binary Coded Decimal System**

The binary coded decimal (BCD) system is a modified form of the pure binary system. This system uses the weighted 8-4-2-1 bits to represent each individual digit of a decimal number. Therefore, four binary bits are required for each decimal digit. For example, representing the decimal number 249 in BCD form would require  $3 \times 4$ , or 12 binary bits. The 2 would become 0010; the 4, 0100; and the 9, 1001. This would be written out as: 0010.0100. 1001. The dots between each binary group indicates that the BCD code is used. The BCD system requires more bits to represent a given decimal number than does the pure binary system. For example, the number 249 in the pure binary system requires only 8 bits (11111001) whereas 12 bits are required in the BCD system (0010.0100.1001). This factor makes the circuitry for BCD system is that it is easier for most of us to make the conversion between decimal numbers and binary numbers in BCD form.

Since there are only 10 different codes used in the BCD system, one who uses the system regularly soon learns to recognize the decimal equivalents at a glance. The conversion codes for the 10 different digits are shown in Table 1-1. This BCD system is also used in some PLL ICs to program the programmable dividers. Some dividers can be programmed with either the BCD or the pure binary system.

| Decimal number | BCD Equivalent |

|----------------|----------------|

| 0              | 0000           |

| 1              | 0001           |

| 2              | 0010           |

| 3              | 0011           |

| 4              | 0100           |

| 5              | 0101           |

| 6              | 0110           |

| 7              | 0111           |

| 8              | 1000           |

| 9              | 1001           |

# **Programming the Divider**

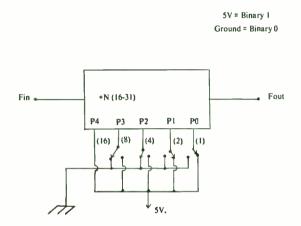

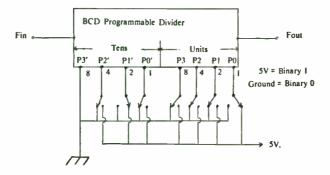

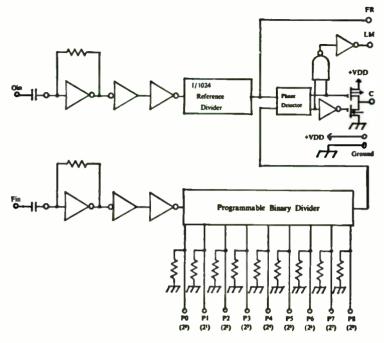

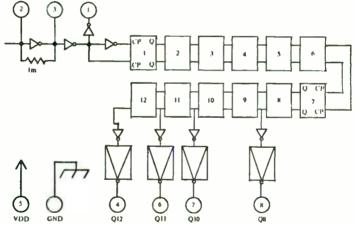

Figure 1-1 is a block diagram of a programmable divider. The pins labeled P0 through P4 are the programming pins of the device. Each pin has a specific *weight*. The individual pin weights are P0=1, P1=2, P2=4, P4=8, and P4=16. The divider will divide the input frequency by the number N, which is programmed into the divider. The number programmed is determined by adding together the weights of the pins at the binary 1 level. (binary 1 = 5 volts, and binary 0 = 0 volts or ground). You can see that P4 is connected directly to the 5-volt supply, so P4 will always be at bi-

nary 1 level. This means that its weight of 16 will always be used in determining the divisor N. The other program pins (P3 through P0) are connected to a switch that can either ground the pin or apply 5 volts to it; that is, the switch can apply either binary 1 or binary 0 to the pin. Thus, the device can be programmed by the various combinations of switch positions. Because there are four switches used and each switch has two positions, there are 24, or 16, possible combinations. Therefore, 16 different divisors N are possible using this arrangement. Table 1-2 shows the 16 different combinations.

Fig. 1-1. Block diagram of a programmable divider. This divider is capable of dividing the input frequency by any divisor from 16 through 31. The minimum divisor of 16 is set by connecting P4 directly to 5 volts. The weights of the program pins P0 through P4 are shown in parentheses.

Look closely at the switch positions in Fig. 1-1 and see if you can determine the divisor, N, which is programmed into the divider. If necessary, use the chart in Table 1-2. The divisor, N, is determined by simply adding the weights of the pins that are at the binary 1 level. In the example in Fig. 1-1, the pins at binary 1 level are P4 (always at binary 1), P1, and P0. Simply add the weights of these pins as shown below to find the divisor N:

The divider will divide its input frequency by 19, so the frequency appearing at the output of the divider will be  $F(in) \div 19 = F$ (out). This divider is programmed using the pure binary code.

Let's look at a divider that is programmed using the BCD system. An example is shown in Figure 1-2. In this illustration, the divider is shown to be programmed for channel 21. An internal *code converter* is built into the device. This converter in turn determines the proper divisor, N, for each channel. For a

Fig. 1-2. Block diagram of a BCD programmable divider. The tens digit is set by PO' through P3' and the units digit is set by P0 through P3. The divider here is programmed for channel 21. The program lines shown are actually connected to a code converter, which in turn applies the proper binary levels to the internal programmable divider.

40-channel CB, for example, the digit in the tens position cannot be allowed to exceed 4 and the digit in the units position cannot be allowed to exceed 9. Otherwise, improper programming would result. The channel selector switch is designed to prevent this from occurring. Some IC PLL devices incorporate a special circuit to detect when the program pins are improperly programmed. This detector output can be used to kill the transmitter output when *misprogramming* occurs, caused by loose contacts on the channel switch or other reasons. This prevents the radio from radiating improper frequencies.

Referring again to Fig. 1-2, you can see that the tens position has 4 program lines: P0', P1', P2', and P3', with respective weights of 1, 2, 4, and 8. The units position also has 4 program lines: P0, P1, P2, and P3, with respective weights of 1, 2, 4, and 8. The binary level on pins P0 through P3 determines the number in the units position, while the binary level applied to pins P0' through P3' determine the number in the tens position. Table 1-2 shows the allowable combinations for the numbers 1 through 40. Notice that P3' is always at binary 0 so it is connected directly to ground.

Programmable dividers used in CB PLL synthesizers generally aren't capable of dividing input frequencies in excess of 5 MHz. These devices are usually constructed with CMOS circuitry for low power dissipation.

| PIN    | P4 | P3 | P2 | <b>P1</b> | P0 |

|--------|----|----|----|-----------|----|

| Weight | 16 | 8  | 4  | 2         | 1  |

| N=16   | 1  | 0  | 0  | 0         | 0  |

| N=17   | 1  | 0  | 0  | 0         | 1  |

| N=18   | 1  | 0  | 0  | 1         | 0  |

| N=19   | 1  | 0  | 0  | 1         | 1  |

| N=20   | 1  | 0  | 1  | 0         | 0  |

| N=21   | 1  | 0  | 1  | 0         | 1  |

| N=22   | 1  | 0  | 1  | 1         | 0  |

| N=23   | 1  | 0  | 1  | 1         | 1  |

| N=24   | 1  | 1  | 0  | 0         | 0  |

| N=25   | 1  | 1  | 0  | 0         | 1  |

| N=26   | 1  | I  | 0  | 1         | 0  |

| N=27   | 1  | 1  | 0  | 1         | 1  |

| N=28   | 1  | 1  | 1  | 0         | 0  |

| N=29   | 1  | 1  | 1  | 0         | 1  |

| N=30   | 1  | 1  | 1  | 1         | 0  |

| N=31   | 1  | 1  | 1  | I         | 1  |

| Table 1-2. Different Program Combinations | Applied to Divider of Fig. 1 | 1-1. |

|-------------------------------------------|------------------------------|------|

|-------------------------------------------|------------------------------|------|

# **FIXED DIVIDERS**

The fixed dividers used in PLL circuits usually operate with higher input frequencies than the programmable dividers. The reference oscillator frequency (usually 10.240 MHz) is divided by the fixed divider to yield the basic reference frequency. The basic reference frequency is usually 10 kHz. Sometimes, though, 5 kHz is used as the reference. For a 10 kHz reference frequency, the divider would have to divide the reference oscillator frequency (10.240 MHz) by 1024. Some fixed dividers also have the divideby-2 output available at a terminal of the IC. This would be 10.240 MHz divided by 2, or 5.12 MHz. This frequency can be multiplied and used in some PLL systems to mix with the voltage-controlled oscillator frequency for down conversion. You will see an example of this later.

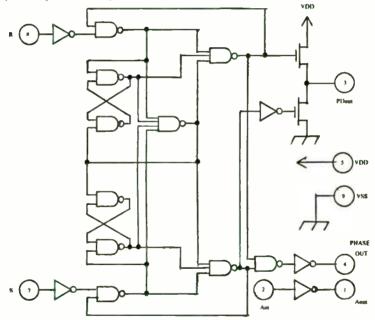

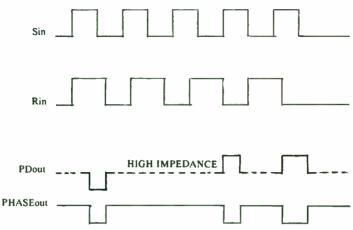

# PHASE DETECTORS/LOCK DETECTORS

The output of the programmable divider is fed to an input to the phase detector or comparator. The 10 kHz reference signal from the fixed divider is fed to a separate input of the phase detector. The phase and frequency of the two inputs are compared, and a pulsed output is produced. The pulse width and spacing of the output pulses depend upon the relative frequency and phase of the detector inputs. The output of the phase detector is used to control the voltage-controlled oscillator. However, the pulse output of the detector must be properly filtered before being applied to the voltage-controlled oscillator. Usually associated with the phase detector is an output which indicates a *locked* or *unlocked* condition. If an unlocked condition exists, the lock detector output provides a signal for stopping the transmitter output. This prevents signal radiation at improper frequencies.

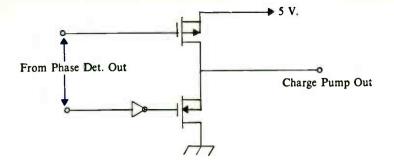

### CHARGE PUMPS AND FILTERS

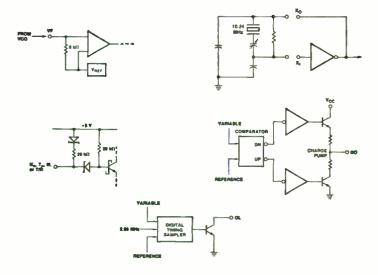

A typical CMOS charge pump is shown in Fig. 1-3. The function of the charge pump is to feed the pulses from the phase detector to an RC (resistor-capacitor) filter nerwork to filter out the pulsations. Then the smooth DC voltage can be used to control the voltage-controlled oscillator. Notice that the charge pump accepts two inputs from the phase detector and has a single ended output. Some ICs incorporate an *active filter*. This is a specially designed amplifier with a controlled feedback network. This amplifier filter resists any rapid or high-frequency changes in its output. The result is a low-pass filter.

### **VOLTAGE-CONTROLLED OSCILLATORS**

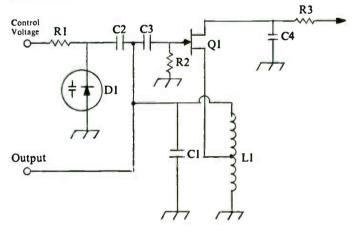

As the name implies, a voltage-controlled oscillator (VCO) is an oscillator whose frequency is governed by a control voltage. The component which makes this possible is the varactor diode. All diodes exhibit a certain amount of capacitance when they are reverse biased. The varactor diode is simply a junction diode that is carefully manufactured so that the capacitance varies nearly linearly with a changing reverse bias or control voltage. The

Fig. 1-3. A typical charge pump. Notice the dual inputs from the phase comparator is converted to a single ended output.

schematic of a voltage-controlled oscillator is shown in Fig. 1-4. Diode D1 is the varactor diode. Notice the symbol used to represent the varactor. The capacitor in the circle indicates the diode is a varactor.

Fig. 1-4. A voltage-controlled oscillator in the Hartley configuration. A control voltage applied to varactor diode D1 through resistor R1 controls the oscillator frequency.

This oscillator is basically a Hartley-type oscillator. The frequency-determining components consist of the varactor, D1; C2; C1; and L1. Because D1 forms part of the frequency-determining network, any change in the capacitance of DI will change the output frequency of the VCO. The capacitance of DI can be changed by varying the positive control voltage applied to DI through resistor R1. The control voltage would have to be positive in order to reverse bias the varactor. If the varactor were connected oppositely a negative control voltage would then be required. Normally, PLL circuits use positive control voltages.

# **CRYSTAL-CONTROLLED OSCILLATORS**

Anyone reading this book should be familiar with crystalcontrolled oscillators. One of the main advantages of PLL synthesizers is that the use of crystals is minimized. Some PLL synthesizers require three or more crystals; some require only one. The basic reference frequency is always derived from a crystalcontrolled oscillator. The reference oscillator in the majority of PLL synthesizers operates at 10.240 MHz. This usually serves as second oscillator frequency for the receiver, also.

Other crystal-controlled oscillators in PLL synthesizers are usually used to mix the VCO frequency for up or down conversion. Usually the VCO operates at higher frequency than the input of the programmable divider can accept. So the VCO frequency must be converted down to a frequency which can be handled by the divider. These operations are discussed in detail in the following chapters.

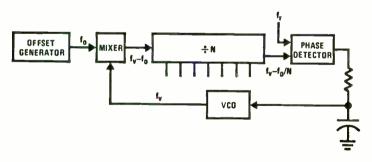

# **MIXERS**

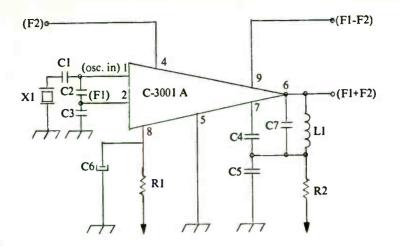

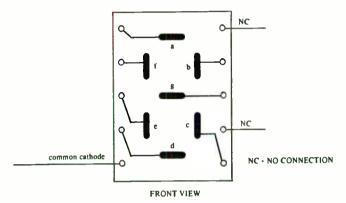

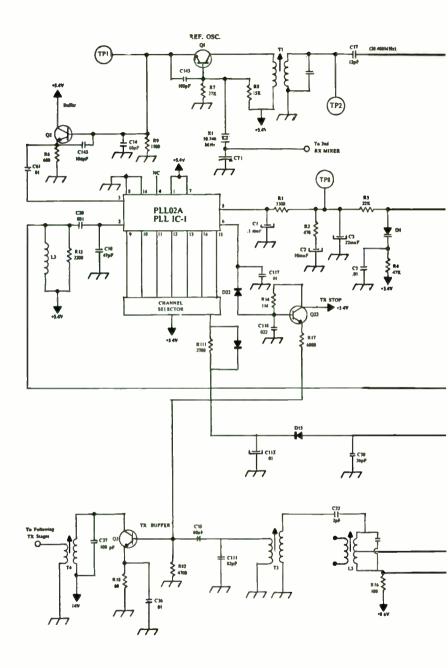

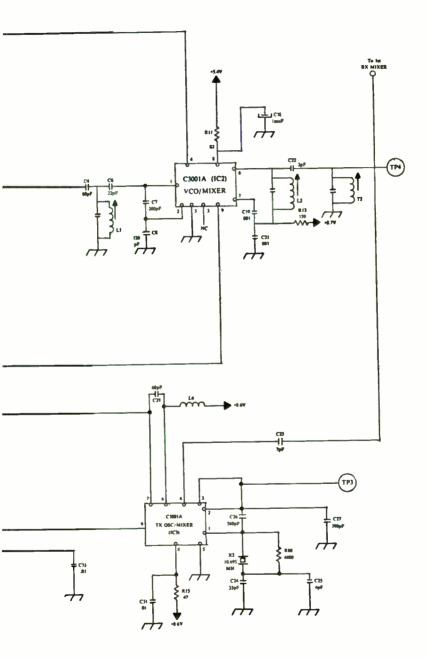

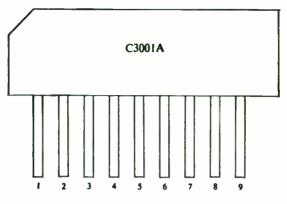

Mixer circuits are used in most PLL synthesizers. The operation of these circuits is no great mystery to the average technician. There are, however, some special IC mixers used in PLLs which deserve some special attention. Two commonly used IC mixers used in PLLs are the C3001-A and the TA7310P. Basically, these devices consist of dual-balanced mixers and an oscillator. When two input frequencies are applied to this device, both the sum and the difference of these frequencies are available at separate output terminals. Figure 1-5 shows the basic setup for the C3001-A.

The frequency of the oscillator is controlled by the crystal (X1) connected to pin 1 through capacitor C1. A portion of the oscillator signal is fed to pin 2 through the voltage divider network C2-C3. This signal at pin 2 is identified as F1. Another signal (F2) is fed to pin 4. Now the sum of F1 and F1 is taken from pin 6 and the difference of F1 and F2 is taken from pin 9. These mixers are used to advantage, as you will see in a following chapter.

Fig. 1-5. A typical setup for the dual balanced mixer/oscillator IC, C3001-A. Both the sum and the difference of inputs f1 and f2 are available at separate output terminals.

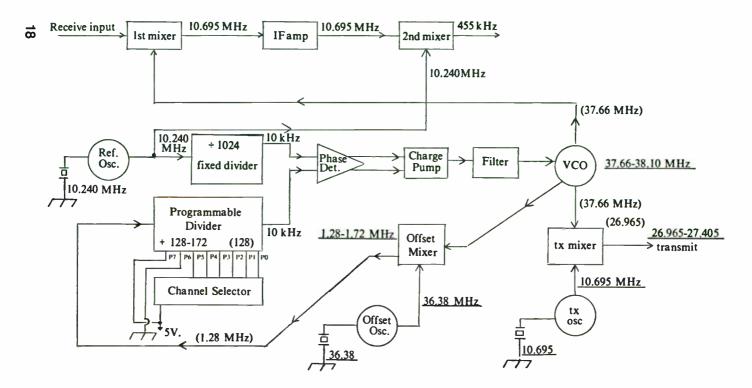

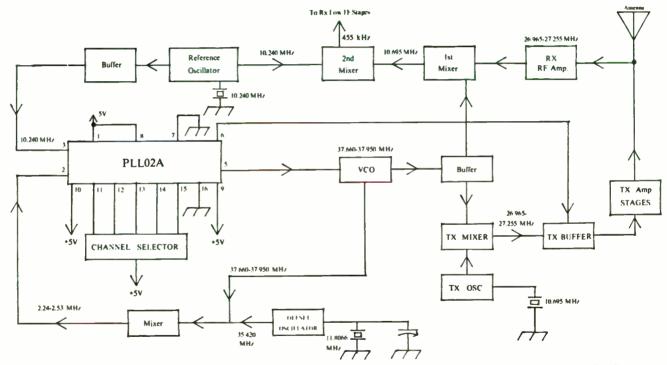

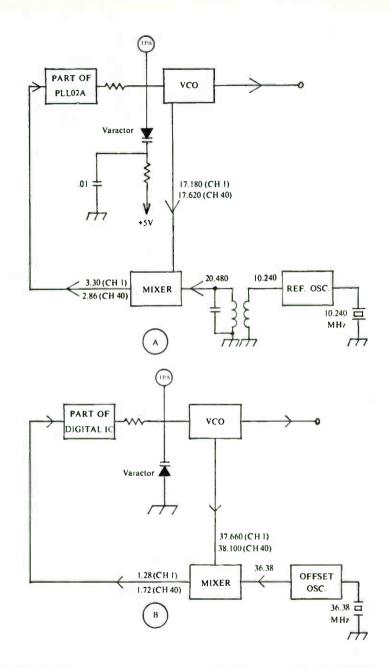

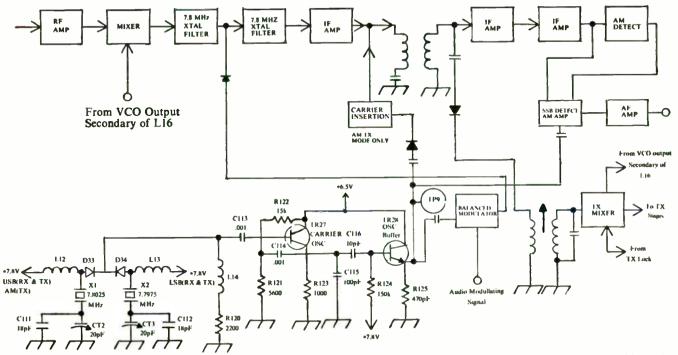

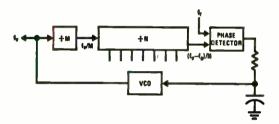

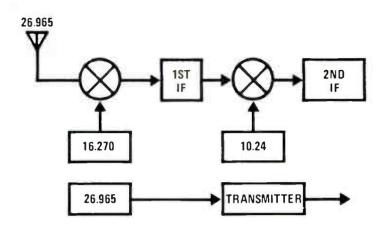

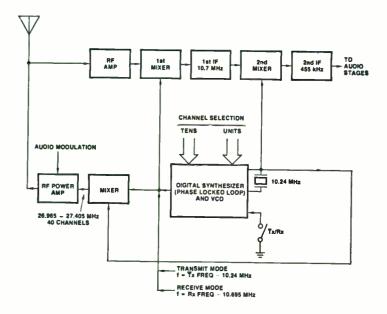

# THE PLL AS A SYSTEM

Now that the function of the various individual PLL stages have been discussed, it is time to analyze the PLL system as a whole. During this discussion, refer to the block diagram in Fig. 1-6. the basic reference frequency is derived from the reference oscillator. The 10.240 MHz signal from the reference oscillator is fed to the fixed divider where the frequency is divided by 1024 to yield 10 kHz. This 10-kHz signal is then used as the basic reference frequency. The reference oscillator also serves as the second receive oscillator.

The programmable divider divides its input frequency by divisor N. The N number is determined by the binary levels applied to the program inputs, P0 through P7. The weights of P0-P7 are:

| <b>P0</b>  | = | 1   |

|------------|---|-----|

| <b>P1</b>  | = | 2   |

| P2         | = | 4   |

| <b>P3</b>  | = | 8   |

| P4         | = | 16  |

| <b>P</b> 5 | = | 32  |

| <b>P</b> 6 | = | 64  |

| <b>P</b> 7 | = | 128 |

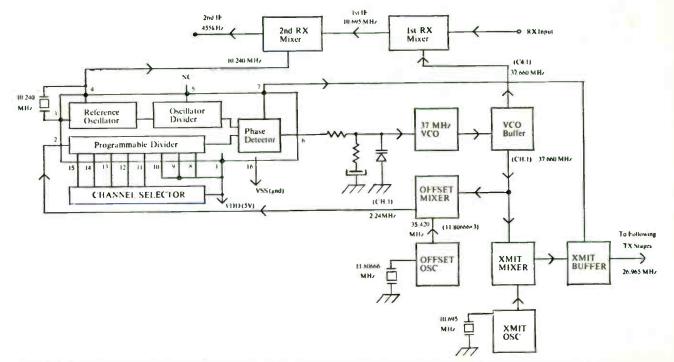

Fig. 1-6. The complete block diagram of a typical PLL synthesizer. The frequencies shown in parentheses are for channel 1 operation.

Notice that P7 does not connect to the channel selector switch. Instead it is connected directly to the 5-volt supply source. This means that P7 (weight of 128) will be at the binary 1 level at all times, regardless of the channel selector position. This automatically sets the *minimum divisor* N at 128. Also notice that P6 is not connected to the channel selector switch. It instead connects directly to ground, thus keeping P6 at the binary 0 level at all times. The weight of P6 (64) will therefore never be used. The other program lines, through P0, P5, all connect to the channel selector switch, so the binary level on these lines will depend upon the channel selector position.

The divider is set up to have an N range of 128 through 172. Actually, with P6 grounded, the divider could possibly be programmed to divide by up to 191 if all the other program lines were set to binary 1. See the calculation:

| P0 = 1      |

|-------------|

| P1 = 2      |

| P2 = 4      |

| P3 = 8      |

| P4 = 16     |

| P5 = 32     |

| P7 = 128    |

| 191 total N |

However, the maximum divisor needed for this particular setup is 172. So the channel selector switch is designed to limit the maximum divisor N to 172.

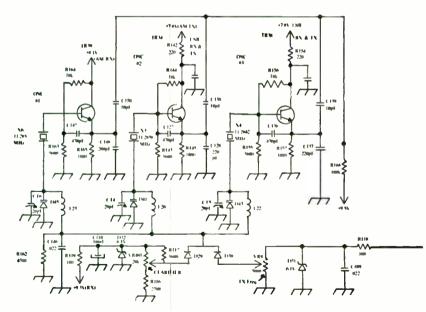

Let's go through the analysis of the complete PLL using channel 1 as an example. The VCO operates in the 37-MHz range. The VCO itself serves directly as the first receive oscillator. The first intermediate frequency (i-f) is 10.695 MHz, so the VCO must operate at a frequency that is equal to the sum of the channel frequency and the 10.695-MHz first i-f. For CB channel 1, for example, the VCO frequency would be 26.965+10.695, or 37.660 MHz. In the transmit mode, the VCO frequency is mixed with a 10.695-MHz signal to yield the transmit frequency. For channel 1 this would be 37.660-10.695, or 26.965 MHz. Notice that this is just the reverse of the mixing operation for the receive mode.

The programmable divider is not capable of dividing the 37-MHz VCO frequency, so an offset crystal-controlled oscillator is used to mix with the VCO frequency to yield a difference frequency which the divider can handle. This difference frequency maintains proper frequency relationships with the VCO frequency. If the VCO frequency increases, so will the offset frequency. Likewise, if the VCO frequency decreases, so will the offset frequency. Futhermore, the frequency changes of the VCO will be equalled by the changes in the offset frequency. For example, if the VCO frequency increases by 10 kHz, then the offset frequency will also increase by 10 kHz.

It would be easier to go through the analysis after first assuming that the radio has already been switched on and the PLL system stabilized. It only takes a fraction of a second for the PLL to stabilize after power is applied but what happens in that fraction of a second is important. The sequency of events could go like this. When power is first applied, the VCO will not operate exactly on the proper frequency. Instead, it will be operating at a random frequency. Say the VCO frequency initially starts at a lower frequency than needed. This signal is fed to the offset mixer where it is mixed with the signal from the offset oscillator to yield a difference frequency. This difference frequency is then sent to the programmable divider. So the output of the programmable divider would be the difference frequency divided by the programmed divisor, N. This output signal is sent to the phase detector where it is compared to the standard reference. The large difference in frequency causes the phase detector to issue a proportionately large error signal. This pulsed error signal is fed to the charge pump which in turn feeds a signal to the filter. The output of the filter is a smooth DC voltage whose amplitude is proportional to the phase or frequency difference of the phase detector inputs. This correction voltage is now applied to the control line of the VCO. Remember, changing the reverse bias to the varactor diode will change the VCO frequency. This is precisely what the correction voltage does. This causes the VCO to move its frequency in a direction which will make the output of the programmable divider approach the reference frequency. So the VCO frequency gradually increases toward the desired frequency. As the VCO approaches this frequency, the output of the programmable divider will approach the 10-kHz reference frequency. Thus, the correction voltage will become smaller and smaller. And finally, after a fraction of a second, the PLL will stabilize. At the point of stabilization, the VCO frequency will be the desired one. Because the output of the programmable divider is now equal to the reference frequency, the phase detector will issue no error signal.

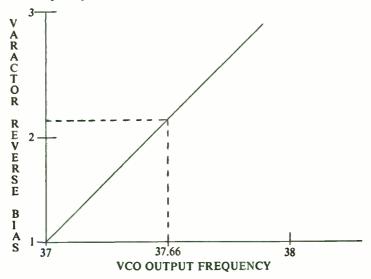

There will be a voltage applied to the control line of the VCO

even under locked conditions, but this voltage will not contain an error signal component. This is important to keep in mind. A study of the graph in Fig. 1-7 should clarify this point for you. The vertical axis represents the varactor reverse bias voltage, and the horizontal axis represents the VCO frequency. You can see from the graph that as the varactor reverse bias increases, the VCO frequency also increases. Conversely, when the varactor reverse bias decreases, the VCO frequency decreases. A specific bias voltage relates to a specific VCO frequency. For example, the dotted lines on the graph shows that approximately 2.2 volts bias causes the VCO frequency to be 37.660 MHz.

Fig. 1-7. This graph shows the relationship between the varactor bias and the vco output frequency, the dotted line shows that approximately 2.2 volts bias relates to a VCO frequency of 37.660 MHz.

# SOME PRACTICAL CONSIDERATIONS

PLL synthesizers are normally very reliable and the frequencies they generate are usually very precise. Even the best of systems can falter at times, though. Lets look at a few examples of PLL malfunctions which can cause the frequencies it generates to be out of tolerance. During this discussion, refer again to Fig. 1-6. Because the reference oscillator is used as the frequency standard let's first take a look at what happens if this 10.240 MHz oscillator is operating off frequency. You might be a little surprised at the effect! Table 1-3. Program Codes Applied to Program Lines of BCD Device of Fig. 1-2.

|       | 0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-            | - 0      |

|-------|---------------------------------------------------|----------|

| Units | 2000000000000000000000                            | 00       |

|       | 200000000000000000000000000                       | 0        |

|       | G                                                 | - 0      |

|       |                                                   | - 0      |

|       |                                                   | - 0      |

| Tens  | ,<br>2000000000000000000000000000000000000        | <b>-</b> |

|       |                                                   | 0        |

|       | Chanel<br>6 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | 40       |

Assume that the reference oscillator is operating 1000 H off frequency to the high side. This frequency would therefore be 10.241 MHz. The reference frequency would then be 10.241 MHz+1024, or 10,000.976. So a 1000-Hz increase in the reference oscillator frequency results in less than a 1-Hz increase in the basic reference frequency (0.976 Hz, to be exact). This new reference frequency will change the receive and transmit frequencies, but how much? To find out work your way backward from the output of the programmable divider to the VCO itself.

The output of the programmable divider will have to equal the new reference frequency (10,000.976 Hz) for the loop to achieve lockup. Let's say the divider is programmed to divide its input by 128. So if the output of the programmable divider is to be 10,000.976 Hz, the input to the divider will have to be  $128 \times 10,000$ . 976, or 1,280,124.9 Hz. This is the new offset frequency. You probably remember from the previous discussion that the offset frequency changes are directly related to VCO frequency changes. Because the new offset frequency increased by 124.9 Hz, the VCO frequency also increased by 124.9 Hz. To find the VCO frequency, add the offset frequency to the frequency of the offset oscillator. This would be 1,280,124.9 Hz $\div$ 36,380,000, or 37,660,124.9 Hz. The normal output frequency of the VCO is 37,660,000 Hz, so the VCO is operating only 124.9 Hz too high. This difference will also show up in the transmit and receive frequencies.

The interesting point here is that even though the reference oscillator frequency changed by 1000 Hz, the VCO frequency only changed by 124.9 Hz. The change in VCO frequency is equal to the change in reference frequency multiplied by the N number programmed into the divider. The formula could be written out as:  $\Delta$  Fvco= $\Delta$  Fref×N. The main point to remember is that a change is in the reference oscillator frequency will also change the receive and transmit frequencies, but to a lesser degree.

If the frequency of the offset oscillator changes, then the VCO frequency will also change and by the same amount. Hence, the receive and transmit frequencies will change accordingly. If the transmit oscillator changes in frequency only, the transmit frequency will be affected.

By now you should have a basic understanding of PLL operation. The basic stages were covered individually and then analyzed as a system. The following chapters cover specific PLLs in detail and should serve to strengthen your understanding of PLLs in general.

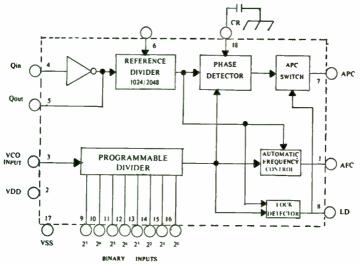

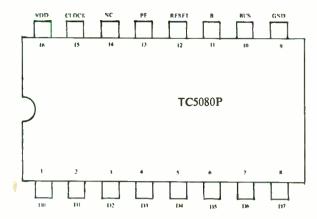

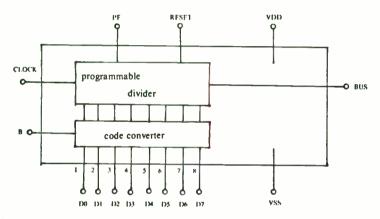

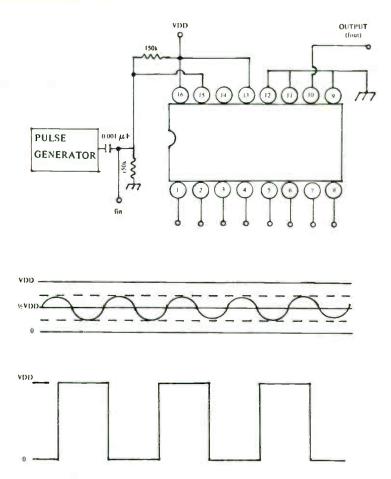

# Chapter 2 The $\mu$ PD2816C Digital Synthesizer

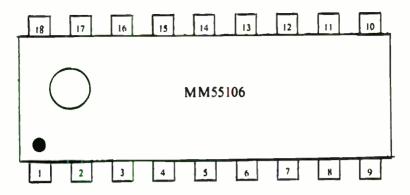

The  $\mu$  PD2816C is a CMOS LSI (large-scale integrated circuit) designed especially for CB PLL synthesizers. The IC is packaged in a 22-pin dual in-line package. First we will take a close look at the muPD2816C IC itself. A block diagram of a typical application will then be analyzed in detail. Then the Cobra 1000 GTL PLL synthesizer, which uses the muPD2816C, will be explained in detail. Adjustment and test procedures will be included also.

# SPECIAL FEATURES

Only one crystal required for CB 40-channel AM operation.

□ On-chip filter amplifier.

□ Buffered 10.240-MHz output.

□ Protection circuit for misprogramming and unlocked conditions.

□ BCD 6-bit input channel select code.

□ High-speed, low-power consumption due to CMOS.

□ Selectable reference frequency (5 kHz or 10kHz).

□ On-chip pullup resistors.

□ On-chip inverter which can be used for oscillator with external crystal.

# INTERNAL STRUCTURE

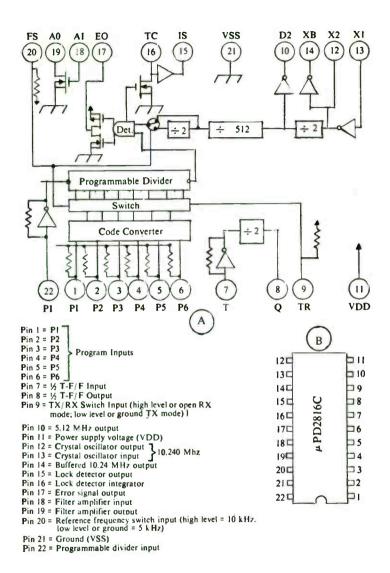

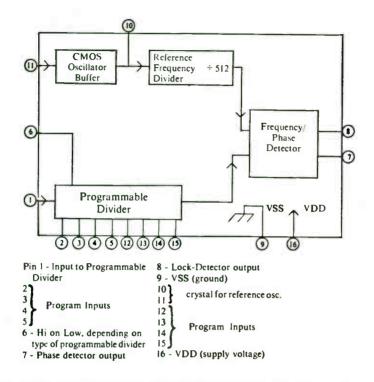

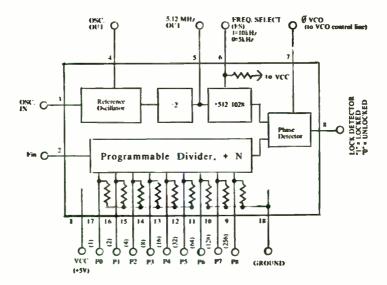

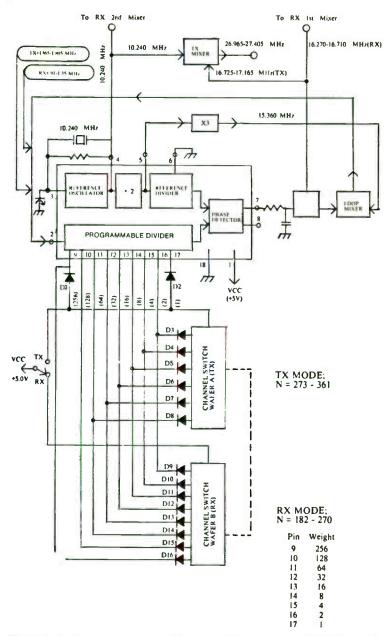

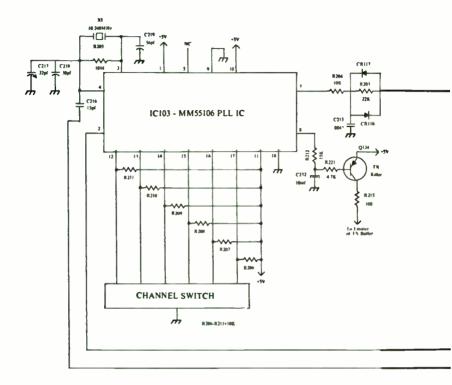

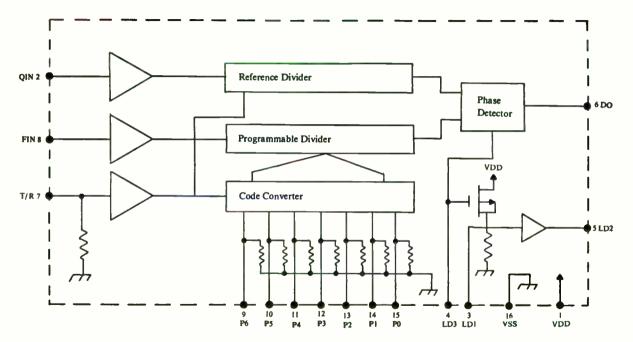

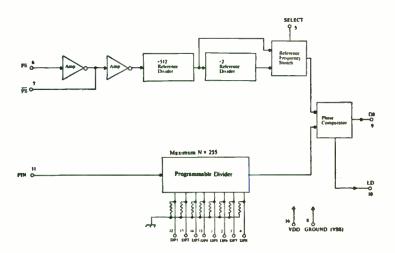

Figure 2-1A is a block diagram of the internal structure of the muPD2816C. The functions of the terminal pins are listed with

the illustration. Pins 1 through 6 are the programming inputs, P1 through P6. The programming is applied to these pins in BCD form. Pullup resistors are shown connected to the various program pins. These resistors are part of the IC itself. If one of the program pins is ungrounded, the pullup resistor places a HIGH level (binary 1) on the pin. This simplifies the design of the channel selector switch to some extent. The program lines connect internally to the code converter. The code converter converts the BCD code to another code which is applied through the switch to the programmable divider. This then sets the divider to divide by the appropriate divisor N.

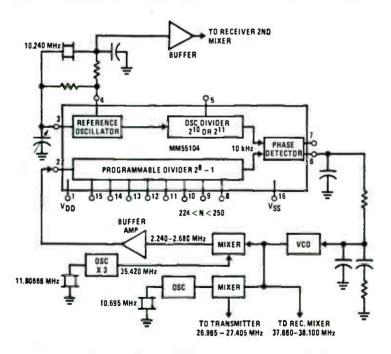

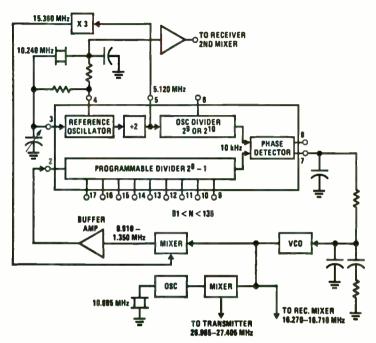

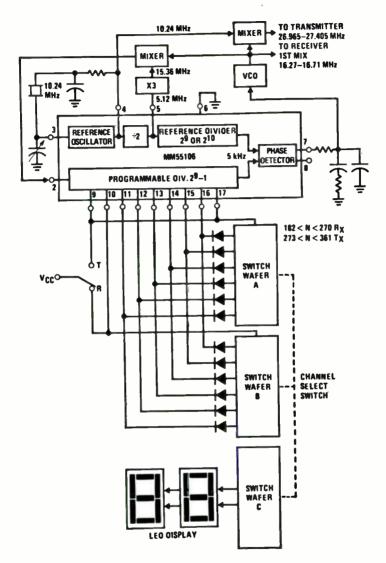

Pin 7 is the input to a divider which divides by 2. Pin 8 is the output of this divider. Pin 9 connects to the internal program switch. If pin 9 is open or at a HIGH level, the programmable divider will divide by N. If pin 9 is at ground potential, the programmable divider will divide by N + 91. The reason for this setup is that with this PLL system, the VCO frequency is not the same for the transmit and receive modes of operation. Pin 10 is connected to the output of a divider which divides the 10.240-MHz reference oscillator frequency by 2. Thus, the output of pin 10 is a 5.12-MHz signal. Pin 11 is connected to the supply voltage to power the IC. Pin 12 is the output of the 10.240-MHz oscillator. Notice that the output of the reference oscillator also feeds the input of a divider which divides it by 2. The output of the divide by 2 divider is then 5.12 M Hz. This is then divided by the divide by 512 divider to vield 10 kHz. This 10-kHz signal can be used for the reference frequency for the phase detector or if a 5-k Hz reference frequency is desired, the reference input of the phase detector is taken from the output of another divide by 2 divider, which divides the 10-k Hz signal by 2 to yield 5 k Hz. The reference input to the phase detector is determined by an electronic switch. This switch is drawn as a mechanical switch in the illustration for simplification. The voltage level applied to pin 20 determines whether the switch will connect the phase detector reference input to the 5-k Hz or the 10-k Hz terminal. If pin 20 is connected to a HIGH level or simply left open, the reference frequency will be 10 kHz. If pin 20 is grounded, the reference frequency will be 5 kHz.

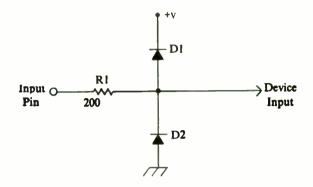

Pin 14 is a buffered 10.240-MHz output. Pin 15 serves to stop the transmitter if an unlocked condition exists. Pin 16 is used to connect an external RC network and supply voltage. The output of the lock detector is a series of pulses which are fed to the external integrator circuit through the MOS transistor. The integrated signal is then used to set the level at pin 15. Pin 17 is the error signal output from the charge pump. This error signal can be applied through external components to the input of the active filter amplifier at pin 18. The output of the active filter amplifier is brought out to pin 19. This DC voltage can then be used to control the VCO. Pin 21 is common or ground. Pin 22 is the input to the programmable divider. The pins are numbered as shown in Fig. 2-1B.

Table 2-1 shows the 40-channel codes that are applied to the programming inputs of the  $\mu$  PD2816C. Also shown at the bottom of the table are six input codes which are *not allowed*. Program lines P6 and P5 are used to represent the tens digit, and program lines P4, P3, P2, and P1 are used to represent the units digit. The weight of P6 is 2 and the weight of P5 is 1. The weights of P4 through P1 are P4=8, P3=4, P2=2, and P1=1. To find the decimal equivalent of the code add the weights of the pins where binary 1 appears. For example for channel 37 to get the tens position digit, P6 and P5 are at binary 1 so add their weights together:

P6 (weight) = 2 P5 (weight) =  $\frac{1}{2}$ Tens digit = 3

P3, P2, and P1 are at binary 1 so add the weights of these positions to get the units digit.

P1 (weight) = 1 P2 (weight) = 2 P3 (weight) =  $\frac{4}{7}$ Units digit = 7

So we have the tens digit of 3 and the units digit of 7. One exception to this is channel 40. On channel 40, all the program lines are LOW (binary 0). The code converter recognizes this as channel 40. This simplifies the programming.

Notice at the bottom of the chart that there are six program codes for P4 through P1 which are not allowed. If these codes appear on the program lines P4 through P1, the level at the lock detector output (IS) will go low. This is used to kill the transmitter to prevent out-of-band signal radiation.

Fig. 2-1. Block diagram of the internal structure of the  $\mu$  PD2816C is shown at A. The drawing at B is a top view of the  $\mu$  PD2816C showing pin numbering. The functions of the various pins are listed.

#### World Radio History

Table 2-1. Program Codes, VCO Frequencies, and Divisors.

|          | D  |      |        | Im |     | 3    | _          |                        |            | actiones, att          |            |                |     |

|----------|----|------|--------|----|-----|------|------------|------------------------|------------|------------------------|------------|----------------|-----|

| Chan.    | P  | rogi | am     | In | out |      |            | = 1(Rx)                |            | = 0(Tx)                |            | TR = I IS      |     |

| Che      |    |      |        | Un | its |      |            | = 0 (5 kHz)<br>/CO Fr. |            | = 0 (5 kHz)<br>'CO Fr. |            | FS = 1 (10 kH; | 7.) |

|          | Pe | P5   | P4     |    |     | 2 PI | 14         | VCO FI.                | IN V       | CU Fr.                 |            | N VCO Fr.      |     |

| 1        | 0  | 0    | 0      | 0  | 0   | 1    | 182        | 16.27 MHz              | 273        | 16.725 MHz             | 10         | 16.27 MHz      | t   |

| 2        | 0  | 0    | 0      | 0  | 1   | 0    | 184        | .28                    | 275        | .735                   | 92         | .28            | i.  |

| 3        | 0  | 0    | 0      | 0  | 1   | 1    | 186        | .29                    | 277        | .745                   | 93         | .29            | i   |

| 4        | 0  | 0    | 0      | 1  | 0   | 0    | 190        | .31                    | 281        | .765                   | 95         | .31            | i   |

| 5        | 0  | 0    | 0      | 1  | 0   | 1    | 192        | .32                    | 283        | .775                   | 96         |                | i   |

| 6        | 0  | 0    | 0      | 1  | 1   | 0    | 194        | .33                    | 285        | .785                   | 97         |                | 1   |

| 7        | 0  | 0    | 0      | 1  | 1   | 1    | 196        | .34                    | 287        | .795                   | 98         |                | I   |

| 8        | 0  | 0    | 1      | 0  | 0   | 0    | 200        | .36                    | 291        | .815                   | 100        |                | 1   |

| 9        | 0  | 0    | 1      | 0  | 0   | T    | 202        | .37                    | 293        | .825                   | 101        |                | 1   |

| 10       | 0  | 1    | 0      | 0  | 0   | 0    | 204        | .38                    | 295        | .835                   | 102        |                | 1   |

| 11       | 0  | 1    | 0      | 0  | 0   | 1    | 206        | .39                    | 297        | .845                   | 103        |                | i   |

| 12       | 0  | I    | 0      | 0  | 1   | 0    | 210        | .41                    | 301        | .865                   | 105        |                | 1   |

| 13       | 0  | 1    | 0      | 0  | 1   | 1    | 212        | .42                    | 303        | .875                   | 106        |                | i   |

| 14       | 0  | 1    | 0      | 1  | 0   | 0    | 214        | .43                    | 305        | .885                   | 107        |                | 1   |

| 15       | 0  | 1    | 0      | 1  | 0   | 1    | 216        | .44                    | 307        | .895                   | 108        |                | i   |

| 16       | 0  | 1    | 0      | 1  | 1   | 0    | 220        | .46                    | 311        | .915                   | 110        |                | 1   |

| 17       | 0  | I.   | 0      | 1  | 1   | 1    | 222        | .47                    | 313        | .925                   | 111        |                | 1   |

| 18       | 0  | 1    | 1      | 0  | 0   | 0    | 224        | .48                    | 315        | .935                   | 112        | .48            | 1   |

| 19       | 0  | 1    | 1      | 0  | 0   | 1    | 226        | .49                    | 317        | .945                   | 113        | .49            |     |

| 20       | 1  | 0    | 0      | 0  | 0   | 0    | 230        | .51                    | 321        | .965                   | 115        | .51            | 1   |

| 21       | 1  | 0    | 0      | 0  | 0   | 1    | 232        | .52                    | 323        | .975                   | 116        | .52 1          | 1   |

| 22       | 1  | 0    | 0      | 0  | 1   | 0    | 234        | .53                    | 325        | .985                   | 117        | .53            | 1   |

| 23       | 1  | 0    | 0      | 0  | 1   | 1    | 240        | .56                    | 331        | 17.015                 | 120        | .56 1          | l   |

| 24       | 1  | 0    | 0      | 1  | 0   | 0    | 236        | .54                    | 327        | 16.995                 | 118        | .54 1          | 1   |

| 25       | 1  | 0    | 0      | 1  | 0   | 1    | 238        | .55                    | 329        | 17.005                 | 119        | .55 1          | 1   |

| 26<br>27 | 1  | 0    | 0      | 1  | 1   | 0    | 242        | .57                    | 333        | .025                   | 121        | .57 1          |     |

| 28       | 1  | 0    | 0<br>1 | 1  | 0   | 1    | 244        | .58                    | 335        | .035                   | 122        | .58 1          |     |

| 29       | 1  | 0    | 1      | 0  | 0   | 1    | 246<br>248 |                        | 337        | .045                   | 123        | .59 1          |     |

| 30       | i  | ĩ    | 0      | 0  | 0   | 0    | 240        |                        | 339        | .055                   | 124        | .60 1          |     |

| 31       | 1  | i    | õ      | õ  | 0   | 1    | 250        |                        | 341        | .065                   | 125        | .61 1          |     |

| 32       | î. | ī    | ŏ      | õ  | 1   | ò    | 254        |                        | 343<br>345 | .075                   | 126        | .62 1          |     |

| 33       | i  | i    | ŏ      | õ  | i   | 1    | 256        |                        | 345<br>347 | .085<br>.095           | 127        | .63 1          |     |

| 34       | 1  | ī    | ŏ      | 1  | 0   | 0    | 258        |                        | 347<br>349 |                        | 128        | .64 1          |     |

| 35       | i  | i    | ŏ      | 1  | õ   | 1    | 260        |                        | 351        |                        | 129        | .65 1          |     |

| 36       | ī  | i    | ŏ      | i  | ĩ   | ò    | 262        |                        | 353        |                        | 130<br>131 | .66 1<br>.67 1 |     |

| 37       | i  | 1    | Õ      | i  | 1   | 1    | 264        |                        | 355        |                        | 131        | .67 I<br>.68 I |     |

| 38       | 1  | 1    | 1      | 0  | 0   | 0    | 266        |                        | 357        |                        | 133        | .69 1          |     |

| 39       | 1  | 1    | 1      | 0  | 0   | 1    | 268        |                        | 359        |                        | 134        | .70 1          |     |

| 40       | 0  | 0    | 0      | 0  | 0   | 0    | 270        |                        | 361        |                        | 135        | .71 1          |     |

|          |    |      | 1      | 0  | 1   | 0    |            |                        |            |                        | 100        | 0              |     |

|          |    |      | 1      | 0  | 1   | 0    |            |                        |            |                        |            | 0              |     |

|          |    |      | 1      | 1  | 0   | 0    |            |                        |            |                        |            | 0              |     |

|          |    |      | 1      | 1  | 0   | 1    |            |                        |            |                        |            | Ő              |     |

|          |    |      | 1      | 1  | 1   | 0    |            |                        |            |                        |            | Ő              |     |

|          |    |      | 1      | 1  | 1   | I –  |            |                        |            |                        |            | 0              |     |

|          |    |      |        |    |     |      |            | low level (1           |            |                        |            |                |     |

|          |    |      |        |    |     |      | 1 =        | high level (           | binar      | y 1)                   |            |                |     |

|          |    |      |        |    |     |      |            |                        |            |                        |            |                |     |

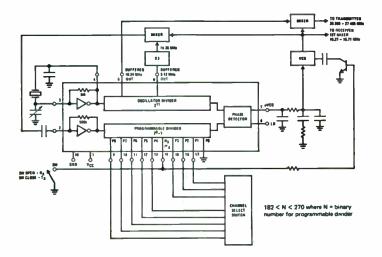

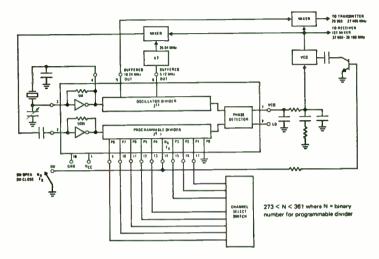

Notice that the first column (where TR=1 and FS=0) lists the N numbers and the VCO frequencies. When TR=1, this is the receive mode. The transmit mode is when TR=0. Where FS=0, the reference frequency is 5 kHz. If FS = 1, the reference frequency is 10 kHz. The first column lists the N numbers (divisors) and the VCO frequencies for the receive mode where the reference frequency is 5 kHz. The third column lists the N divisors and the VCO frequencies where the reference is 10 kHz (receive mode).

Notice that where 5 kHz is used as the reference frequency the N numbers increase by 2 for each incremental channel change. This is because the CB channel spacing is 10 kHz. Because the reference frequency is only half that frequency, the N will have to be changed by 2 when switching between channels separated by 10 kHz. The spacing between channels 3 and 4 is 20 kHz, so the N number would have to change by 4 when switching between 3 and 4. There is also a 20-k Hz separation between CB channels 7 and 8, 11 and 12, 15 and 16, and 19 and 20. You will notice on the chart that the N divisors change by 4 when switching between these channels. Also, between channels 22 and 23 there is a 30-kHz separation, so switching between these channels requires the N number to change by 6. The new channels, 24 and 25, were placed between 22 and 23. You can see in column 1 of Table 2-1 that the N divisor for channel 22 is 234 and for channel 23 is 240. On channel 24. the N number goes back to 236 and for channel 25 is 238. There is another 20-kHz jump between channels 25 and 26, but channel 23 fits between channels 25 and 26.

The third column in Table 2-1 is based on a reference frequency of 10 kHz. The column shows the various N values and VCO frequencies for the receive mode. Notice that the N numbers are consecutive, except where odd channel spacing exists. This is because the reference frequency is the same as the channel spacing -10 kHz.

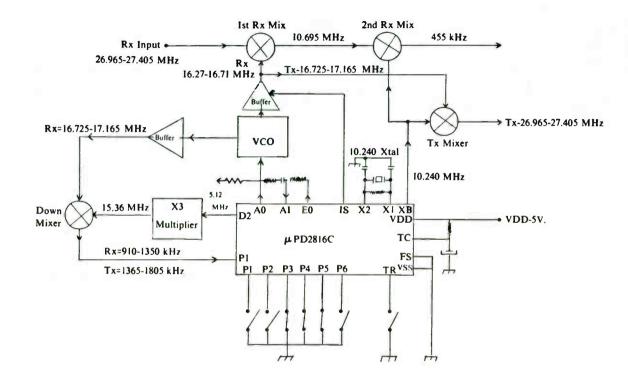

# A TYPICAL APPLICATION

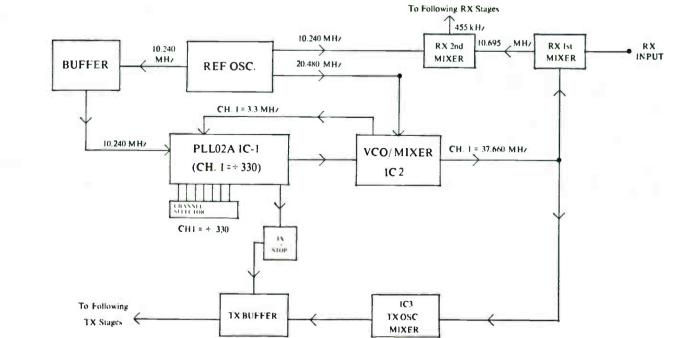

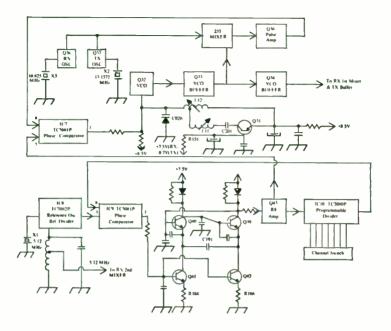

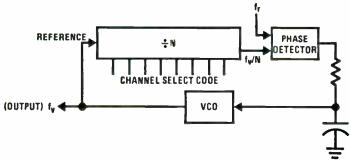

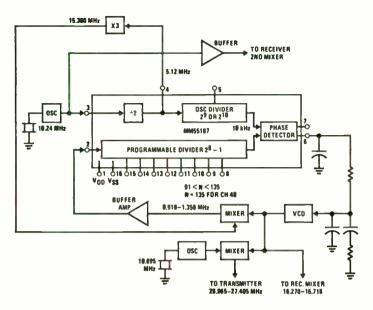

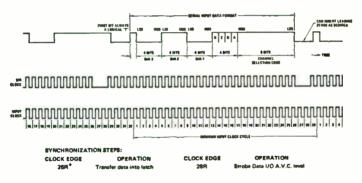

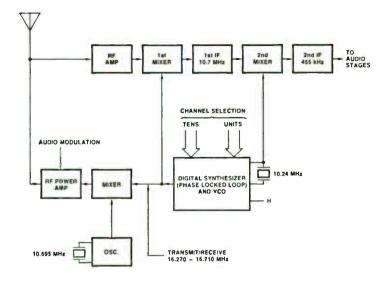

Figure 2-2 shows a block diagram of a theoretical application of the  $\mu$  PD2816C. Let's analyze the operation of the system using channel 23 as the example. The program lines (P1 through P6) are connected to switches that can either ground the program line or leave it open. The line is at binary 0 when grounded. If the line is left open, the internal pullup resistor will place the line at a H1GH level or binary 1. The switches are shown as being set up for channel 23. And for channel 23, the code converter sets the divider

Fig. 2-2. This is a block diagram of a typical application of the  $\mu$  PD2816C.

30

to divide by 240 in the receive mode. For the transmit mode, the divider will be set up to divide by 331. Notice that FS is grounded so this sets the reference frequency at 5 kHz. In the receive mode, the VCO frequency is mixed with the incoming receive signal to produce a difference frequency of 10.695 MHz. This is the first intermediate frequency. This 10.695-MHz i-f is then sent to the *second mixer* where it is mixed with the signal from the buffered 10.240-MHz output (XB) of the 1C. The difference of these two signals (10.695-10.240 = 455 kHz) is the low intermediate frequency. In the transmit mode, the VCO frequency is mixed with a 10.240 MHz signal (from the XB terminal of the 1C) to produce a sum frequency that is the transmit signal.

The VCO frequency is mixed with a 15.360-MHz signal to produce a difference output which the programmable divider can handle. Notice the switch connected to the TR terminal of the lC. In the receive mode, the switch is open and the divider is set to divide by N. When the switch is closed, TR is grounded. This changes the divisor to N + 91.

The frequency of 27.255 MHz is CB channel 23. To receive this signal, the VCO frequency will have to be 27.255-10.695 (first i-f), or 16.560 MHz (see Table 2-1). The VCO frequency is mixed with a 15.360-MHz signal in the down mixer to produce the frequency 16.560-15.360, or 1.200 MHz. This 1.200-MHz signal is sent to the programmable divider where it is divided by 240 to yield 5 kHz. Because the output of the divider is equal to the reference frequency, no correction voltage will be issued so the VCO frequency remains constant. Notice that the error signal output, EO, is fed to the input of the filter amplifier, A1. The control voltage for the VCO is taken from the output of the filter amplifier, AO.

In the transmit mode, the TR terminal of the 1C is grounded when the transmitter is keyed. This can be done through the microphone switch, through relay contacts, or by an electronic switch. Regardless of how this is achieved, when TR is grounded, the divisor of the programmable divider is increased by 91. In the channel 23 receive mode, the divisor is 240. In the transmit mode, therefore, the divisor becomes 240+91, or 331. At the instant the transmitter is keyed, the VCO frequency will still be 16.560 MHz. Therefore, the input to the divider will be 1.200 MHz+331, or 3.625 kHz. Thus, a large error now exists between the divider output frequency and the 5-kHz reference frequency. The phase detector detects this error and produces a corresponding error signal. This error signal is amplified and filtered by the filter amplifier and then applied to the control line of the VCO. This error signal causes the VCO frequency to gradually increase. As the VCO frequency increases, the output of the programmable divider will move closer and closer to 5 kHz. When the output of the programmable divider reaches 5 kHz, the phase detector produces no more error signal. Hence, the VCO frequency stabilizes. The new VCO frequency is now 17.015 - 15.360, or 1.655 MHz. This is in turn divided by 331 to yield 5 kHz.

To obtain the transmit frequency, the VCO frequency is mixed with the 10.240-MHz signal: 17.015 MHz + 10.240 MHz = 27.255 MHz. When the transmitter is first keyed, a finite amount of time is required for the VCO frequency to reach and stabilize at the new frequency. During this time interval, the PLL is unlocked. The lock detector detects this unlocked condition and issues a signal that kills the transmitter output. In Fig. 2-2, this signal is fed from IS to the buffer to kill the buffer stage. This in turn kills the transmitter output. This prevents improper signal radiation from the transmitter. When the VCO reaches the correct frequency, the PLL will lock. The lock detector output will then return to normal and thus enable the transmitter. Actually, it only requires a small fraction of a second for the PLL to lock.

When the transmitter is unkeyed, the programmable divider will revert to the divisor 240. Momentarily, the VCO will still be operating at 17.015 MHz. The input to the divider will still be 1.655 MHz. The output of the divider will be 1.655 MHz $\div$ 240, or 6.896 kHz. This is quite higher than the 5-kHz reference, and the phase detector detects this and produces an error signal that is filtered and then applied to the control line of the VCO. This error signal causes the VCO frequency to decrease. As it decreases, the output of the programmable divider approaches the 5-kHz reference frequency. When the output frequency of the divider reaches 5 kHz, the phase detector produces no more error signal, so the VCO stabilizes. The VCO is now back at 16.560 MHz.

# **COBRA 1000 GTL CB SYNTHESIZER**

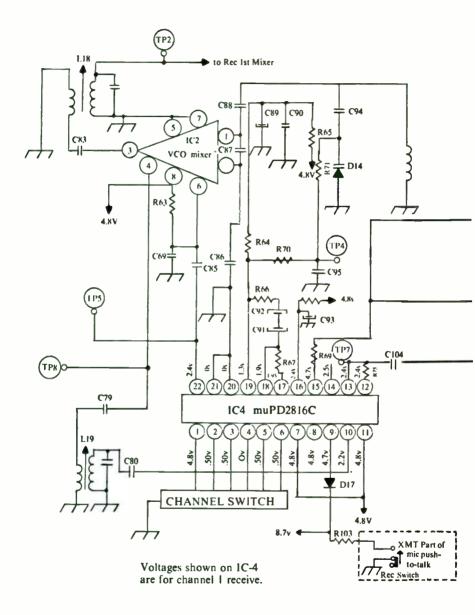

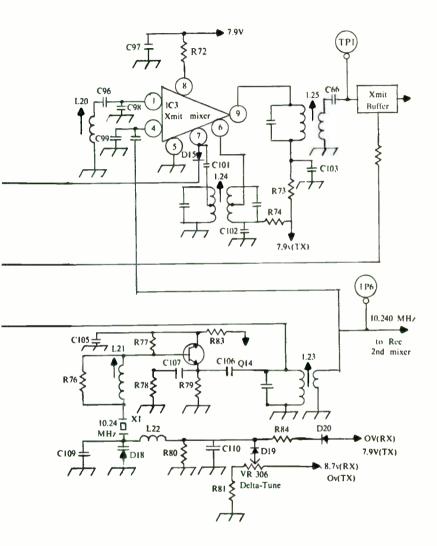

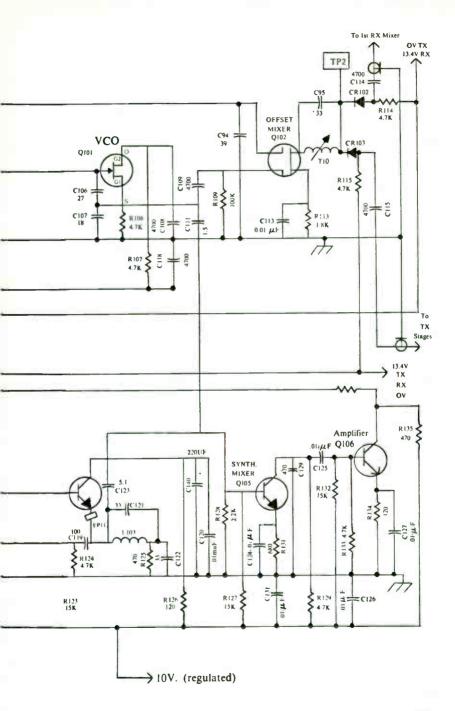

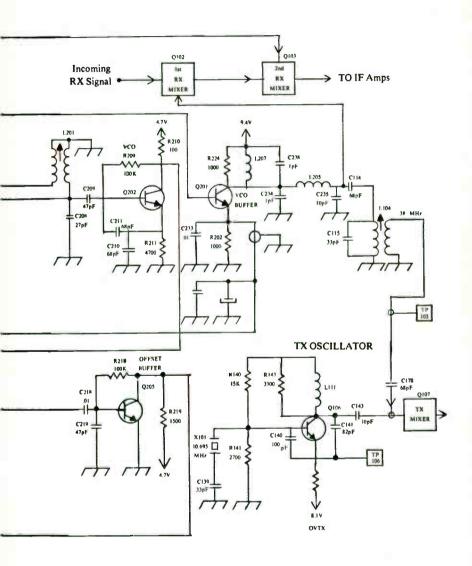

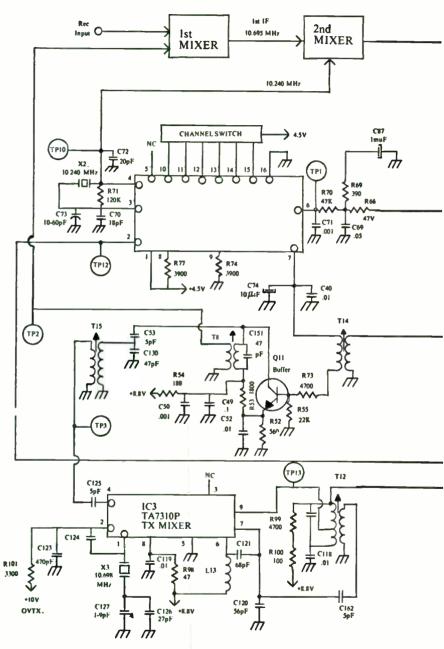

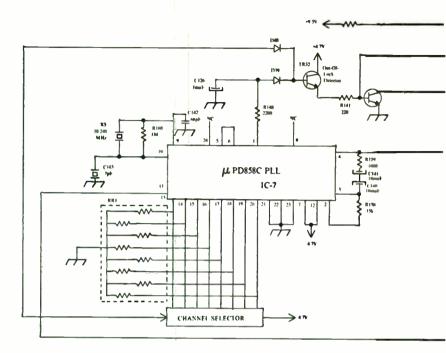

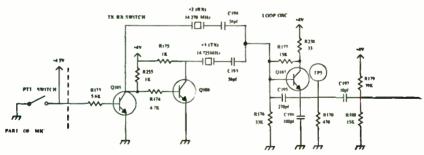

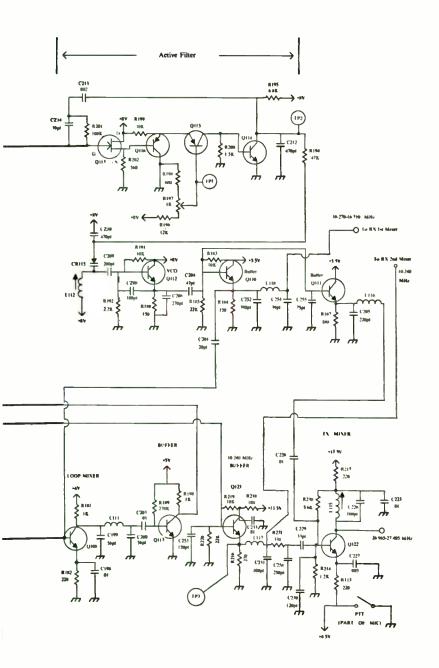

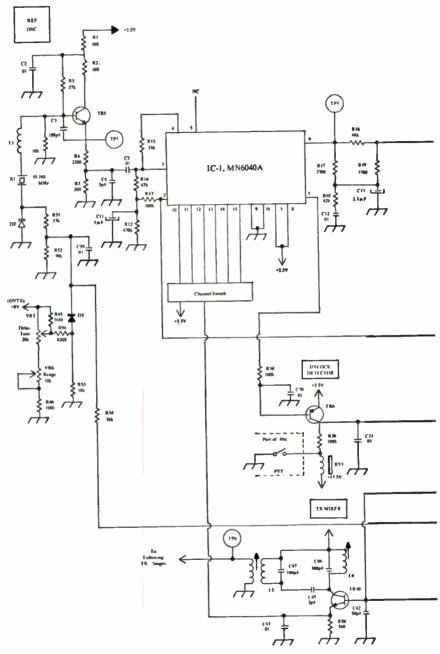

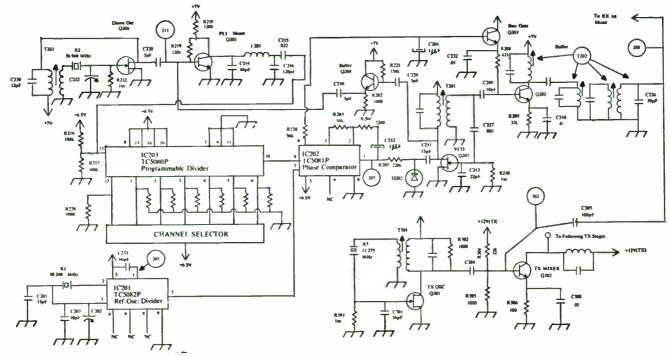

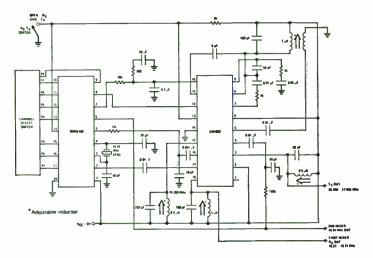

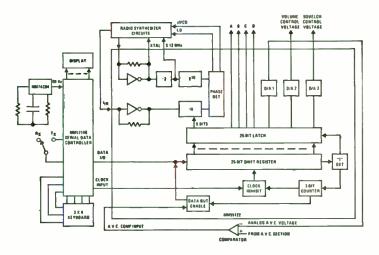

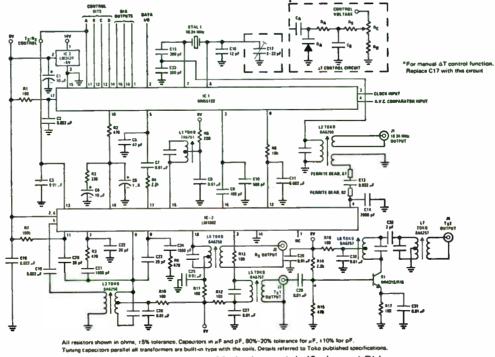

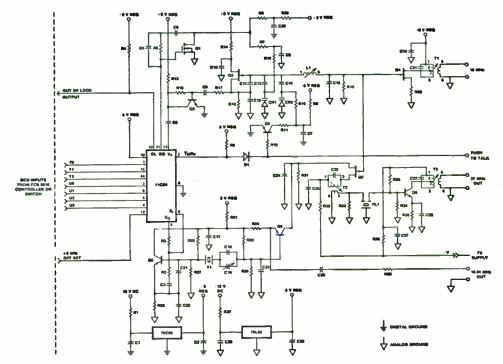

The Cobra 1000 GTL is pictured in Fig. 2-3. The digital synthesizer circuit of the Cobra 1000 GTL is built around the  $\mu$  PD2816C IC. During this discussion, refer to the schematic in Fig. 2-4. Also, Table 2-1 will be referred to in this discussion.

Remember that the  $\mu$  PD2816C can have a reference frequency of 5 kHz or 10 kHz, depending on the voltage level at pin 20. If pin 20 is grounded, the reference frequency is 5 kHz. If pin 20

Ĩ

Fig. 2-3. The Cobra 1000 GTL Transceiver.

is high, the reference frequency is 10 kHz. On the schematic, pin 20 is connected to ground, so this sets the reference frequency at 5 kHz. The reference oscillator operates at 10.240 MHz. This oscillator consists of transistor TR14 and the associated circuitry. The frequency of the oscillator is determined primarily by crystal X1 which resonates at 10.240 MHz. Inductor L21 is used to set the oscillator precisely on frequency.

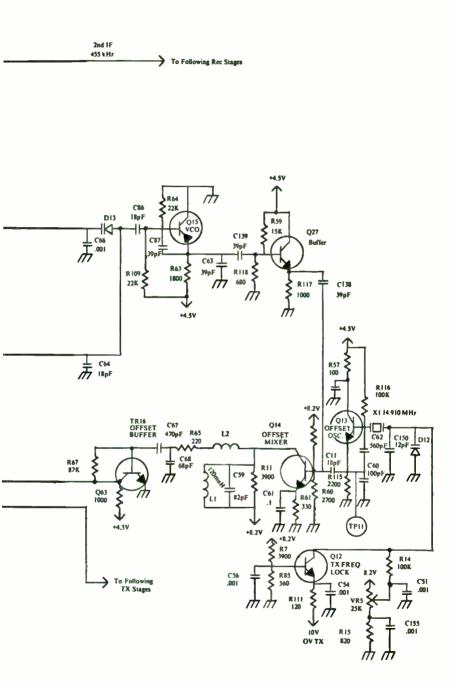

Also, notice varactor diode D18. This is shown connected from one side of crystal XI to ground. The varactor serves as a fine tuning control. In the receive mode, diode D19 is forward biased. This allows the voltage at the arm of the delta-tune control (VR306) to appear across the varactor diode, D18. This voltage reverse biases the varactor. As the delta-tune control is varied, the reverse bias across D18 also varies. Hence, the capacitance exhibited by D18 varies. The changing capacitance of D18 will change the oscillator frequency. This can improve the reception of off-frequency signals. In the transmit mode, it is undesirable for the delta-tune control to affect the oscillator frequency. Otherwise, the transmitter would be operating off frequency. This is illegal, of course! So in the transmit mode, 7.9 volts is applied to the anode of diode D20. This sets up a current flow from ground through R80, R84, and D20 back to the 7.9-volt supply. Resistors R80 and R84 form a voltage divider. The voltage at the junction of R80 and R84 will be approximately 3.5 volts. This will set a fixed reverse bias across the varactor. Also, the supply voltage in the transmit mode is removed from the delta-tune control, so D19 will be reverse biased. This isolates the delta-tune control from the circuit.

The 10.240-MHz signal that is developed by the reference oscillator is fed to pin 13 of 1C4. This signal is divided by 2048 to yield a 5-kHz reference signal at the reference input of the phase detector.

The voltage-controlled oscillator consists of part of IC2, along with the external components. The components that determine the resonant frequency of the VCO are L20, C94, and, of course, the varactor diode, D14. The VCO designed to operate in the 16 to 17 MHz range. The exact frequency is determined by the control voltage fed from pin 19 of 1C4 through resistors R70 and R71 to the anode of the varactor, D14.

From a previous discussion on the  $\mu$  PD2816C, you learned that a 5.12-MHz signal is available at pin 10 of IC4. Figure 2-4 shows that L19 is connected to pin 10 through capacitor C80. The primary of L19 is tuned to 15.360 MHz (the third harmonic of 5.12 MHz). The secondary of L19 feeds this 15.360-MHz signal to one input of the VCO/mixer, pin 4 of IC2. Inside IC2, the 15.360-MHz signal is mixed with the VCO frequency to yield FVCO -15.360 MHz, or FPDI, where FVCO is the VCO frequency and FPDI is the programmable divider input frequency.

The operation of the entire PLL circuit using channel 1 as the example, is next. In the receive mode on channel 1, the programmable divider is set to divide its input frequency by 182. To yield a 5-kHz signal at the output of the programmable divider, the input to the divider will have to be  $5000 \times 182$ , or 910.000 Hz or 0.910MHz. By the formula, then, the VCO frequency would have to be FVCO = 15.360 + FPD1 = 15.360 + 0.910, or 16.270 MHz. The difference frequency of 0.910 MHz is taken from pin 6 of IC2 and fed to the input of the programmable divider at pin 22 of IC4. The frequency at the input of the programmable divider varies directly as the VCO frequency varies. On channel 1, if the input to the programmable divider is not exactly 0.910 MHz, an error signal will appear at the output of the phase detector. This error signal will be amplified, filtered, and then applied to pin 19 of 1C4. This error signal will change the control voltage applied across varactor diode D14. This will in turn move the VCO frequency until the input to the divider is exactly 0.910 MHz. When the input to the divider is exactly 0.910 MHz, the phase detector will produce no more error signal. Thus, the control voltage stabilizes at a level that keeps the VCO at 16.270 MHz and consequently the input to the programmable divider at 0.910 MHz.

The VCO frequency is taken from pin 3 of IC2. From pin 3,

the signal is fed through L18 to the receiver first mixer where it is heterodyned with the incoming channel 1 signal to yield 26.965 MHz - 16.270 MHz, or 10.695 MHz. This 10.695-MHz signal is the first i-f. This first i-f signal is then mixed with a 10.240-MHz signal which is taken from the secondary of L23. The difference frequency is 10.695 MHz - 10.240 MHz, or 455 kHz. This is the second intermediate frequency.

In the transmit mode, the VCO is made to operate at a frequency which is 455 kHz higher than the receive mode frequency. For channel 1, the VCO frequency would therefore be 16.725 MHz. Let's see how this change in VCO frequency is accomplished. When the transmitter is keyed, a set of contacts on the push-to-talk switch is used to ground pin 9 of 1C4 through a 2.2ohm resistor (R103) and diode D17. When pin 9 of IC4 goes low, the divisor of the programmable divider increases by 91. The divisor in the receive mode was 182, so the divisor for the transmit mode will be 182 + 91, or 273. So the input to the programmable divider must be  $5000 \times 273$ , or 1.365 MHz. Notice that this is a 455kHz increase over the receive mode divider input frequency.

When the transmitter is first keyed, a large difference will exist in the output frequency of the programmable divider and the 5-kHz reference frequency. The phase detector issues a large error signal. As a result, a correction voltage is applied to the VCO control line. This causes the VCO frequency to move upward until the frequency at the input of the programmable divider reaches 1.365 MHz. When the input to the divider is 1.365 MHz, the output of the programmable divider will be 5 kHz. Because this is the same as the reference frequency, the phase detector will not produce an error signal now. This allows the voltage on the control line of the VCO to stabilize the vco at 1.365 + 15.360, or 16.725 MHz.

A sample of the VCO frequency is taken from the secondary of L20 and fed to pin 1 of IC3 (transmit mixer). Also, a 10.240 MHz signal from the reference oscillator is fed to pin 4 of IC3. The sum of these two frequencies is taken from pin 9. The frequency at pin 9 for channel 1 is 10.240 MHz + 16.725 MHz, or 26.965 MHz. This signal is fed through L25 on to the buffer stage.

When an out-of-lock condition exists, pin 15 of IC4 will go LOW. This will kill transmit buffer stage TR 12. Also, a misprogramming condition will cause the lock detector output to go LOW. By measuring the voltage at pin 15, you can immediately tell whether the PLL is locked or unlocked. This is an important troubleshooting clue.

#### Alignment

□ With an rf voltmeter connected to TP6, adjust L23 for maximum indication on the meter. Make this adjustment with the channel selector on channel 20.

□ Connect a frequency counter to pin 13 of IC4 and check the accuracy of the 10.240-MHz reference frequency. Make sure that the delta-tune control is in the center or detent position. Also, check this frequency in the transmit mode. There should be very little difference in frequency in the transmit and receive modes of operation.

□ With the set on channel 40, monitor the DC voltage at TP4. Adjust L20 for 2.1 volts. On channel 1, the voltage should be approximately 1.3 volts. Make this adjustment very carefully, because this is a fairly critical adjustment.

□ With an rf voltmeter connected to pin 4 of IC2, adjust L19 for maximum indication on the meter. Then, using a frequency counter, check for 15.360 MHz at pin 4 of IC2.

□ With a frequency counter connected to TP5 (pin 22 of IC4), check on all channels for the frequencies shown in Table 2-2. Check this in the receive and transmit modes of operation.

$\Box$  With an rf voltmeter connected to TP2, adjust L18 for maximum indication on the meter.

Using a frequency counter, check TP2 for the proper VCO frequencies on all channels. Check this in the receive and the transmit modes. Refer to Table 2-1 for the proper frequencies for all 40 channels.

□ With an rf voltmeter connected to TP1, adjust 124 and 125 for maximum indication on the meter.

Using a counter, check for the proper transmit frequencies at the transmitter output.

#### **Troubleshooting Hints**

There are two test points that tell quite a lot about the condition of the PLL. These are the lock detector/misprogramming detector output and the VCO control line voltage at TP4.

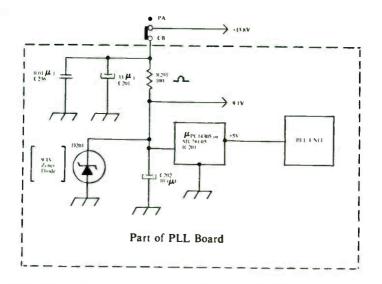

If the voltage at pin 15 of IC4 is normal, this indicates that the PLL is locked and operating. But the VCO frequency could still be wrong even with a locked condition. For example, if the 15.360-MHz signal were off frequency, the VCO would be forced to operate off frequency to maintain the proper input frequency at the programmable divider. If the voltage at pin 15 of IC4 is low, this is an indication that either the loop is unlocked or that im-

proper programming is applied to the program inputs.

If the control line voltage at TP4 is abnormally high or low, this indicates that the VCO frequency is wrong or missing altogether. This could also indicate that the reference (10.240-MHz) signal is wrong or missing. Also if the 15.360-MHz signal is wrong or missing, the voltage at TP4 will be abnormal. Infact, almost any trouble within the loop will affect the voltage at TP4, so you can see how important it is to check here first when troubleshooting this PLL circuit.

No Transmit or Receive On Any Channel. Check for the presence of rf voltage at TP2 (output of VCO). If there is no rf voltage at TP2, troubleshoot the VCO. If there is rf voltage at TP2 check the frequency with a frequency counter just to verify that it is in the 16 to 17 MHz range. If so, check for the 15.360-MHz signal at TP8. If this frequency is wrong or missing, check the reference oscillator signal at TP7. If the 15.360-MHz signal is present at TP8, check for rf voltage at TP5. The frequency at TP5 should be equal to the VCO frequency minus 15.360 MHz. Check to see that it is. If not, check the VCO/mixer stage.

Providing everything else checks OK, a VCO adjustment might be all that is needed. If L20 is badly out of adjustment, the voltage at TP4 will be either abnormally high (near 4.8 volts) or abnormally low (near 0.5 volts). With the set on channel 1, monitor the DC voltage at TP4 while carefully adjusting L20. If, after a few turns in one direction, the voltage at TP4 does not change, turn the slug in the opposite direction. After a few turns or less, the voltage at TP4 should start to change. When it does, adjust it to 1.3 volts on channel 1. If the voltage at TP4 does not change, then there might be a defect in the  $\mu$  PD2816C itself. In this case you would need to return L20 to its original setting.

No Operation On High Channels With Low Channels OK. This is almost always caused by misadjustment of the VCO. Refer to the third step under ALIGNMENT.

No Operation On Low Channels With High Channels OK. This is almost always caused by misadjustment of the VCO. Refer to the third step under ALIGNMENT.

Weak Receive, Off-Frequency Transmit On All Channels. With this condition, the VCO frequency is not correct, but the fault does not lie with the VCO itself. The 10.240-MHz oscillator is usually to blame for this problem. Suppose that the actual fre-

Fig. 2-4. A schematic of the PLL circuit used in the Cobra 1000 GTL.

Table 2-2. Correct Frequencies for Test Point 5 in the Cobra 1000 GTL PLL Synthesizer.

| Channel  | Frequency At TP5<br>RX MODE    | Frequency At TP5<br>TX MODE |

|----------|--------------------------------|-----------------------------|

| 1        | .91 MHz                        | 1.365 MHz                   |

| 2        | .92 "                          | 1.375 "                     |

| 3        | .93 "                          | 1.385 "                     |

| 4        | .95 "                          | 1.405 "                     |

| 5        | .96 ″                          | 1.415 "                     |

| 6        | .97 ″                          | 1.425 "                     |

| 7        | .98 ″                          | 1.435 "                     |

| 8        | 1.00 MHz                       | 1.455 "                     |

| 9        | 1.01 ″                         | 1.465 "                     |

| 10       | 1.02 ″                         | 1.475 ″                     |

| 11       | 1.03 ″                         | 1.485 ″                     |

| 12       | 1.05 ″                         | 1.505 "                     |

| 13       | 1.06 "                         | 1.515 "                     |

| 14       | 1.07 "                         | 1.525 "                     |

| 15       | 1.08 "                         | 1.535 "                     |

| 16       | 1.10 "                         | 1.555 "                     |

| 17       | 1.11 "                         | 1.565 "                     |

| 18       | 1.12 ″                         | 1.575 "                     |

| 19       | 1.13 "                         | 1.585 "                     |

| 20       | 1.15 "                         | 1.605 "                     |

| 21       | 1.16 "                         | 1.615 "                     |

| 22       | 1.17 "                         | 1.625 "                     |

| 23       | 1.20 "                         | 1.655 "                     |

| 24       | 1.18 "                         | 1.635 "                     |

| 25       | 1.19 "                         | 1.645 "                     |

| 26       | 1.21 "                         | 1.665 "                     |

| 27       | 1.22 "                         | 1.675 "                     |

| 28<br>29 | 1.23 "                         | 1.685 "                     |

| 30       | 1.24 <i>"</i><br>1.25 <i>"</i> | 1.695 "                     |

| 31       | 1.26 "                         | 1.705 "                     |

| 32       | 1.27 "                         | 1.715 "                     |

| 33       | 1.28 "                         | 1.725 "                     |

| 34       | 1.29 "                         | 1.735 "                     |

| 35       | 1.30 "                         | 1.745 "                     |

| 36       | 1.31 "                         | 1.755 ″<br>1.765 ″          |

| 30       | 1.32 "                         | 1.765 "                     |

| 38       | 1.32                           | 1.785 "                     |

| 39       | 1.34 "                         | 1.795 "                     |

| 40       | 1.35 "                         | 1.805 "                     |

|          |                                |                             |

quency of the reference oscillator is 10.242 MHz. This would then make the reference frequency at the phase detector 10.242 MHz + 2048, or 5,000.9 Hz. So the phase detector reference frequency changed by less than 1 Hz. Obviously, this won't have much effect on the VCO frequency, but the frequency at TP8 will no longer be 15.360 MHz. Instead, it will be  $\frac{10.242 \cdot 3}{2}$ , or 15.363 MHz. This will cause the VCO frequency to operate 3000 Hz higher in order for the frequency at TP5 to remain unchanged.

When this condition is present, your first step should be to check the reference frequency at TP6 with a frequency counter. If the frequency is wrong, adjust or repair the 10.240-MHz reference oscillator.

Some Channels Inoperative. Check the voltage levels at the program pins 1 through 6 on IC4. If these levels don't correspond with those shown in Table 2-1 for the selected channel, the problem must be in the channel selector switch or a short or open on the program lines. If none of these conditions are present, the  $\mu$  PD2816C itself might be at fault.

Some Channels Intermittent. Check the channel selector switch. Clean it with a good tuner cleaner if needed. If necessary, replace the channel switch.

No Transmit With Receive OK. Check the transmit mixer stage (1C3). Check to see if pin 9 of IC4 is low when the transmitter is keyed. If not, check the keying circuit and diode D17.

No Receive With Transmit OK. Check for proper VCO frequency at TP2 and at the first mixer stage. Check the voltage at pin 9 of IC4. It should be around 4.7 volts in the receive mode.

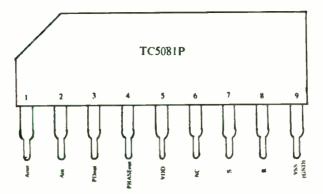

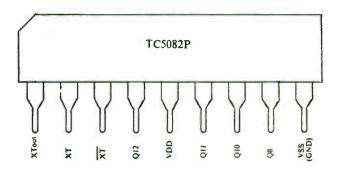

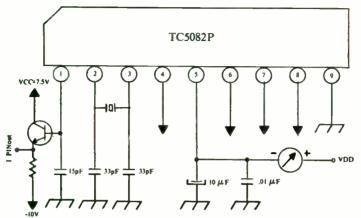

## Chapter 3 Chapter 3 The SC42502P/ 3001-201Digital Synthesizer

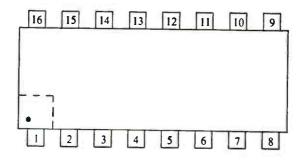

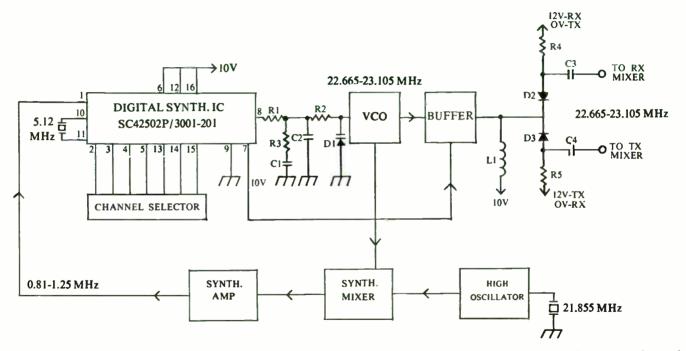

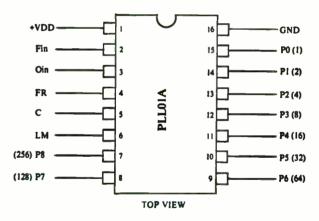

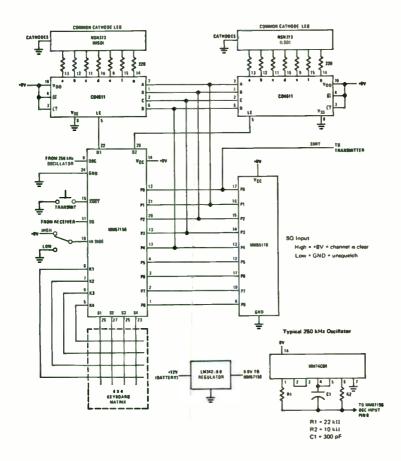

The SC42502P or 3001-201 IC is a custom made IC. It is manufactured especially for E. F. Johnson by one of the major semiconductor manufacturers. This is a CMOS device and is encased in a 16-pin dual-in-line package. This device is used in many Johnson CB models. In this discussion, the Johnson Messenger 4140 will be used as the example.

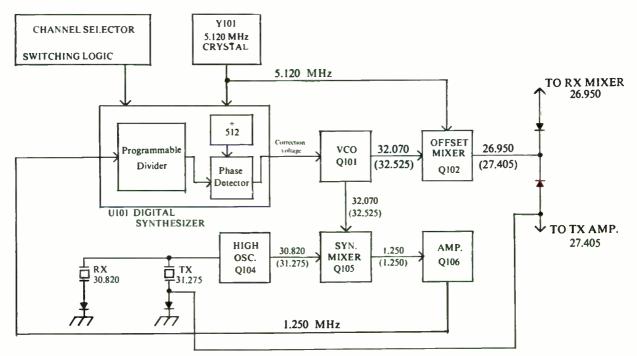

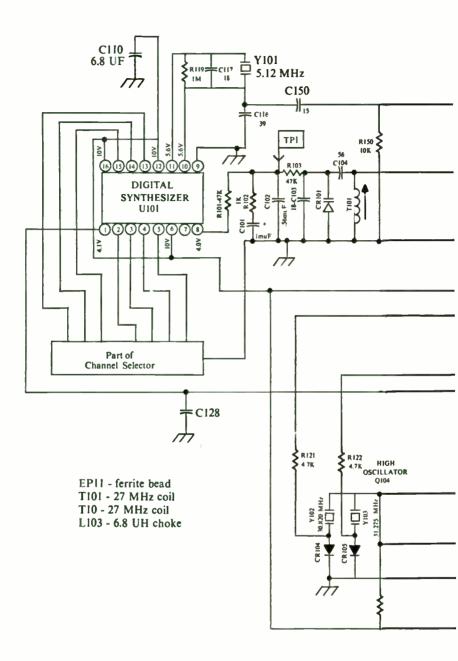

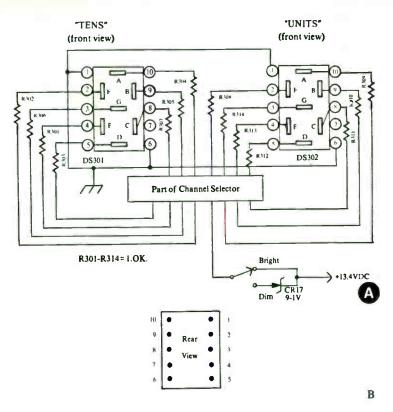

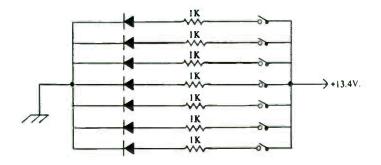

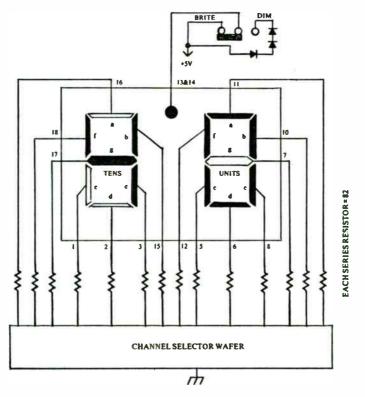

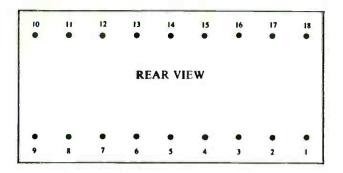

First, the IC itself will be discussed. Then a block diagram of a typical application of the IC will be analyzed. Next, a thorough analysis of the Johnson Messenger 4140 PLL synthesizer will be presented. Also, alignment and troubleshooting will be covered. Then, the LED readout display circuitry will be explained.

#### SPECIAL FEATURES

□ Low-Power CMOS

On-chip oscillator (with external xtal)

□ On-chip pullup resistors

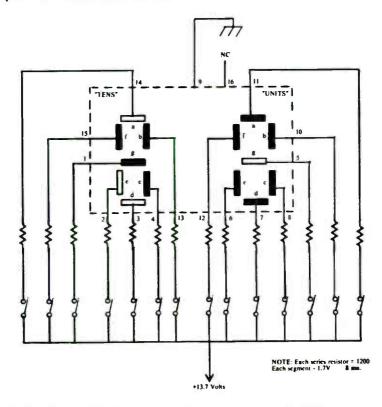

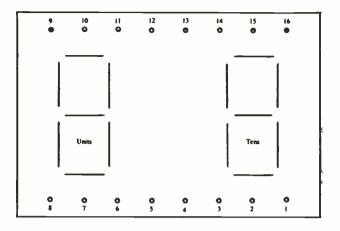

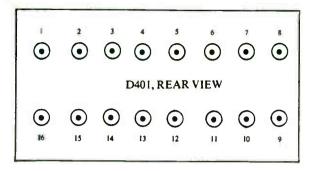

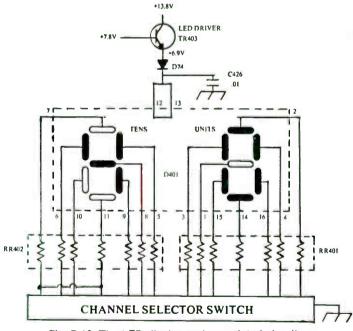

□ Wide supply voltage range

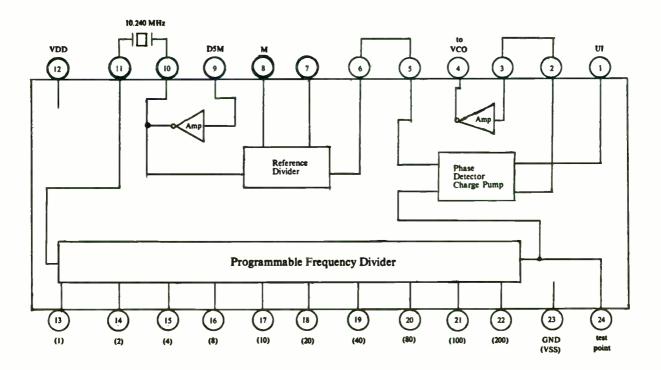

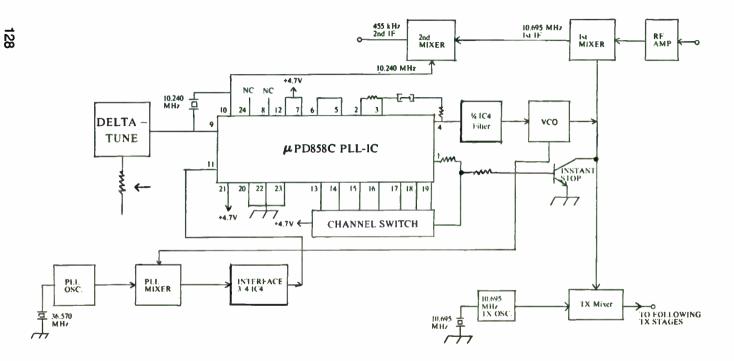

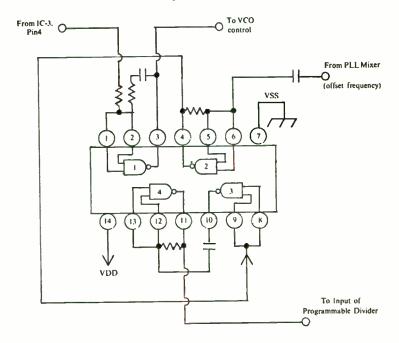

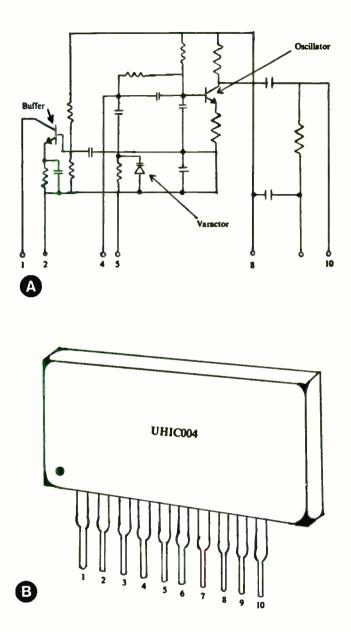

□ 16 pin dual-in-line construction