1. 经公司运行时间 2015年19月4日前,他们的时间的时候,他们就是这些个时间,但不可能。

No. 1218 \$16.95

# HOW TO TROUBLESHOOT & REPAIR ELECTRONIC CIRCUITS By Robert L. Goodman

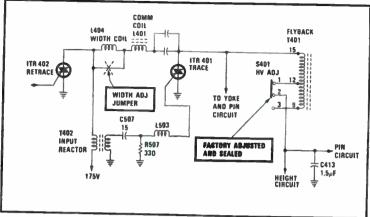

**FIRST EDITION**

**FIRST PRINTING**

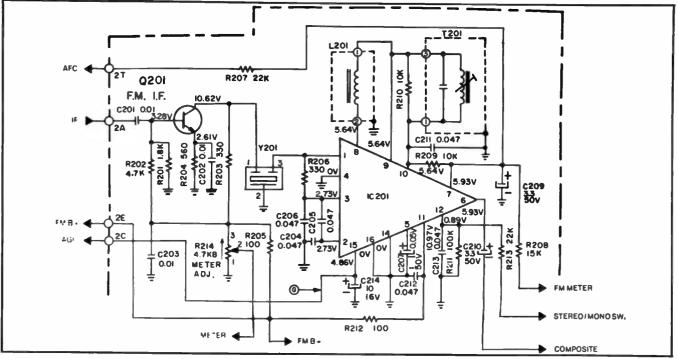

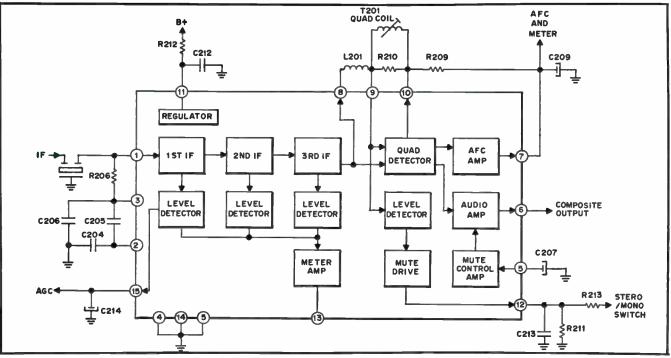

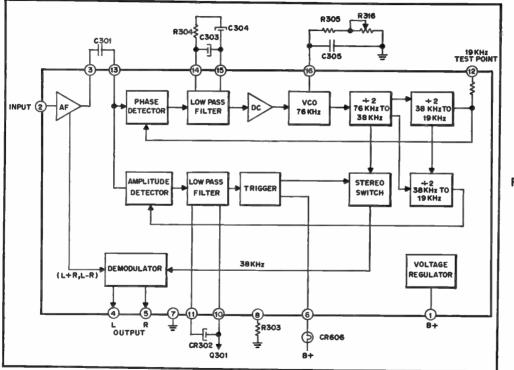

**APRIL 1981**

Copyright © 1981 by TAB BOOKS Inc.

Printed in the United States of America

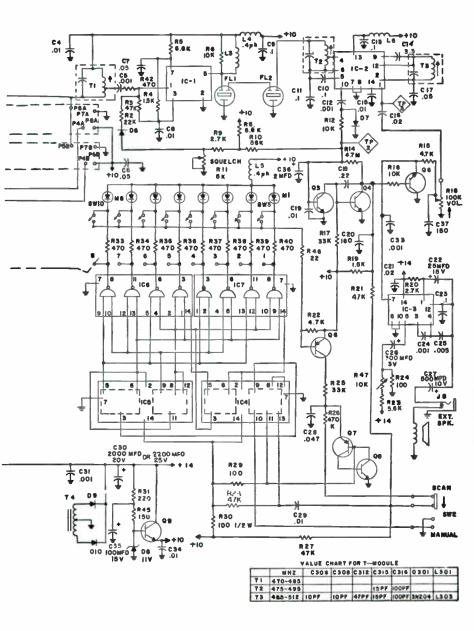

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

Library of Congress Cataloging in Publication Data

Goodman, Robert L. How to troubleshoot & repair electronic circuits.

Includes index. 1. Electronic apparatus and appliance—Maintenance and repair. I. Title. TK7870.2.G64 621.3815'3 80-28466 ISBN 0-8306-9656-3 ISBN 0-8306-1218-1 (pbk.)

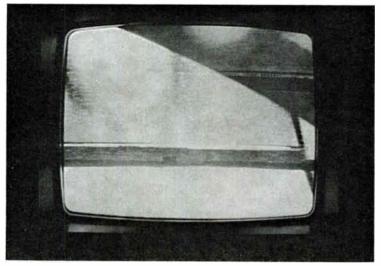

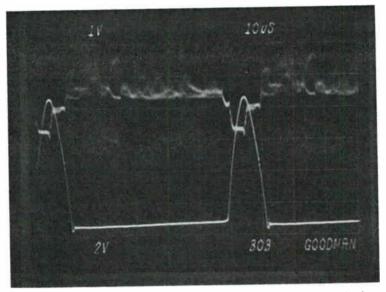

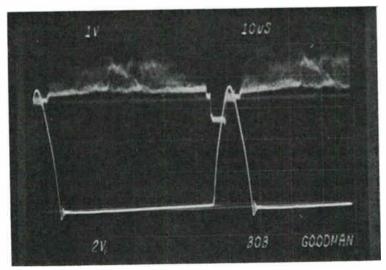

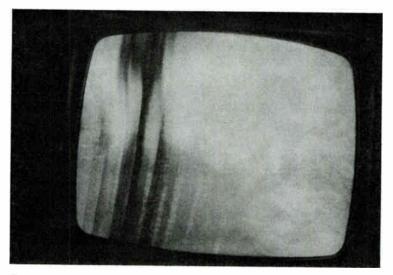

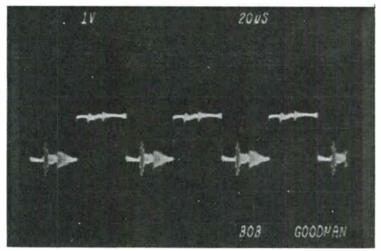

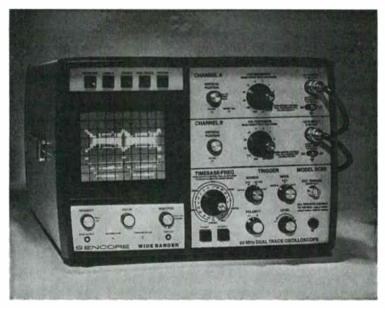

In this book you will find selected electronic circuits, ways to troubleshoot them, and known component failures. Some actual case-history problems will also be given. In some TV circuits a photo of the picture symptoms will be provided. Voltage, resistance, and oscilloscope waveforms will be included where applicable.

Included in this book you will find tube type, transistor, IC, microprocessor, analog and digital logic circuits for various consumer electronic devices. Old and new circuits will be found along with the types of electronic equipment in which the circuits are found.

The electronic circuit reference data in this book will give you up-to-date troubleshooting and theory of operation information to assist you in keeping on top of today's advanced space age electronic systems.

In all, 30 years of electronic troubleshooting experience and knowhow has been collected and presented in this reference book for your convenience and enlightenment.

Robert L. Goodman

I wish to thank the following Electronics Companies and their personnel for all of the technical information and circuit diagrams that they furnished for this book. Svlvania - GTE Magnavox Corp. Radio Shack - Dave Gunzel Sencore, Inc. - Mr Bowden and Greg Carey **RCA/Consumer Electronics** General Electric Co. Quasar Electronics - Charlie Howard Sony Corporation of America - Howard L. Katz Hewlett-Packard B & K Dynascan Corp. - Myren E. Bond Zenith Radio Corp. - James F. White Continental Specialities Corp. The Electra Company - Bearcat Scanners The Heath Company

#### **1** Color TV Tuners

The Sylvania Manual Electronic Tuning System—Zenith Direct Access Tuning System—Electronic Tuning System (RCA CTC-93 Chassis)—Basic Phase-Locked Loop Theory—Basic Phase-Locked Loop Operation—Automatic Offset Tuning—DC Tuning Voltage and Prescaler Frequency—Band Switching—LED Display—Servicing the Scan FS Control Module—Electronic Tuning System (Varactor) GE ET-20 System

#### 2 TV Remote Control Systems

Direct Access Remote Control (Zenith 2000 System)—MSC-003 FS Scan Remote Control (RCA)—Remote Receiver Power Supply (RCA CTC-48-68)—Remote Control Logic Systems (RCA CTC-74,81 Chassis)—Magnavox "Star" TV Tuning System

# **3 Color TV Circuits**

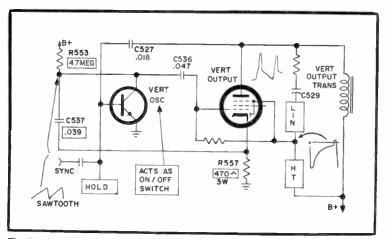

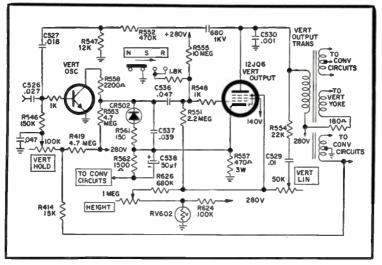

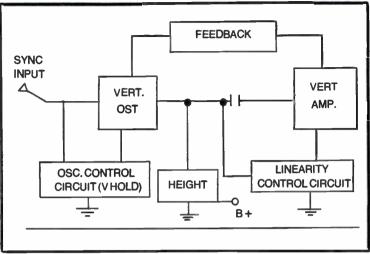

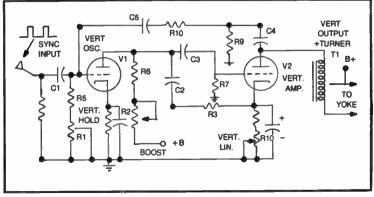

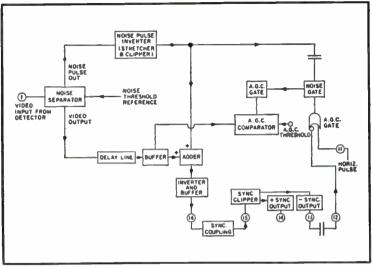

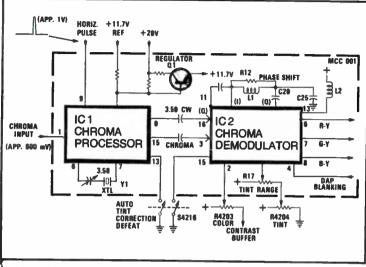

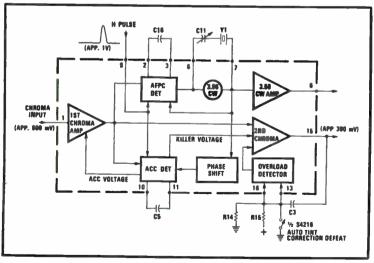

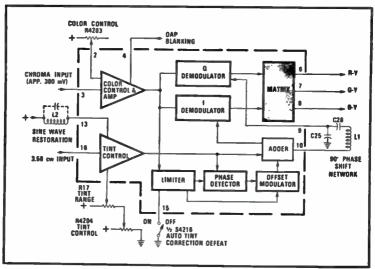

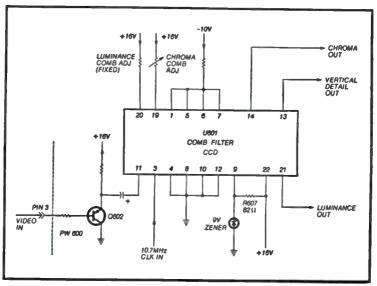

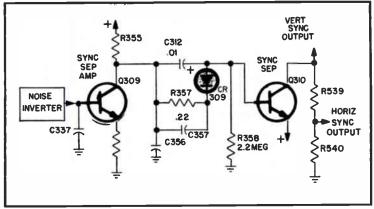

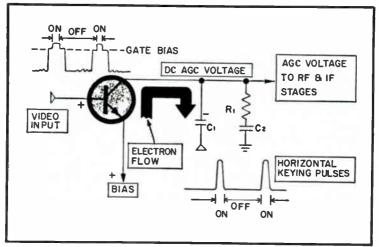

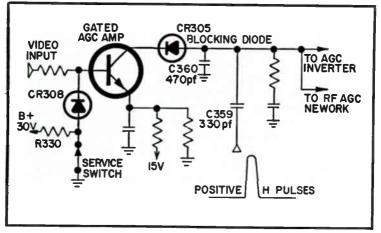

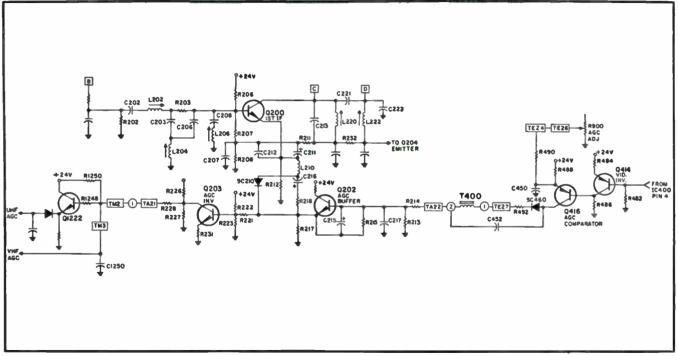

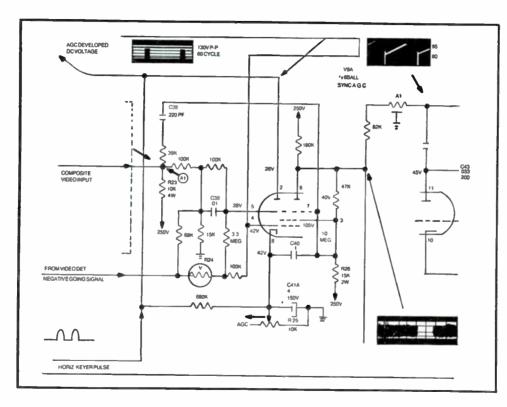

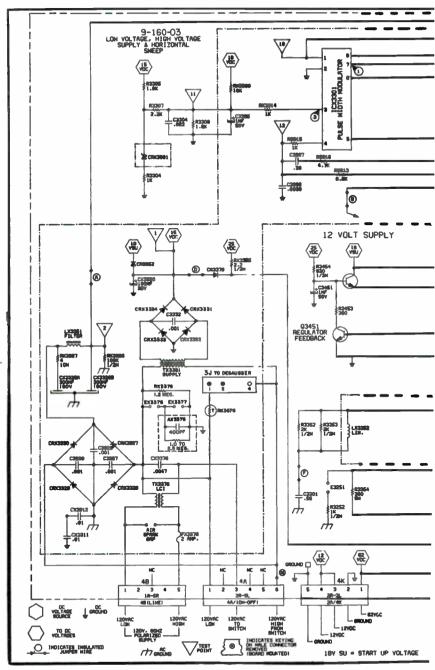

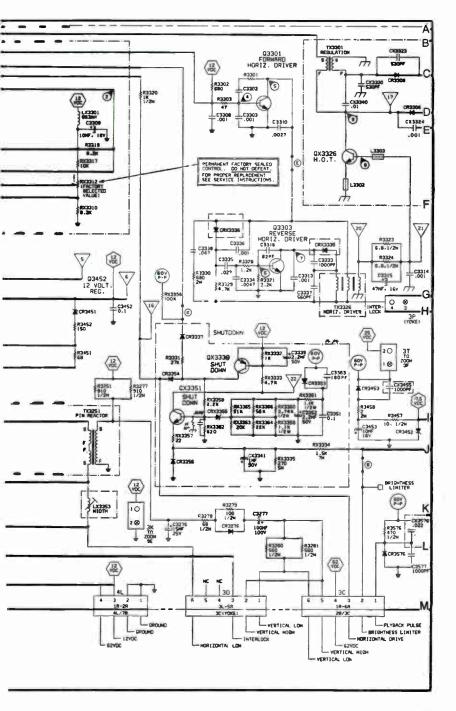

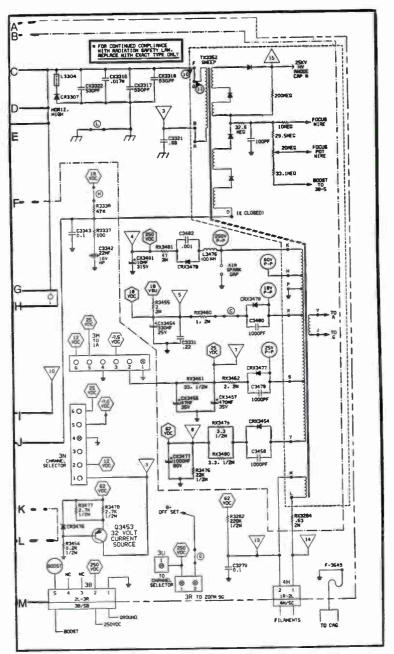

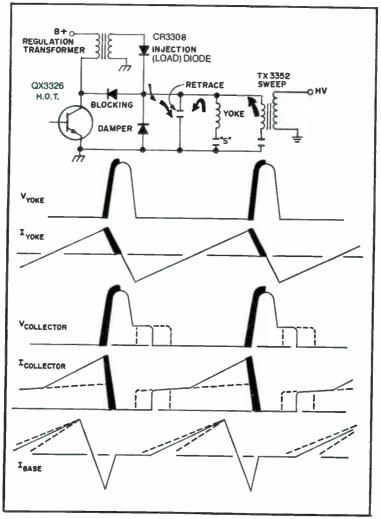

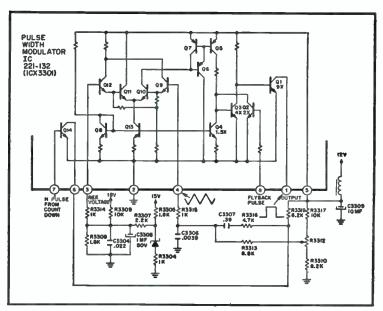

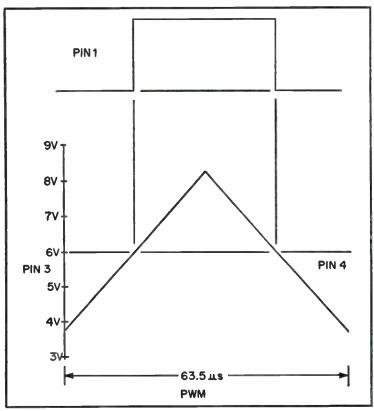

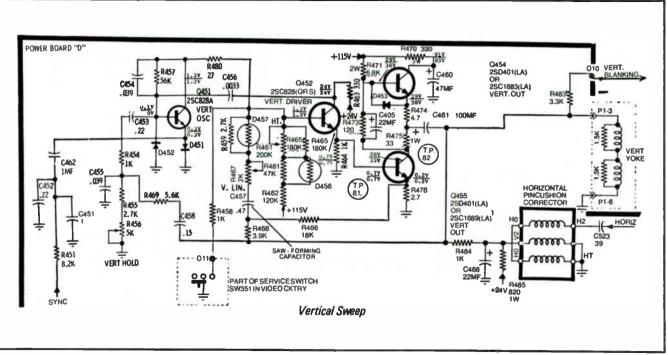

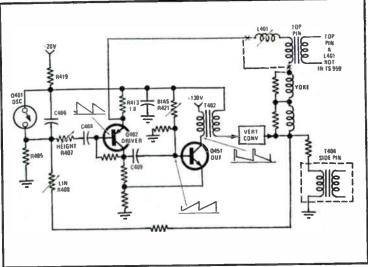

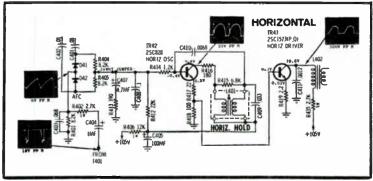

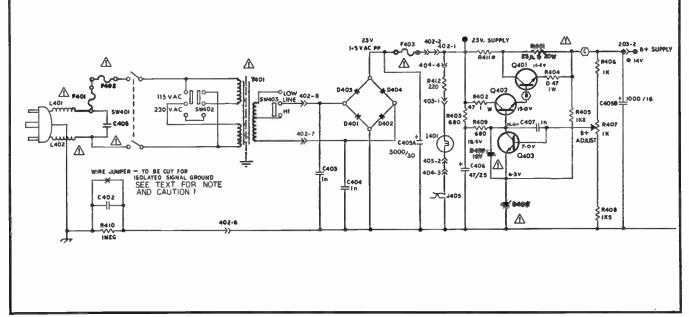

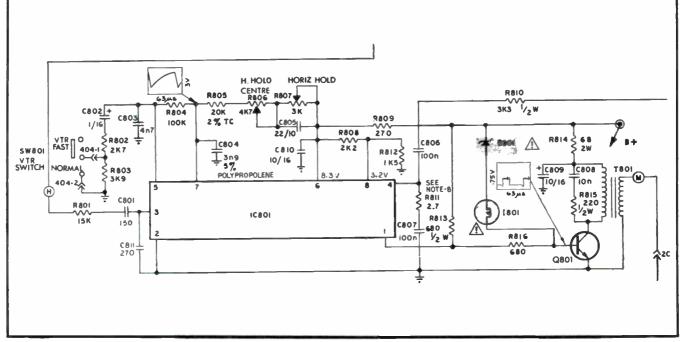

Horizontal Oscillator/Vertical Countdown System-Vertical Sweep Amplifier (Solid-State) RCA 99/101 Chassis-Horizontal Sweep Output Circuit (Solid-State) RCA CTC 99/101 Chassis-Chroma Circuitry (IC Chip) RCA CTC93 Chassis-Hybrid Vertical Sweep Circuit-Plate Coupled Vertical Sweep Circuit (Tube Type)-Plate-Coupled Multivibrator (Two-Tube Type Vertical Oscillator and Amplifier)-The Zenith Sync/AGC Processor Chip 221-45-Video Amplifier Circuit (Solid-State)-Power Supply Circuit (Full-Wave Voltage Doubler, S-S Diodes)-Horizontal Sweep-Trace/Retrace Circuit (RCA Type)-Chroma System (RCA Solid-State ICs)-Comb Filter Circuit (RCA CTC 99/101 Chassis)-Video Circuit Amplifiers (Tube Type-AC Coupled)-Vertical Blanking Circuit (Tube Type)-Color Difference Amplifiers (Tube Type Circuit)-TV Sound Circuit (Solid-State IC)-Sync Separator Circuitry (Solid-State)-Automatic Gain Control (AGC) Circuit (Solid-State)-AGC Control System (Solid-State Transistor)—Sync and AGC Circuits (Tube Type-Zenith)—Zenith System 3 Electronic Power Sentry and Horizontal Sweep System-TV Sound Solid-State IC (Quasar TS-958 & TS-959 Chassis)-Vertical Sweep System (Solid-State Transistor) Quasar-Vertical Sweep Circuit-Solid-State (Quasar TS-951 Chassis)

9

57

# **4** Black and White TV Circuits

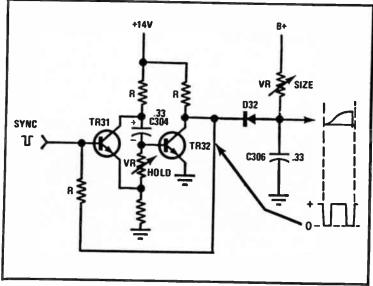

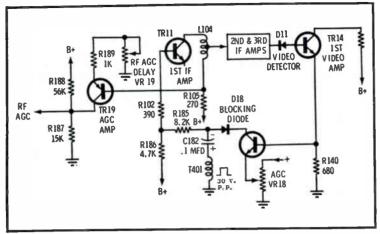

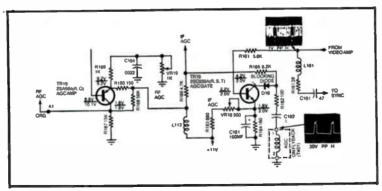

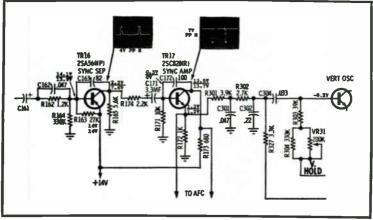

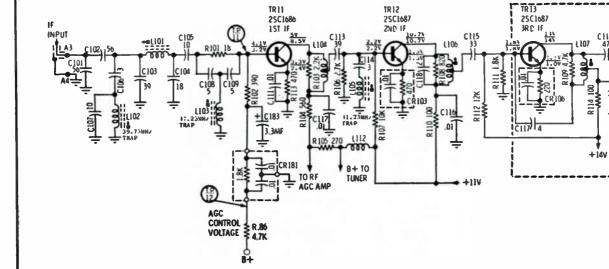

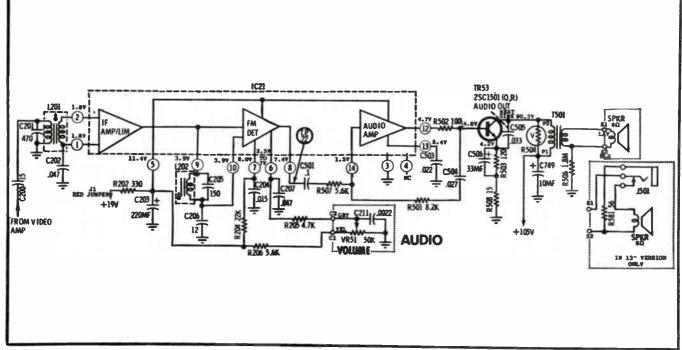

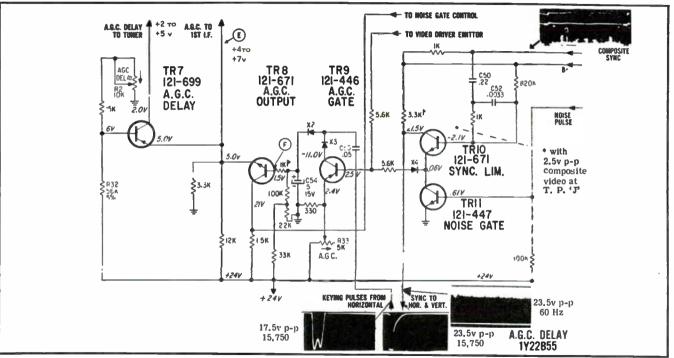

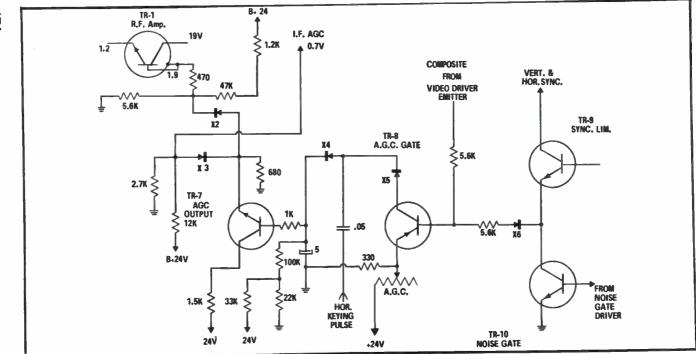

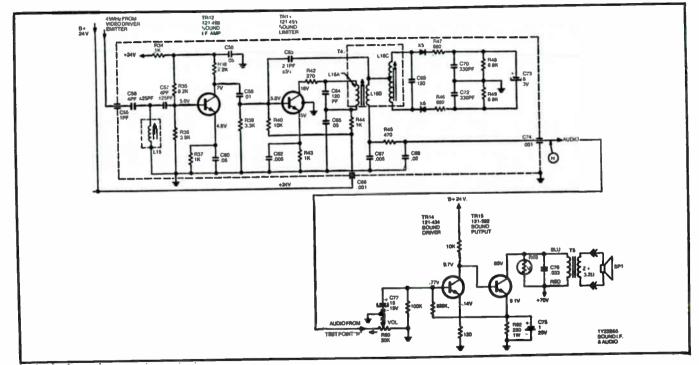

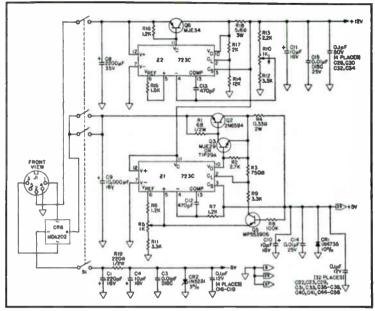

Vertical Sweep System (Transistor) Quasar TS-481 Chassis-IF AGC Circuits-Quasar B & W TV (Solid-State)-Sync Separator Circuit (B & W TV Solid-State)-Video IF Circuits (B & W TV Solid-State)-Audio System (IC Solid-State)-Horizontal Oscillator and Driver (Solid-State)-Power Supply Circuit (Solid-State Regulated)—Power Supply Service Tips (Regulated)—Horizontal Oscillator (Solid-State IC)-Power Supply (B & W TV) AC/Battery Type—Solid State IF System (B & WTV)—Video Amplifier Circuits (Zenith B & W TV)—AGC Circuit (Solid-State Zenith B & W TV)

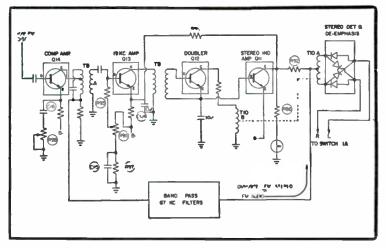

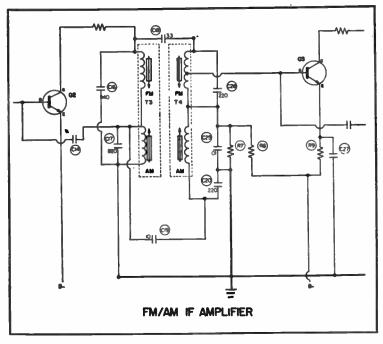

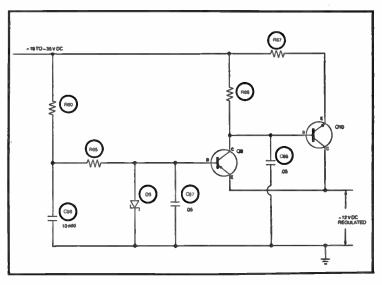

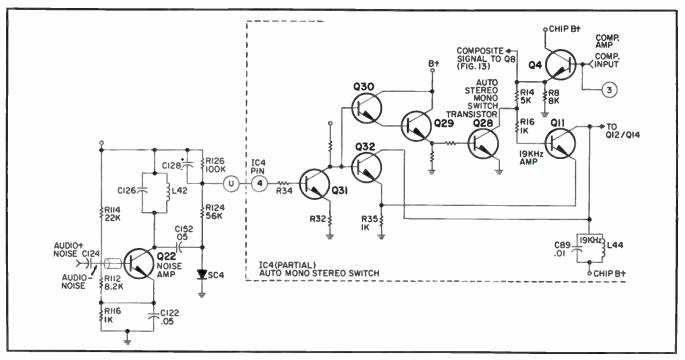

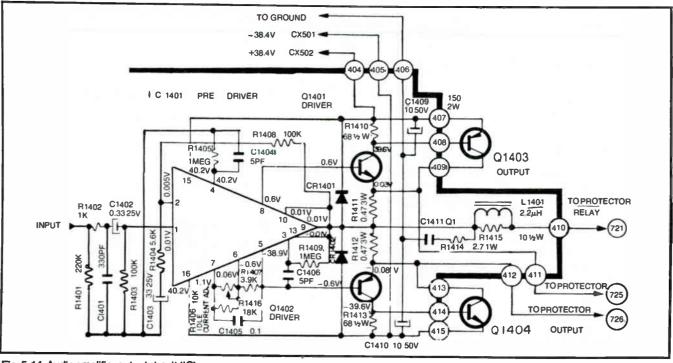

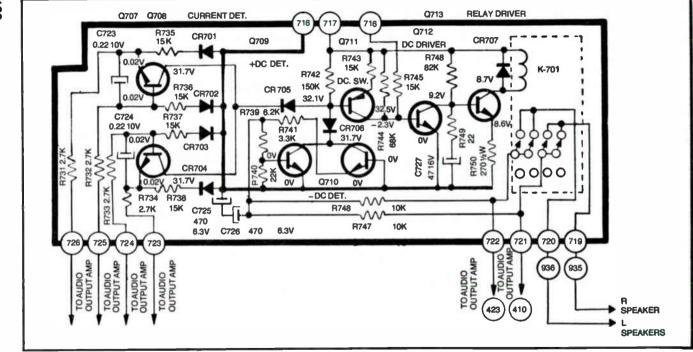

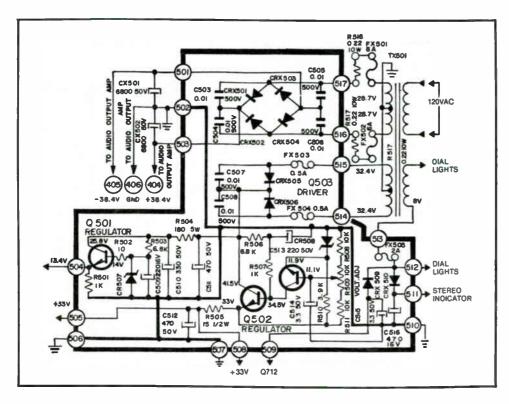

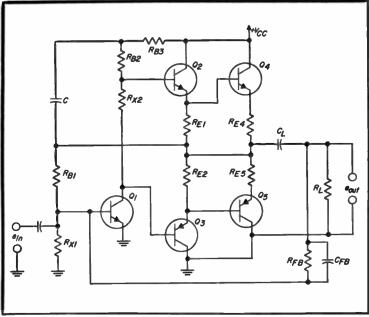

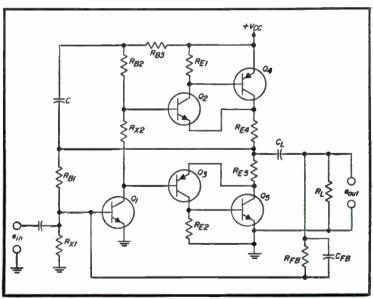

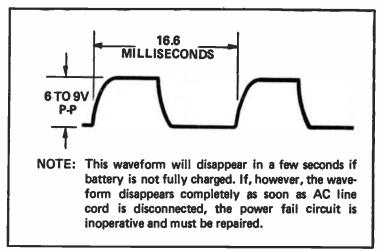

## 5 AM/FM Stereo Tuners and Amplifiers

FM Stereo Receiver Circuit (GE TU-100)—AM/FM IF Amplifier Circuit (GE TU-100 Chassis)—AM/FM Tuner Power Supply Circuit-Noise Amplifier (Sylvania)-FM Detector (IC2) Sylvania Stereo-IF Circuit Strip-FM Stereo (Zenith)-FM Quadrature Detector-FM Multiplex Circuit Operation (Zenith)-Audio Amplifier Circuitry (Mono-Stereo)-Stereo Output Stages (IC and Transistor)-Automatic Speaker Protection Circuit-Power Supply Circuit-Stereo Push-Pull Amplifier Circuits-Complementary Transistor Amplifiers—Stereo Amplifier Troubleshooting

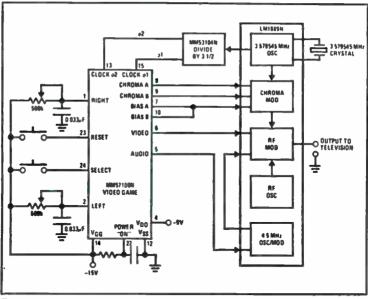

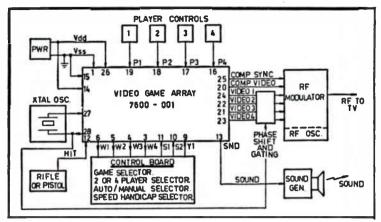

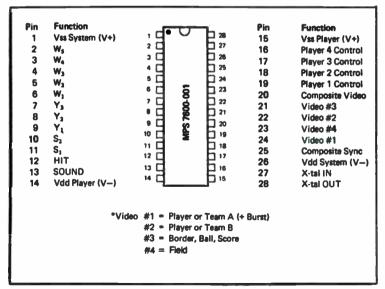

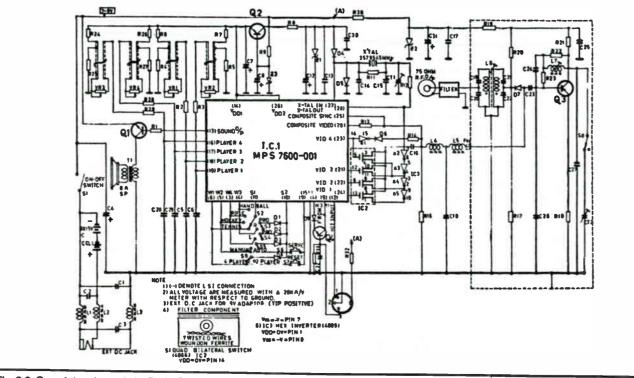

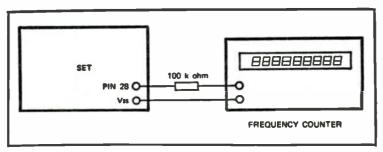

#### **Electronic Video Game Circuits** 6

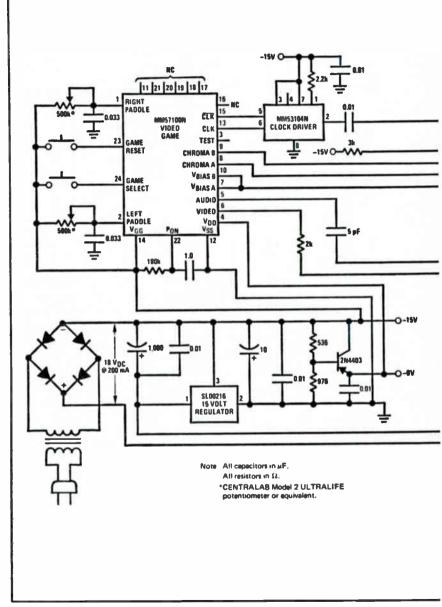

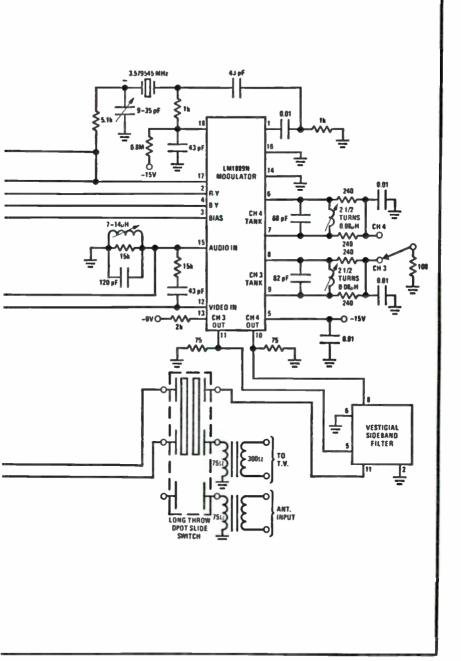

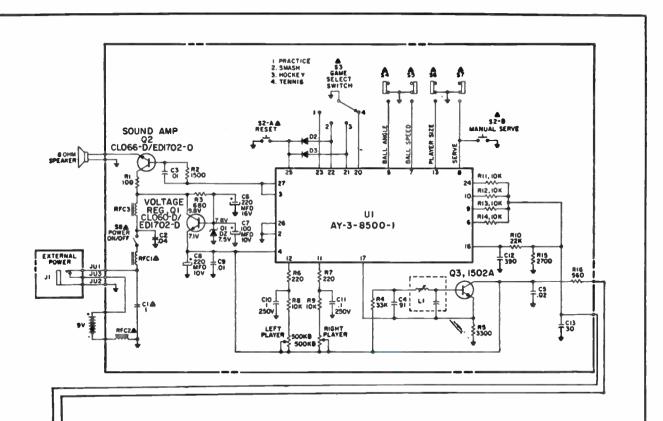

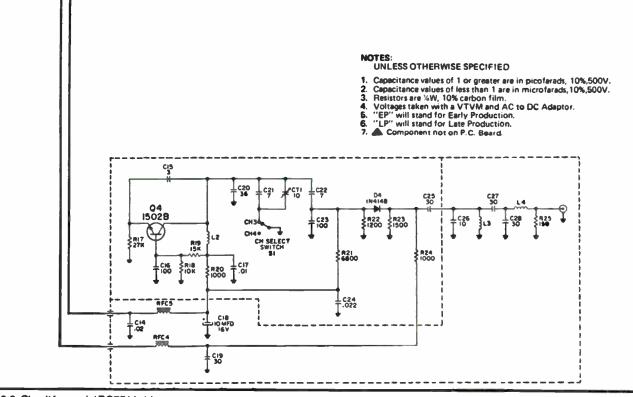

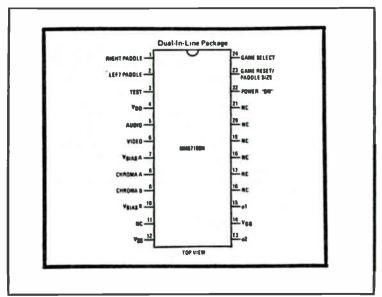

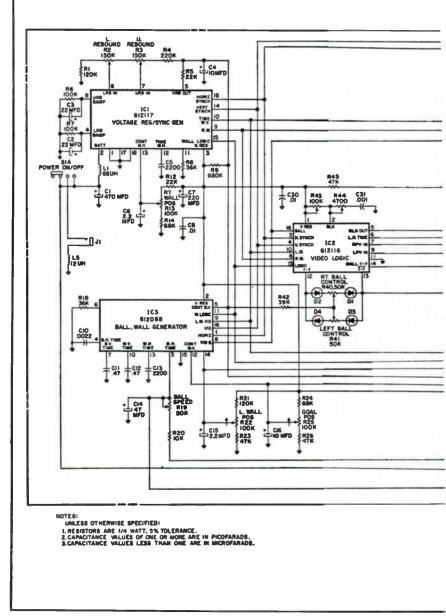

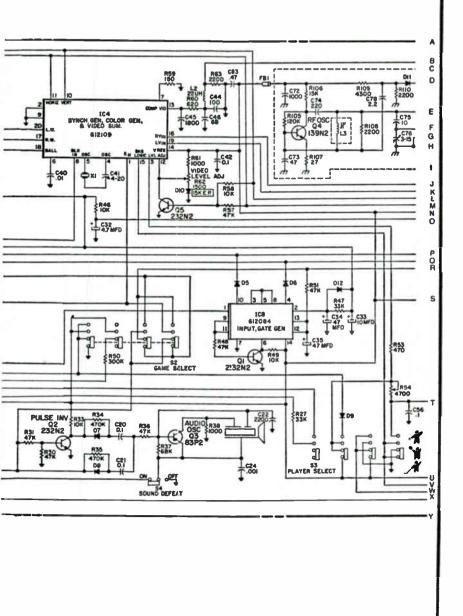

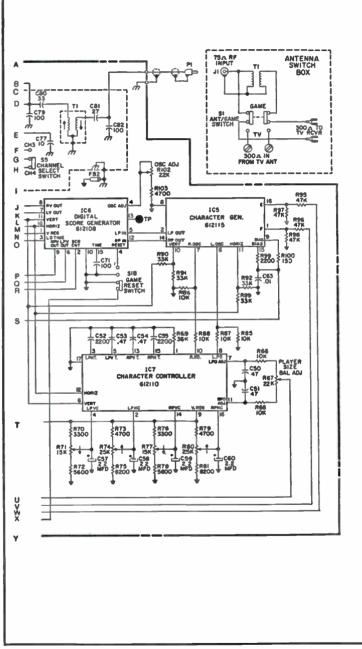

National Semiconductor Video Game Chip-Magnavox Video Games (Odyssey Model BH7514)-Radio Shack Video Game (Model 60-3057)-Game Chip Replacement-Troubleshooting Video Game Circuits

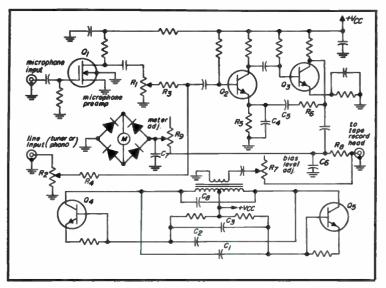

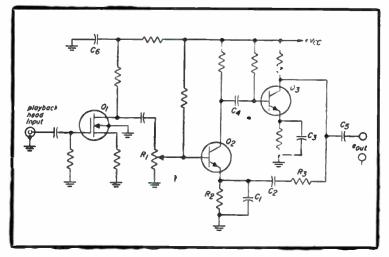

#### 7 **Tape Deck Electronics**

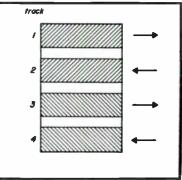

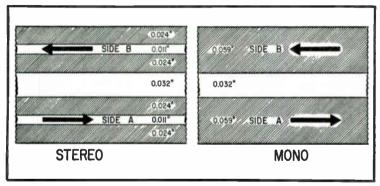

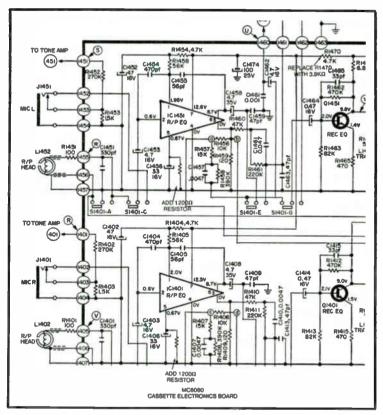

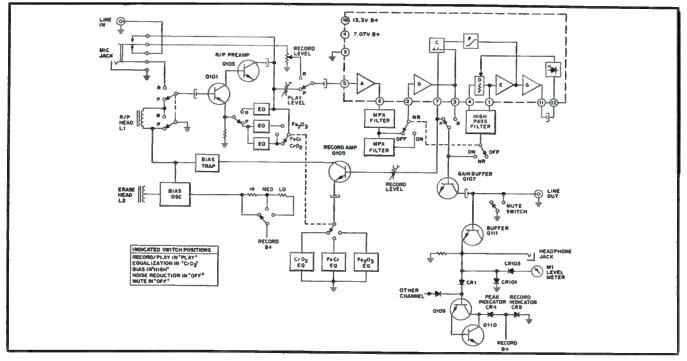

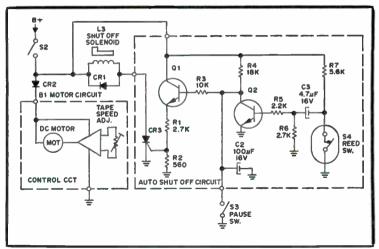

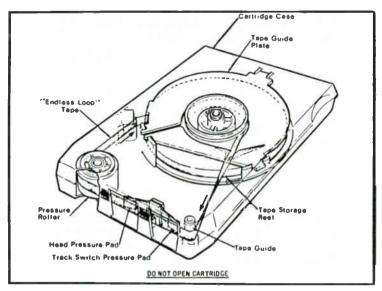

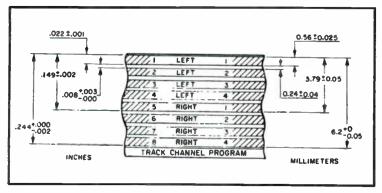

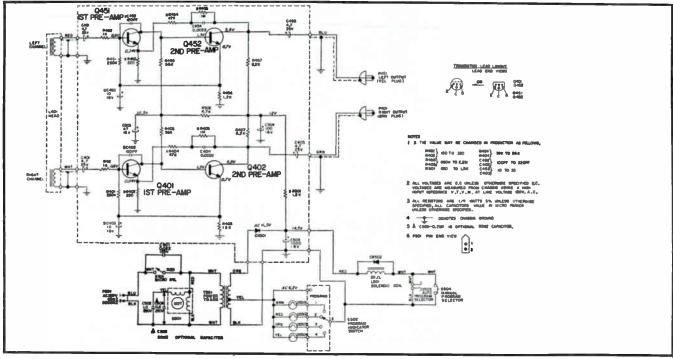

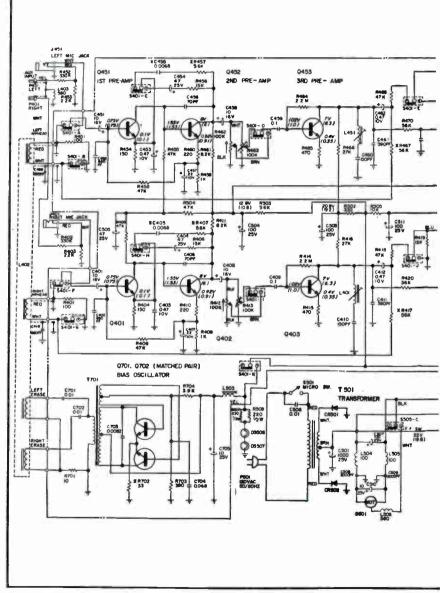

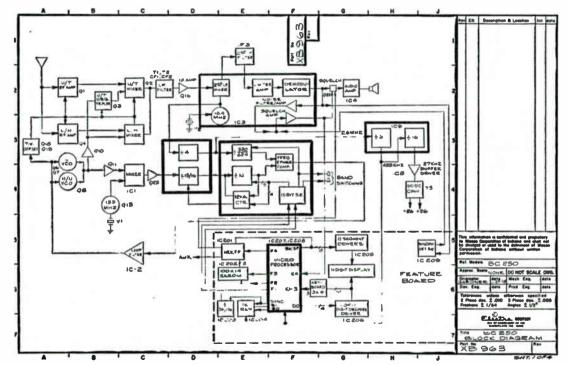

Introduction to Tape Recording-The Playback System-Stereo Tape System-General Cassette Tape Recorder Data-Play/ Record Amplifier Operation-Bias Oscillator Circuit-Professional Cassette Play/Record Tape Unit Zenith MC9070-Noise Reduction Systems (Tape Recorders)-Auto Shut-Off Circuit (Cassette Players)-8-Track Tape Player/Recorder System

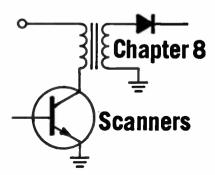

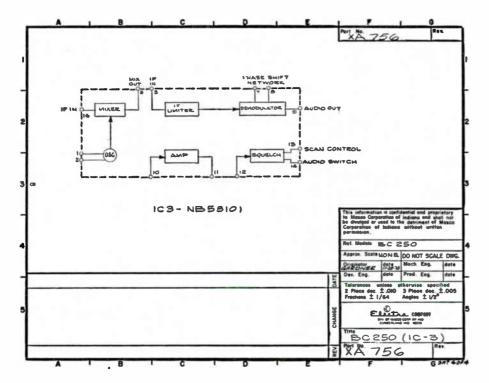

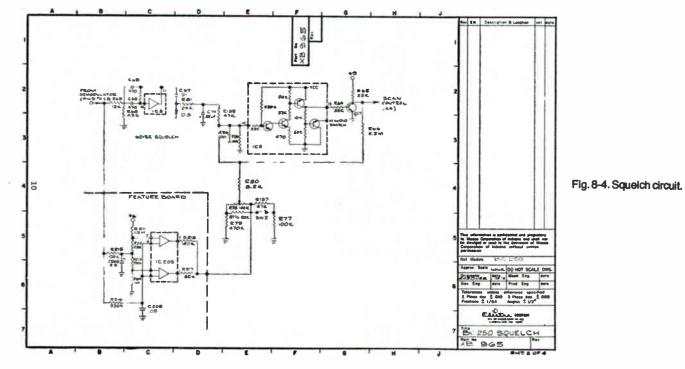

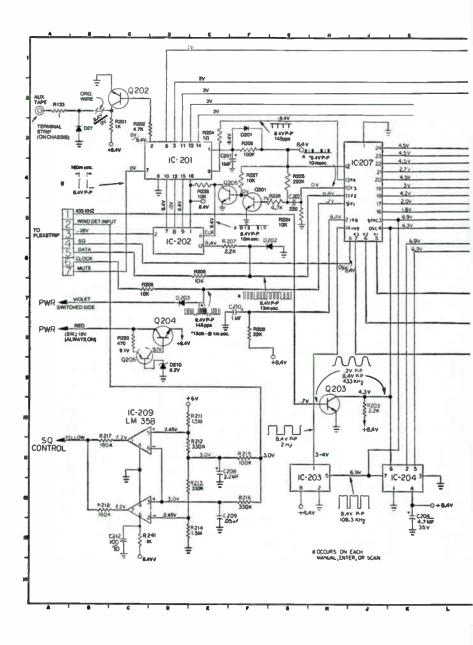

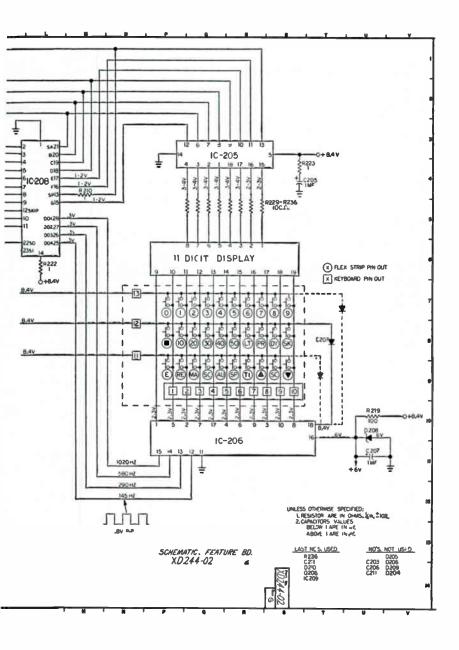

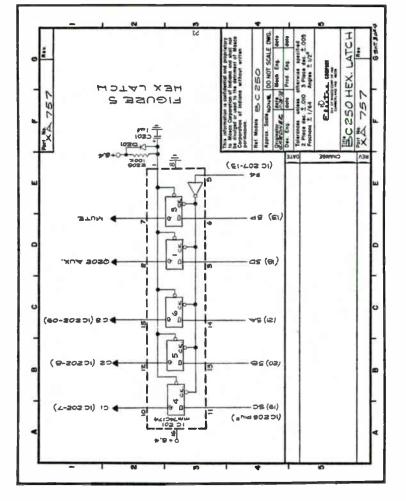

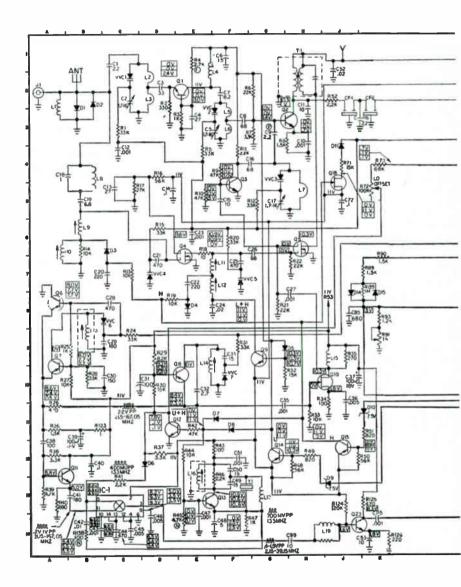

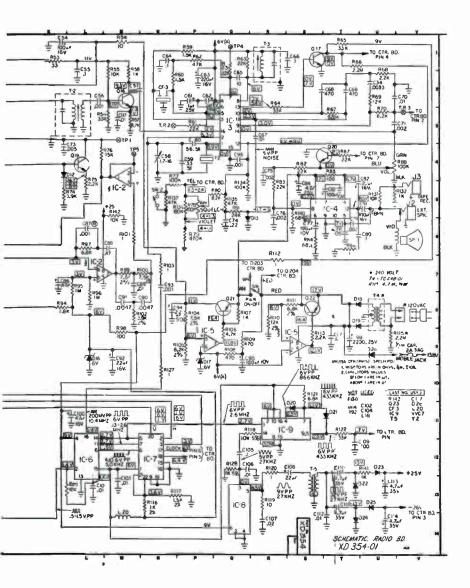

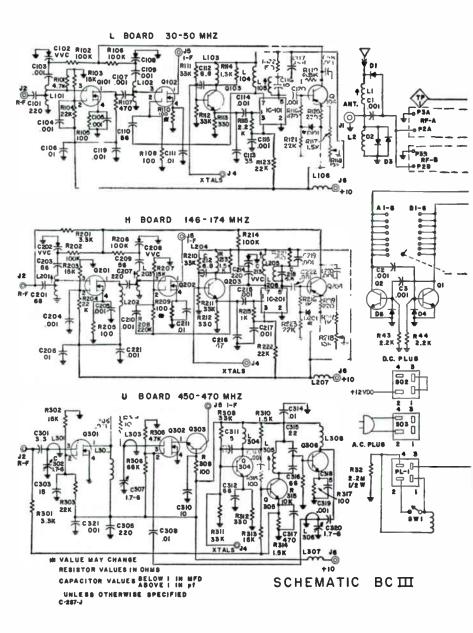

- 8 Scanners Bearcat BC 250 Scanner Circuits-Radio Shack PRO-2008

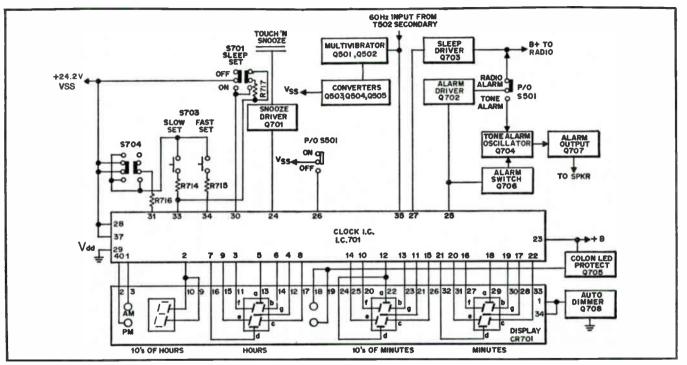

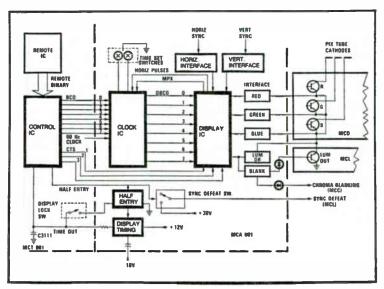

- **Digital Clock Readouts** 9 Electronic Digital Clock Checks (Zenith Model L480)-RCA Digital **Clock and Screen Readout System**

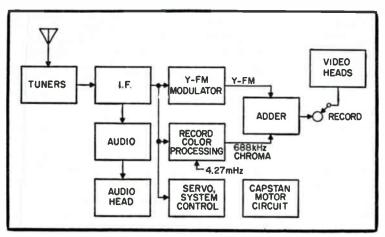

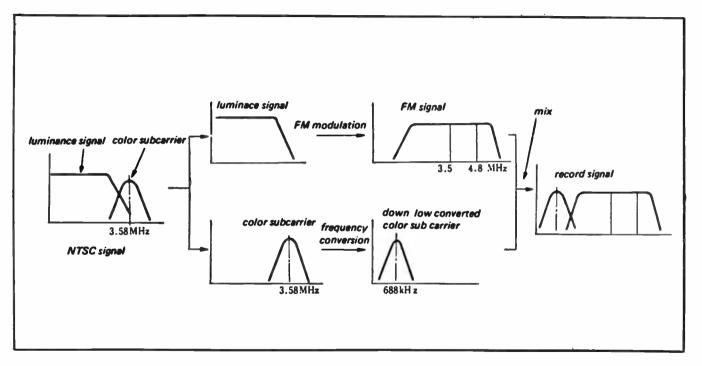

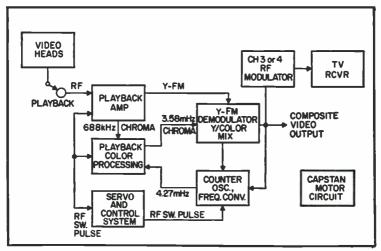

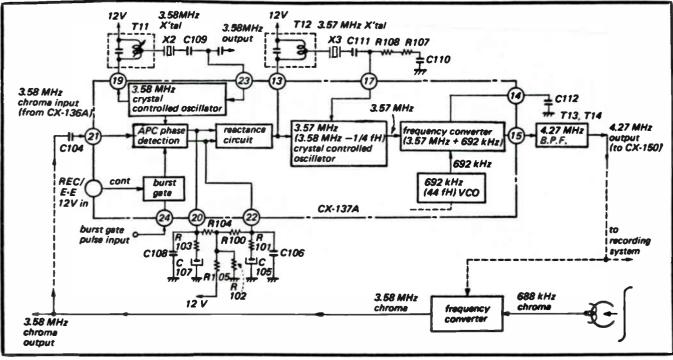

- Video Tape Recorder (VCR) Circuits 286 10 RCA VCR Circuit Operations-Zenith (Sony) Betamax VCR System-Zenith Model KR9000 VCR

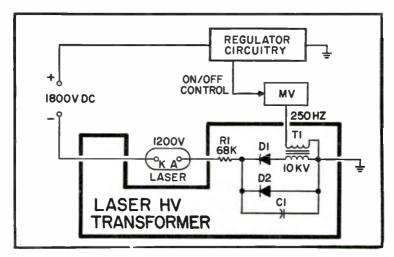

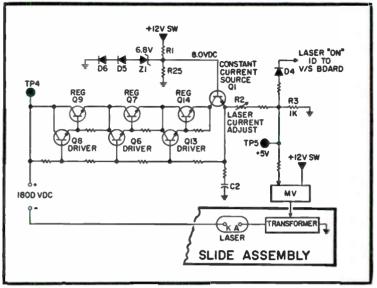

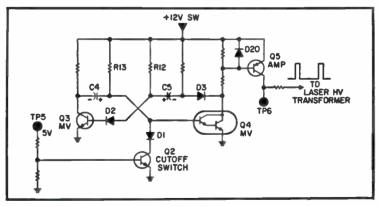

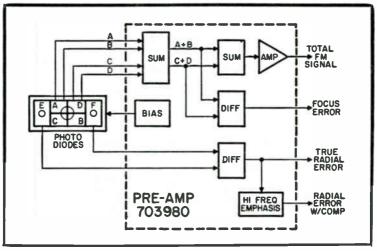

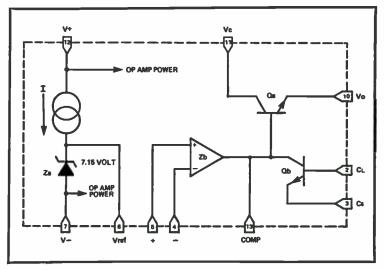

#### 314 Unique Circuits Found in Video Disc Players 11 Magnavox Model VH8000 Video Disc Player-Fundamental Video Disc Operation-Laser Drive Circuit Operation-Laser Power Supply Circuit-Laser Multivibrator Circuit-Signal Processina

178

204

226

269

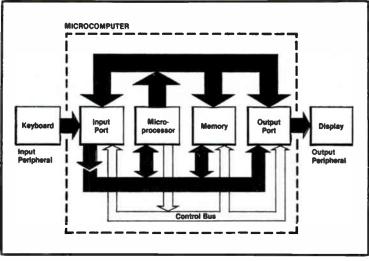

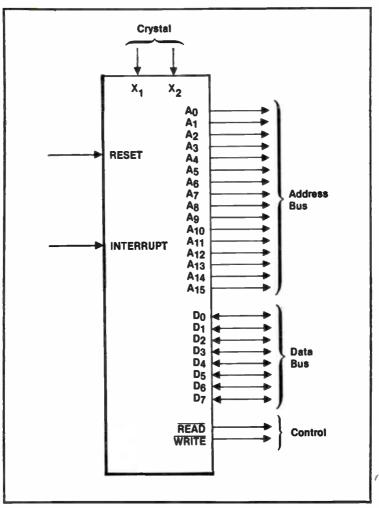

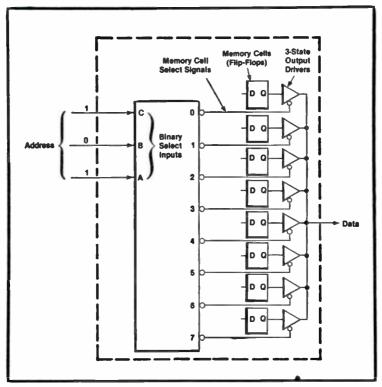

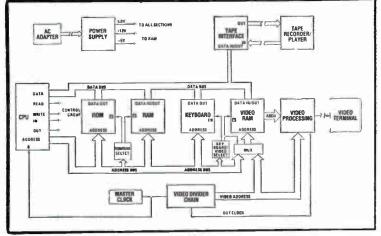

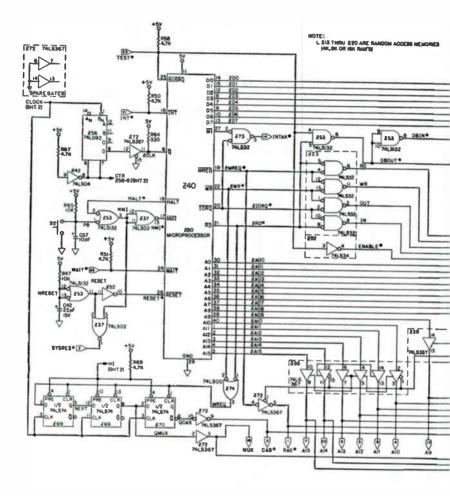

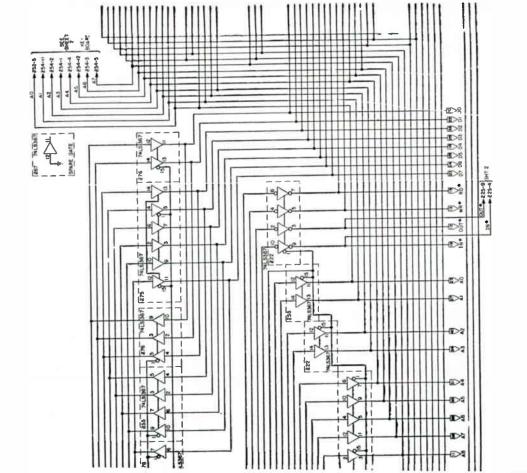

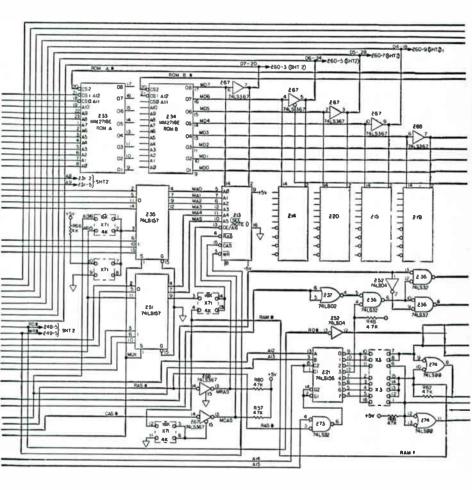

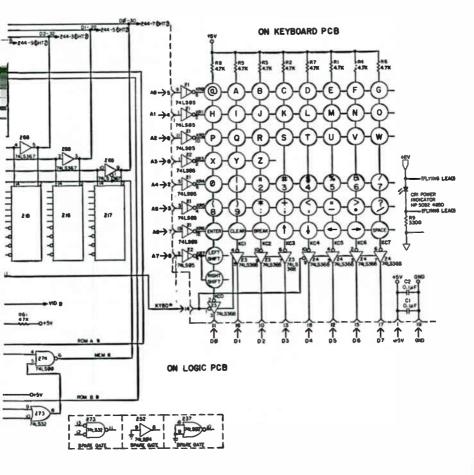

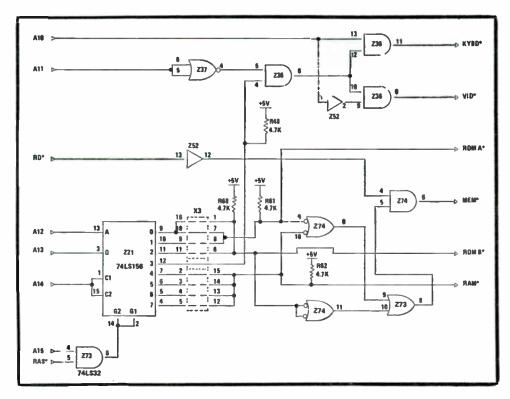

# 12 Introduction to Microcomputer Systems and Microprocessors

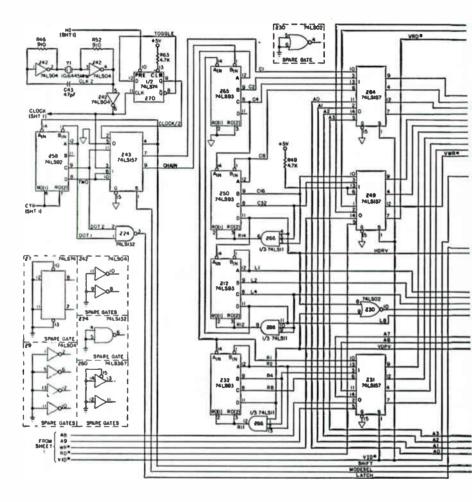

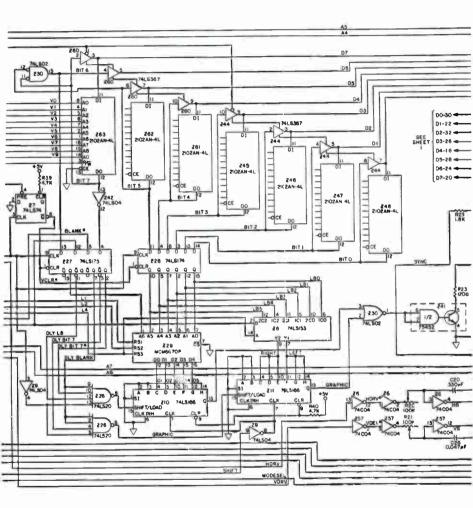

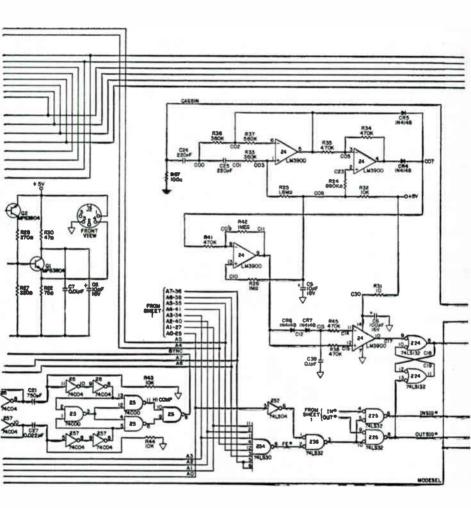

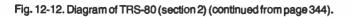

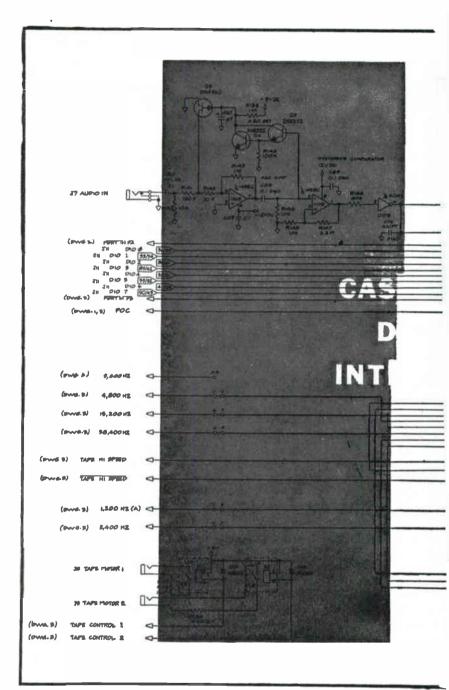

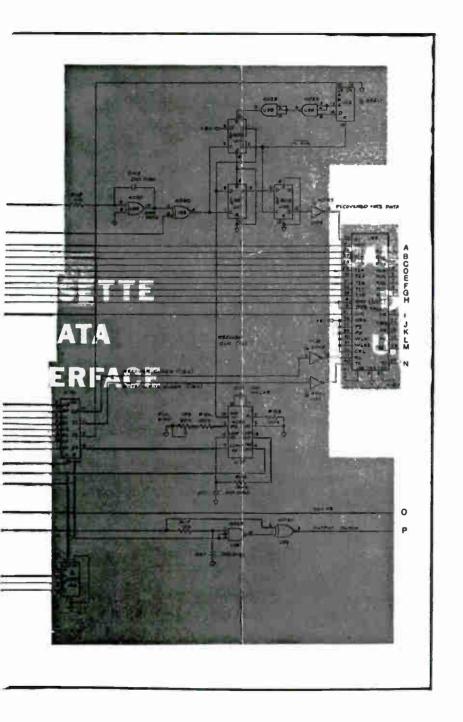

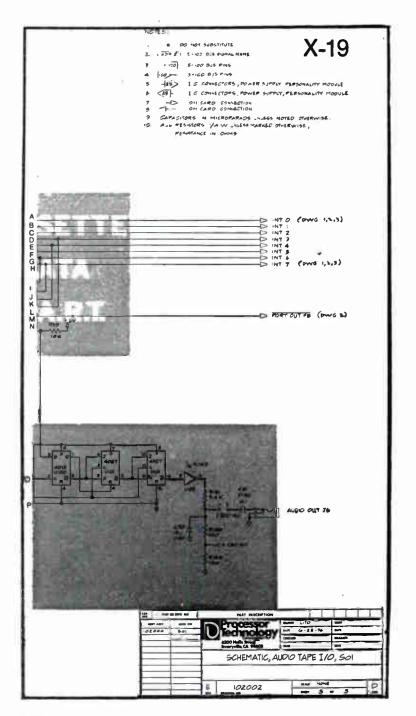

Development of the Microprocessor-Microprocessor Use-A Basic Microprocessor System-Three-State Drivers-The Microprocessor-Memories Are Made Like This-Microcomputers and Minicomputers-Radio Shack's TRS-80 Microcomputer System-Processor Technology Corp. SOL-20 Microcomputer

Index

In this chapter we will cover operation and troubleshooting information on various electronic tuners used in assorted makes of color TV receivers. The circuits will include the VHF and UHF tuners along with their control center circuits. Some will be the manual channel selector control units, while others will be remote controlled via all electronic switching IC and transistor devices. Various DC voltage control and AFC (automatic frequency control) circuit schemes for electronic tuners will be reviewed.

# THE SYLVANIA MANUAL ELECTRONIC TUNING SYSTEM

Some Sylvania color sets have conventional two knob UHF and VHF tuning systems, but others have a combination UHF/VHF varactor tuner with a one knob addressing system. One channel selector and one fine tuning knob are used to change and adjust both UHF and VHF stations.

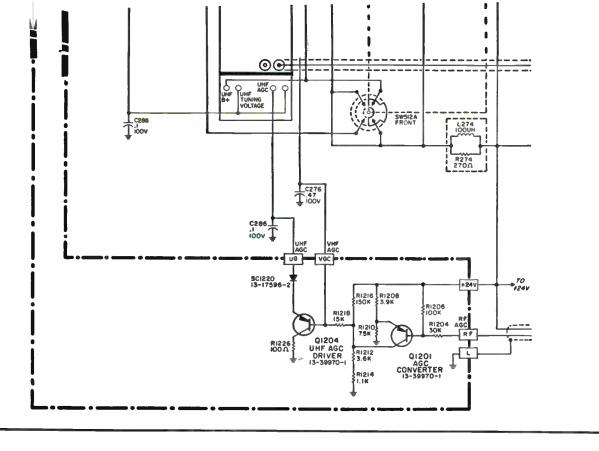

The tuning voltage applied to the UHF/VHF tuner is varied in two ways. Note the tuner control circuit shown in Fig. 1-1. Band switches apply the 24 volt B+ line to either the UHF or VHF portions of the tuner. The variable tuning voltage comes from the 112 volt B+ line and is dropped and regulated by a 33 volt Zener on the tuner cluster assembly. This 33 volts is varied by adjusting variable resistors mounted in a tuning assembly that looks like a small barrel type tuner. Instead of many contacts on each of the strips, as with a conventional barrel type tuner, these strips have only three contacts on the variable 10 K ohm resistor. The voltage output from the variable resistors, ranges from +1 volt to +28 volts. As the channel selector is rotated, a different dial appears through the viewing window. This dial indicates the channel ranges in either the UHF or VHF spectrums. As the fine tuning knob is varied, a red pointer moves up and down the indicator dial showing the channel being tuned. This dial is located below the channel knob. A second channel indicator window is visible above the channel knob. It indicates all of the VHF channels and has

=

positions to insert the UHF channel numbers that the set will be tuned to in the viewing area. Once the channels have been programmed, the viewer turns the channel selector until the desired station number appears in the top viewing window.

In addition to varying the tuning voltage with the variable resistors, the tuning voltage is also varied slightly by the AFC system. The AFC voltage is applied to a printed circuit board mounted on the tuner cluster that has the various circuits required to drive the varactor tuner. The AFC voltage is fed to Q1208 the VHF compensator and Q1210 the UHF AFC compensator. The output of these two transistors varies the tuning voltage slightly to produce automatic fine tuning action.

The output of the varied 33 volts from the addressing turret is applied to Q1206 the tuning voltage buffer transistor. The output of this emitter follower transistor is varied slightly by the AFC system and then applied to the varactor tuner itself.

The RF AGC voltage from the set is applied to Q1201 the AGC converter transistor and Q1204 the UHF AGC driver transistor, both of which are mounted on the PC board on the tuner cluster. The RF AGC voltage outputs of these two transistors are fed to the UHF and VHF sections of the varactor tuner.

The AGC voltages measured with a signal (the set tuned to a local station) and without a signal (the set tuned to an unused channel) are RF AGC input +8 volts with signal, +4 volts without signal. VHF tuner input +4 volts with signal, +8 volts without. UHF tuner input +4 volts with a signal and +9 volts without a signal.

#### ZENITH DIRECT ACCESS TUNING SYSTEM

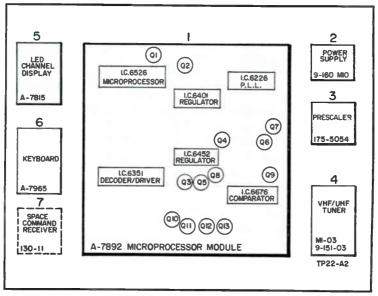

Looking at the block diagram in Fig. 1-2, you will see seven major block sections that are required to make the direct access tuning system operational. As you may guess, the heart of the system is the new microprocessor module. This A-7892 module consists of six integrated circuits and 13 transistors with all of the associated circuitry. The 175-5104 direct access tuning unit package consists of the new microprocessor module (A-7892), keyboard channel selector, prescaler, and the space command remote receiver. There is also a manual version of this direct access tuning system.

#### **Channel Selection Operation**

The receiver-mounted keyboard consists of 15 snap-action push buttons. This type of push button switch offers a positive user feel and has the following features:

• Separate on/off buttons (button must be held a moment for on/off action).

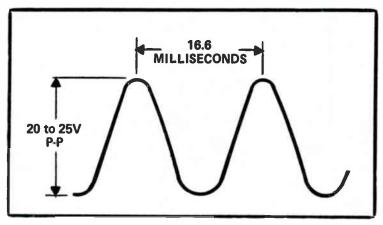

- 0 to 9 channel selector buttons.

- Separate volume up/down buttons.

- Enter button.

A channel can be selected by pushing the desired channel number and then pressing the *enter* key. Also, a 0 does not have to be entered for a single channel number. If a channel number is selected without pressing the enter key, the display will show the new number, but will return to the original number after 4.5 seconds have elapsed.

This direct access system will also tune the cable TV channels that are referred to as the **super** band channels J through W and the **mid-channels** A through I. The mid and super channels are tuned on channels 14 to 36.

#### **Direct Access Functional Blocks**

As we know, the microprocessor IC is the heart of this complete tuning system. It is essentially a small computer which controls all of the functions of the tuning system.

• It constantly scans the receiver mounted keyboard looking for a contact closure.

• It constantly monitors the remote receiver output looking for a remote key closure.

• It controls the operation of the LED channel display through a decoder/driver IC.

$\bullet\,$  It provides B+ switching and bandswitching for the VHF and UHF tuners.

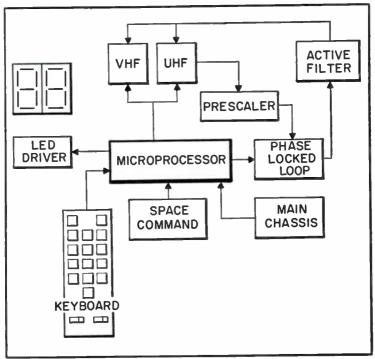

• It controls the operation of a phase-locked-loop IC which results in precise control of the tuner oscillator frequency. See Fig. 1-3.

Fig. 1-2. Direct access system block diagram.

Fig. 1-3. Functional block diagram of direct access system.

# **Phase-Locked Loop Operation**

This tuning system is referred to as a frequency synthesis tuning system. In a voltage synthesis type, a precise, stable tuning voltage is generated and used to control the tuner oscillator. This type of system depends heavily on conventional AFC operation for oscillator frequency stability.

In a frequency synthesis system, a precise frequency is generated and maintained. When a channel is selected, the microprocessor knows what the correct FCC designated frequency should be for that channel. It develops a tuning voltage that will put the oscillator at the correct frequency. It constantly monitors the oscillator frequency by dividing, counting and comparing it to a reference, which results in automatic correction of the tuning voltage, assuring oscillator stability.

As you will note in Fig. 1-4, a crystal-controlled oscillator, operating at 3.581055 MHz, is divided by a 14 stage reference divider in the phase-locked-loop IC, to provide an output frequency of 976.5625 Hz. This frequency, rounded off to 1 kHz, becomes the reference base which is applied to one input of a comparator.

The VHF or UHF oscillator frequencies are applied to a *prescaler* circuit. This prescaler IC and its associated circuitry, is required because

the normal VHF and UHF oscillator frequencies for each channel are much too high to be used as a comparison in the phase-locked-loop IC. The prescaler drives the oscillator signal down by 256.

Referring to Fig. 1-4 again, we see the divide-down oscillator signal is applied to a programmable divider in the phase locked loop IC. Here, it is further divided by a variable ratio, to produce an output frequency which becomes the second input to the comparator. The comparator produces an output which is dependent on the differences between the crystal controlled reference signal and the divided down oscillator signal.

The comparator output is a series of pulses with variable duty cycles. These pulses are fed to an active filter circuit. The active filter smoothes these pulses and produces a DC output with a negligible amount of 1 kHz ripple. This DC voltage is in fact the tuning voltage which is applied to the varactor diodes in both tuners. In this manner, the tuner oscillator assumes the stability of the crystal reference.

In order for the comparator to operate correctly, the two input frequencies (tuner oscillator and reference) should be about equal (1 kHz). Since the oscillator frequencies are different for each channel, a different divide ratio must be used for each channel. For example, the channel 2 local oscillator frequency is 101 MHz. In order to yield a 1 kHz output, the signal must be divided by 101,000. The channel 13 local oscillator is at 257 MHz. This frequency must be divided by 257,000 to produce the same 1 kHz signal. This task is accomplished in the programmable divider.

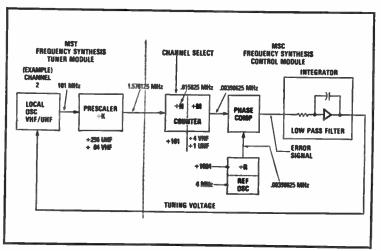

Fig. 1-4. Phase locked-loop block diagram.

The divide ratio is determined by information provided by the microprocessor via four data input control lines. Each time a channel is selected, the microprocessor will put the correct binary control signal on each of the four input lines to establish the correct divide ratio for that particular channel.

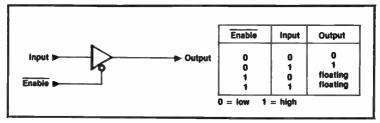

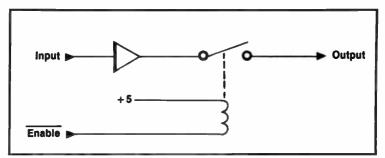

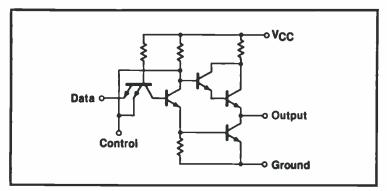

Three data steering input lines are used to determine to which internal registers the binary signals belong. The microprocessor performs many other functions besides controlling the phase-locked-loop IC. Because of this, there may be information on the control input lines which is not meant for the phase-locked-loop IC. The eighth input from the microprocessor is the *enable*. Information on this line permits the phase-locked-loop IC to receive the correct data and exclude all other information.

The 1 kHz pulse width modulated output from the phase locked loop IC is applied to the base of Q1. A Darlington stage is used here to maintain an extremely high input impedance. The output of the collector of Q2 is fed back to Q1 via C14, C15 and R67. This filtered DC voltage at the collector is then routed through Q12, an emitter follower, to provide a low impedance drive to the tuner.

Connected to the base of Q12 is an adjustable clamp circuit. This circuit does not allow the tuning voltage to go below 2.25 volts DC on the high VHF or mid-band CATV channels. Misadjustment of this clamp circuit can cause the tuner oscillator to stall, ultimately making the system to lock-out.

The clamp voltage is set by a potentiometer located on the A-7892 microprocessor module.

The correct adjustment procedure is as follows:

- Set the mode switches to normal.

- Select a high (7 to 13) channel.

- Remove the shielded cable between the VHF tuner and prescaler.

- Adjust the potentiometer for 2.25 volts DC on the tuning voltage

line.

Reconnect the shielded cable.

#### **Keyboard Scanning**

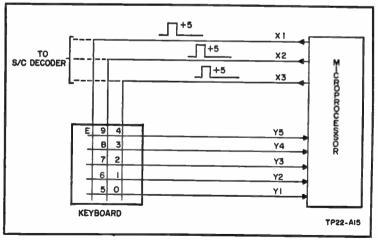

The microprocessor constantly scans the keyboard by sending pulses on three output scan lines. See Fig. 1-5. These lines are arranged in such a way as to represent the vertical, or x axis of the keyboard (three vertical rows of keys). The horizontal, or y axis of the keyboard is represented by five output lines. When a key is depressed, the appropriate x-y contact is made. The contact closure transfers the pulse back to the microprocessor via one of the five output lines. The microprocessor detects the pulse, producing the desired digit on the display.

# Microprocessor Organization

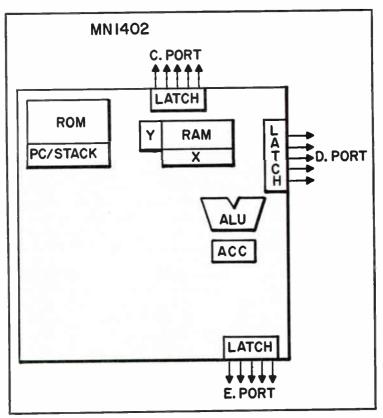

All of these circuits are controlled by a microprocessor which is essentially a small computer. The internal organization of the microprocessor is shown in Fig. 1-6. The microprocessor consists of four major sections:

• The arithmetic logic unit (ALU) performs a sequence of operations determined by commands which are stored in various memory locations. It can do additions, subtractions, comparisons and so forth. It performs these operations one at a time.

• The accumulator (ACC) section of the IC is used by the (ALU) to temporarily store information while it performs its various duties.

• Read only memory (ROM) section contains all the instructions and sequencing information for the *arithmetic logic unit*. This program is designed to do a specific job and it enables a general purpose microprocessor to become suited for use in a tuning system. The ROM section of this microprocessor cannot be changed except by changing the metal mask used in fabricating the IC.

• The random access memory (RAM) however, can be changed. It is used to temporarily store information that can be altered as required. This is necessary because the microprocessor performs numerous functions on a time sharing basis. The microprocessor also has its own internal clock which is set by R6528. The nominal clock frequency is 375 kHz and can be measured at pin 28 of IC6526 with a low capacity probe.

#### **Microprocessor Voltage Information**

All the integrated circuits in this system are powered from two 5 volt regulators on the microprocessor module. One regulator supplies all the

Fig. 1-5. Keyboard scanning block diagram.

Fig. 1-6. Microprocessor organization diagram.

LED current and is turned on and off with the TV set. The other regulator is powered from the remote control power supply which enables the system to have last channel memory.

NOTE OF CAUTION: The IC's in this system are mostly MOS devices and can be damaged by a static discharge. Use care when troubleshooting!

# **ELECTRONIC TUNING SYSTEM (RCA CTC-93 CHASSIS)**

This RCA electronic tuner system utilizes a phase-locked-loop (PLL) in conjunction with a digital frequency programmer to generate a number of discrete frequencies. To better understand the total system let's look at the basic PLL operation.

# **BASIC PHASE-LOCKED LOOP THEORY**

Phase-locked loops have been used for many electronic systems in the past few years. Phase locking is actually a technique of forcing the phase of an oscillator signal to exactly follow the phase of a reference signal. The PLL automatically locks onto and tracks a signal, even though its frequency changes. The PLL does all this with the help of its phase comparator and a voltage-controlled oscillator (VCO). The phase comparator samples the frequency of an input signal with that of a reference oscillator and produces an error voltage directly proportional to the difference between the frequencies of the two.

The error voltage serves two purposes. It is fed back to the VCO and changes its frequency to match that of the input signal. This feedback enables the PLL to lock onto and track the signal. The error voltage can also be considered a demodulated FM output since it varies directly with a shift in the input signal frequency. Thus, the error voltage from the phase comparator permits the PLL to lock onto a frequency, and to track it continually over a given range.

# **BASIC PHASE-LOCKED LOOP OPERATION**

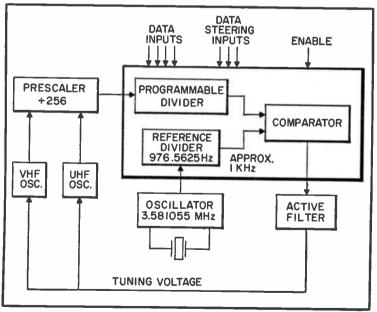

Lets now look at a digital phase-locked loop or *frequency synthesis* (FS) phase-locked loop operation. See Fig. 1-7.

The FS tuning system for a TV receiver includes a phase-locked loop for synthesizing local VHF/UHF oscillator signals. When the RF input receives standard TV frequency carriers, the mixer combines them with local oscillator signals to form IF signals having a picture carrier equal to the nominal IF picture carrier frequency, 45.75 MHz. The PLL includes a local oscillator, a divide-by-K prescaler, a divide-by-N unit, and a divide-by-M unit, operating in conjunction with comparator, reference oscillator reference divider, and a low-pass filter.

The local oscillator, located in the MST tuner module (a voltage controlled type), generates a signal whose frequency is determined by the

Fig. 1-7. Basic phase-locked loop operation.

DC voltage applied to it from the low-pass filter located in the MSC tuner control module.

The output of the local oscillator is coupled to the divide-by-K prescaler which divides the frequency of the relatively high frequency local oscillator. This step is necessary to produce signals whose frequency is compatible with the operating frequency range of the portions of the tuning system following it. Factor K equals 256 for UHF and 64 for the VHF range.

The output of the divide-by-K prescaler is coupled to the divide-by-N unit. The divide-by-N unit performs a number of functions: One of these functions is to divide the frequency of the output signal of the K prescaler, by a number (N), which is equal to the frequency necessary to derive (in the closed loop system) the correct local oscillator signal for the desired TV channel.

The factor N is controlled in accordance with the channel selected via a channel selection unit. The channel select unit may be a keyboard type which can sequentially select the two decimal digits for the desired channel. The channel selection unit converts the selected two-digit decimal number into binary signals arranged in a binary coded decimal (BCD) format. The binary signals are partitioned into a group of four bits (binary digits) for the most significant digit (MSD) and another group of four bits for the least significant digit (LSD). The binary signals are coupled to the divide-by-N unit and are also coupled to a display unit which functions to provide an indication of the channel number selected.

A band decoder (part of the divide-by-N unit) determines the frequency band in which the selected channel resides. A band identification signal, indicating that the selected channel is in the VHF or UHF range, is coupled to the divide-by-K prescaler from the band switch stage to control the factor K (64 or 256).

The output of the divide-by-N unit is coupled to a divide-by-M stage which divides the frequency of the output signal of the divide-by-N unit by 1 for UHF channels and by 4 for VHF channels, in accordance with the state of the signal coupled to it from the band decoder. The output of the divide-by-M is coupled to the phase comparator which provides an output signal comprised of a series of pulses whose polarity and duty cycle represent the phase and/or frequency deviation between the output signal of the divide-by-M divider and the output signal of the reference divider R.

The output of the phase comparator is coupled to an active low-pass filter. This integrates the output signal of the phase comparator, to form a DC signal, which controls the frequency of the local oscillator.

The loop just described is arranged so that the low-pass filter couples a DC tuner control voltage to the local oscillator, which tends to minimize the frequency and phase differences between the output signals of the divide-by-M and reference divider.

#### **AUTOMATIC OFFSET TUNING**

The offset signals sometimes encountered with CATV converters, MATV systems, home video games, and video recorders fall in a range of  $\pm 2$  MHz around the FCC assigned VHF broadcast channel frequencies. These odd signals, however, must be tuned by the receiver.

The following details give the sequence of events involved with frequency synthesis automatic offset tuning. First, the desired VHF channel is selected. The synthesis system (PLL) tunes the FCC assigned frequency for that channel. When a phase lock has been completed, the system switches to an AFT mode for signal searching within the AFT pull-in range. At this time, if a station carrier frequency is within AFT range, the system stays in AFT mode and remains on channel. If a station carrier is not detected, with the oscillator tuned to this center synthesis frequency to produce 45.75 MHz, the synthesis system is again activated. Now, however, the system automatically offsets the local oscillator plus 1 MHz above the nominal FCC frequency and the AFT search mode is reactivated. If lock occurs, the system stabilizes in AFT mode, holding the offset carrier frequency. If lock is not achieved, the system will again go to the synthesis mode, this time tuning the local oscillator to a frequency 1 MHz below the FCC nominal oscillator frequency for the channel. The AFT search is again activated, seeking a station carrier within ±1.25 MHz of this new synthesized oscillator frequency. If a carrier is available, AFT lock is established, otherwise, synthesis again returnes the oscillator to its nominal FCC channel frequency. The system will continue to perform alternate cycles of synthesis (PLL) and AFT in search of a station signal in the sequence just described.

The choice of  $\pm$  1.25 MHz for the AFT control limit prevents the possibility of AFT lockout to the lower adjacent sound carrier (-1.5 MHz) during dropout of the desired stations signal.

In summation:

• A channel is selected, synthesis occurs, tuning the local oscillator to the FCC nominal frequency to receive that channel.

• The AFT search mode is activated. If a station signal carrier is within  $\pm 1.25$  MHz, AFT lock-up is established and the system stabilizes in AFT mode.

• If during AFT search no carrier is available, synthesis is re-engaged shifting the local oscillator 1-MHz high; AFT search is activated, seeking a station carrier. If available, AFT lock-up is established and the system stabilizes.

• If lock-up is not achieved, the system now tunes the oscillator 1 MHz lower than nominal. AFT search is set in the same sequence as in the previous high offset mode.

• A third failure to get an AFT lock will return the system back to the FCC nominal frequency. There it will do alternate cycles of synthesis (PLL) and AFT in search of a signal, but with no further stepping. If AFT lock is established for 3 seconds, further stepping is prevented.

# DC TUNING VOLTAGE AND PRESCALER FREQUENCY

A DC tuning voltage and prescaler chart for VHF low, VHF high, and UHF is shown in Fig. 1-8. Use this voltage chart when troubleshooting electronic tuner troubles in this system. The DC tuning voltage is connected to the MST 001 tuner module at point P1. Tuning voltage is developed on the MSC control module, which is part of the synthesis tuning loop.

If a tuning voltage problem exists, remove power then check with an ohmmeter. Check point J1 to see if the tuning voltage is being shorted out. If not, sub in a battery or power supply. This will serve as a tuning voltage source and will check operation of the tuner. Also, check for correct band switch voltage. Now the desired station can be tuned in by adjusting the battery or power supply to the desired tuning voltage as shown in Fig. 1-8. With this set-up the prescaler frequency can now be checked with a frequency counter. If the tuner module checks out good, the problem is probably in the MSC control module.

#### **BAND SWITCHING**

Because of the limited tuning range of varactor diodes, it remains necessary to provide band-switching capability to select the low band VHF channels (2 through 6), the high band VHF channels (7 through 13) and the UHF channels (14 through 83). This is accomplished by applying +19 volts to the appropriate band-switching terminal. Refer to the band-switching chart in Fig. 1-9. Also included on the chart is the Mixer B+ voltage for each tuning band.

#### **LED DISPLAY**

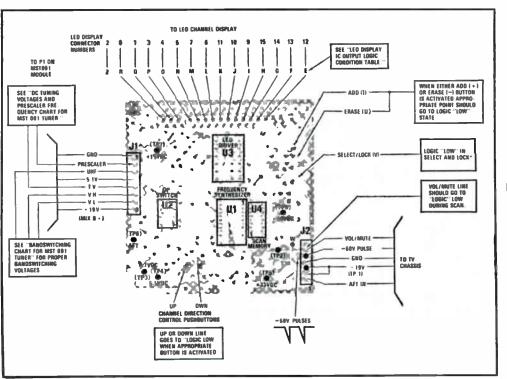

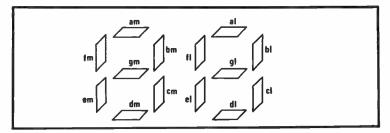

The LED display decoder driver IC is used to drive a two-digit, seven-segment LED channel indicator. Eight lines of *binary coded decimal* (BCD) information are supplied to the IC located as part of the MSC control module to allow continuous, non-multiplex operation. The code which relates to the input and output states is the standard BCD-to-seven segment code which activates the appropriate segment or segments. Figure 1-10 gives the logic condition or output code of the LED display driver IC. If a problem occurs resulting in loss of, or incorrect LED display, Fig. 1-10 will aid in determining if the problem exists in the MSC module or LED assembly.

#### **SERVICING THE SCAN F S CONTROL MODULE**

In the following checks assume that the MST 001 tuner module and IF link cable are operating properly.

#### Scan Control Module Symptoms

• Channel selecting problems in either VHF low, VHF high, or UHF bands.

Channel selecting capability lost on all channels.

• Channel selecting OK - LED display is incorrect or segments missing.

| CHANNEL                     | TUNING VOLTAGE<br>(TYPICAL)                                                                                                                  | PRESCALER FREQ<br>(MHZ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                           | 1.8                                                                                                                                          | 1.58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>5                      | 5.4<br>11.4                                                                                                                                  | 1.76<br>1.92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>* * * * * * * * *<br>7 | *******                                                                                                                                      | 2.01<br>***********<br>3.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8                           | 9.6<br>11.0                                                                                                                                  | 3.54<br>3.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11                          | 12.6<br>14.6                                                                                                                                 | 3.73<br>3.84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13<br>******                | 17.5<br>22.0<br>★★★★★★★★★★                                                                                                                   | 3.92<br>4.01<br>* * * * * * * * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14<br>24<br>30              | 1.8<br>3.8                                                                                                                                   | 2.02<br>2.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 43<br>53                    | 8.4<br>10.5                                                                                                                                  | 2.48<br>2.69<br>2.93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 63<br>73<br>83              | 13.4<br>17.0<br>24.0                                                                                                                         | 3.16<br>3.40<br>3.63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                             | 2<br>3<br>4<br>5<br>6<br>* * * * * * * *<br>7<br>8<br>9<br>10<br>11<br>11<br>12<br>13<br>* * * * * * * *<br>14<br>24<br>34<br>43<br>53<br>63 | CHANNEL         (TYPICAL)           2         1.8           3         3.3           4         5.4           5         11.4           6         16.0           * * * * * * * *         * * * * * * * * *           7         8.5           9         11.0           10         12.6           11         14.6           12         17.5           13         22.0           * * * * * * * * * *         * * * * * * * * * *           14         1.8           24         3.8           34         6.3           43         8.4           53         10.5           63         13.4           73         17.0 |

Fig. 1-8. Tuning voltage and prescaler frequency chart.

- Improper or no volume-mute.

- No tuning voltages to MST 001 tuner.

- Channel selecting OK, but tuning system hunts.

# **Service Procedures**

Check all interface connections and wiring to and from MSC control module. Make sure that channel entered is a valid entry. Each time a channel entry is made, note the display readout. This visual indication can prove to be a useful aid in tracking down a particular problem.

# Channel Selecting Problems (VL, VH, or UHF Bands)

The above problems usually indicate a defect in either the MSC or MST modules. Check appropriate bandswitch voltages on the MSC

| TV<br>TUNING BAND | MIXER<br>8 +<br>(J1-8) | VHF LOW<br>B +<br>(J1-7) | VHF HIGH<br>B+<br>(J1-6) | UHF<br>B +<br>(J1-3) |

|-------------------|------------------------|--------------------------|--------------------------|----------------------|

| VHF LOW (2-6)     | + 19V                  | + 18V                    |                          |                      |

| VHF HIGH (7-13)   | + 19V                  | + 18V                    | + 19V                    |                      |

| UHF (14-83)       | + 19V                  |                          |                          | + 19V                |

Fig. 1-9. Band switching chart.

|                                                    | tm gm br<br>em dm cn                                                                                                                                 |                                                |                                                                                                                                 |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| LEFT OIGIT                                         | LINES LOW<br>(MSC BOARD)                                                                                                                             | RIGHT OIGIT                                    | LINES LOW<br>(MSC BOARO)                                                                                                        |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br> | L.M.R.Q.P.O<br>M.R<br>L.M.N.P.Q<br>L.M.N.R.Q<br>O.N.M.R<br>L.O.N.R.Q.P<br>L.M.R<br>L.M.R,Q.P.O.N<br>L.M.R.Q.P.O.N<br>L.M.R.Q.P.O.N<br>L.M.N.O.R<br>N | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | E,J,I,H,G,F<br>F,G<br>E,F,K,I,H<br>E,F,K,G,H<br>J,K,F,G<br>E,J,K,G,H<br>E,J,K,G,H,I<br>E,F,G<br>E,F,G,H,I,J,K<br>E,J,K,F,G<br>K |

Fig. 1-10. LED display IC output logic condition table.

module. If proper bandswitch voltage appears, sub in a new tuner module. Check the proper keyboard data lines that go to logic low when buttons are depressed on the keyboard. Logic low condition means voltage goes low, to about .2 volts or lower.

#### **Channel Selecting Capability Lost On All Channels**

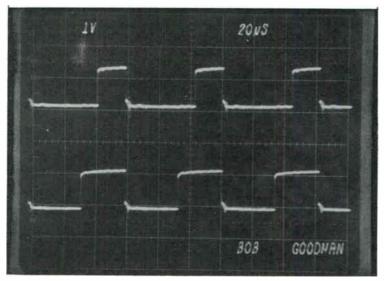

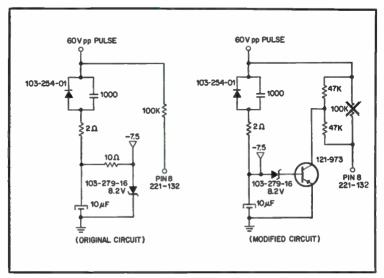

First check that all DC operating voltages are present. Most DC voltages for the MSC 001 are derived from the negative 60 volt horizontal pulse. These pulses are scan derived from the sweep deflection system and can be checked with an oscilloscope. Next, check keyboard data lines; if ground is not available to the keyboard assembly, channel select capability is lost.

# Channel Selecting OK - LED Display Not Correct

When the tuner responds to the correct commands and the display does not, check appropriate outputs from the MSC board. Note LED display output logic condition in Fig. 1-10 for data regarding logic condition of display driver IC located on MSC 001 module. Replace module if incorrect logic conditions are found on the MSC module. If the correct logic conditions are found on the MSC module, then the channel display assembly may be defective.

#### Improper Or No Volume Mute

Check volume-mute line at J2 for a momentary "dip" toward a logic "low" condition which should exist when a channel change is initiated. If not, check plug connections and then try new MSC module. Voltage at J2 should be about +2 volts during normal station reception.

#### No Tuning Voltages to MST 001 Tuner

Replace tuner control module or sub in a battery and potentiometer, or power supply in place of the tuner voltage. Remember that proper bandswitch voltage must be present to perform this test. Refer to Fig. 1-8 for proper tuning voltages and prescaler outputs.

## **Channel Selecting OK-Tuning System Hunts**

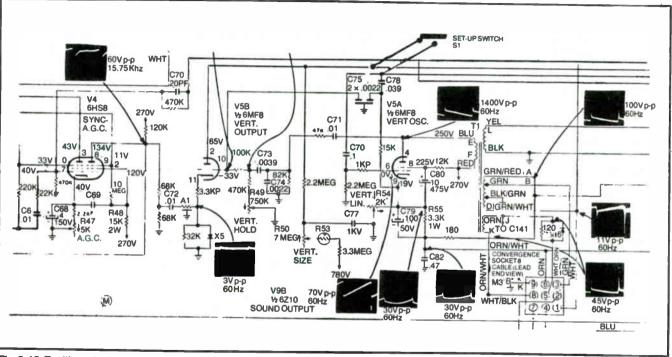

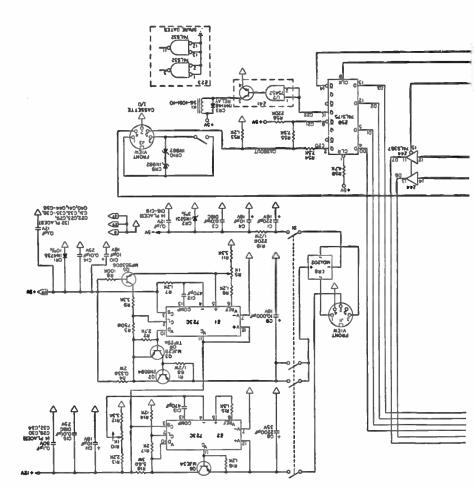

This type situation usually indicates an AFT problem. Tuning capability is not lost, but picture will drop in and out rapidly, or hunt. Check AFT voltage at J2 on the MSC module. DC voltage should measure about +6 volts and should be stable with a strong TV station tuned in. Problem could be related to IF/AFT on main chassis or MSC control module. For other voltages and waveform information refer to the scan FS control module in Fig. 1-11.

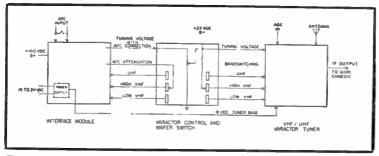

## **ELECTRONIC TUNING SYSTEM (VARACTOR) GE ET-20 SYSTEM**

Three functional blocks make up the GE ET-20 system as shown in Fig. 1-12. The varactor tuner is designed to tune three separate frequency bands which are activated, one at a time, by the application of +22 volts to the proper tuner terminals. These bands are as follows:

Channels 2-6 54-88 MHz (low VHF)

Channels 7-13 174-216 (HIGH VHF)

Channels 14-83 470-890 MHz (UHF)

The band switching voltage is fed by means of a wafer switch, controlled by the channel selector knob. The tuning of a specific channel within the frequency band selected is done with potentiometers in the varactor control assembly.

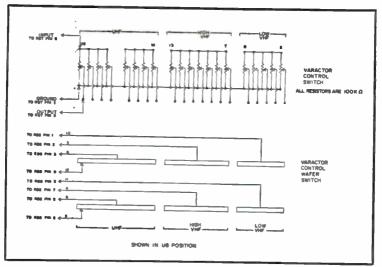

The varactor control assembly, shown in Fig. 1-13 contains not only the bandswitching wafer switch, but also has twenty slide-type pots arranged on a cylinder. The wipers of each pot are mechanically engaged, one at a time, by an external tuning knob. The wipers are electrically connected to an output terminal on the assembly.

There are a different number of pots in parallel for each band. Five on the low VHF band, seven on the high VHF band, and four on each of the two UHF sections.

Each of the pots, once mechanically and electrically engaged, is capable of tuning in any channel within the selected frequency band.

The VHF channels are normally pre-tuned sequentially from the low to the high channels in order to match the numerals on the channel readout drum, and also to line up the red indicator with the white marks on the tuning dial.

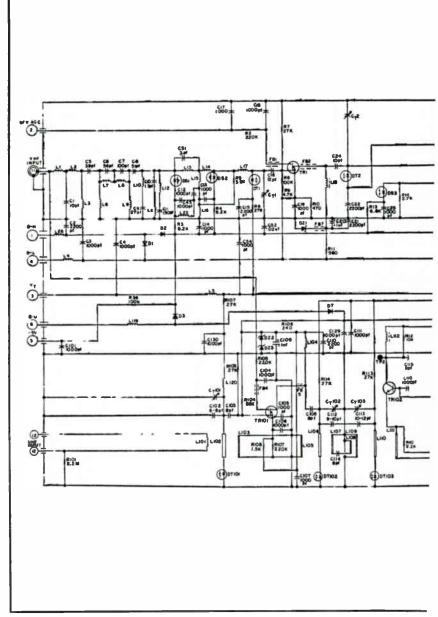

Fig. 1-11. Scan FS control module.

Fig. 1-12. Block diagram of ET-20 electronic tuning system.

The wafer-type bandswitch is mechanically connected to the potentiometer drum and, in addition to activating the proper tuner band with +22 volts DC, it also helps provide the system with the voltage needed to maintain the correct AFC range for each band. Each band requires a different amount of AFC voltage for 1 MHz of pull-in range.

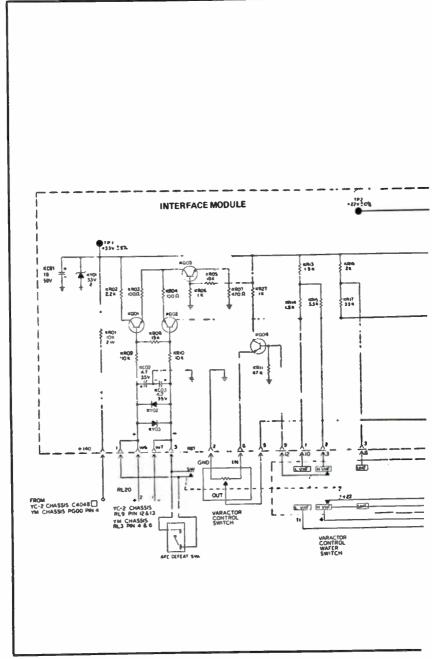

The interface module shown in Fig. 1-14, contains the circuitry necessary to process the AFC and switching voltages required by the varactor tuner.

The AFC voltage from the main TV chassis IF module is applied to the network of KY02 and KY03. These diodes limit the differential voltage variations to 0.6 volts.

The differential amplifier stage KQ01, KQ02, and KQ03 modifies the AFC from a double ended to a single ended voltage source present at the collector of KQ02. Because of the requirement for AFC correction voltage

Fig. 1-13. Varactor control assembly diagram.

Fig. 1-14. Interface module diagram.

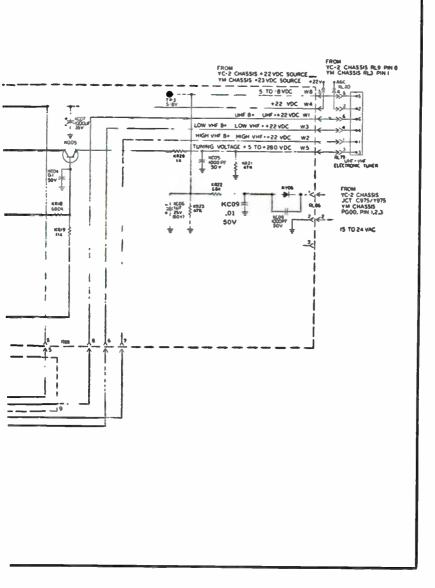

Fig. 1-15. GE Varactor electronic tuner circuit.

decreases, from the low to high channels, three levels of attenuation are needed. These are provided by voltage-dividing resistors and are switched by the varactor control bandswitch to the base of KQ04. The divider network KR16 and KR17 is used for AFC level correction on the UHF band. KR13 and KR15 are used to attenuate the voltage for high VHF channels, while the collector voltage of KQ02 is used directly on the VHF low band channels.

The varactor control (tuning pots) tunes in the selected channel frequency by setting the voltage level required at terminal 3 of the varactor tuner via the buffer stage KQ05. The tuning voltage is altered by KQ04 in direct proportion to the AFC correction voltage present at its base.

A bias voltage which can vary from -5 to -8 volts DC is applied to terminal 5 of the varactor tuner. This voltage is developed by KY06 and its associated circuitry. The bias prevents the tuner from producing unwanted oscillations under certain conditions. The complete circuit for the VHF -UHF Varactor tuner is shown in Fig. 1-15.

Several different manufacturers offer remote controls for TV receivers. This chapter covers some of the more popular models.

# DIRECT ACCESS REMOTE CONTROL (ZENITH 2000 SYSTEM)

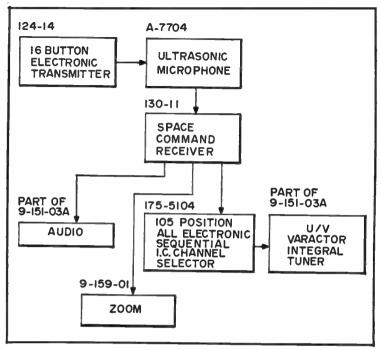

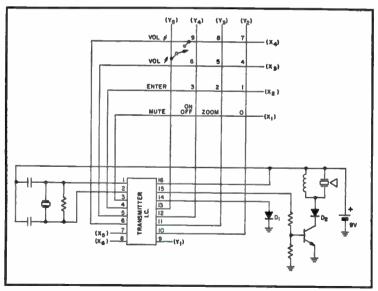

This remote control system will be found in the Zenith color TV set L models. This direct access remote hand unit transmitter is a 16 button keyboard unit that is shown in Fig. 2-1. The functions include on, off, zoom, mute, volume higher and volume lower (continuous through 128 steps), plus channel entry buttons. The frequencies associated with the transmitter are given in Fig. 2-2. A block diagram of the 2000 remote control system will be found in Fig. 2-3.

#### **Remote Hand Unit**

The 124-14 hand unit transmitter is powered by a 9 volt battery. The 16 pin P-MOS digital IC is the heart of the transmitter. The IC senses any switch closures, scans the keyboard to determine which switch is closed, determines that the closure is valid, determines the X and Y coordinates of the closure, converts it to a 5 bit binary number which is used for gating internal counters to generate the desired ultrasonic frequencies. A simplified drawing of the hand transmitter is shown in Fig. 2-4. The output circuit is operated as a class C stage where pulses are applied to the tuned circuit of the ultrasonic speaker and output coil.

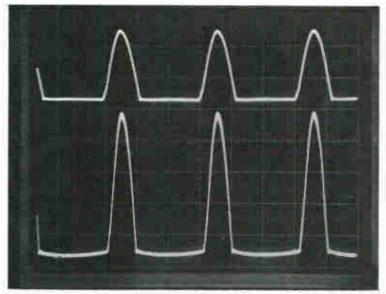

The best technique for testing a transmitter is to connect an oscilloscope to the microphone/preamplifier output. With the transmitter about one foot from the microphone, all buttons should provide a square wave signal which indicates the microphone/pre-amplifier is limiting the strong input signal.

Fig. 2-1. Zenith 2000 remote transmitter.

| Button      | Frequency (±15Hz) |

|-------------|-------------------|

| 0           | 37.150 KHz        |

| Zoom        | 37.497 KHz        |

| On/Off      | 37.843 KHz        |

| Mute        | 38.190 KHz        |

| 1           | 38.537 KHz        |

| 2           | 38.883 KHz        |

| 3           | 39.230 KHz        |

| Enter       | 39.576 KHz        |

| 4           | 39.923 KHz        |

| 5           | 40.270 KHz        |

| 6           | 40.616 KHz        |

| Volume Up   | 40.963 KHz        |

| 7           | 41.309 KHz        |

| 8           | 41.656 KHz        |

| 9           | 42.003 KHz        |

| Volume Down | 42.349 KHz        |

|             |                   |

Fig. 2-2. Frequency chart for Zenith 2000 remote system.

Fig. 2-3. Block diagram for Zenith 2000 remote system.

Fig. 2-4. Circuit for 124-14 hand unit.

#### **Microphone Amplifier Unit**

This portion of the remote system consists of an ultrasonic microphone and a three stage solid-state amplifier. The wider bandwidth requirements of the direct access system have been accomplished by minute changes in the size of the microphone bridge. There is a range control located on the back of the unit that should *not* be adjusted to a *more* sensitive level than the factory setting but may be adjusted to a *less* sensitive level. Good shielding is required and the original shield cover must be retained in place. The B+ is provided directly from the +12 volt position regulator Q201 located in the remote receiver module.

## **Remote Control Receiver (130-11)**

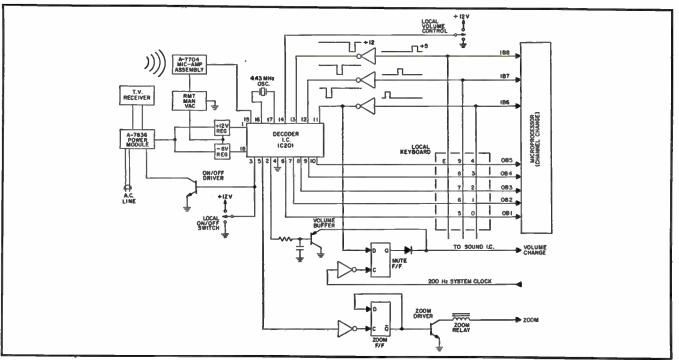

The direct access receiver is made up of two digital integrated circuits and 12 discrete transistors. Power is supplied by two series voltage regulators, Q201, a +12 volt supply, and Q202 a -6 volt supply. Both supplies will provide 40 ma of current. Follow along with this circuit operation by referring to the block diagram of the remote receiver in Fig. 2-5.

The digital P-MOS chip, IC201, processes the received ultrasonic signal and provides direct channel selection by interfacing with a microprocessor. It also controls auxiliary functions such as on-off, volume, mute and zoom.

Since the IC uses a 12 volt supply and the microprocessor a 5 volt supply, level shifters Q203, Q204, Q205, convert positive-going 5 volt scanning pulses from the microprocessor to negative-going 12 volt pulses on pins 11, 12, and 13 of the decoder IC.

A second IC, IC202, is a dual type C-MOS flip-flop. This is required as a memory storage bank for the **mute** and **zoom** functions. This allows continuous operation of the **mute** and **zoom** functions with only momentary depression of the buttons. The outputs available from the decoder IC are high only as long as these buttons are pushed. Hence, the need for storage in a flip-flop.

Transistors Q209 and Q210 are used as current amplifiers to increase the small current capability of the C-MOS flip-flop to that required to pull in the zoom relay.

Another level shifter, Q207, changes the 5 volt 200 Hz clock signal, from the microprocessor, into a 12 volt signal. This is required to gate the **mute** function into the **mute** flip-flop. Basically the microprocessor detects the **mute** function by scanning and then sends this function to be stored in the **mute** flip-flop.

Another inverter, Q208, is used to convert a negative-going transition occurring on pin 5 of the IC into a positive-going transition to clock in the zoom function.

A transistor, Q206, is used as a switch for activating a reed relay in the power module, which gates a Triac for turning the TV set on or off.

37

This transistor can be changed from the off state to the on state either by remote control or manually by the local on-off switches.

The amplified ultrasonic signal from the microphone amplifier assembly is fed to the top end of R224, the trip point adjustment control. This control is factory set, using a standard 200 millivolt RMS signal to compensate for differences in individual chip sensitivity. This control should not be adjusted without proper instruments.

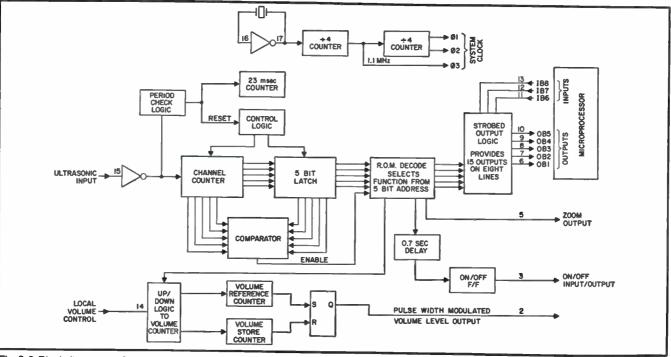

### **More System Operation Notes**

Whenever an ultrasonic signal is fed into pin 15 of the IC201 (Fig. 2-6) a long chain of events begins to take place. After an ultrasonic signal has been received by the chip it begins a measurement cycle. During the first 23 milliseconds, the chip ignores (does not count) the signal and it is basically inactive. This is to allow any room transients to decay. However, the measurement cycle taken during the first 23 milliseconds determines if the received signal has a period which is longer than the minimum requirement of 18 microseconds yet shorter than 36 microseconds the maximum value of a valid signal. If the ultrasonic signal duration is less than 23 milliseconds or the period does not fall within the above limits the chip will not respond. If the ultrasonic signal has a valid period and is longer than 23 milliseconds duration a channel counter counts the number of ultrasonic pulses occurring during the next (2nd) 23 ms period. This value is then transferred to a 5 bit latch and the channel counter counts pulses for another (3rd) 23 ms period. At the end of the second counting period (3rd 23 ms period) the contents of the channel counter are compared to the previous value stored in the 5 bit latch. If a comparison does not exist, then another measurement is made, followed by yet another measurement, if there is again no comparison. Thus, there are three opportunities to obtain a comparison between two consecutive measurements. This is recognized as a valid ultrasonic input and the ROM decoder is enabled and the appropriate output appears.

A check on the period of the ultrasonic signal is made continuously. If, at any time, an ultrasonic pulse is received which has a period less than 18 microseconds or greater than 36 microseconds then the check period logic produces a signal which resets all control and measurement logic and inhibits the output stages.

The zoom output, pin 5 of IC201, is simply a buffered decode from the ROM. The on/off output, pin 3, is toggled by the appropriate ROM output after a delay of 0.7 seconds. The on/off pin is bi-directional since it also acts as an input pin. The external switches force the on/off pin to a particular state, the change is sensed by the chip and that level is held when the input is removed.

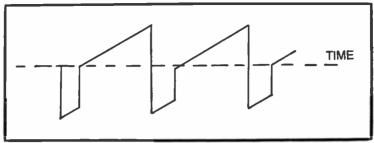

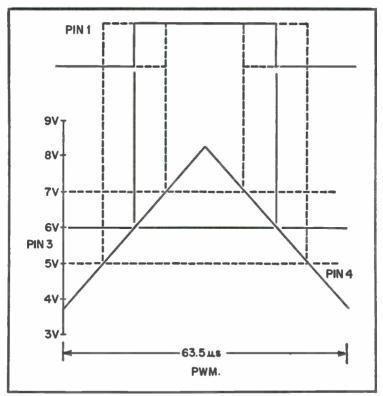

The pin 2 volume out is a 8.7 kHz square wave output with a variable duty cycle. At power-up the duty cycle is essentially 50 percent. This output is filtered by an integrator and applied to the base of the volume

Fig. 2-6. Block diagram of IC 201 in remote receiver.

39

buffer to control the TV volume level. The duty cycle is controlled by two free counters, a reference counter and a store counter. A volume up or volume down command increments the reference or store counter respectively so that there is a resultant change in the duty cycle of the output signal. In order to prevent blaring when the set is first turned on, a separate adjustment control, off emitter Q212 connector 11, (factory adjustment) is provided to compensate for any sound IF chip variations. The manual volume input pin 14 of the IC201 is also tri-state (like the on/off) and the volume is changed by forcing the pin to +12 volts or ground.

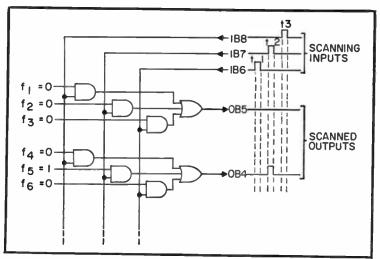

In order to conserve pins on the IC, 15 possible outputs are read via 8 pins. This is accomplished by arranging the pins as three input and 5 output scan lines. Refer to Fig. 2-7. If, for example, the desired function is f5 (digit 5) then by scanning, it is possible to read f4, f5 and f6 on one line i.e., OB4. The microprocessor does this by sending pulses separated in time such as t1, t2 and t3. During t1 only the END gates activated by t1 could be read out, namely f3 and f6. During t2 functions f2 and f5 may be read out. In this case f5 is high and this is shown as a high only during the time t2 is high. Since the microprocessor keeps track of which pulse is being sent, it knows which function the remote has decoded. By this means the digits 0 through 9, enter and mute are detected. As mentioned, mute is returned to be stored at the mute Flip/Flop during the negative transition of the 200 Hz system clock.

## **Service Tips**

If set will not turn on check out the power supply module for the remote system. Check fuse, reed relay and Triac. Next, check for correct B+ voltages to the remote module. If set operates manually then see if the remote hand unit is transmitting the correct signals. If these checks are OK and the remote system seems dead check for the proper 200 Hz clock signal. Then suspect the microprocessor chip and the decoder IC, IC201.

# MSC-003 FS SCAN REMOTE CONTROL (RCA)

The MSC-003 FS scan remote control module is used in the RCA CTC-93 color TV receivers. This unit works with the keyboard, remote receiver and preamp unit that makes up the total remote control system.

#### **Control Module Symptoms**

No or improper channel Up/Down action. No or improper ADD or ERASE of scan memory. No or improper channel change or skip.

### **Preliminary Service Information**

Check all interface connections and wiring to and from the MSC control module. Each time the channel is changed note the display readout.

This visual indication can prove to be useful in tracking down various remote control problems.

# No or Improper Channel Up/Down Action

Scan up and down channel information requires that frequency synthesizer chip (U1) receive proper logic conditions to pins 16 and 17 (from scan channel switch). First, confirm good ground connection at terminals on the MSC-002 module and to up/down switch assembly. If ground connection is open, Scan capability is lost. If either up or down action is lost, check appropriate terminal on MSC-002 module for logic low condition when the correct button is pressed.

## No or Improper Add or Erase of Scan Memory

Confirm that proper logic conditions at terminals T and U on the MSC-002 control module are being made. Make sure select-lock switch is in select position and that there is a good ground connection at all terminals on the MSC board. The appropriate add or erase line must go to logic low condition to indicate an add or erase function to the Scan Memory IC (U4). When add or erase functions are not activated, add and erase lines should be idle at logic high (+5 volts DC).

# No or Improper Channel Change or Skip

These problems are usually associated with the MSC-002 control module. If quick voltage checks do not pin down the problem the best bet is to replace the MSC-002 control module.

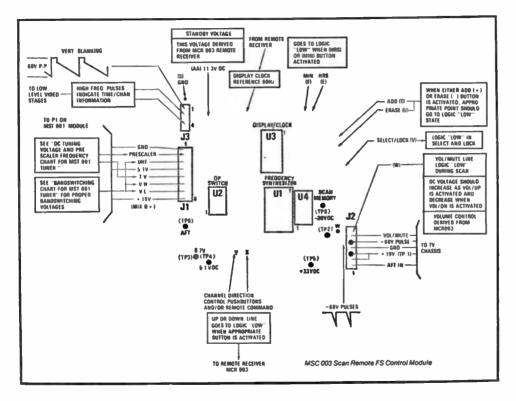

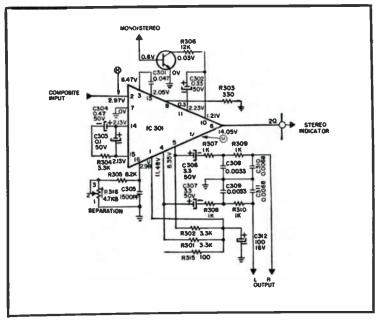

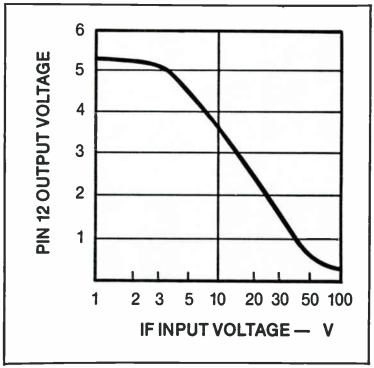

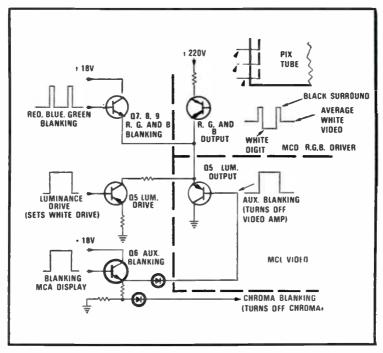

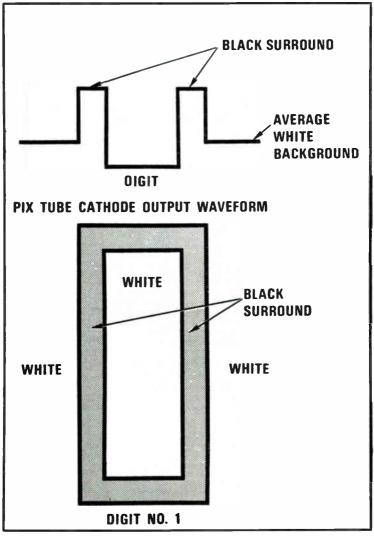

The FS scan remote system (see circuit with voltage and waveform notes in Fig. 2-8) utilizes a frequency synthesizer chip (U1), Op/Amp chip (U2), Memory chip (U4), and an on-screen channel display/clock chip

Fig. 2-7. Strobed output logic.

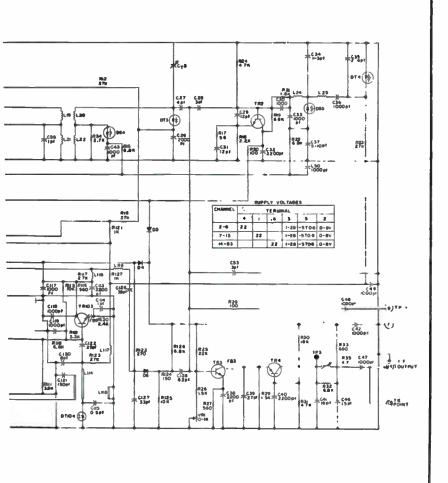

Fig. 2-8. RCA scan remote control module.

(U3). These IC's and associated components make up the MSC-003 tuner control module for the Scan Remote System. With this system, we will now look at the display/clock interface and other remote servicing procedures. Again, much of the circuitry in the system is similar to that found in the keyboard and scan systems. To locate problems, use the isolation techniques to help you pinpoint the portion of the system that is at fault.

The scan remote system includes the MCR-003 remote receiver which utilizes the remote decoder IC that is not shown. This IC processes channel up/down, set on/off, and volume up/down information from the remote control unit via the preamp unit, and sends appropriate voltages to the MSC-003 control module. The remote receiver also processes function commands from the manual pushbutton assembly located on the TV receiver. Also, located on the remote receiver is a +11 volt DC regulator (Q1101), which provides DC voltages to the remote receiver and preamp board (as long as the TV receiver has AC power connected).

A separate power supply transformer (T1) located on the remote receiver assembly provides AC power (12 volts) to regulator Q1101 for standby and operation voltage to the remote receiver and preamp. Relay K1 provides on-off AC power to the TV receiver.

#### **Remote Module Symptoms**

Unable to set time (hours or minutes). Erratic display, loss of time display. No channel up/down - Remote. No channel up/down - Manual buttons. No channel up/down - Remote or Manual. No or improper volume up/down - Remote. No or improper up/down - Manual buttons. No or improper volume up/down - Remote or Manual. No remote control action. No on/off action from either remote or manual buttons.

#### Service Checks

Check all interface connections and wiring to and from the MSC-003 control module, remote receiver MCR-003, Preamp MCY-003, and other assemblies associated with this system.

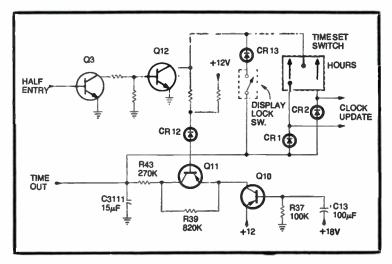

## **Unable To Set Time**

Display problems can be defined as a loss of, erratic, or distortion on screen digit display with otherwise normal operation. Such problems are usually confined to the clock and display IC located on the MSC-003 control module or to connector problems. If these problems are encountered, replace the MSC-003 module. A defective display assembly may also cause instrument video problems on the sets screen. If video problems are suspected as being caused by the display system, remove connector P3-MSC and see if the problem has been cleared.

Failure of the system to maintain the correct time-of-day is a comparatively improbable situation without any other symptoms being evident.

## Make Following Checks If A Problem Is Encountered:

Check for possible intermittent power interruptions. If power to the TV set has been interrupted, the time-of-day displayed will be lost when power is restored - requiring the clock to be reset.

Check the time-set switches and cabling for any possible intermittent connections.

If the clock and display is not operating properly, then check for proper DC voltages around the pins of the U3 IC located on the MSC-003 module. If no reason for an incorrect DC voltage can be found then the U3 IC chip may be defective and will have to be replaced. If the chip is hot to the touch it may well be defective.

## Remote Scan Turn On/Off Problem Notes

In the scan remote system the MCR-003 is used in the CTC-92 and 93 chassis and the MCR-004 is used with the CTC-97 chassis. Repair of the remote receiver is accomplished by the substitution of the remote amplifier module.

Because the CTC-92, 93 and 97 chassis are of the Extended-Lifedesign, a no-turn-on symptom can, of course, be a fault in the TV chassis rather than the remote receiver module. Thus, it is good to use a simple procedure to assist in locating the exact fault area.

The triac is not used in the FS Scan remote systems. Instead, a relay is used as the off/on switch.

The relay driver or switch in each case is a transistor, again controlled by preceding logic circuitry. The relay driver in the MCR-003 is a PNP device with the emitter connected to the 16 volt source through the relay winding. Thus, if the emitter is connected to ground with a clip lead, the TV set should turn on. The relay driver in the MCR-004 is essentially an NPN device so that the collector lead may be shorted to ground to turn-on the set.

You may think the above procedure is not required because an audible click is heard from the relay when the on button is depressed. However, this is not always so. Don't forget that an audible click does not rule out the possibility of oxidized or otherwise defective relay contacts. Of course, this type of problem can be isolated simply by shorting the relay contact terminals 2 and 5 together. If the set does not turn on with this test, the problem is within the TV chassis.

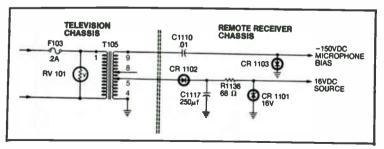

# **REMOTE RECEIVER POWER SUPPLY (RCA CTC-48-68)**

We will now look at some RCA remote control power supply circuits and service tips used in the CTC-48 through CTC-68 chassis series. These sets have the stepper system circuits.

## **Power Supply Circuit Analysis**

As you will note in Fig. 2-9 there is nothing complex or unusual about this power supply circuit. The primary of the remote power transformer, T105, is protected from an overload by a .2A fuse, F103. A metal oxide varistor, RV101 is across the AC line to protect the triac and other devices from any power line surges and spikes. You may want to add a MOV to any sets you find that do not have one in place, especially if you have had line surge damage to the triac and/or remote receiver devices. Addition of the MOV will help insure against other component failures. Make sure you add the MOV after, and not ahead of, the fuse.

Approximately 12 volts AC from terminal 5 of the secondary of T105 is rectified by CR1105, filtered by C1117, and Zener diode regulated to 16 volts DC by CR1101. The set cannot be turned on either by the manual off/on button or by the remote transmitter if this 16 volt DC supply is missing. If the supply is absent just check with an Ohm meter to confirm the presence of an open or shorted condition in either the rectifier or the Zener diode. If either of the devices is shorted, the .2 A fuse will be open. An AC voltage check at T105, pin 5, will reveal any possibility of a defective power transformer, although the line surge required to damage the device is usually very high.

One somewhat unusual symptom is that as long as the off/on button is held depressed, the set will remain on with distortion in the sound. As soon as the button is released, the set will turn off. An open C1117,  $250\mu$ F capacitor, is probably the cause of this symptom.

The top of the remote power transformer secondary, pin 9, delivers AC which is rectified and used to supply -150 volt DC bias to the high impedance remote receiver microphone or transducer. If this supply is not present, or very low, the sensitivity of the remote receiver will be greatly reduced.

## Caution

When measuring this bias voltage, use a meter with a high input impedance like a FET or VTVM. A volt-ohm meter will load the circuit and give a lower reading than the true voltage value. If the supply voltage is

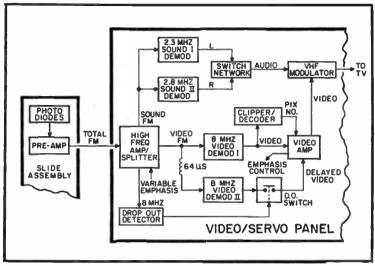

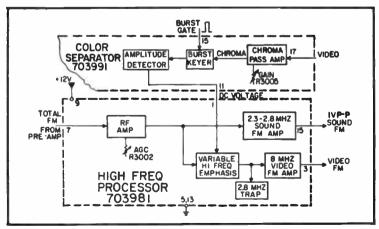

Fig. 2-9. Power supply circuit for remote receiver.

low or missing, possible causes are a leaky or shorted CR1103 or a defective remote preamp module.

## REMOTE CONTROL LOGIC SYSTEMS (RCA CTC-74, B1 CHASSIS)

We will now discuss the stepper system used in several RCA color TV remote control systems. These electronic control systems contain gates which are used to allow remote manipulation of the on/off, channel change, volume level, color level and tint control range. Some combinations of these control functions are used in all RCA remote control systems. This logic circuitry in the later models is modular in design so that most repairs can be completed with a simple module change.

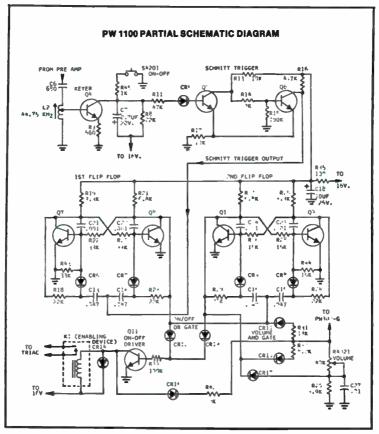

One of the least complex and most widely used logic circuits found in the RCA remote systems is the volume stepper system. Because it is not a plug-in module and must be repaired by the technician we will look at its circuit operation and give some troubleshooting information. Now, follow along with the partial stepper circuit shown in Fig. 2-10.

## **Volume Stepper**

In the volume stepper, two flip-flops or bi-stable multivibrators controlled by a pulse from the Schmitt trigger ultimately determine the logic state of an OR gate which controls the on/off function of the main TV receiver. The OR gate consists of diodes CR12 and CR13, one or both of which must be on (forward biased) to hold the on/off driver, Q11, in saturation. When this transistor is held in saturation, the enabling device is energized to provide the triac gate pulse.

Another pair of diodes controlled by flip-flops, CR10 and CR11, comprise an AND gate which steps the volume through three levels. In series with each of the diodes is a resistor which is switched in parallel with the volume control when that particular diode is forward biased. The smaller the total resistance, the louder the volume. Therefore, when the set is first turned on, the volume is at maximum because CR10 is forward biased by the on condition of Q10 (collector is at logic low). Resistor R30, which is in series with CR10 is the smaller of the two. With the second push of the stepper switch, CR11 is forward biased by conduction of Q8 placing R31 across the volume control. Since the total volume control resistance is thus increased, the set is now at medium volume. With the third push of the stepper switch, Q8 and Q10 are off. Because neither resistor now parallels the volume control the TV sound level is now lowest (muted).

Again, referring to Fig. 2-10, we see the collector of the keyer transistor; Q4, may be taken low either by base bias provided by an ultrasonic signal from the remote transmitter or by manual activation of the stepper switch. The rather poorly shaped pulse produced, will reverse bias CR5 and turn off Q5, the first transistor in the Schmitt trigger. The second transistor in the Schmitt trigger, Q6, which is normally held off by the saturated state of Q5, turns on and a square wave is thus produced. The primary purpose of the Schmitt trigger is to square up the poorly shaped

pulse from the keyer transistor. This square wave, of course, is used to provide gating for the first flip-flop.

The flip-flop is a bi-stable circuit which can exist in either of two stable states indefinitely and has a memory. When power is first applied to the flip-flop, the transistor that conducts first is the one with the larger collector load resistor. It will remain in that state with one transistor on and the other off until it receives a gate pulse. It will then switch states and remain so until the next gate pulse. Gating for the first flip-flop is provided by the Schmitt trigger. The gate pulse for the second flip-flop is provided *only* when the second transistor in the first flip-flop is *on*. Therefore, while the first flip-flop changes state with every push of the stepper switch, the second flip-flop changes state only every *second* push of the switch.

As shown in Fig. 2-10, CR12 conducts when Q8 is off (collector high) and CR13 conducts when Q10 is off. Therefore, the TV set remains on as long as either or both transistors are off.

Fig. 2-10. Partial schematic of an RCA remote unit.

From the preceding information, it appears that the entire system is a complex switching network. Indeed, any logic gate may be schematically represented as a switch. It must be remembered, however, that either logic high or logic low can be chosen as the *on* state.

Since the collector of any transistor in the system is at **logic high** when the transistor is *off*, the logic low condition may be simulated simply by shorting a certain collector to ground. Referring to the schematic in Fig. 2-10, you can see that when the TV set is off, Q4, Q6, Q7, and Q9 are all off. All things being normal, we need only to momentarily short the collector of one of those transistors to ground to turn on the TV set. Because of the memory characteristic of the flip-flop, the set will remain on until it receives another command. Using this clip lead method, it is possible to step the system through the four separate states shown on the chart. Also, this method will help you to determine whether a particular circuit - the keyer, the Schmitt trigger, or one of the flip-flops - is defective.

### Turn On/Off Problem Notes

The entire remote control receiver circuitry in the Frequency Synthesis Scan System is contained on one of two modules. The MCR-003 used with the CTC92 and 93 chassis and the MCR-004 used with the CTC97 chassis. Repair of the remote receiver is accomplished, of course, by the substitution of the remote amplifier module.

The CTC92, 93 and 97 chassis are designed in such a way that a *no-turn-on* symptom can, of course, be a fault in the TV chassis rather than with the remote receiver. Thus, we will now look at a simple procedure to assist you in determining where the trouble is to be found.

The triac is not used in the frequency synthesis scan remote systems. Instead, a relay is used as the off/on switch.

The relay driver or switch in each case is a transistor, again controlled by preceding logic circuitry. The relay driver in the MCR-003 is a PNP device with the emitter connected to the 16 volt source through the relay winding. Therefore, if the emitter is connected to ground with a clip lead, the TV set should turn on. The relay driver in the MCR-004 is essentially a PNP device so that the collector lead may be shorted to ground to activate the set.

If you hear a click of the relay this does not always mean that the relay is good, as the relay contacts could be oxidized and not make contact. However, this problem can be checked by shorting the relay contact terminals 2 and 5 together. If the set does not turn on with this test, the problem is then isolated to the main TV chassis.

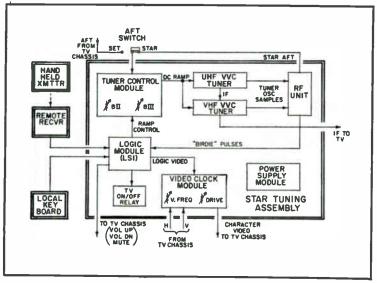

## MAGNAVOX "STAR" TV TUNING SYSTEM BASIC SYSTEM OPERATION

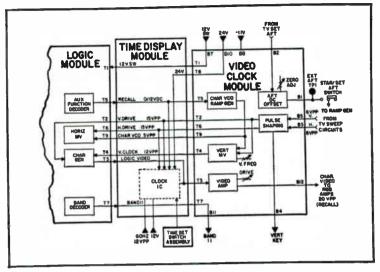

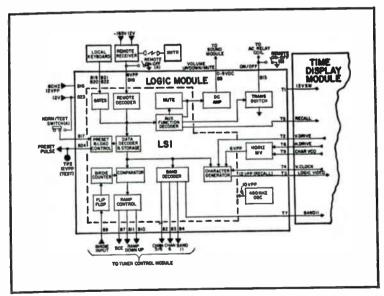

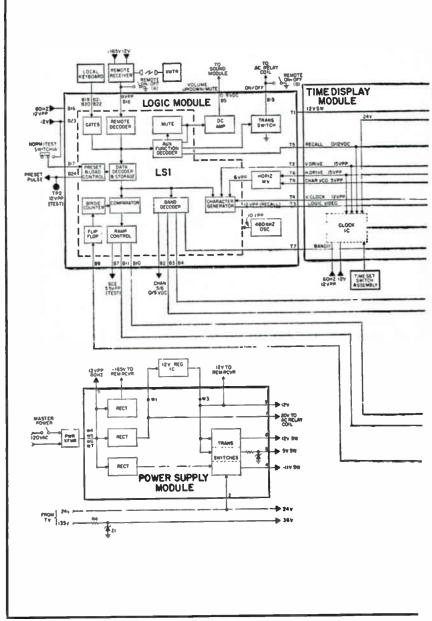

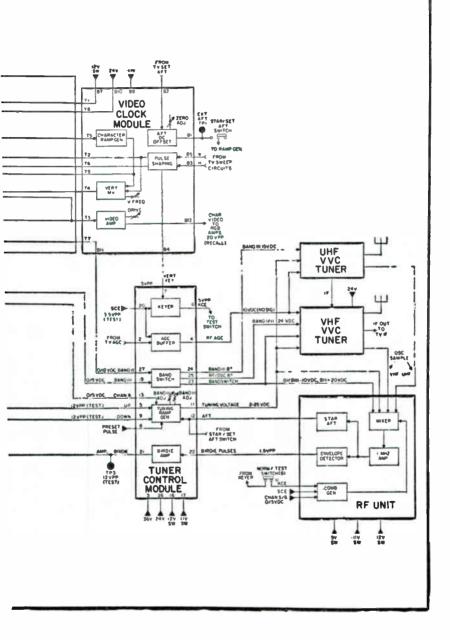

This electronic tuning system has four main units: These are the keyboard assembly, the remote receiver assembly, the transmitter unit, and the tuning assembly. The main parts of the electronics are located on four modules: the power supply module, the logic module, the tuner control module, and the video clock module. Some models have a time clock display module. Note the block diagram for the Star System in Fig. 2-11.

One of fifteen different frequencies are fed from the hand unit transmitter to the remote receiver. The output of the receiver is then coupled to the logic module. A keyboard unit on the set can also be used to control the Star System. In either case, the logic circuits control all functions. The logic circuits are contained within LSI IC's. This custommade device controls TV set off/on, volume level, channel changes and mute. A "logic" video signal, consisting of rectangular pulses, passes through the video clock module to the luminance circuit in the TV chassis. Horizontal and vertical deflection voltages from the TV set serve as timing pulses.

The tuner control module applies a DC ramp voltage to the voltage variable capacitors, or VVC, tuners. The LSI causes the DC ramp, or tuning voltage, to change when a new channel is selected and shifts the tuner oscillator to a new frequency. The tuner IF output signal is then coupled to the IF module on the TV chassis.

A sample of the tuner oscillator signal is coupled to the RF unit. The RF unit contains an internal crystal controlled oscillator which is used to produce "birdie" signals during the tuning cycle. The "birdie" signals are processed in the LSI and provide precision control over the DC ramp voltage and tuner oscillator frequency.

An AFT circuit in the RF unit provides precise correction of the DC tuning ramp in the tuner control module. The AFT correction circuit in the

Fig. 2-11. Block diagram of Magnavox STAR remote system.

Fig. 2-12. Video clock and time display modules.

TV chassis may also be used if necessary. In most cases, the AFT switch should be operated in the *Star* position. The set position is used when a wider pull-in range is required to correct the larger carrier frequency errors found on some cable TV systems.

Fig. 2-13. Logic module found in STAR system.

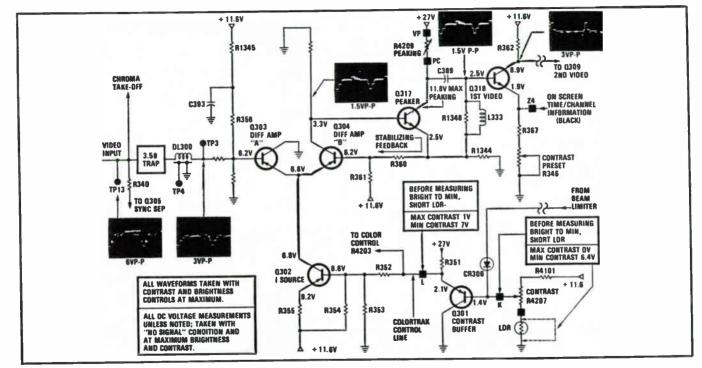

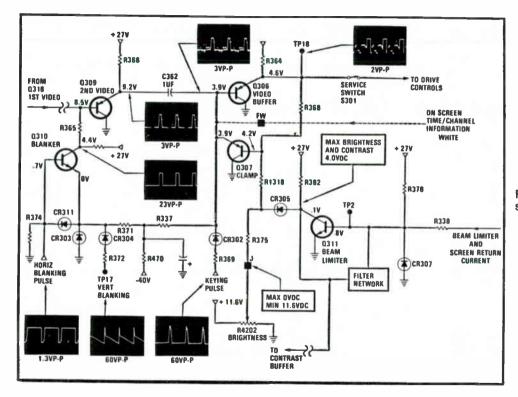

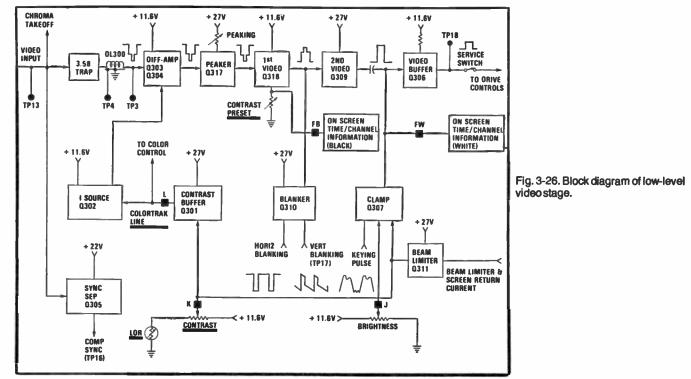

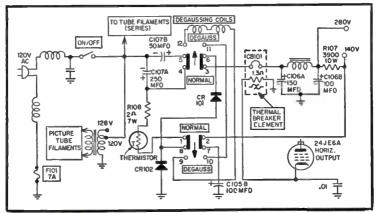

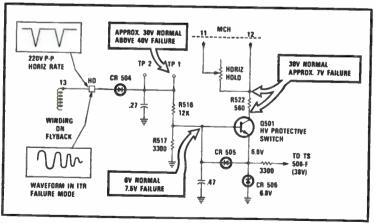

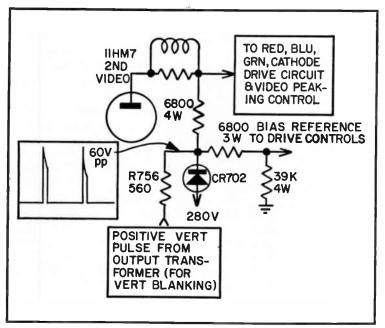

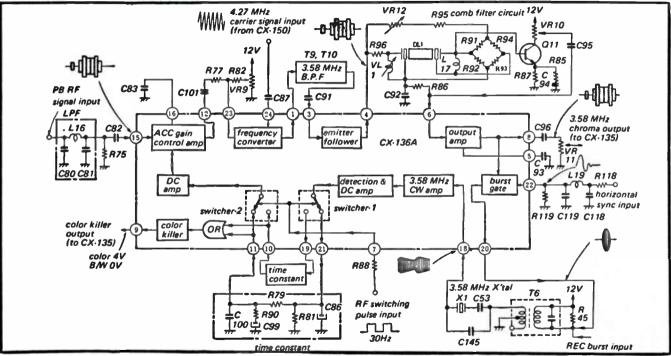

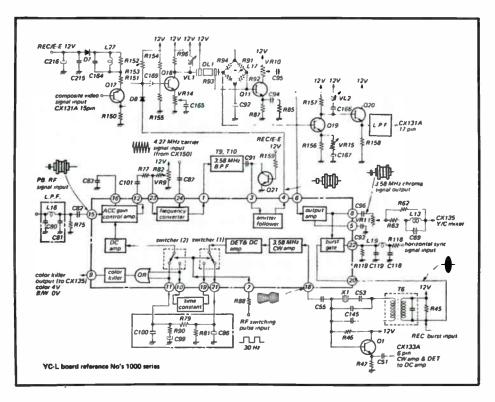

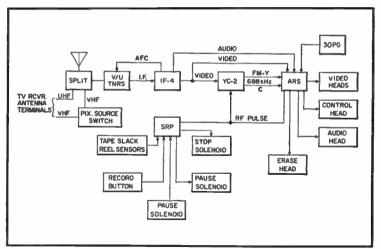

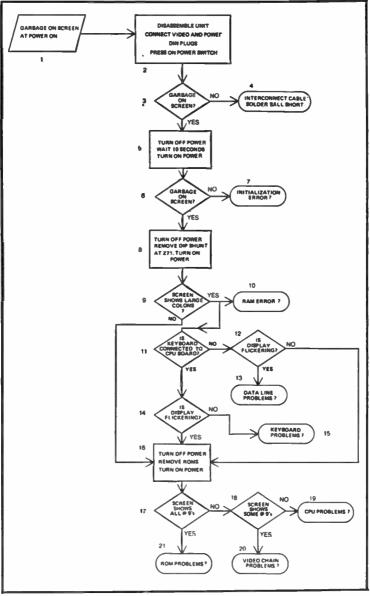

### Video Clock and Time Display System