# Electronic Circuit Design Handbook

by the Editors of EEE Magazine

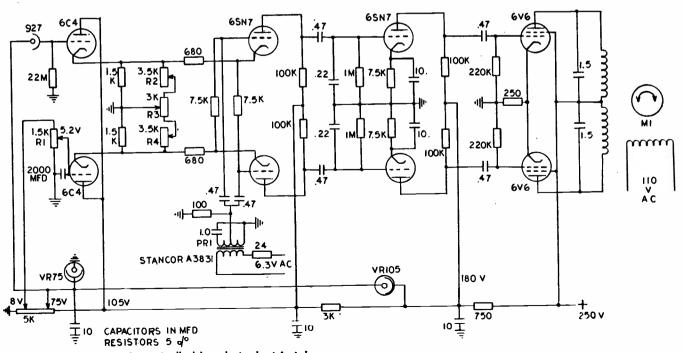

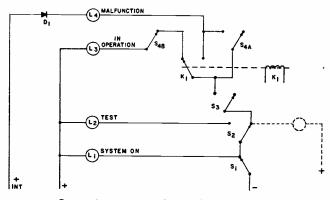

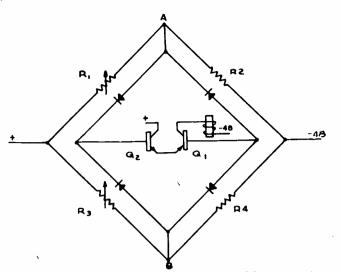

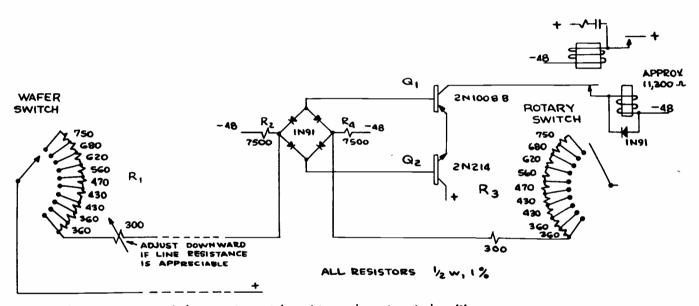

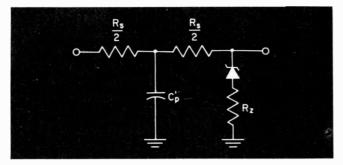

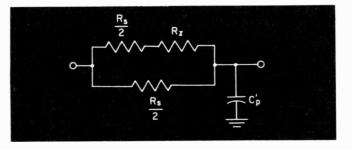

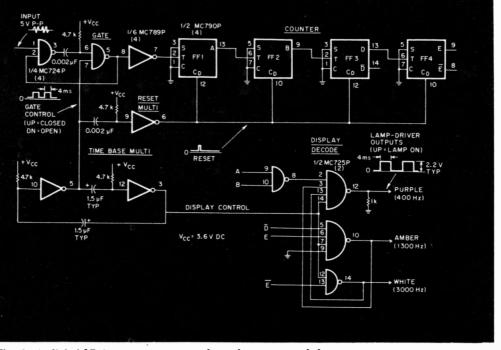

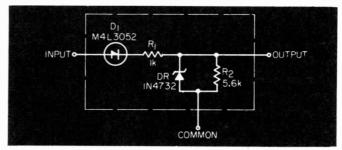

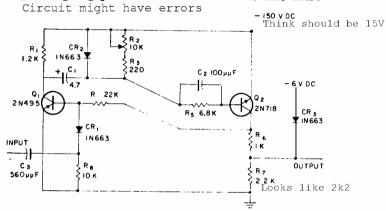

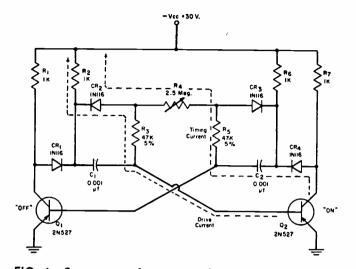

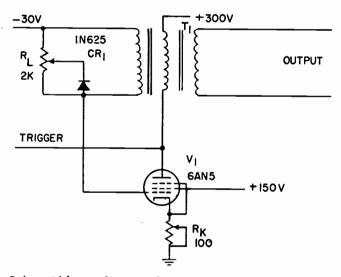

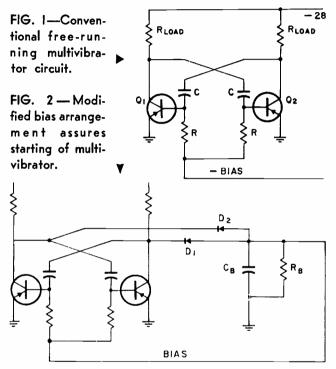

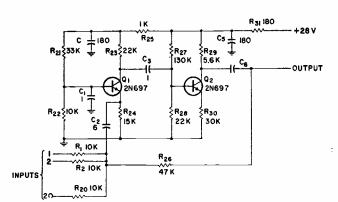

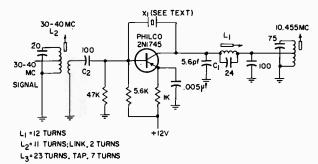

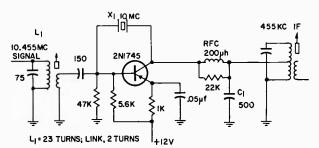

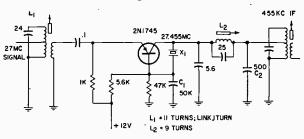

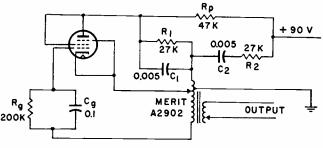

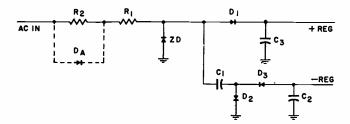

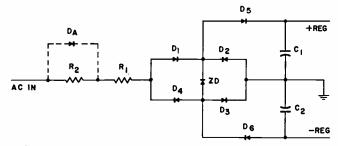

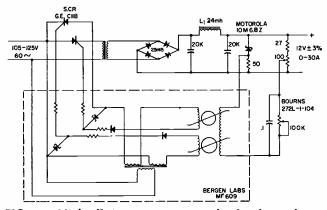

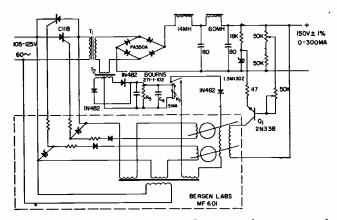

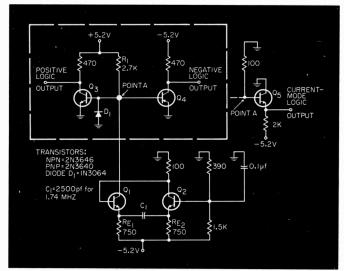

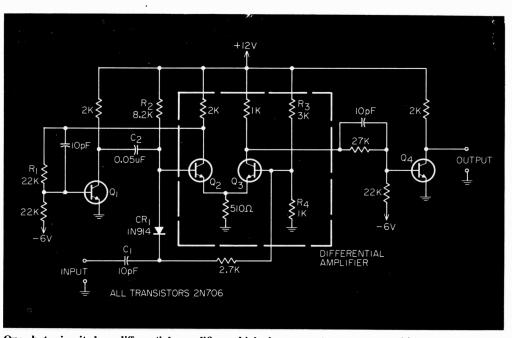

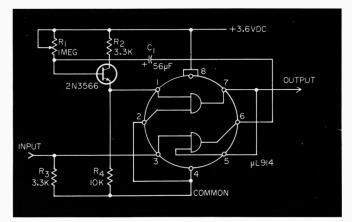

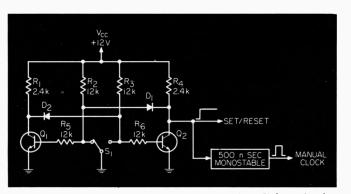

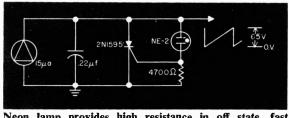

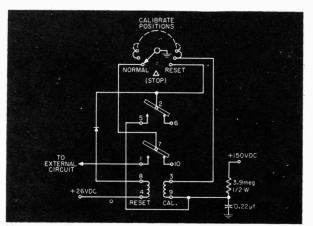

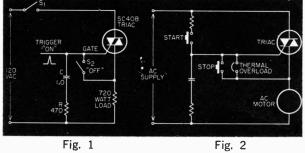

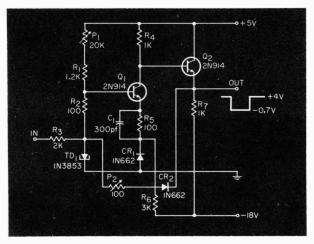

Some notes about this scanned book. 1. Due to poor print quality of the original diagrams, scanning proved difficult and the following four diagrams have been redrawn using EasyPC CAD software. They are to be used in conjunction with the original associated text. 2. In the main body of the book. A few scanned pages have annotations added to help with reading circuit values etc. No guarantees can be given to the accuracy of these annotations due to poor original print quality. 3. Use of the zoom facility available in most Acrobat .pdf document readers will help to view component values. 4. A small number of original pages had print quality too poor to make out the values. Any suggested values are left to the reader to try out or pick a value they think works best.

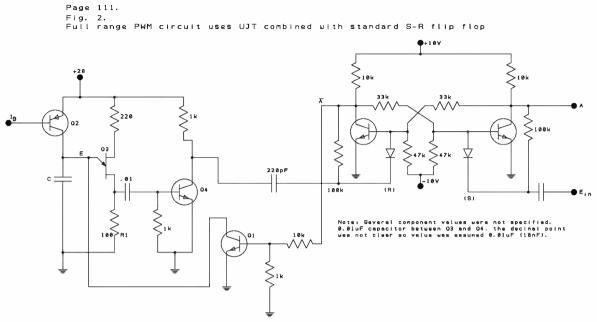

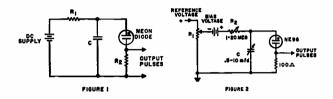

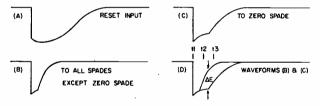

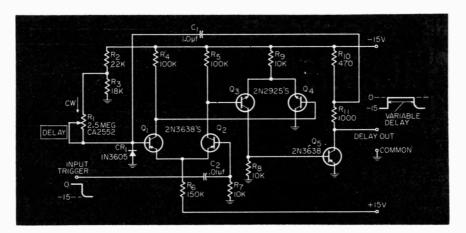

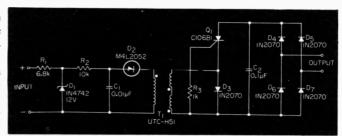

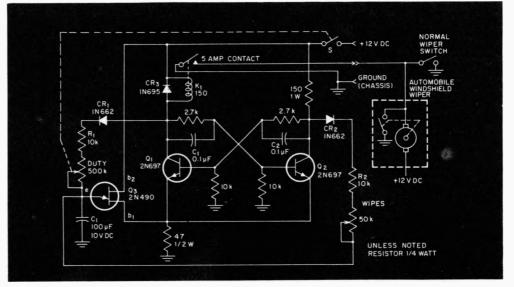

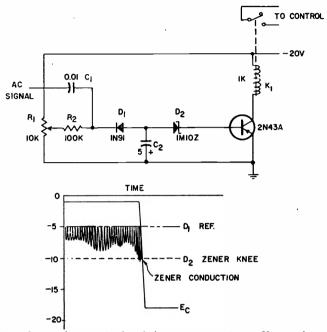

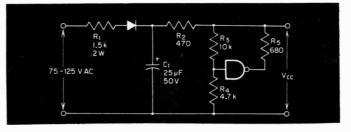

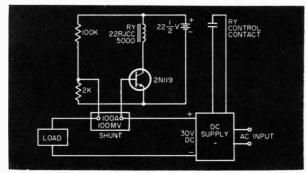

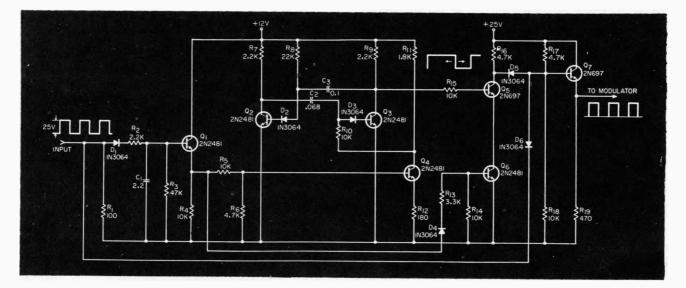

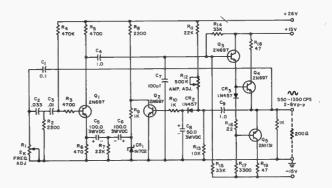

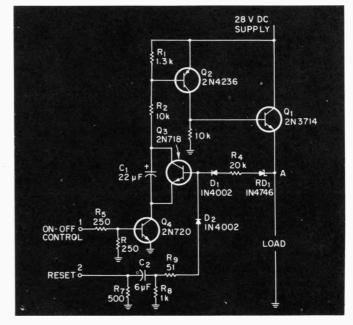

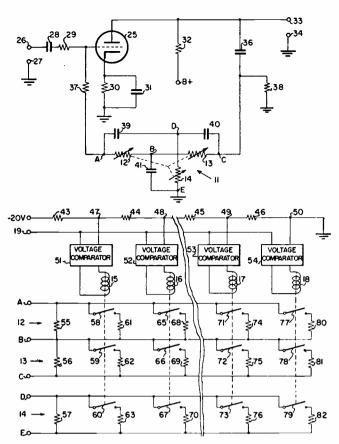

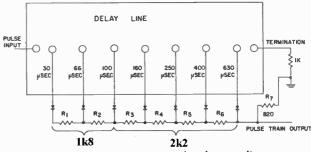

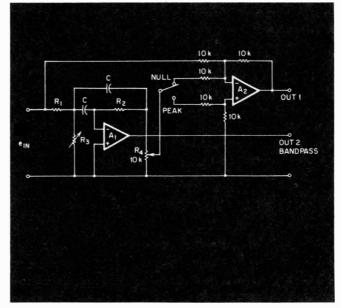

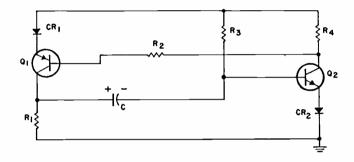

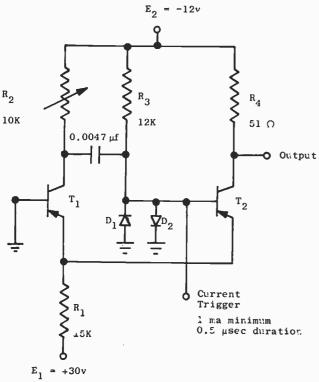

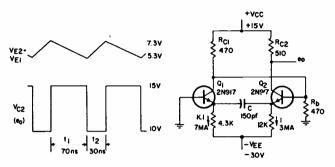

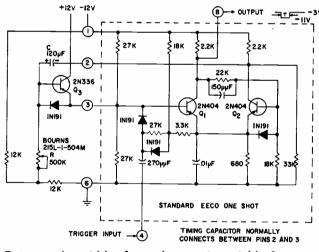

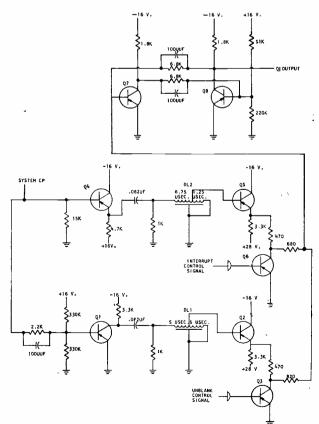

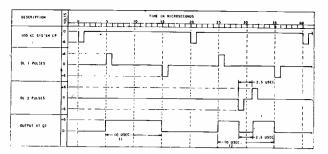

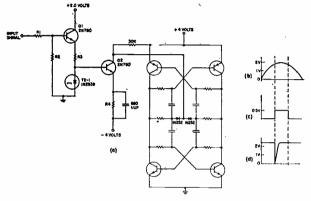

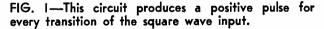

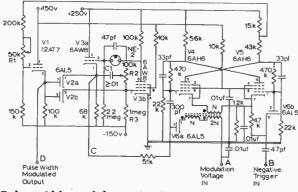

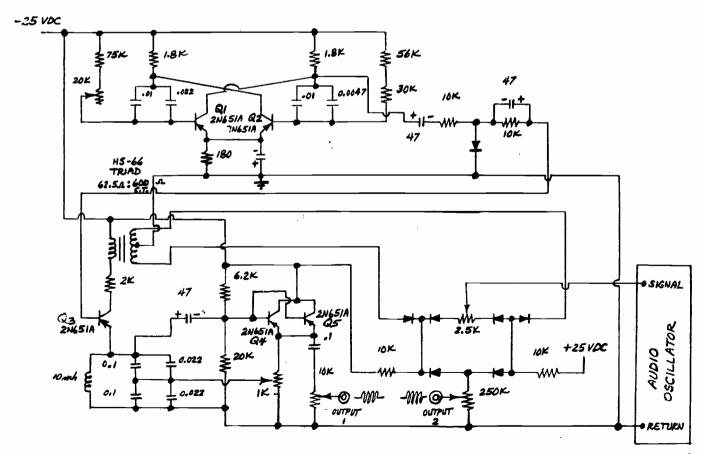

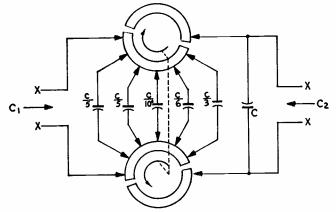

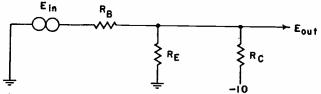

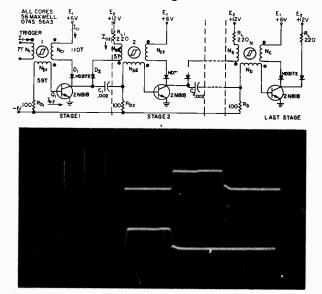

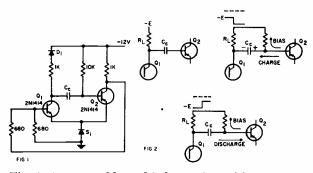

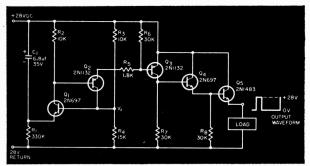

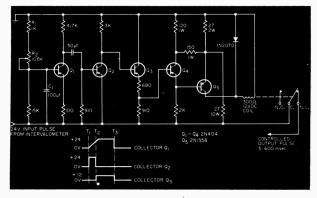

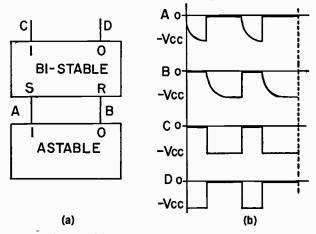

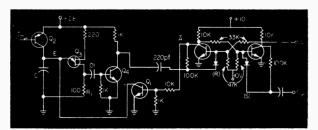

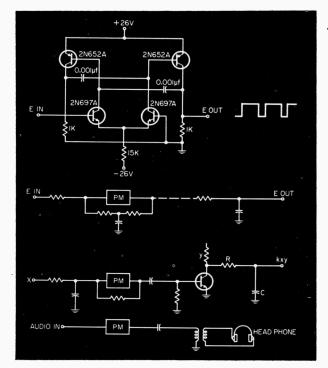

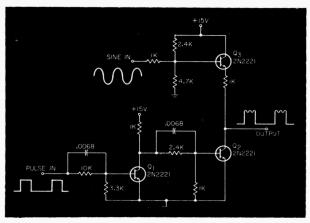

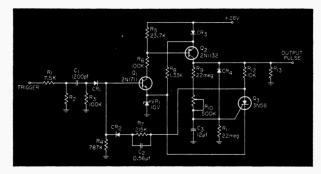

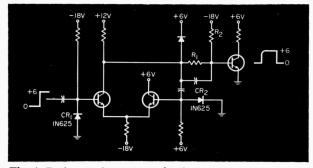

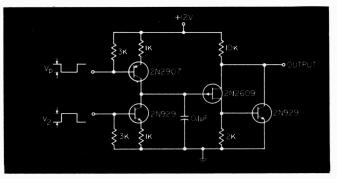

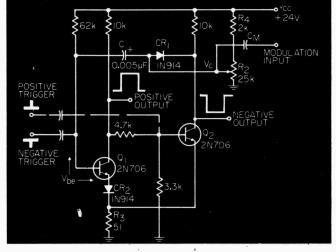

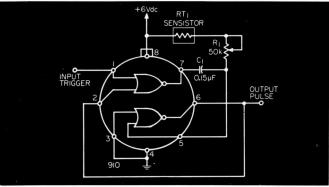

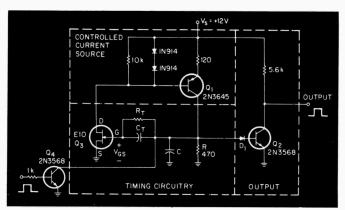

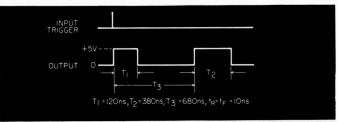

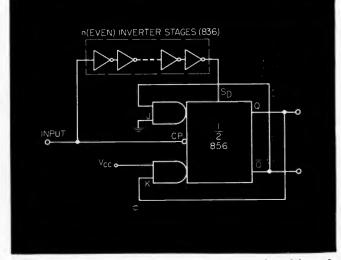

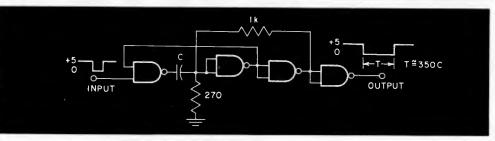

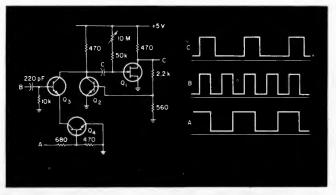

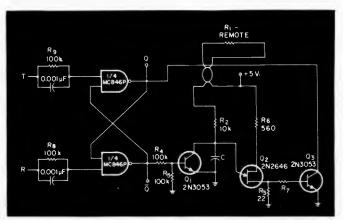

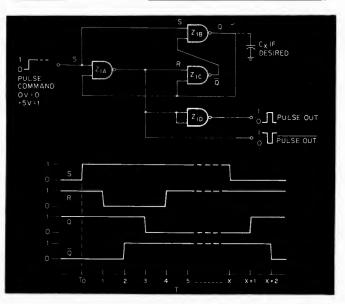

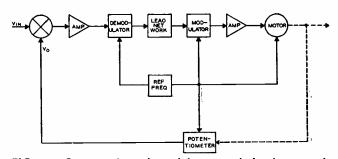

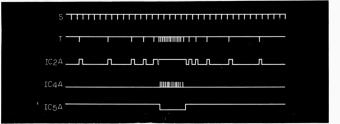

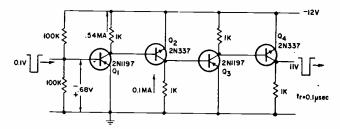

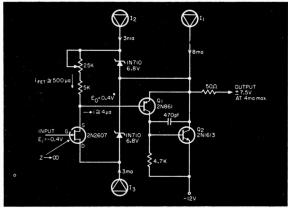

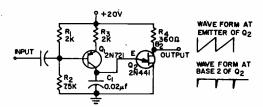

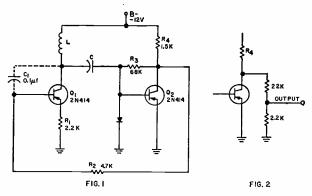

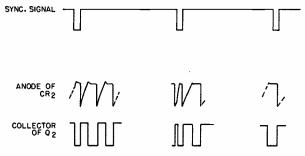

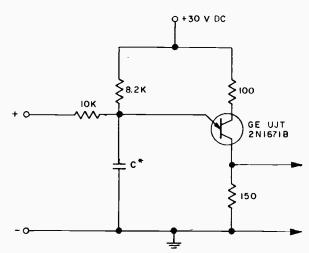

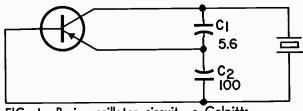

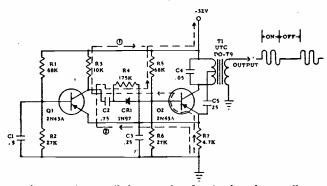

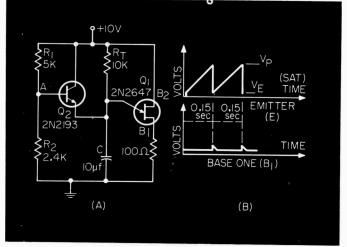

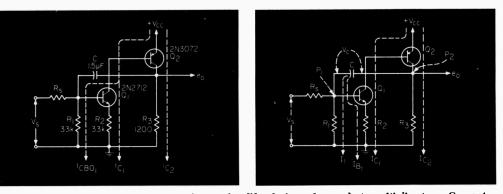

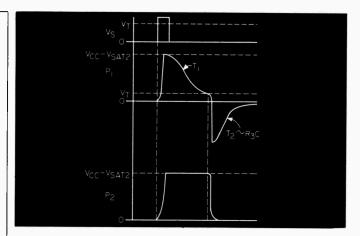

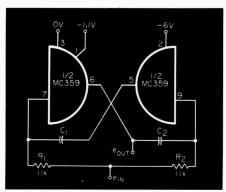

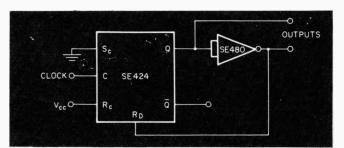

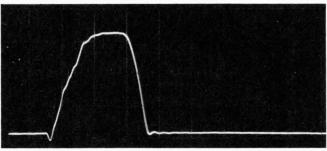

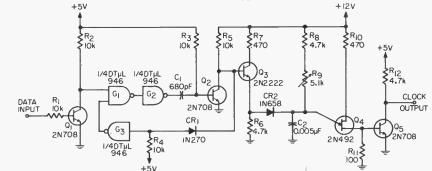

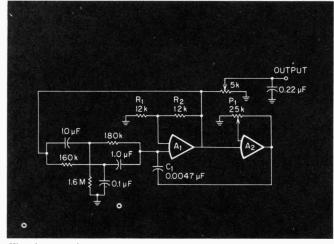

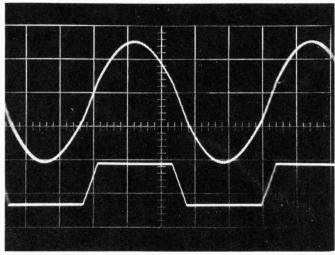

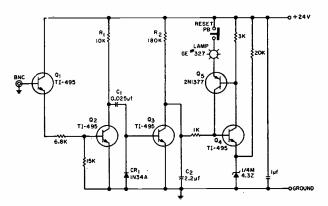

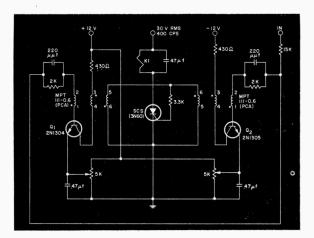

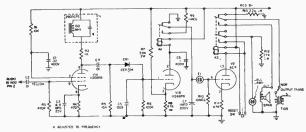

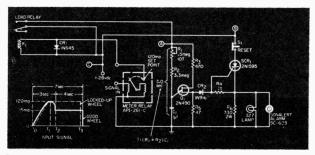

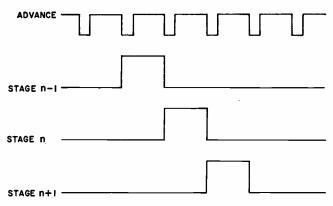

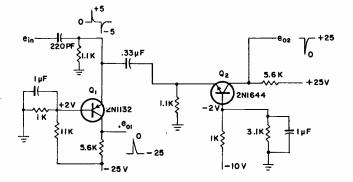

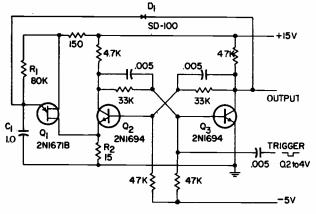

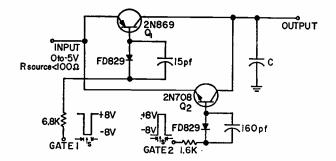

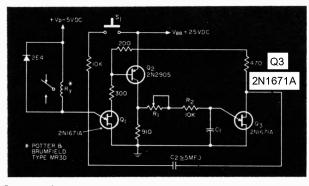

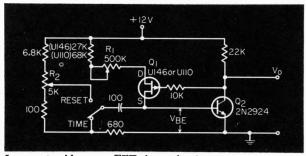

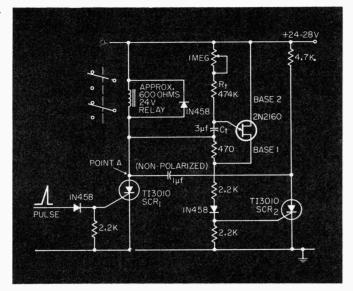

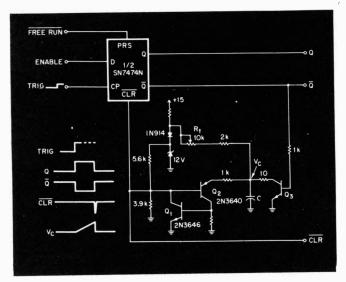

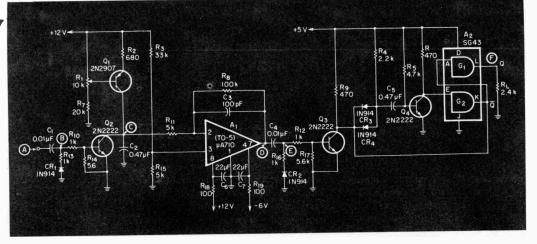

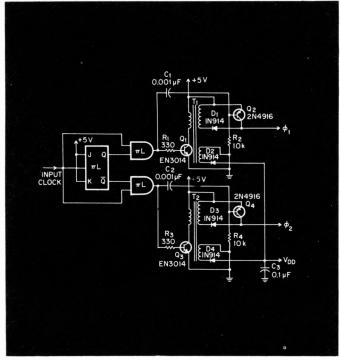

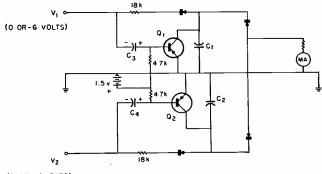

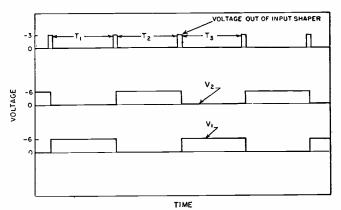

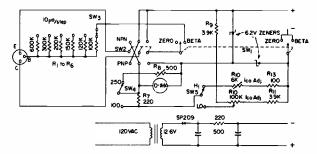

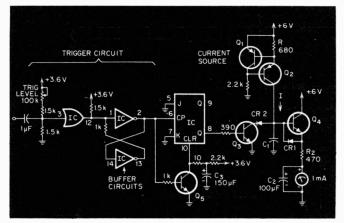

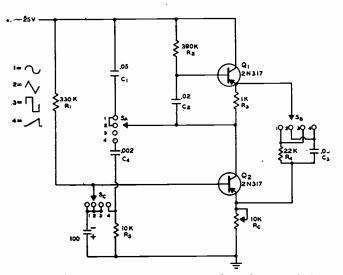

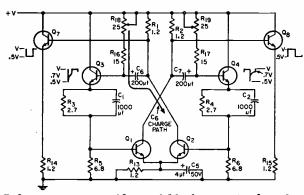

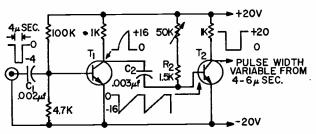

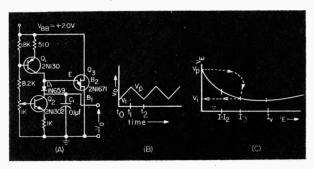

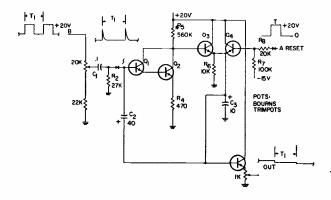

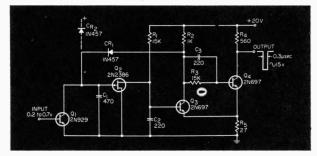

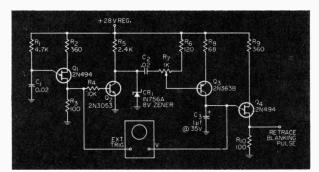

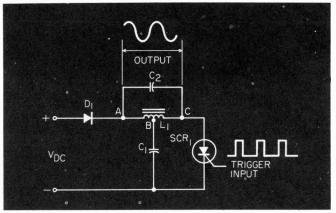

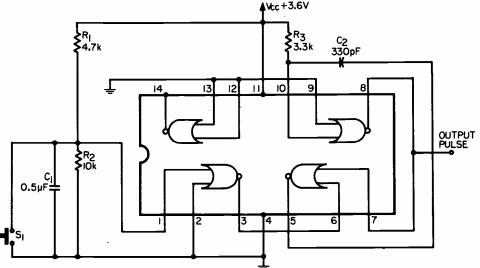

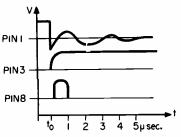

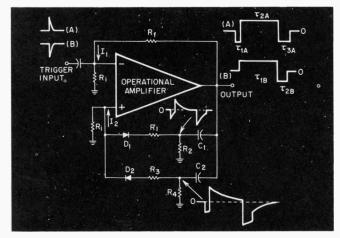

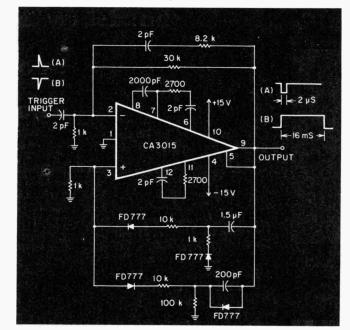

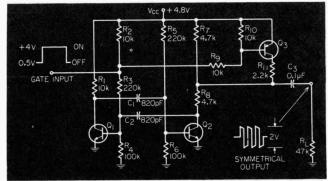

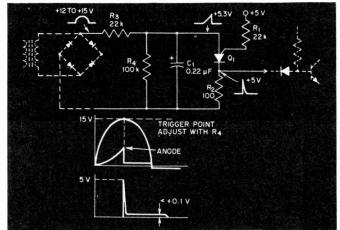

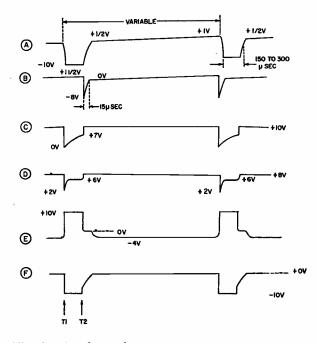

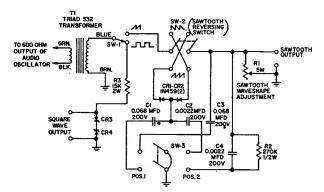

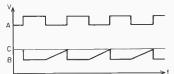

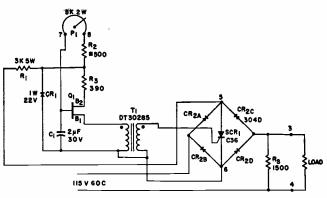

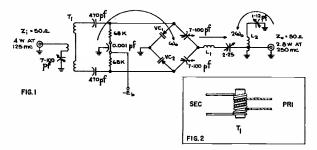

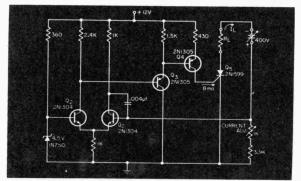

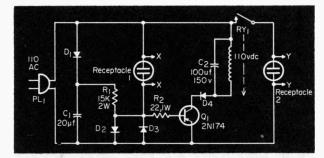

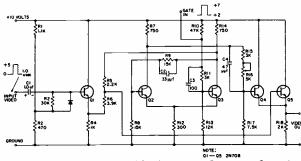

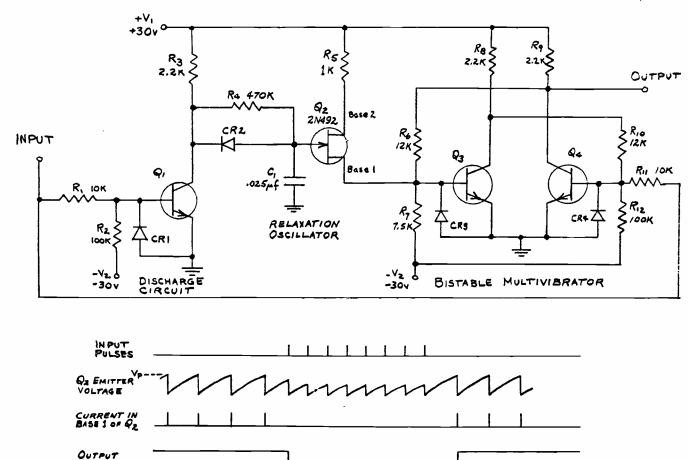

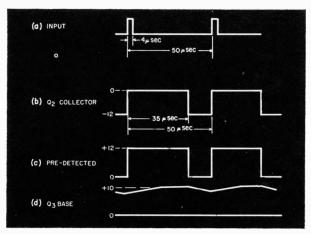

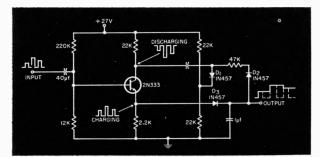

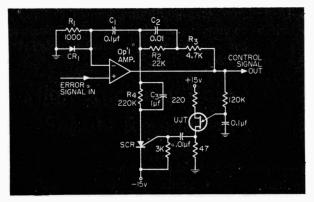

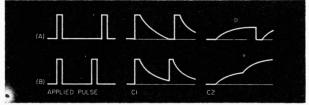

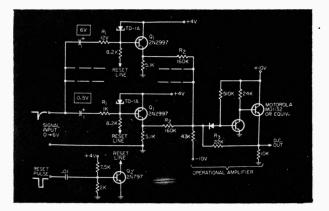

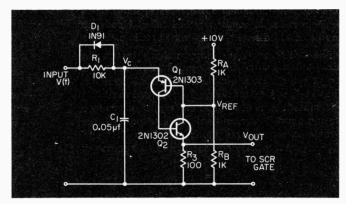

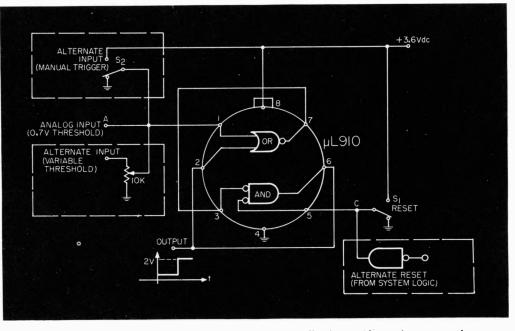

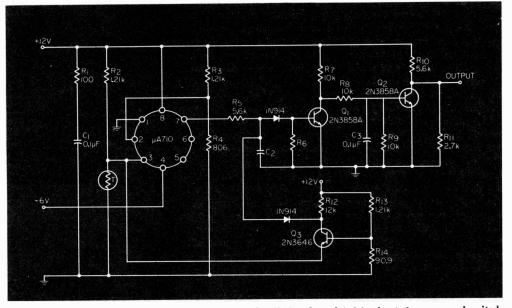

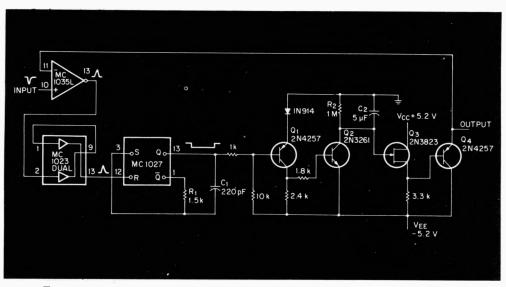

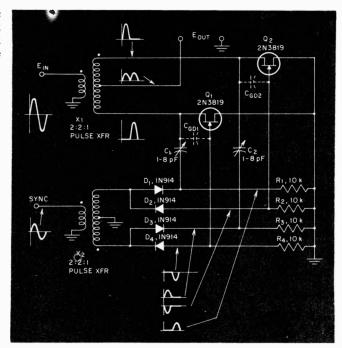

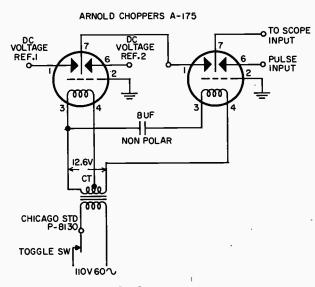

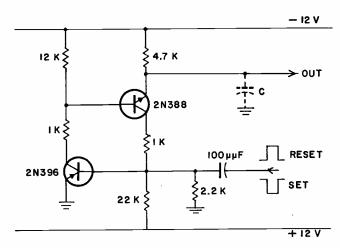

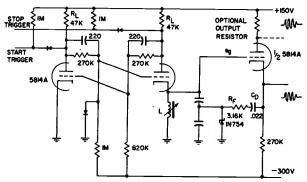

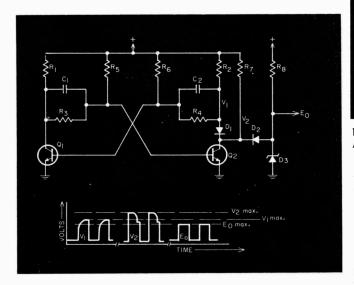

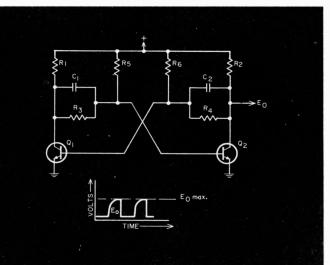

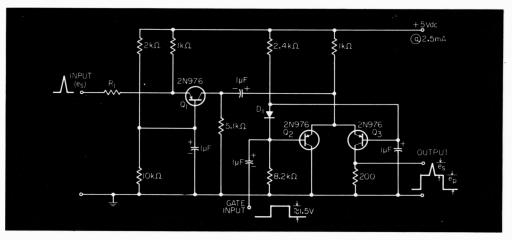

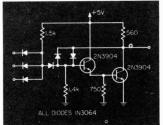

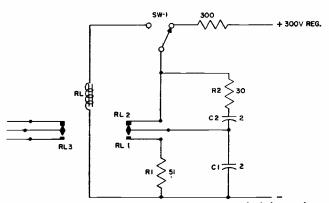

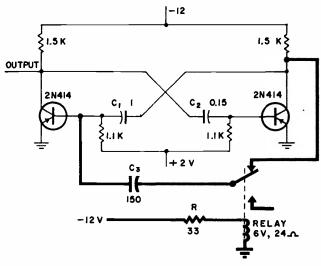

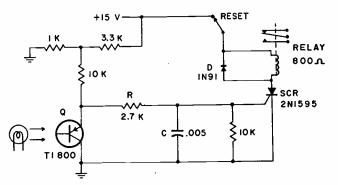

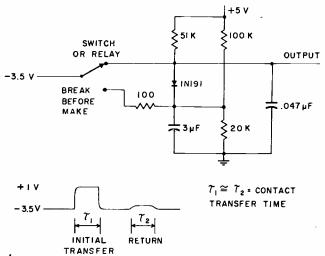

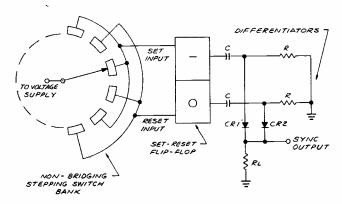

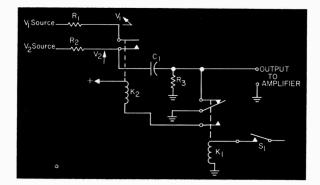

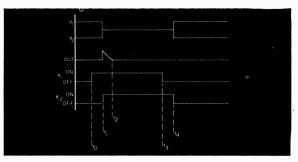

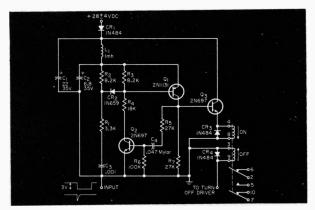

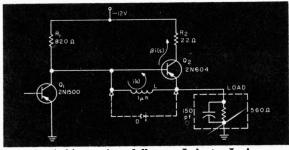

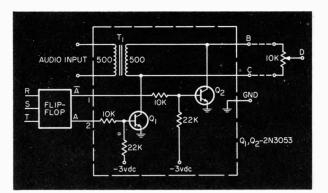

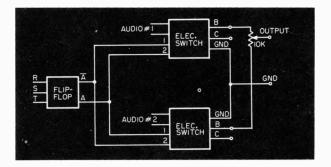

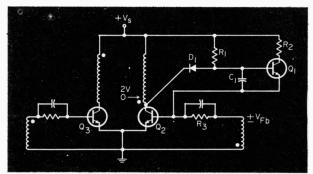

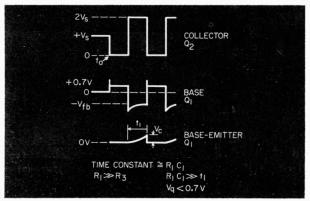

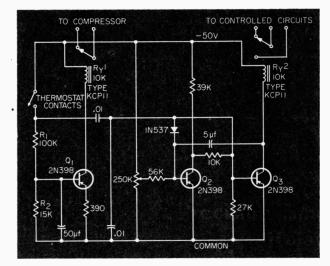

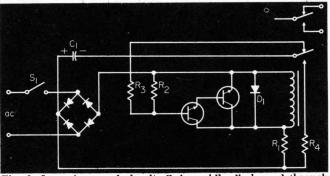

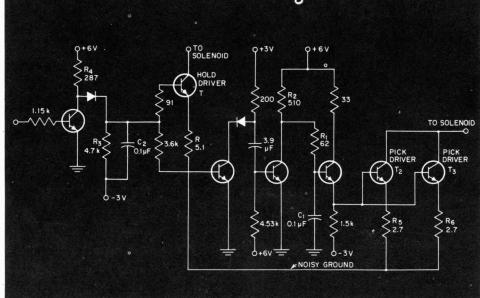

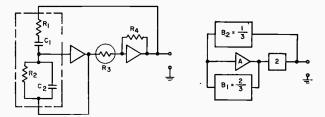

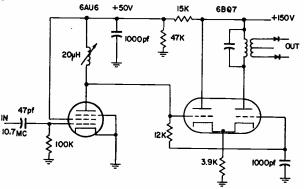

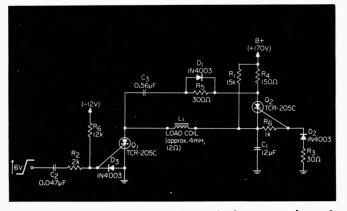

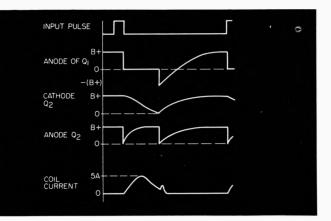

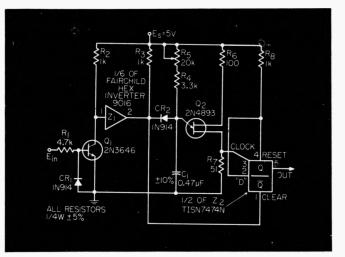

#### Page 111. Fig. 2. Full range PWM circuit uses UJT combined with standard S-R flip flop.

Fig. 2. Full-range PWM circuit uses UJT combined with standard S-R flip flop.

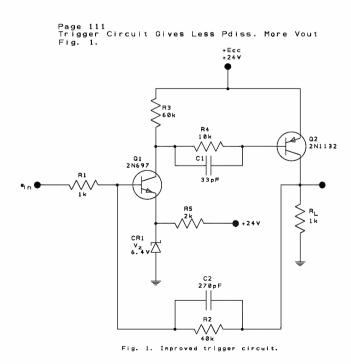

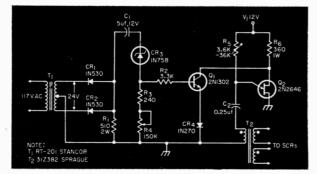

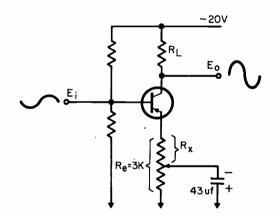

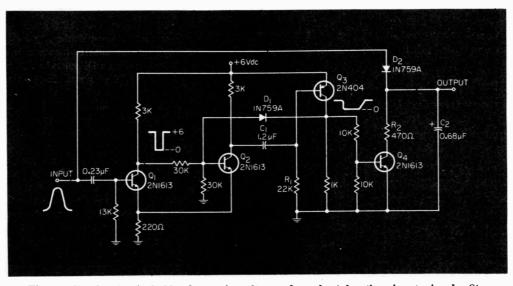

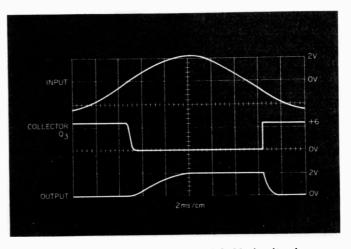

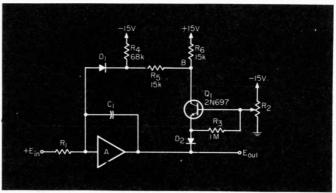

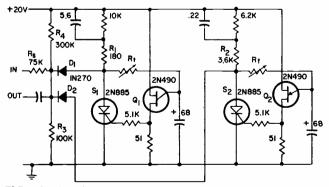

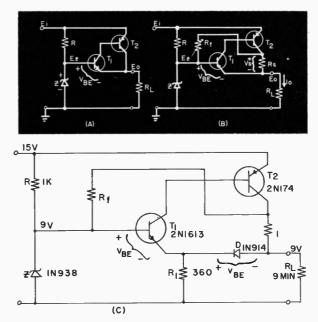

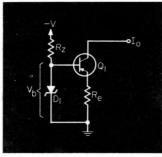

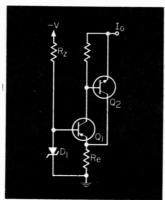

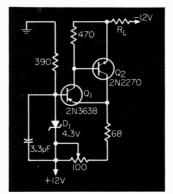

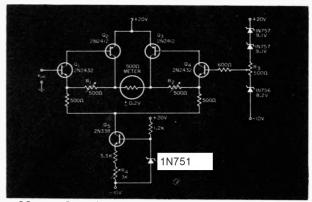

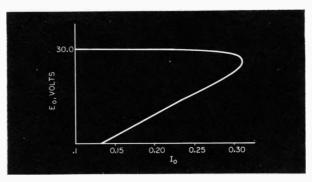

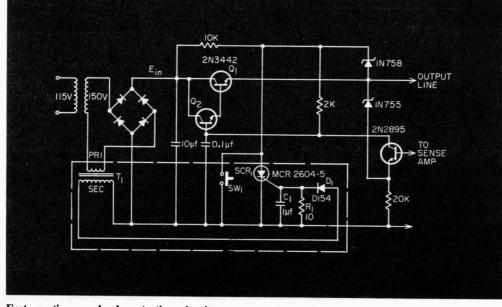

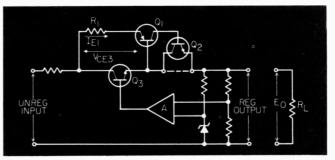

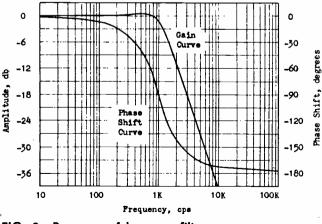

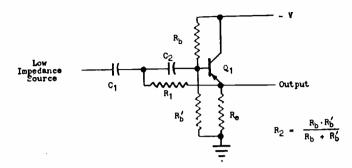

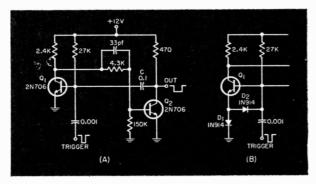

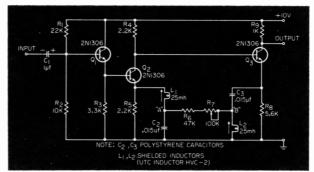

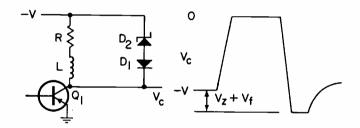

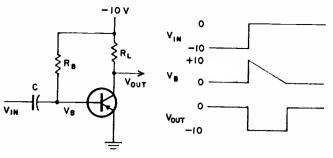

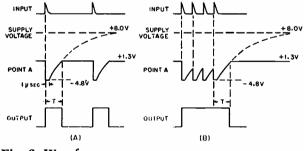

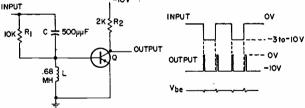

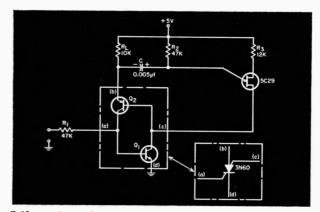

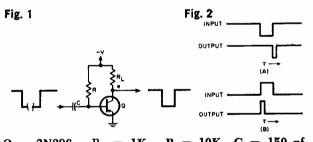

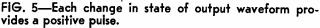

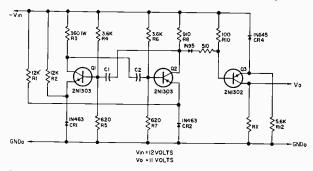

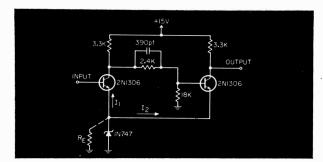

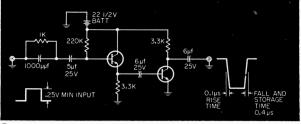

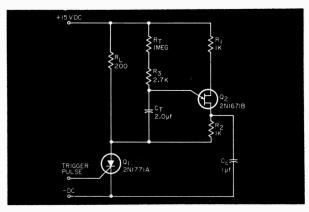

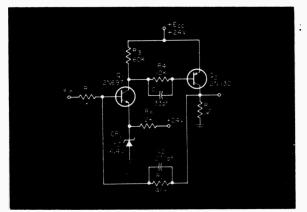

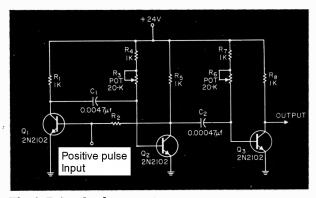

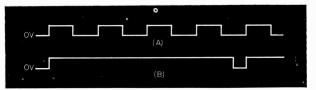

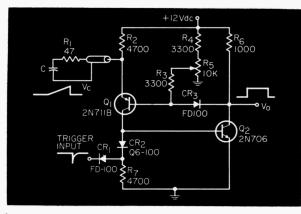

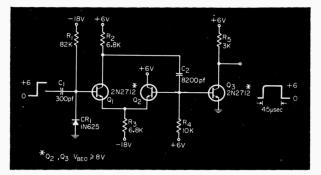

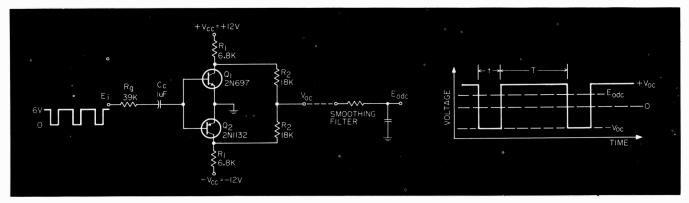

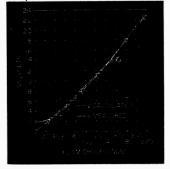

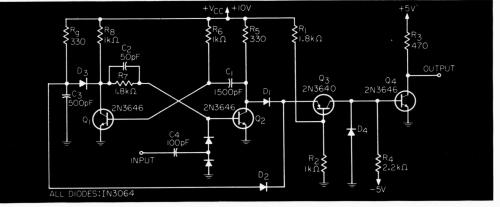

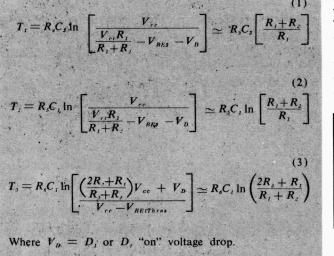

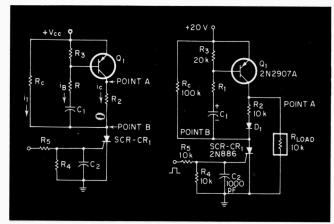

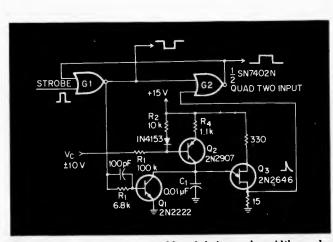

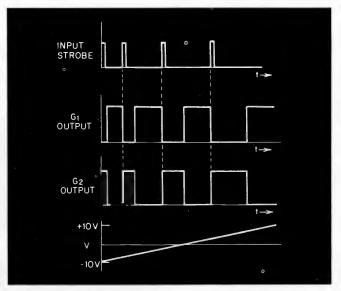

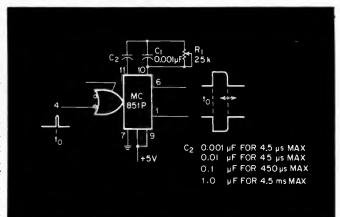

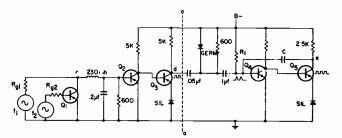

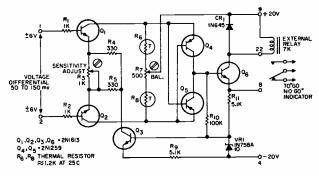

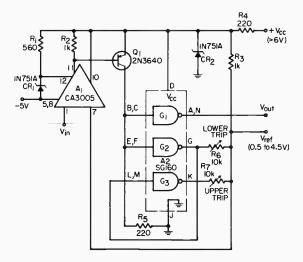

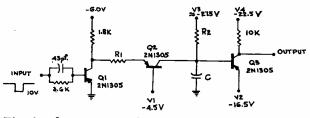

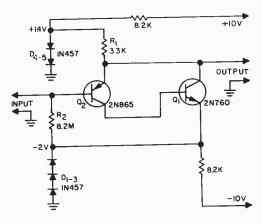

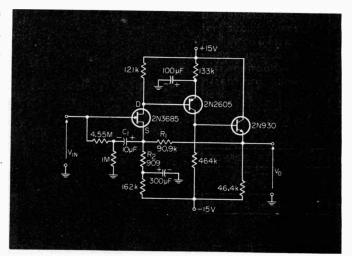

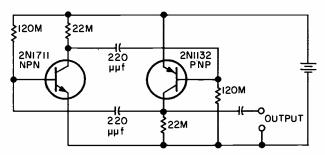

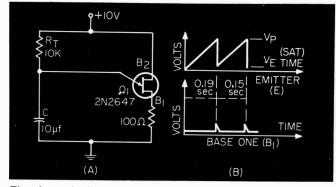

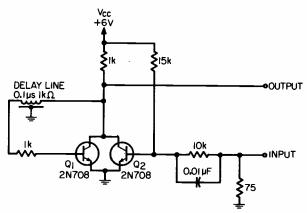

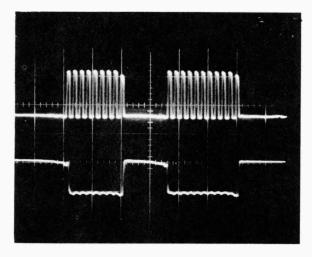

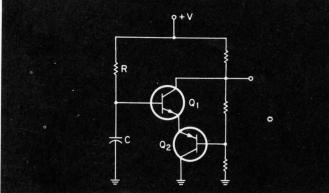

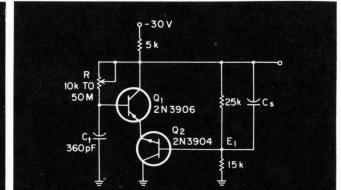

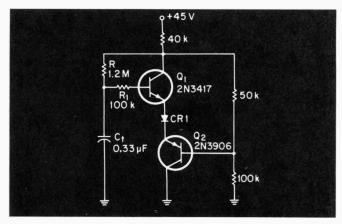

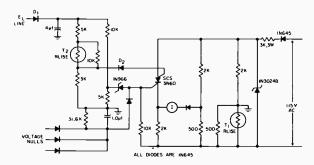

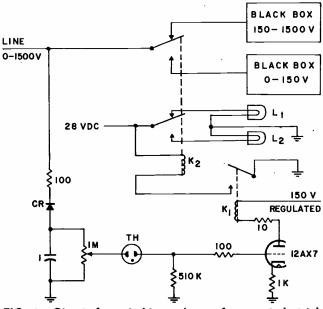

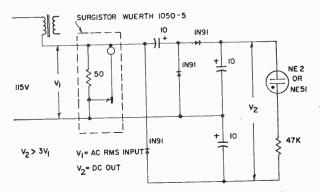

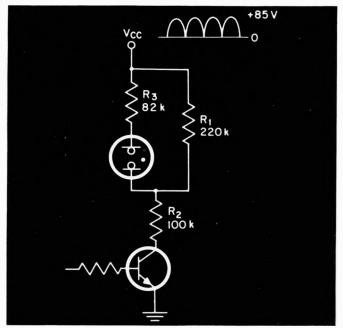

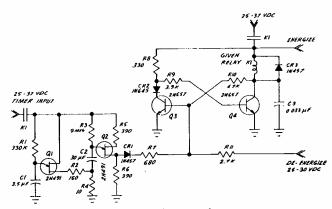

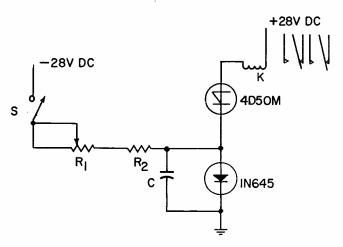

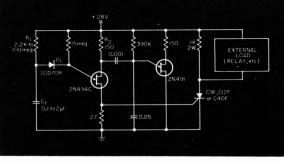

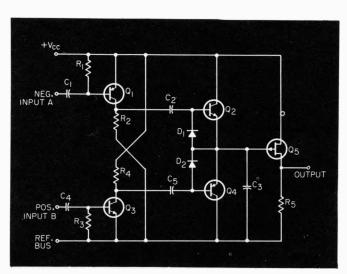

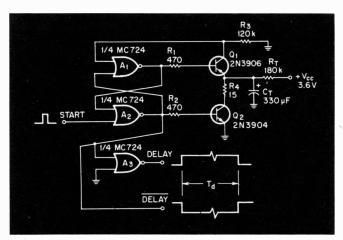

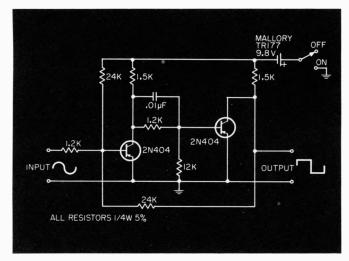

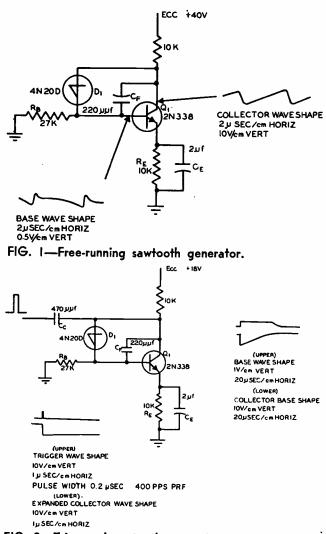

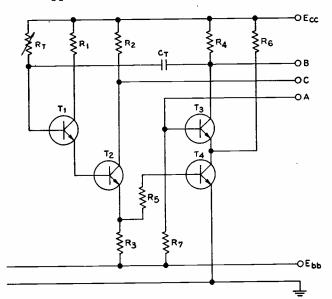

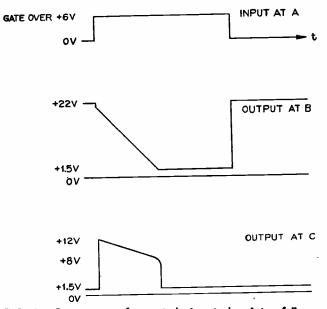

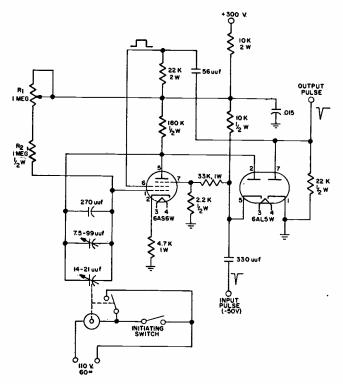

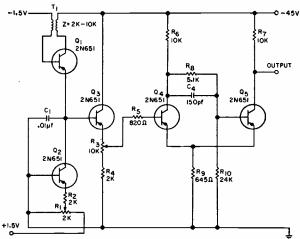

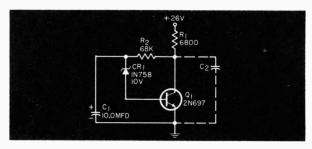

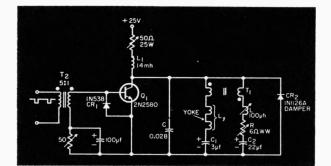

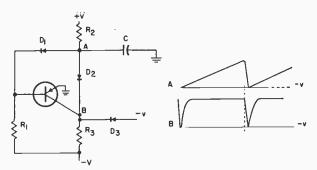

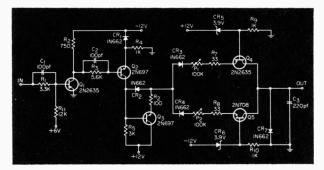

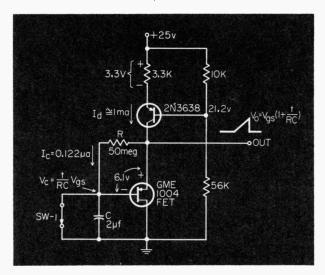

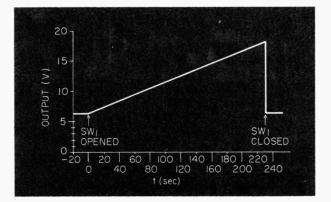

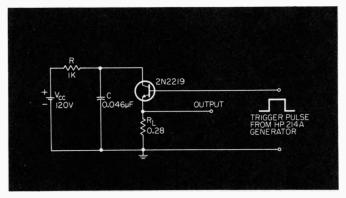

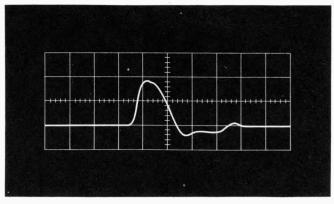

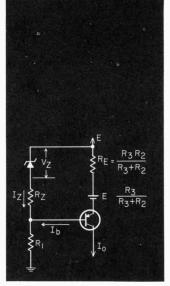

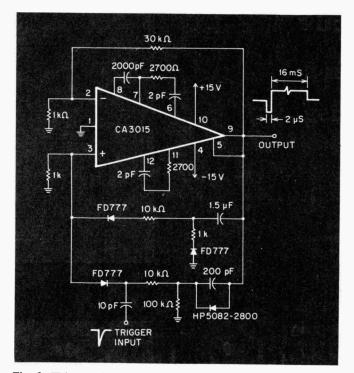

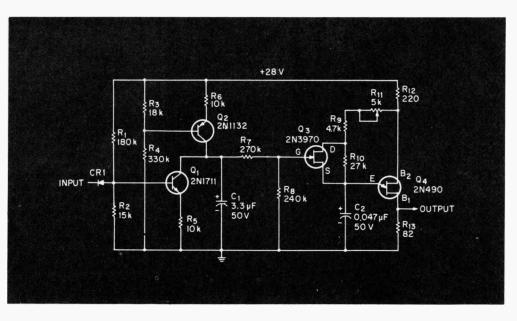

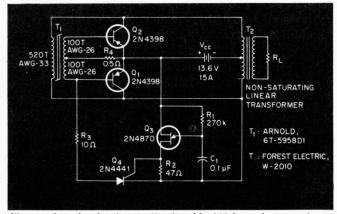

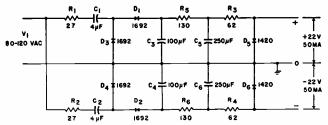

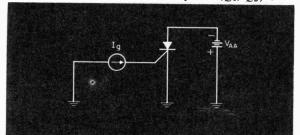

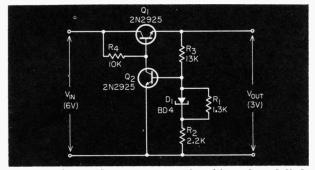

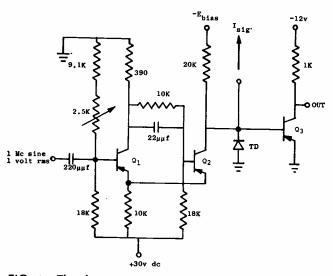

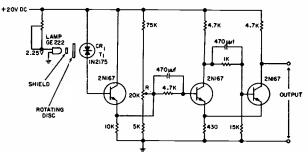

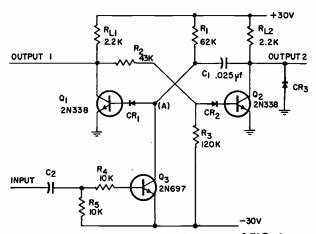

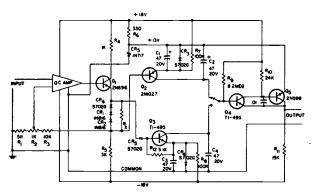

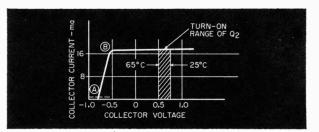

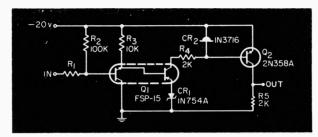

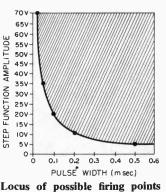

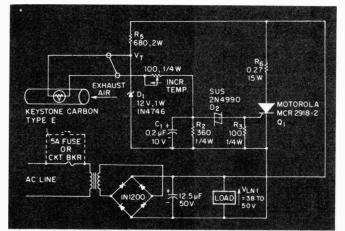

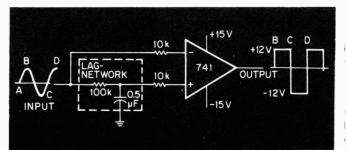

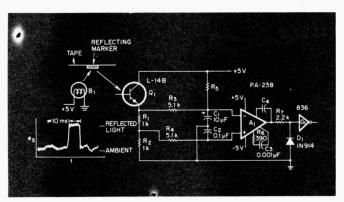

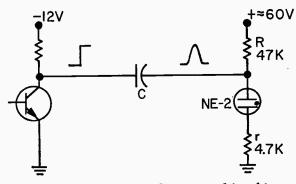

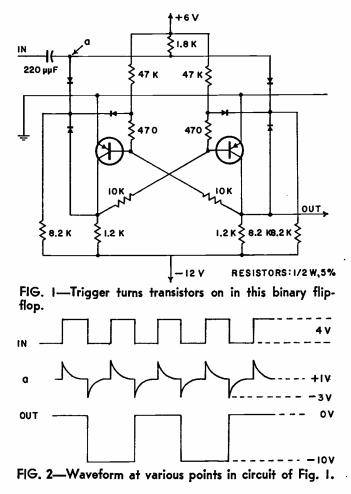

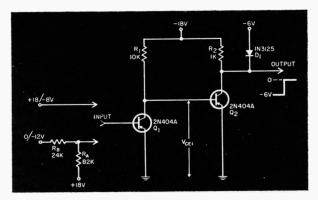

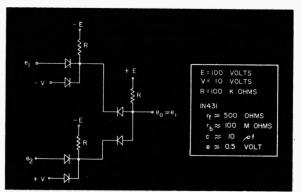

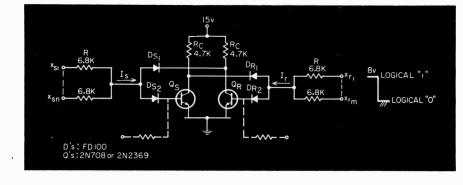

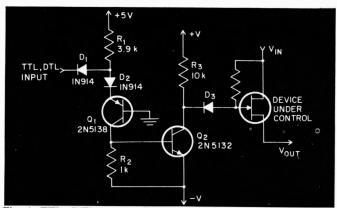

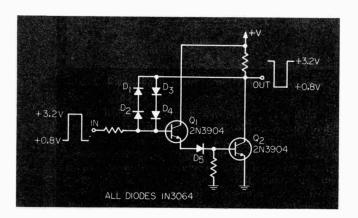

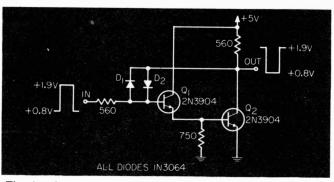

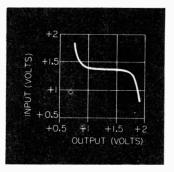

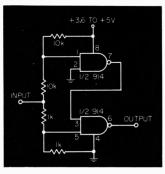

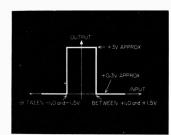

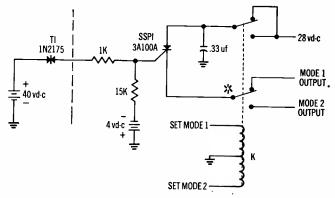

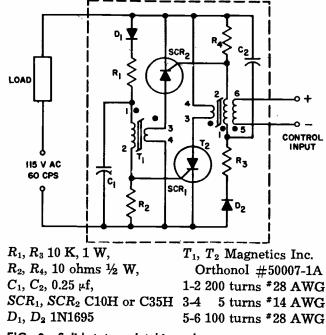

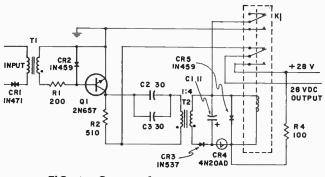

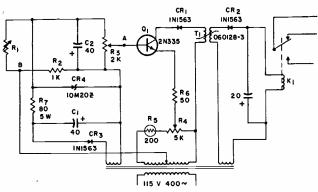

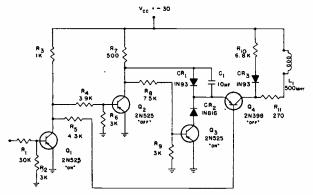

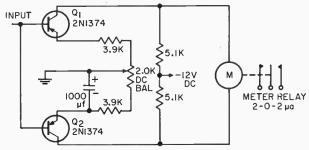

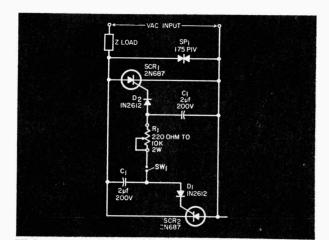

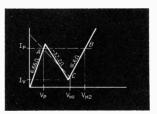

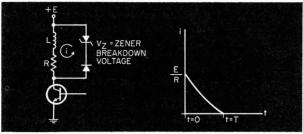

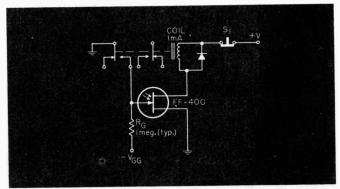

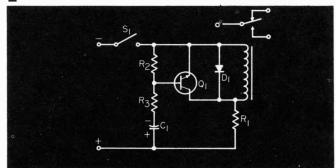

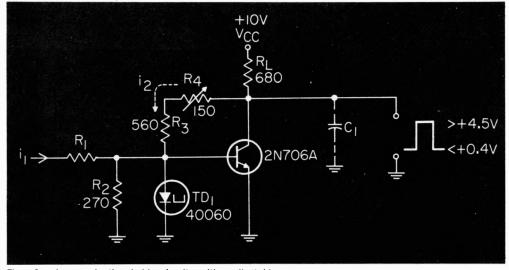

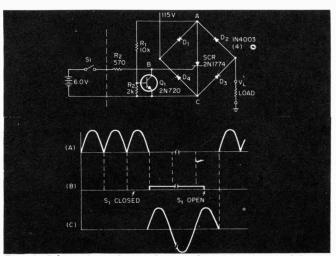

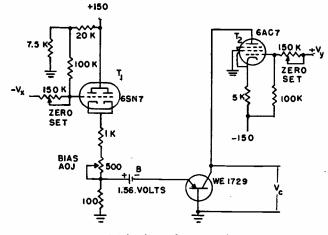

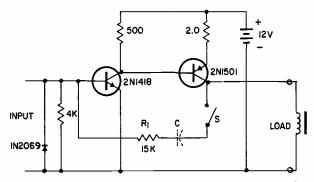

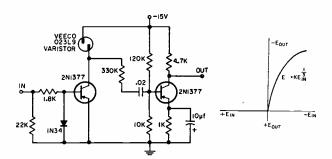

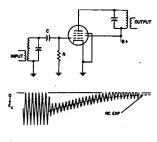

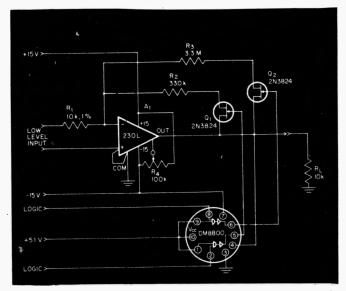

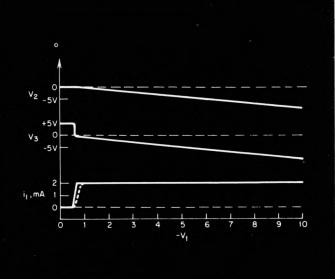

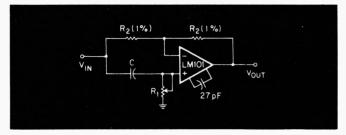

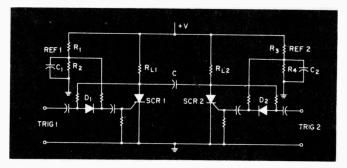

Page. 111 Fig. 1. Trigger Circuit Gives Less Pdiss, More Vout.

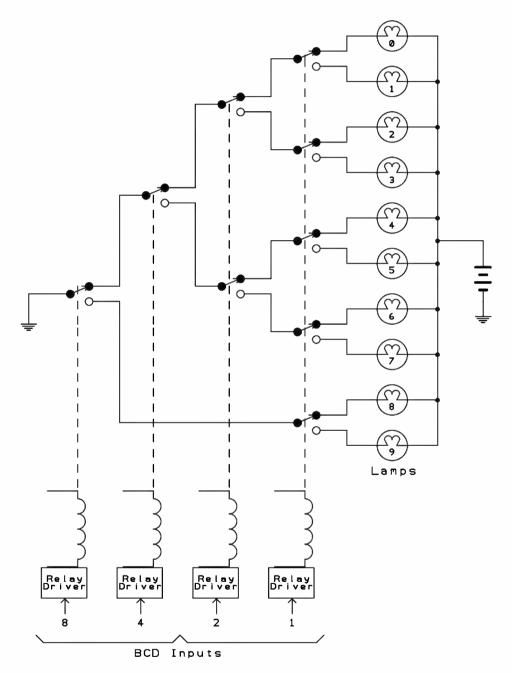

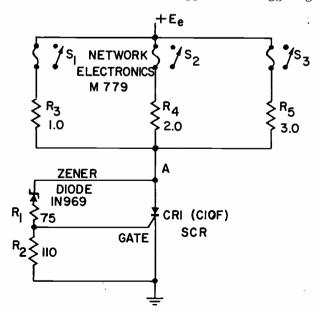

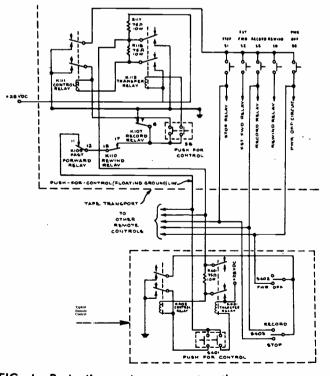

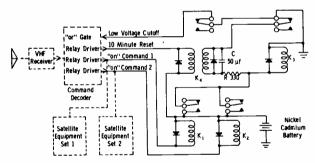

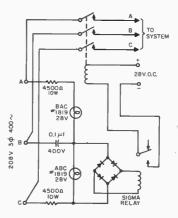

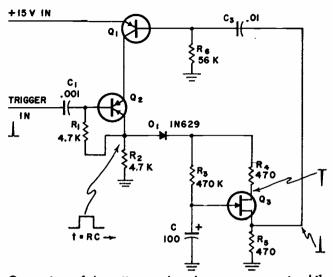

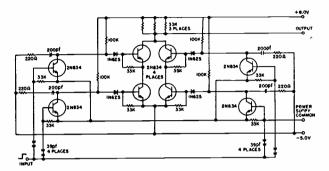

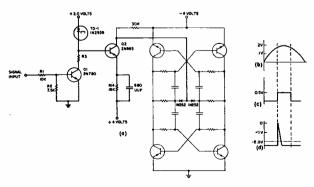

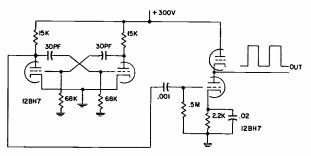

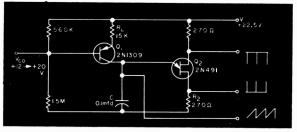

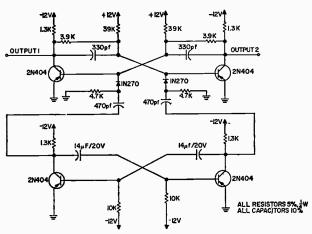

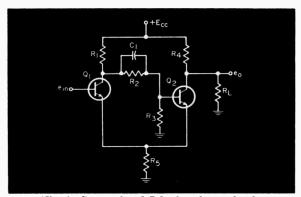

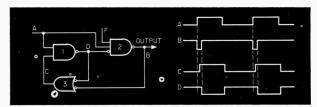

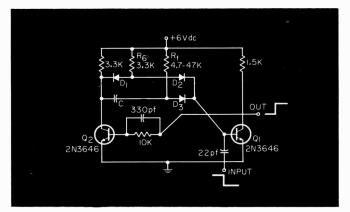

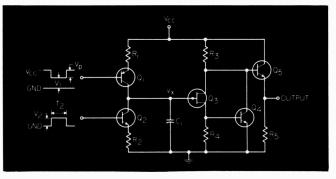

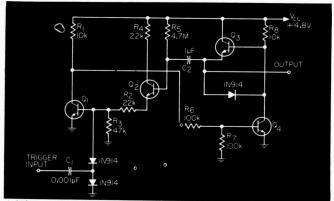

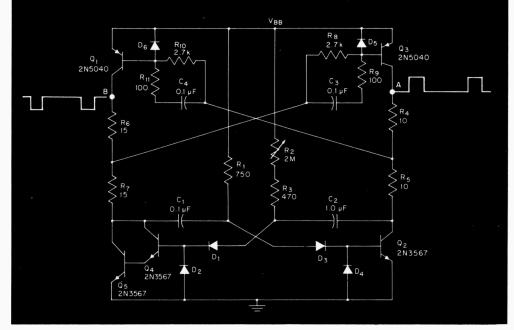

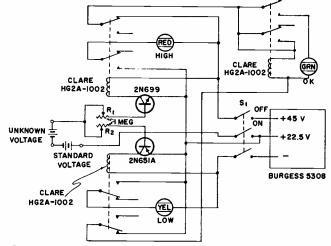

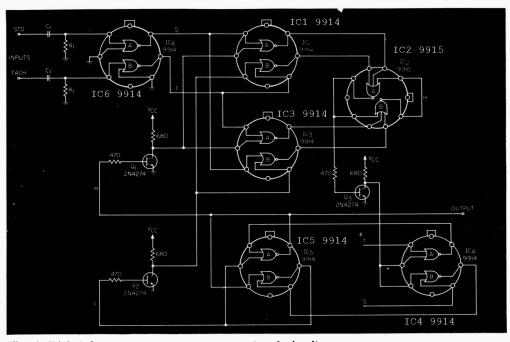

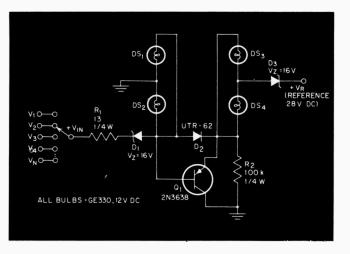

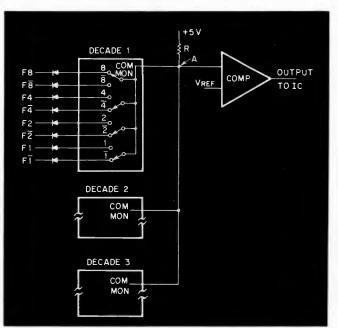

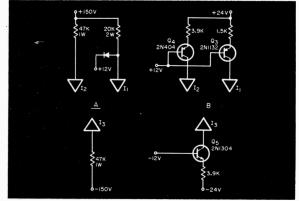

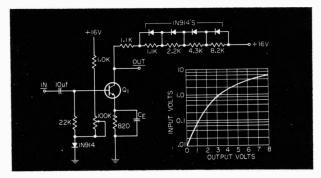

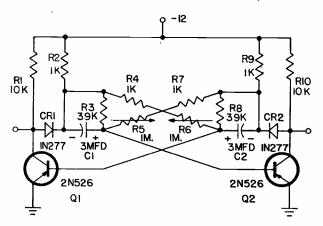

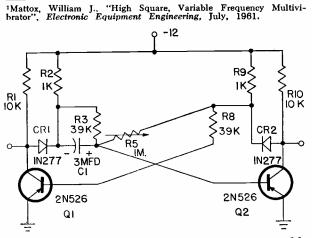

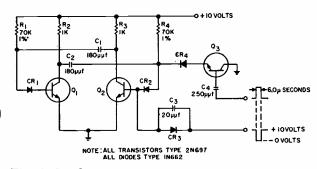

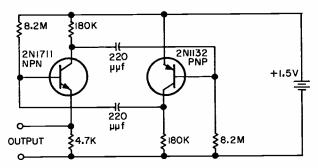

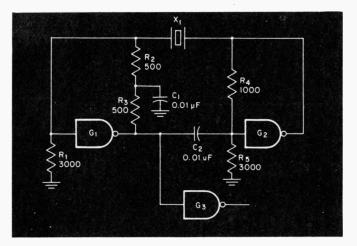

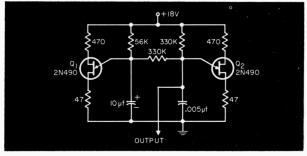

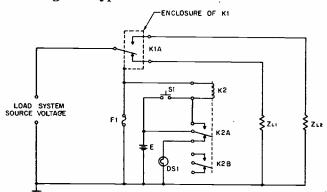

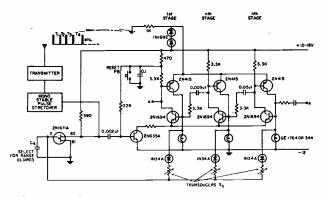

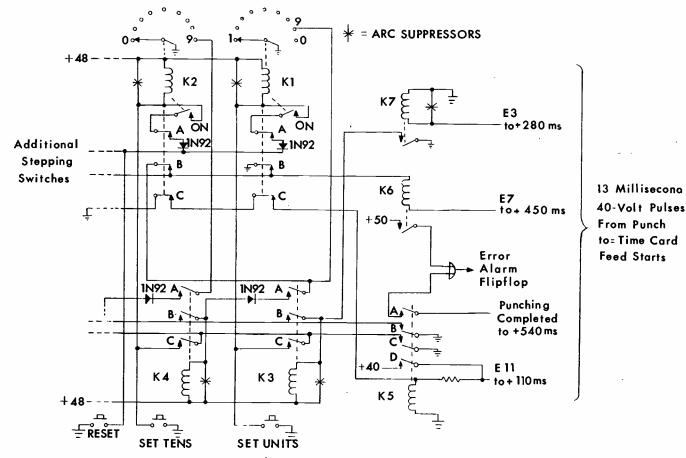

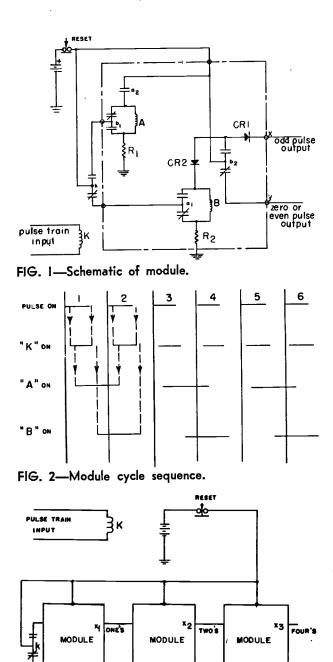

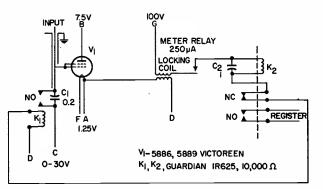

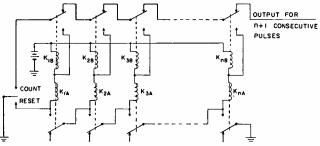

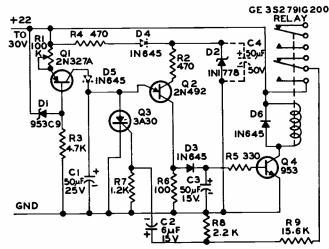

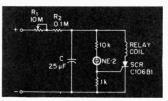

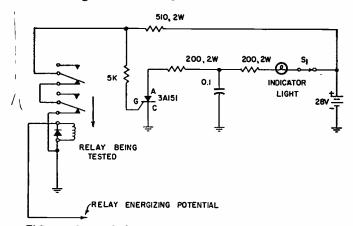

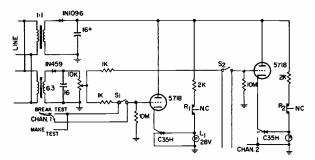

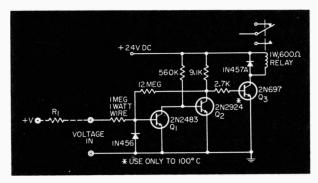

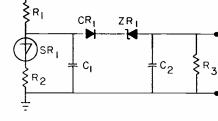

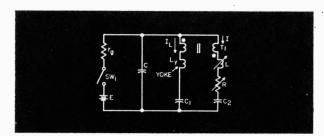

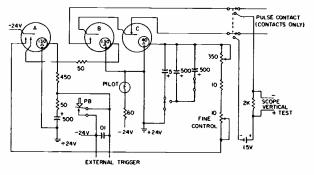

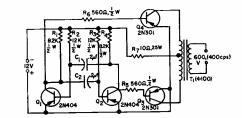

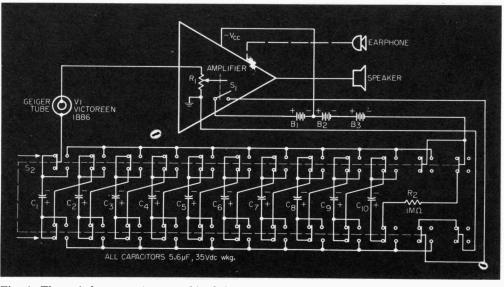

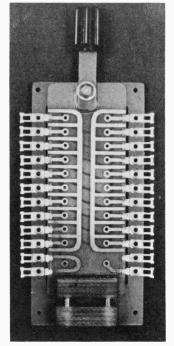

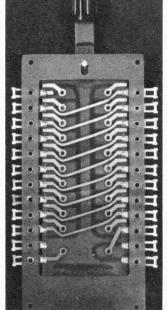

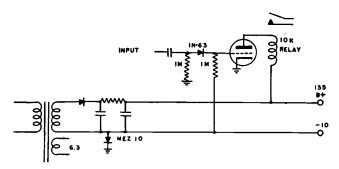

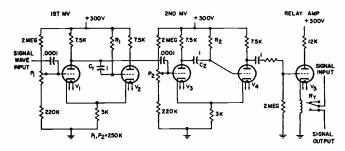

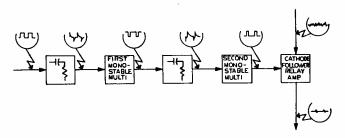

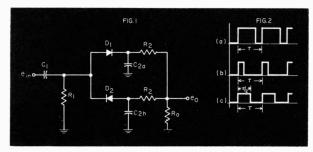

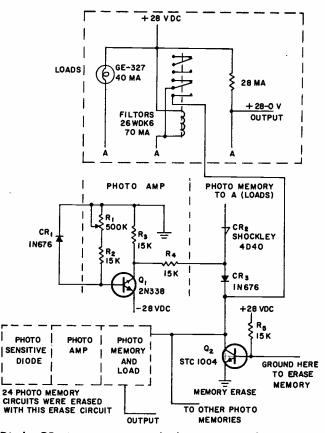

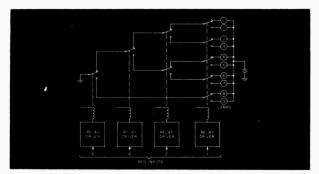

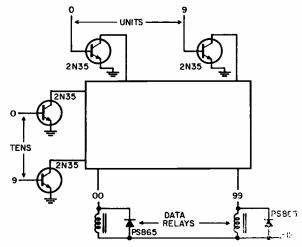

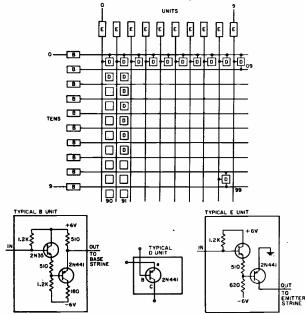

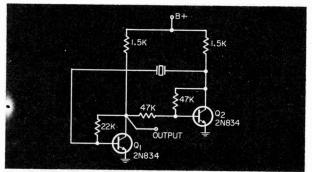

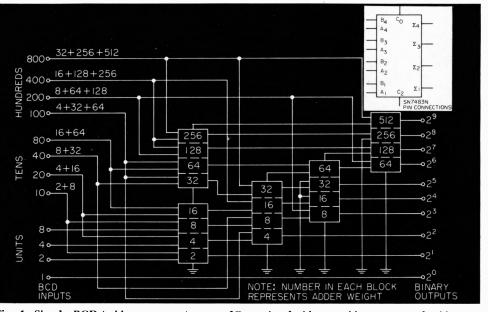

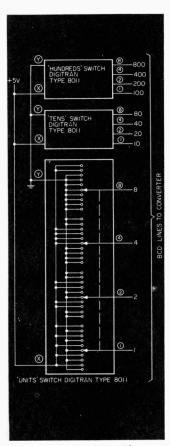

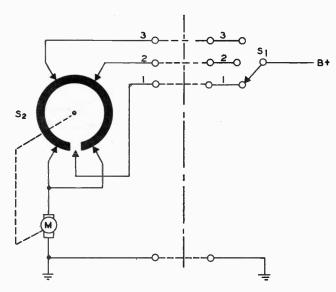

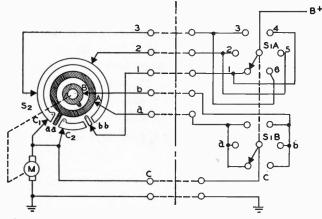

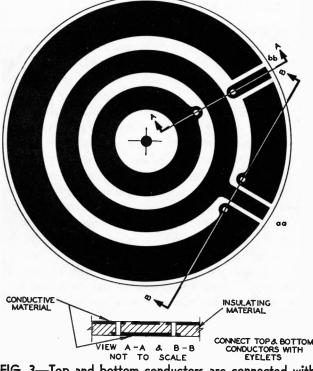

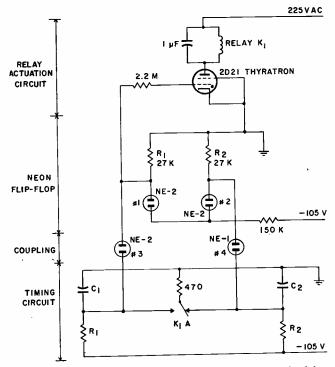

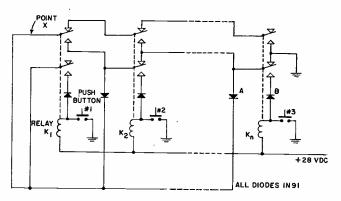

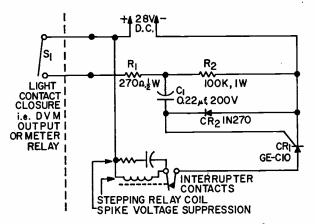

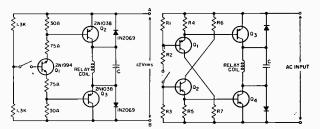

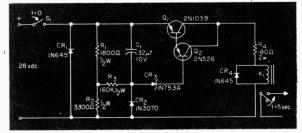

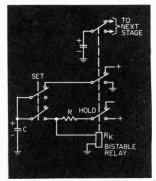

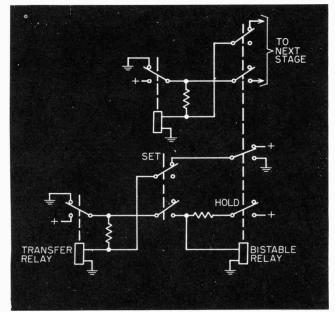

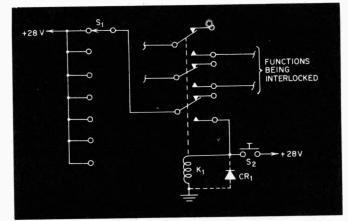

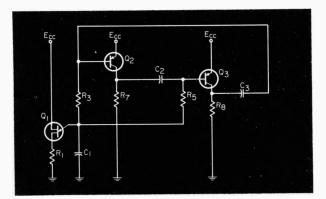

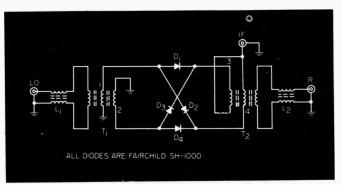

Page 331. Figure 1. Relay BCD – to – decimal converter

Page 331

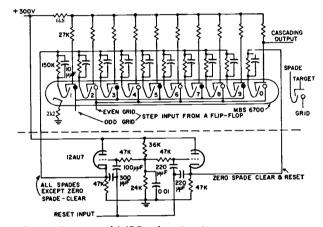

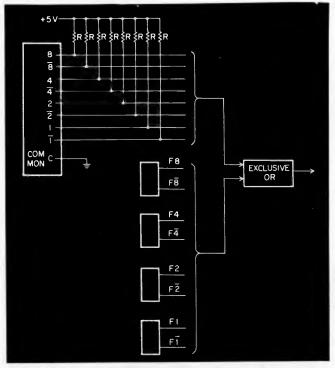

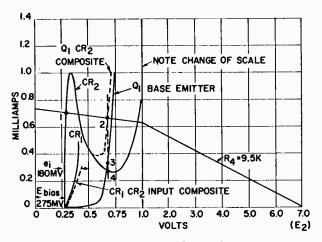

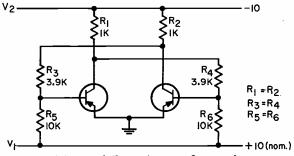

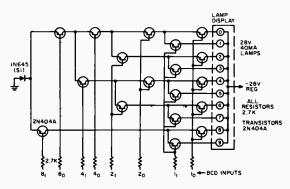

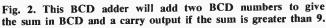

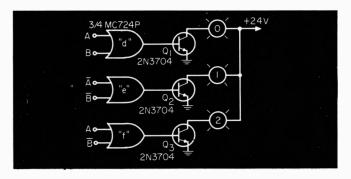

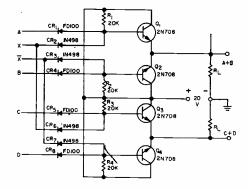

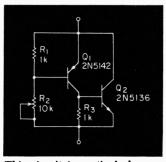

Transistor Matrix for BCD - to - Decimal Indicator

Fig. 1. Relay BCD-to-decimal converter.

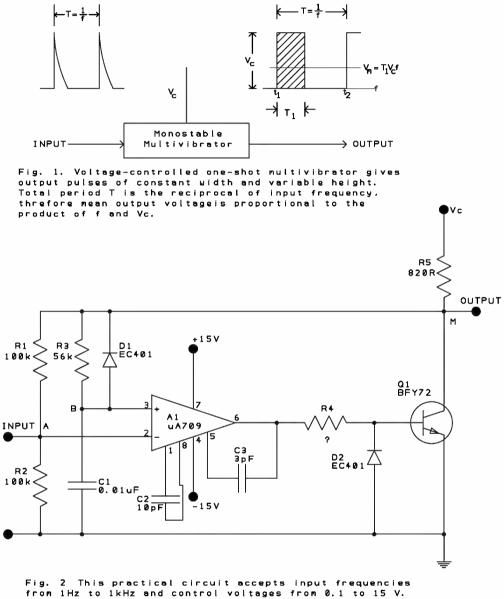

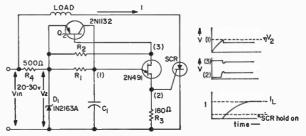

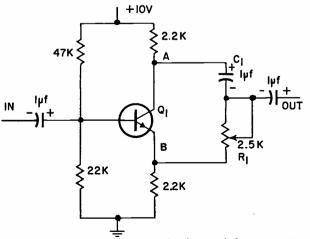

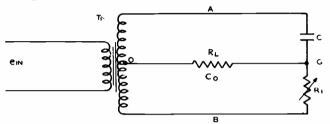

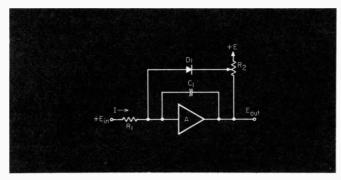

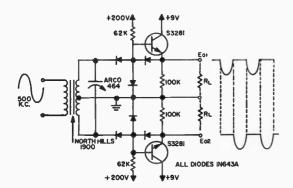

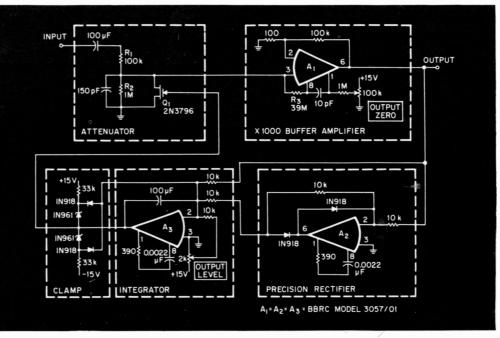

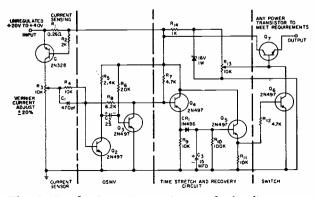

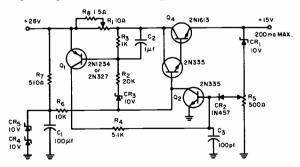

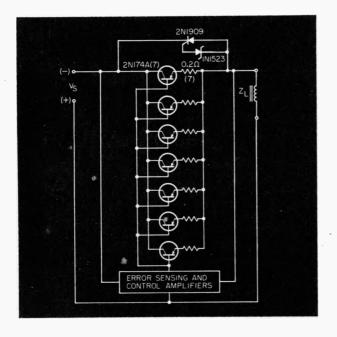

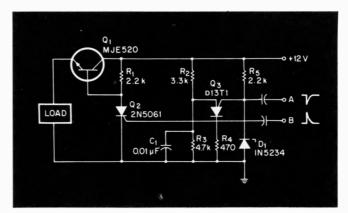

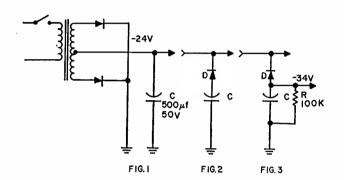

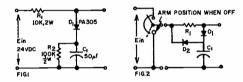

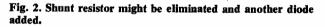

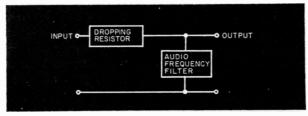

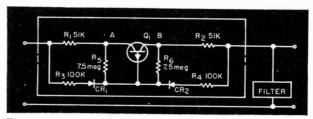

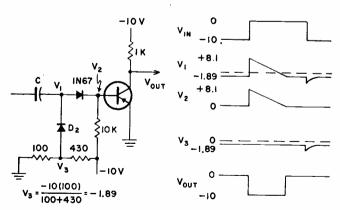

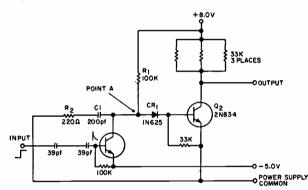

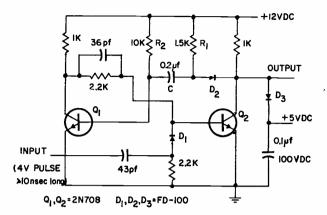

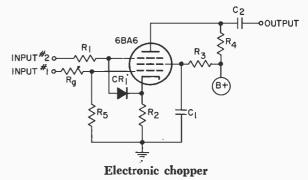

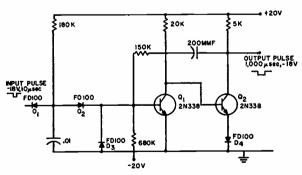

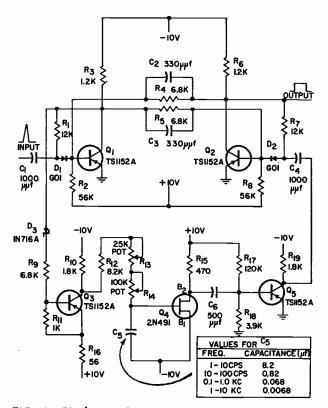

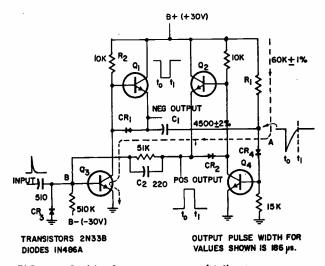

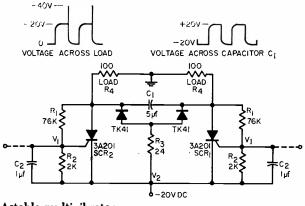

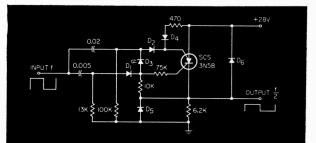

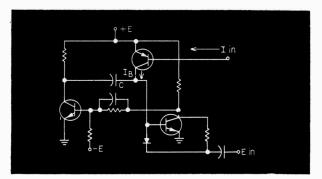

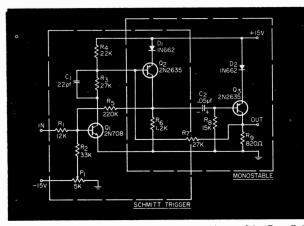

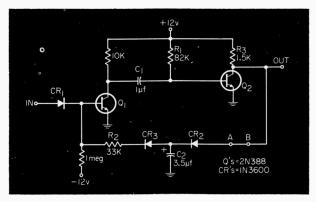

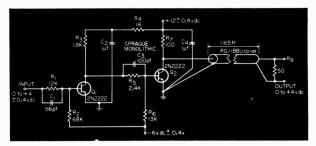

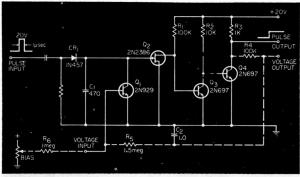

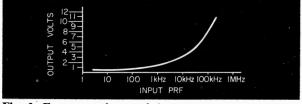

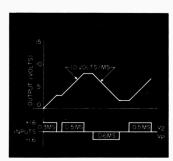

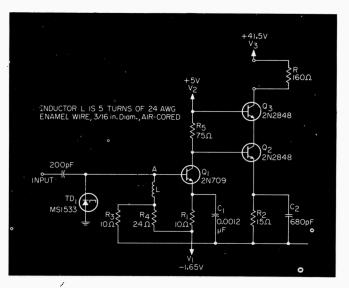

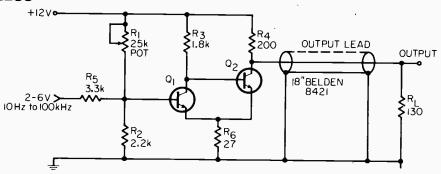

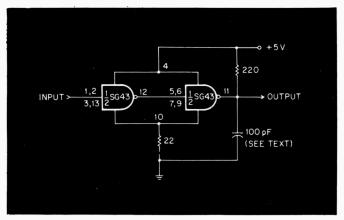

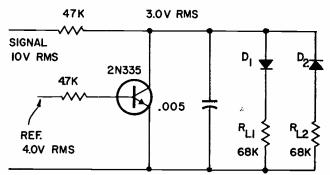

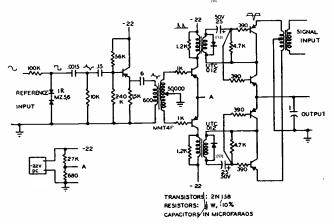

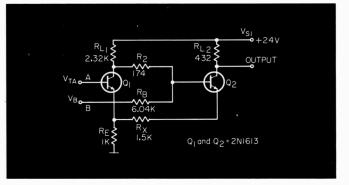

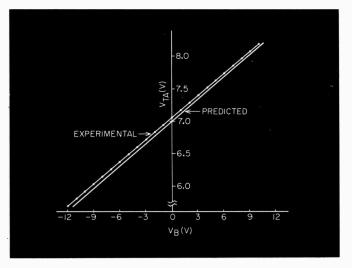

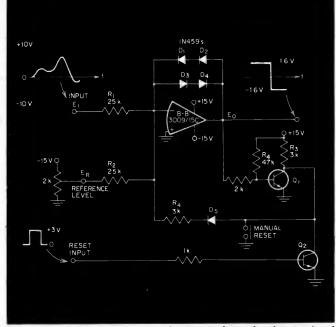

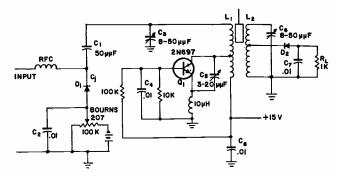

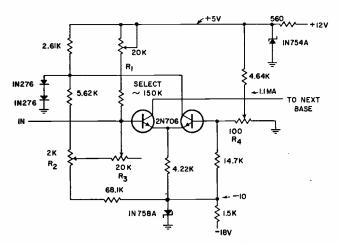

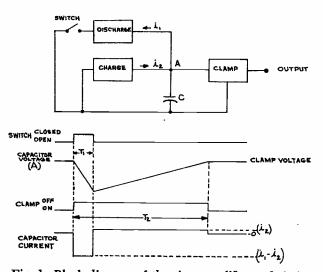

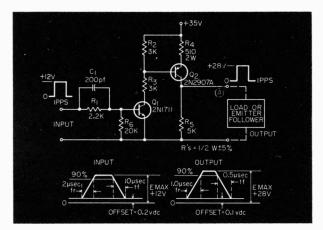

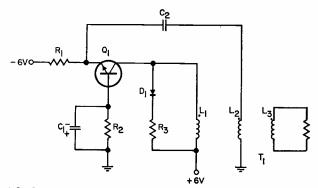

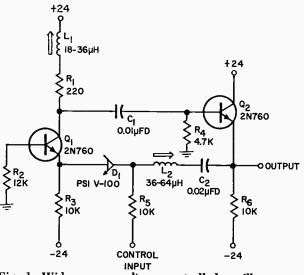

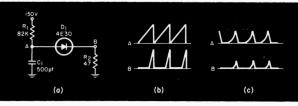

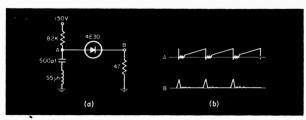

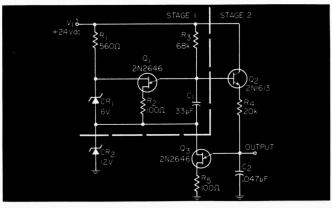

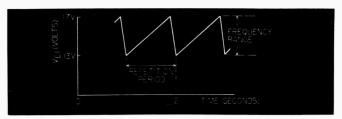

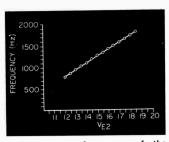

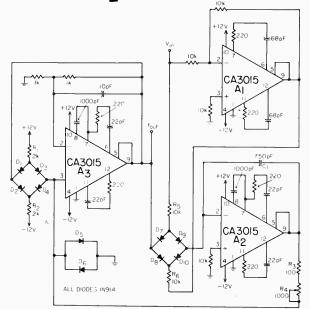

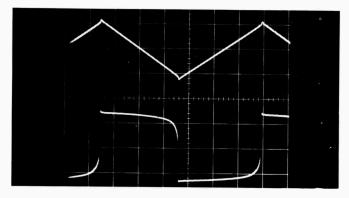

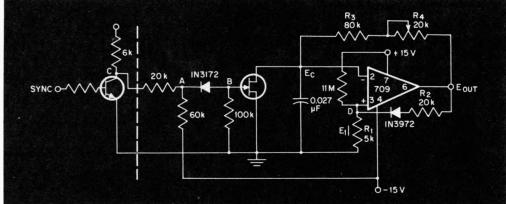

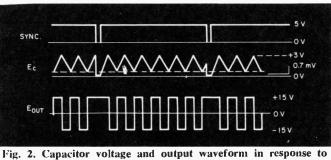

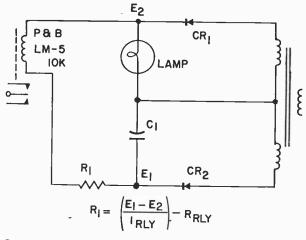

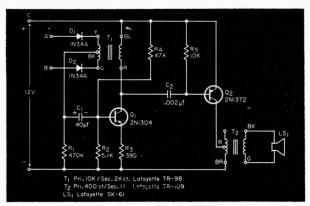

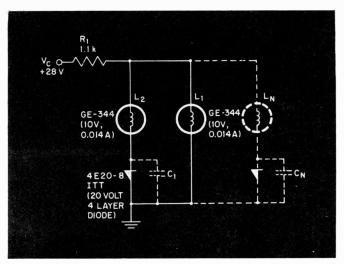

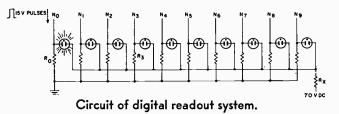

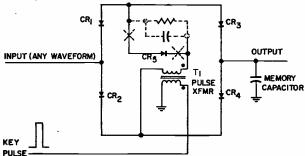

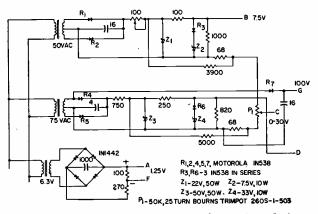

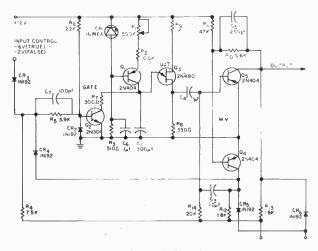

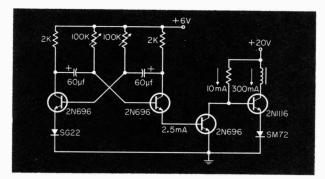

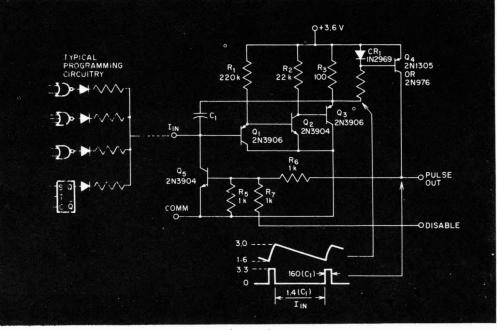

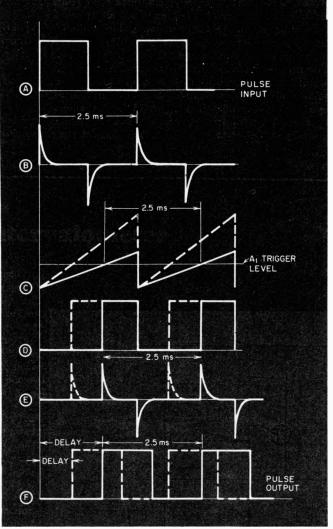

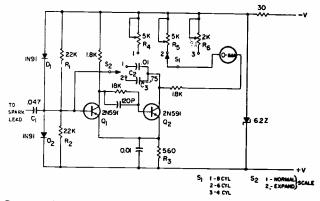

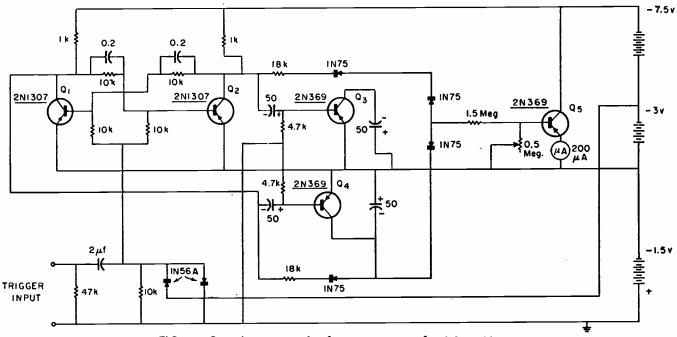

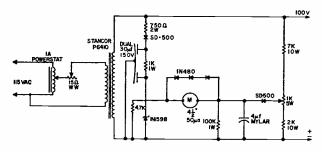

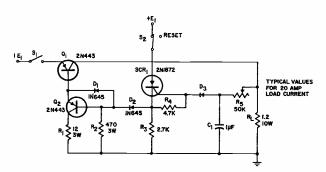

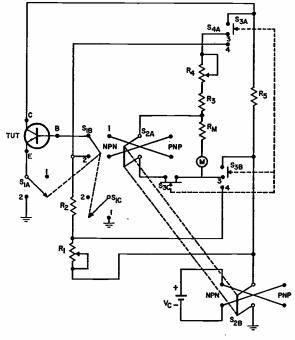

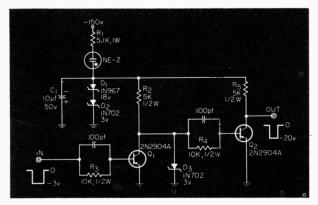

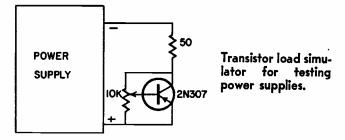

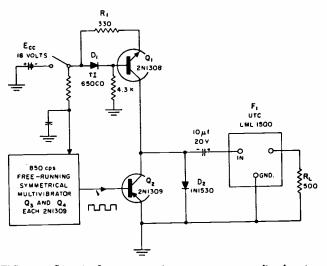

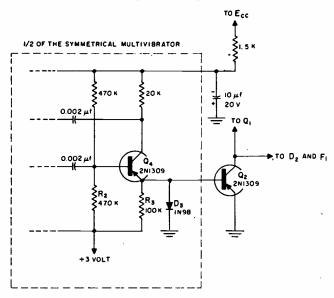

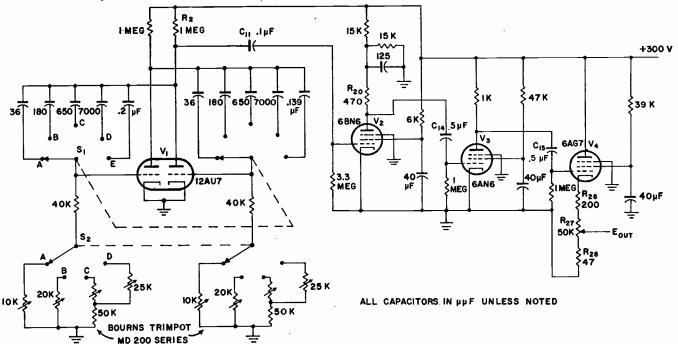

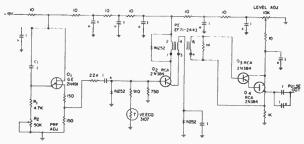

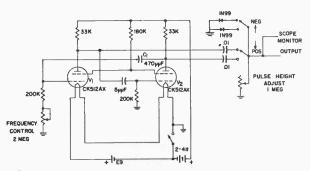

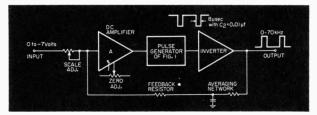

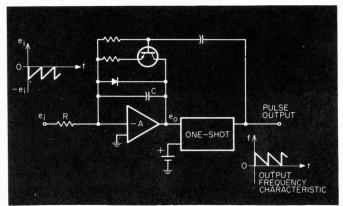

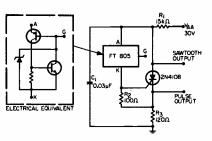

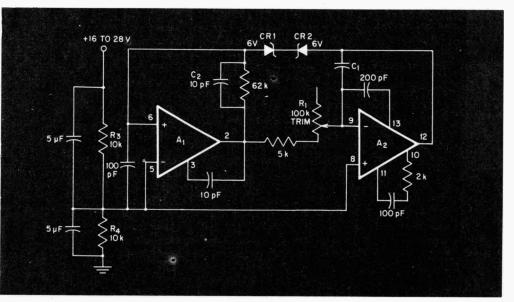

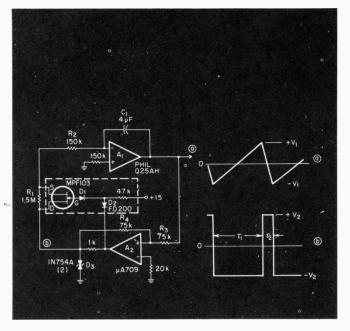

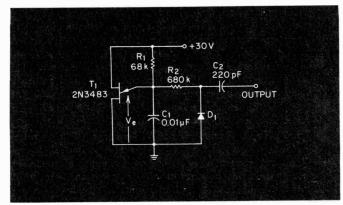

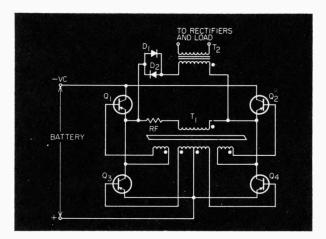

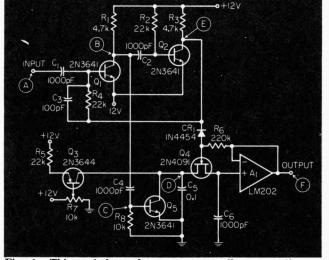

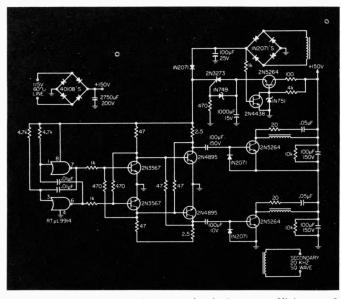

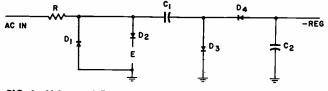

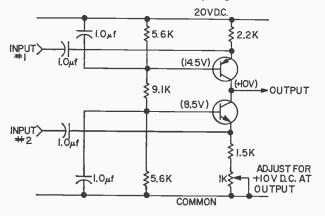

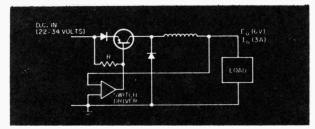

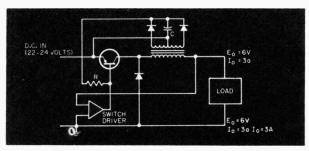

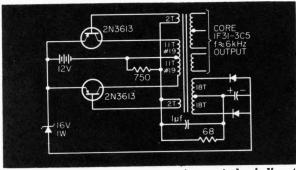

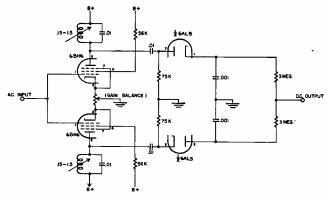

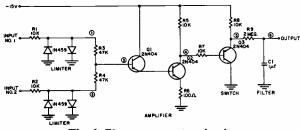

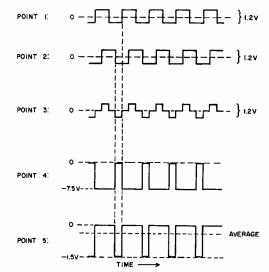

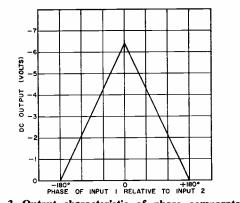

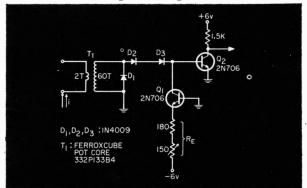

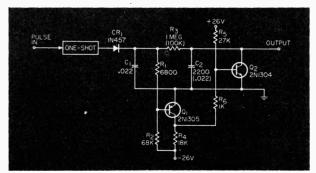

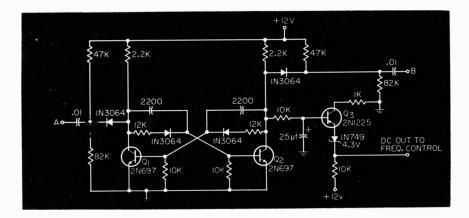

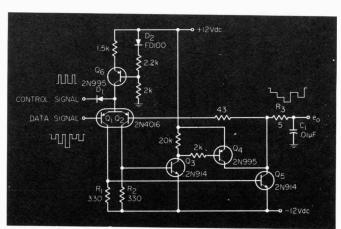

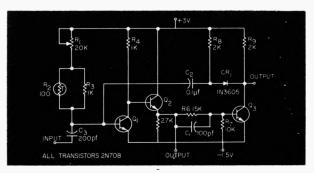

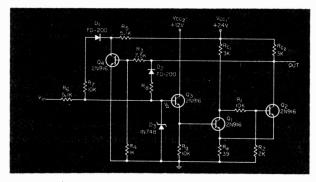

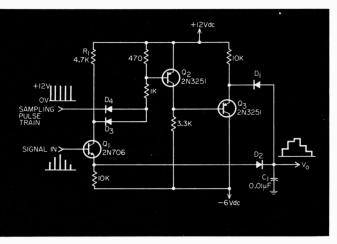

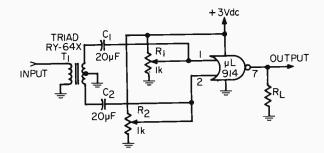

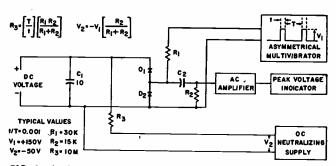

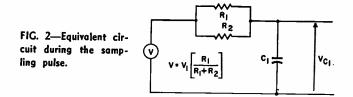

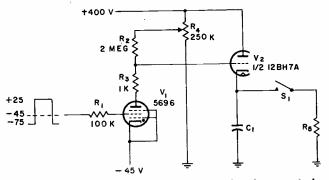

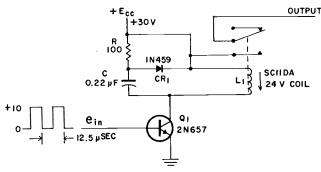

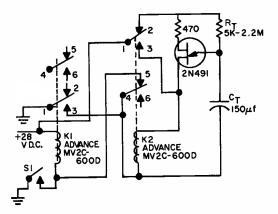

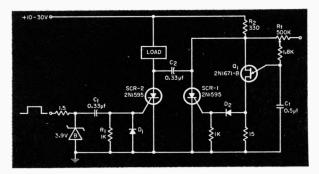

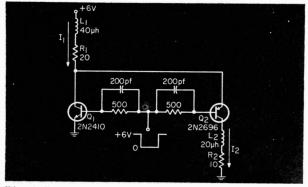

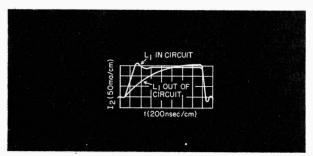

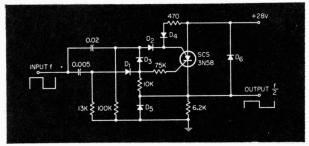

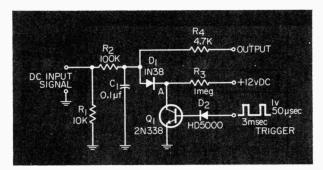

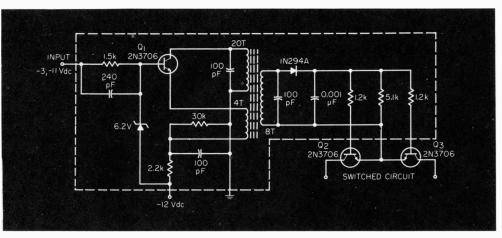

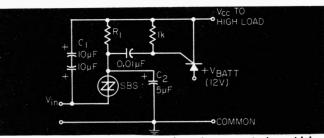

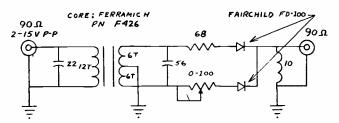

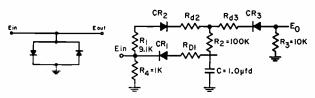

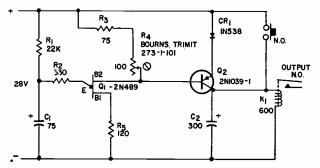

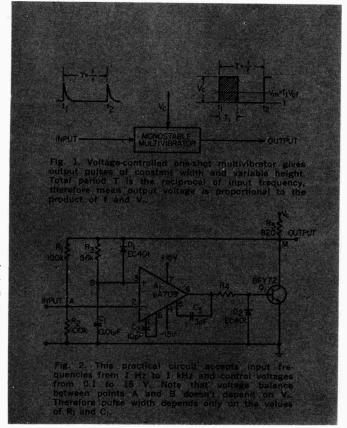

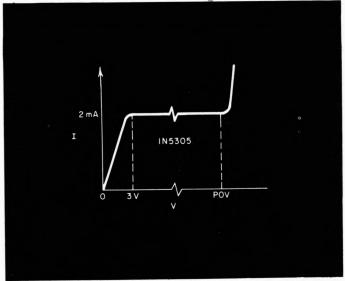

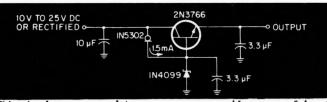

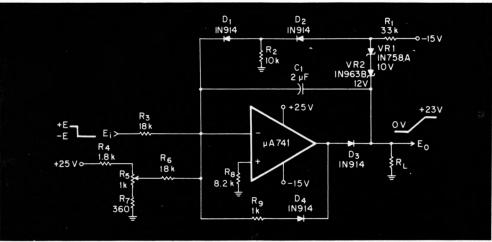

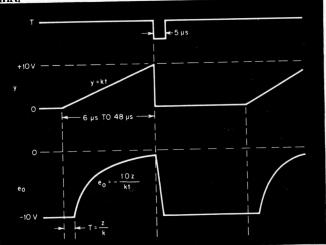

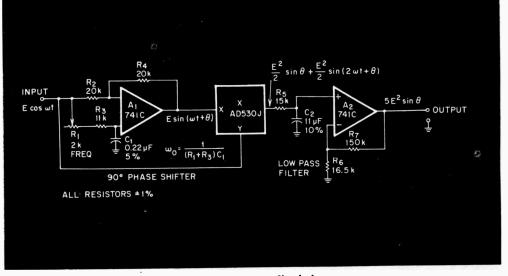

PAGE 406 Pulse-height Modulator multiplies voltage by frequency

from 1Hz to 1kHz and control voltages from 0.1 to 15 V. Note that voltage balance between points A and B doesn't depend on Vc. Therefore pulse widthdepends only on the values of R3 and C1.

Page 406: Pulse-height modulator multiplies voltage by frequency The value for R4 was not specified. Data sheet for EC401 diodes not found, probably not critical. The NTE116 diode may be a substitute (600V 1Amp diode). Many other silicon rectifier type diodes should substitute OK.

## Electronic Circuit Design Handbook

Editors of EEE Magazine

With a specially written chapter for the guidance of the English reader by W. Oliver

.

١

FOULSHAM-TAB LIMITED Slough Berks England

.

.

Foulsham-Tab Limited Yeovil Road Slough Berks England

#### Electronic Circuit Design Handbook

Copyright © 1965, 1968, 1970, 1971 and 1975 by Tab Books and Foulsham-Tab Ltd.

Reproduction or publication of the content in any manner, without the express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein. Library of Congress Number 65-24823

Cat. Code No. 101

ISBN 0-7042-0162-3

Introduction Printed and Made in Great Britain by A. Wheaton & Co., Exeter Balance printed in U.S.A. The circuits in this comprehensive book are as varied as they are numerous. There are plenty of useful projects within these pages to please and interest every keen constructor of radio, television and electronic equipment.

A little adaptation is required in some cases to suit the needs of the British user, because this is a book of American origin and the circuits were designed in the first place around American devices (mostly in the solid-state class) and components.

Where the majority of items are concerned, this is no problem at all. Most of the leading British suppliers are currently carrying large and varied stocks of American diodes, transistors, integrated circuits and, to some extent, components. The lastnamed are much scarcer over here in Americanmade types than are American semiconductors and IC's; and you may need to substitute the nearest British equivalent to some specific American make or model where certain components are concerned.

Resistors and capacitors are mostly in what might be termed a "universal" category; the values, wattage ratings, etc., are sufficiently standardized internationally to present no problem. Colourcoding is also internationally standardized (without exception, in the present writer's experience) where fixed resistors are concerned. But colour codes for capacitors are more liable to variation and you should never rely on these being the same in capacitors from different sources or countries without verification. As for colour coding of transformer leadout wires, coils, etc., this is subject to great variation and must NEVER be relied upon without checking. Mistakes over colour coding of mains transformers could be damaging or dangerous; and mistakes over colour coding of mains leads, resulting in incorrect connections to plug terminals, etc., can easily be LETHAL, so you should NEVER trust to this coding without thorough verification where any imported mains equipment is concerned.

The colour coding of American mains leads, for instance, is quite different from our own; and if you are involved in the use of these, you must make sure by checking both ends of the leads from an appliance to identify each lead beyond all possible doubt before connection is made or the plug inserted into the mains outlet point or socket.

Substitution lists for solid-state devices (which may be obtained from a variety of sources, in trade

literature from semi-conductor manufacturers, distributors or retailers, in handbooks, etc.) are a great help in finding comparable types where the designer's original specification is hard to get. The vast majority of the circuits in this book are solidstate throughout; but there are a few which include valves among the active devices. American valves are stocked by most of the leading British suppliers (mail-order firms and large retailers), but if necessary an Equivalents List will help you to select British substitutions.

In valves, exact equivalents are quite common. But transistors and some other semiconductors tend to show greater variation which makes it difficult to find any *exact* equivalent to a given type. Substitution is often a matter of choosing the nearest comparable type; but adjustment of associated biassing resistor values may be necessary when using near-equivalents or comparables. Often *one* British type will replace *many* different typenumbers in the American ranges.

In this book, the schematics show the circuits and give essential data regarding component-values, etc. No attempt is made to give constructional drawings or physical layout patterns. The information is adequate for the experienced constructor who can work quite happily from circuit diagrams and needs no other drawings.

Absolute beginners may feel rather "lost" without the aid of layout drawings and printed-circuit board designs; but the latter are often a mixed blessing, being too easily upset or even rendered useless if radical changes must be made through substitution of components differing from the original specification in size, shape and leadout configuration.

Moreover, sticking too slavishly to working drawings or detailed layout designs may tend to handicap the beginner by discouraging initiative and the ambition to plan his own designs. Using a book such as the present one compels the beginner to think and plan for himself where practical construction is concerned; and this, in the long run, is of the utmost value—though, in the early stages, it may occasionally cause some delays, disappointments or even minor disasters, through learning the hard way!

Snags to guard against, in planning a practical layout, include unwanted interaction or feedback

through placing any components which are vulnerable to these effects in too close proximity to one another, or incorrectly orientated; and risk of overheating through lack of adequate spacing or ventilation for certain components which tend to run warm or even hot.

Preliminary experimental "breadboarding" or temporary trial hook-ups will be advisable before committing oneself to more permanent and unalterable forms of construction, such as the use of printed-circuit boards (pcbs).

The question of safety looms large where beginners are involved. With projects powered entirely by low-voltage dry batteries (an inherently safe form of energy), no problem is likely to arise. But mains-powered projects are in a different category altogether. With mains there is always, lurking in the background, some element of danger. It can be a slight potential risk in cases where every reasonable precaution is taken; or it can be a downright lethal hazard if anyone goes to the opposite extreme and is utterly foolhardy. In general, although (contrary to popular belief) it is current rather than voltage which kills, the two are so inseparable that, in actual practice, one must act on the assumption that the higher the voltage the greater the risk, in most cases.

For this reason, and one or two others, British mains (running at 240 VAC 50 Hz) must be treated as more dangerous than American mains (usually running at 110–120 VAC 60 Hz, but with an alternative supply in some cases which offers twice that voltage).

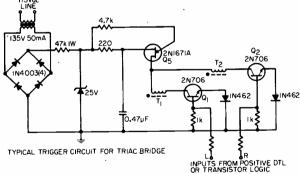

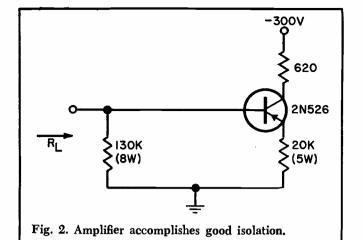

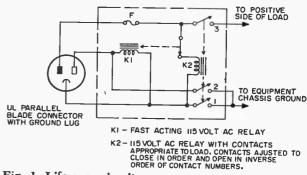

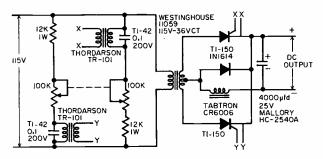

The circuits in this book, being of American origin, are mostly designed (where they fall in the mains class at all) for use on the *typical American* mains voltage of 110-120 or some figure within those limits. Thus, for example, on p. 37 Figs. 1 and 2 show circuits having a mains input from a 115VAC line.

The arrangement in Fig. 1, p. 37, is located in the actual "hot" line from the 115VAC mains and the components are in direct contact with the mains; a maximum shock risk. If this circuit were adapted for use on our 240VAC mains the danger would be even greater with this high-risk type of configuration.

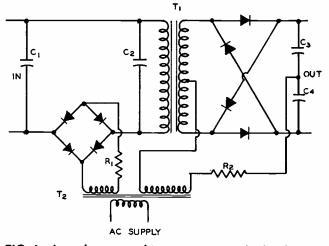

The arrangement shown in Fig. 2 on the same page, however, uses a double-wound mains trans-

former. The secondary is rated at a voltage higher than that of the American mains; in other words the transformer steps up the voltage from 115 to 135; but the double-wound arrangement isolates the user from direct contact with the mains on the secondary side of the transformer, and the current through the secondary is nominally only 50mA in normal operation.

For use on British mains the transformer would need to have a 240VAC primary winding, and in this case would be chosen to step *down* the yoltage, as only 135 volts output is required from the secondary.

Some American circuit designs are easily adaptable for British mains—say, by provision of a suitable double-wound mains transformer—while others are less amenable to easy conversion. Whatever method is proposed, make sure it is a *safe* one.

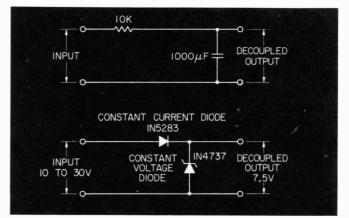

Nothing in this book must be misconstrued as an encouragement to construct or use any projects in a way which would contravene existing safety rules or regulations. If you are in the slightest doubt about any matter affecting safety, *don't take risks*; seek expert advice from a competent source, preferably at a local level. Some arrangements which are quite reasonably safe in one environment may be dangerous or even lethal in different surroundings. (That is, of course, the reason for extra stringent precautions in, for example, bathrooms where electrical equipment is concerned.)

To avoid delays or disappointments in completing constructional projects, make absolutely sure beforehand that you can obtain *all* the necessary components or materials, either in the specified form or in acceptable substitutions. Nothing is more annoying than to spend hours and pounds on a project only to find that supplies of some essential component are nowhere to be had!

Comprehensive catalogues can be bought from leading suppliers such as Home Radio of Mitcham, Laskys of London and other towns, Doram of Leeds, A. Marshall's of London and Glasgow, Electrovalue of Egham, Henrys of London, and various other firms. For full particulars and complete addresses of these concerns, see the advertisement pages of the principal technical journals catering for radio, electronic, and TV interests.

With over 400 different circuits involved in this book, it is obviously impossible in the present chapter to cover all the points that must be allowed for in using these circuits for British versions of the projects.

The reader must, therefore, bear in mind the general principles of British and American electrical and electronic practice, making due allowance for the specific differences between the respective systems or techniques.

For example, where television circuits are concerned, one must remember that the various British standards involved are different from the American ones. Very briefly, the chief points of difference include these: American, 525 lines; British, 405 (the obsolescent standard) and 625 lines. British 405-line transmitters, working on VHF channels and with AM sound accompanying the vision, are being gradually phased out. The 625-line transmitters on UHF channels supersede them, and these have FM sound on an intercarrier system.

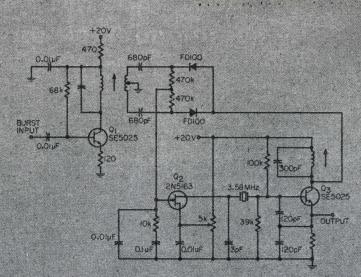

American stations use FM sound with intercarrier at 4.5 MHz, British intercarrier is at 6 MHz. In colour TV, the Americans use the NTSC system, whereas we use a modified PAL system. The American colour subcarrier is 3.58 MHz, and ours is 4.43 MHz. (An example of a circuit based on the American 3.58-MHz version is on p. 177.)

Radio and other regulations differ in different countries. What is legal in the States is not necessarily legal here. Latest information should be obtained from the official departments concerned, if you are contemplating anything that could possibly contravene transmitting licence regulations, telephone regulations, etc. It is, in general, a punishable offence to operate a radio transmitter without the appropriate licence. The Radio Regulatory department of the Home Office, which deals with such matters, is at Waterloo Bridge House, Waterloo Road, London SE1 8UA.

A project such as that on p. 410, Automatic Telephone Recorder, would contravene regulations (of the Post Office) in this country and should be regarded therefore as of academic and not practical interest over here.

# Electronic Circuit Design Handbook

,

# Electronic Circuit Design Handbook

Editors of EEE Magazine

With a specially written chapter for the guidance of the English reader by W. Oliver

Foulsham-Tab Limited Yeovil Road Slough Berks England

#### Electronic Circuit Design Handbook

Copyright © 1965, 1968, 1970, 1971 and 1975 by Tab Books and Foulsham-Tab Ltd.

Reproduction or publication of the content in any manner, without the express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein. Library of Congress Number 65-24823 Cat. Code No. 101

ISBN 0-7042-0162-3

Introduction Printed and Made in Great Britain by A. Wheaton & Co., Exeter Balance printed in U.S.A. The circuits in this comprehensive book are as varied as they are numerous. There are plenty of useful projects within these pages to please and interest every keen constructor of radio, television and electronic equipment.

A little adaptation is required in some cases to suit the needs of the British user, because this is a book of American origin and the circuits were designed in the first place around American devices (mostly in the solid-state class) and components.

Where the majority of items are concerned, this is no problem at all. Most of the leading British suppliers are currently carrying large and varied stocks of American diodes, transistors, integrated circuits and, to some extent, components. The lastnamed are much scarcer over here in Americanmade types than are American semiconductors and IC's; and you may need to substitute the nearest British equivalent to some specific American make or model where certain components are concerned.

Resistors and capacitors are mostly in what might be termed a "universal" category; the values, wattage ratings, etc., are sufficiently standardized internationally to present no problem. Colourcoding is also internationally standardized (without exception, in the present writer's experience) where fixed resistors are concerned. But colour codes for capacitors are more liable to variation and you should never rely on these being the same in capacitors from different sources or countries without verification. As for colour coding of transformer leadout wires, coils, etc., this is subject to great variation and must NEVER be relied upon without checking. Mistakes over colour coding of mains transformers could be damaging or dangerous; and mistakes over colour coding of mains leads, resulting in incorrect connections to plug terminals, etc., can easily be LETHAL, so you should NEVER trust to this coding without thorough verification where any imported mains equipment is concerned.

The colour coding of American mains leads, for instance, is quite different from our own; and if you are involved in the use of these, you must make sure by checking both ends of the leads from an appliance to identify each lead beyond all possible doubt before connection is made or the plug inserted into the mains outlet point or socket.

Substitution lists for solid-state devices (which may be obtained from a variety of sources, in trade literature from semi-conductor manufacturers, distributors or retailers, in handbooks, etc.) are a great help in finding comparable types where the designer's original specification is hard to get. The vast majority of the circuits in this book are solidstate throughout; but there are a few which include valves among the active devices. American valves are stocked by most of the leading British suppliers (mail-order firms and large retailers), but if necessary an Equivalents List will help you to select British substitutions.

In valves, exact equivalents are quite common. But transistors and some other semiconductors tend to show greater variation which makes it difficult to find any *exact* equivalent to a given type. Substitution is often a matter of choosing the nearest comparable type; but adjustment of associated biassing resistor values may be necessary when using near-equivalents or comparables. Often one British type will replace many different typenumbers in the American ranges.

In this book, the schematics show the circuits and give essential data regarding component-values, etc. No attempt is made to give constructional drawings or physical layout patterns. The information is adequate for the experienced constructor who can work quite happily from circuit diagrams and needs no other drawings.

Absolute beginners may feel rather "lost" without the aid of layout drawings and printed-circuit board designs; but the latter are often a mixed blessing, being too easily upset or even rendered useless if radical changes must be made through substitution of components differing from the original specification in size, shape and leadout configuration.

Moreover, sticking too slavishly to working drawings or detailed layout designs may tend to handicap the beginner by discouraging initiative and the ambition to plan his own designs. Using a book such as the present one compels the beginner to think and plan for himself where practical construction is concerned; and this, in the long run, is of the utmost value—though, in the early stages, it may occasionally cause some delays, disappointments or even minor disasters, through learning the hard way!

Snags to guard against, in planning a practical layout, include unwanted interaction or feedback

through placing any components which are vulnerable to these effects in too close proximity to one another, or incorrectly orientated; and risk of overheating through lack of adequate spacing or ventilation for certain components which tend to run warm or even hot.

Preliminary experimental "breadboarding" or temporary trial hook-ups will be advisable before committing oneself to more permanent and unalterable forms of construction, such as the use of printed-circuit boards (pcbs).

The question of safety looms large where beginners are involved. With projects powered entirely by low-voltage dry batteries (an inherently safe form of energy), no problem is likely to arise. But mains-powered projects are in a different category altogether. With mains there is always, lurking in the background, some element of danger. It can be a slight potential risk in cases where every reasonable precaution is taken; or it can be a downright lethal hazard if anyone goes to the opposite extreme and is utterly foolhardy. In general, although (contrary to popular belief) it is current rather than voltage which kills, the two are so inseparable that, in actual practice, one must act on the assumption that the higher the voltage the greater the risk, in most cases.

For this reason, and one or two others, British mains (running at 240 VAC 50 Hz) must be treated as more dangerous than American mains (usually running at 110–120 VAC 60 Hz, but with an alternative supply in some cases which offers twice that voltage).

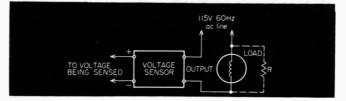

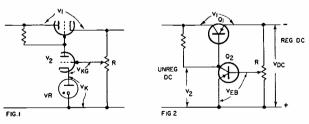

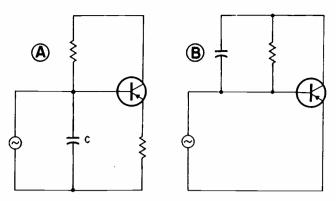

The circuits in this book, being of American origin, are mostly designed (where they fall in the mains class at all) for use on the *typical American mains voltage of 110–120* or some figure within those limits. Thus, for example, on p. 37 Figs. 1 and 2 show circuits having a mains input from a 115VAC line.

The arrangement in Fig. 1, p. 37, is located in the actual "hot" line from the 115VAC mains and the components are in direct contact with the mains; a maximum shock risk. If this circuit were adapted for use on our 240VAC mains the danger would be even greater with this high-risk type of configuration.

The arrangement shown in Fig. 2 on the same page, however, uses a double-wound mains trans-

former. The secondary is rated at a voltage higher than that of the American mains; in other words the transformer steps up the voltage from 115 to 135; but the double-wound arrangement isolates the user from direct contact with the mains on the secondary side of the transformer, and the current through the secondary is nominally only 50mA in normal operation.

For use on British mains the transformer would need to have a 240VAC primary winding, and in this case would be chosen to step *down* the voltage, as only 135 volts output is required from the secondary.

Some American circuit designs are easily adaptable for British mains—say, by provision of a suitable double-wound mains transformer—while others are less amenable to easy conversion. Whatever method is proposed, make sure it is a *safe* one.

Nothing in this book must be misconstrued as an encouragement to construct or use any projects in a way which would contravene existing safety rules or regulations. If you are in the slightest doubt about any matter affecting safety, don't take risks; seek expert advice from a competent source, preferably at a local level. Some arrangements which are quite reasonably safe in one environment may be dangerous or even lethal in different surroundings. (That is, of course, the reason for extra stringent precautions in, for example, bathrooms where electrical equipment is concerned.)

To avoid delays or disappointments in completing constructional projects, make absolutely sure beforehand that you can obtain *all* the necessary components or materials, either in the specified form or in acceptable substitutions. Nothing is more annoying than to spend hours and pounds on a project only to find that supplies of some essential component are nowhere to be had!

Comprehensive catalogues can be bought from leading suppliers such as Home Radio of Mitcham, Laskys of London and other towns, Doram of Leeds, A. Marshall's of London and Glasgow, Electrovalue of Egham, Henrys of London, and various other firms. For full particulars and complete addresses of these concerns, see the advertisement pages of the principal technical journals catering for radio, electronic, and TV interests.

With over 400 different circuits involved in this book, it is obviously impossible in the present chapter to cover all the points that must be allowed for in using these circuits for British versions of the projects.

The reader must, therefore, bear in mind the general principles of British and American electrical and electronic practice, making due allowance for the specific differences between the respective systems or techniques.

For example, where television circuits are concerned, one must remember that the various British standards involved are different from the American ones. Very briefly, the chief points of difference include these: American, 525 lines; British, 405 (the obsolescent standard) and 625 lines. British 405-line transmitters, working on VHF channels and with AM sound accompanying the vision, are being gradually phased out. The 625-line transmitters on UHF channels supersede them, and these have FM sound on an intercarrier system.

American stations use FM sound with intercarrier at 4.5 MHz, British intercarrier is at 6 MHz. In colour TV, the Americans use the NTSC system, whereas we use a modified PAL system. The American colour subcarrier is 3.58 MHz, and ours is 4.43 MHz. (An example of a circuit based on the American 3.58-MHz version is on p. 177.)

Radio and other regulations differ in different countries. What is legal in the States is not necessarily legal here. Latest information should be obtained from the official departments concerned, if you are contemplating anything that could possibly contravene transmitting licence regulations, telephone regulations, etc. It is, in general, a punishable offence to operate a radio transmitter without the appropriate licence. The Radio Regulatory department of the Home Office, which deals with such matters, is at Waterloo Bridge House, Waterloo Road, London SE1 8UA.

A project such as that on p. 410, Automatic Telephone Recorder, would contravene regulations (of the Post Office) in this country and should be regarded therefore as of academic and not practical interest over here.

۰.

# Preface

While many of us may be reluctant to admit it, most modern electronic circuits are patterned after existing designs. A generation ago the minds of men like Eccles and Jordan, Wheeler, Hazeltine, Black, Schmitt, Hartley, Armstrong, and others developed the basic designs for many of today's circuits. Yet, even today, truly original circuits, bearing almost no resemblance to anything previously developed, occasionally reach the light of day. For the most part, however, the majority of new circuits are modifications of previous designs.

It is indeed fortunate that we do not slavishly worship a cult of originality simply for the sake of originalty. How wasteful it would be of our nation's engineering talent if we repeatedly re-invented the Schmitt trigger, the blocking oscillator, or the flip-flop. In truth, our progress can be measured in how successfully we can stand on each other's shoulders. Previously designed circuits are continually modified, refined, and improved as engineers adapt them to their specific needs. This is genuine progress.

This volume is a collection of circuits originally published in EEE magazine. The circuits were selected for their originality, novelty, or sophistication—but most of all, they were selected for their usefulness. These award-winning circuits can be used as building blocks in designing circuit configurations best suited to your needs. Most importantly, however, these circuits will serve as imagination triggers, stimulating you to think of more efficient designs for specific applications.

In this expanded Fourth Edition, 639 individual circuit designs are included, arranged as much as possible by function and applications. Of course, many circuits serve a multitude of functions and can serve in a myriad of applications. Some control circuits, for example, can also be classed as sensing or detection circuits. Many multivibrators described in the Pulse Circuits Section are also oscillator circuits. Thus, when seeking a circuit for a specific function, you'll find scanning the Contents pages the easiest way to locate the most applicable designs.

This book is the answer to the long-felt need for a one-source handbook of triedand-tested circuits. It is also the answer to thousands of requests from readers of EEE, who virtually demanded that these circuits be published in book form.

The Editors

#### **Table of Contents**

#### Section One—CONTROL CIRCUITS

- 21....A Reliable Open Loop Amplifier

- 22....Zero-Crossing Sync Circuit For SCRs

- 22....Instrument Servo Cycling Circuit

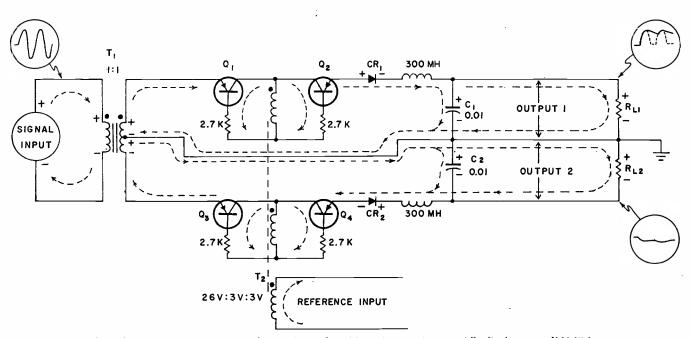

- 23....Double-Channel Servo Controls Two Motors

- 23.... Unijunction Latchup for SCR's Driving Inductive Loads

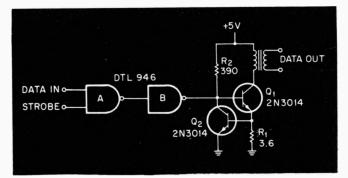

- 23....Simple Intervalometer

- 24....SCR-Zener Combination Senses Voltage Limits

- 24.... Transistorized Phase Shifter

- 25....SCR Voltage Sensitive Time Delay Switch

- 25.... Transistorized Motor Switching Circuit

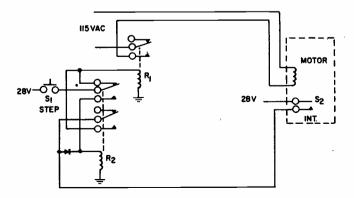

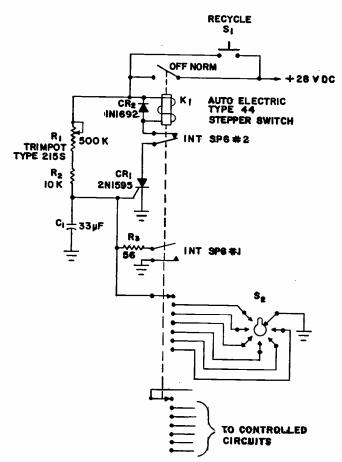

- 26....Step Control for Motor-Driven Selector Switch

- 26....Beam Switching Tube Reset

- 27....Gain Control

- 27....Supervisory and Protective Relay Control

- 28....Variable Transistorized Phase Shifter

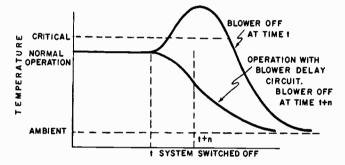

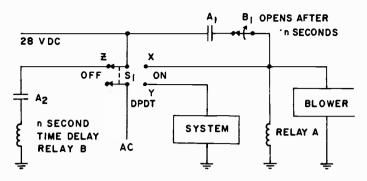

- 29....Blower Delay Circuit

- 29....Low Cost Servo Motor Control

- 31....Control Switching Circuit

- 31....Remote Controlled Rotary Switch

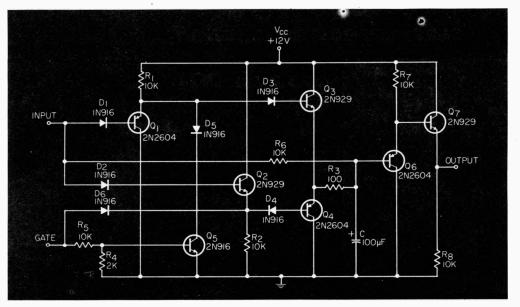

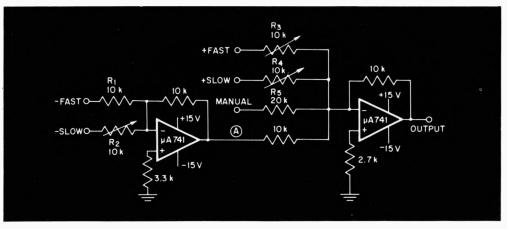

- 32....Non-Interacting Positioning and Attenuating Controls

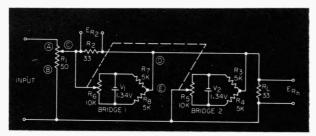

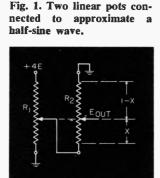

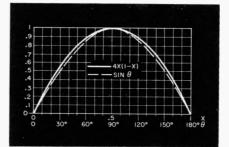

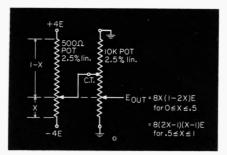

- 33....Dual-Linear Pot Approximates Sine Pot

- 33....Wide-Range Delay Circuit

- 34....Peak-Hold Circuit

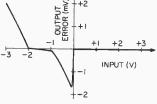

- 35.... Modified Limiter With Improved Accuracy

- 35....Signal-Powered DC Voltage Sensor Controls AC Loads

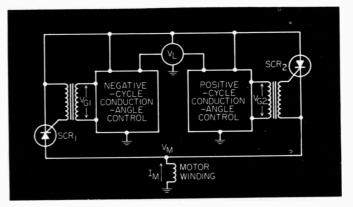

- 36....Simple Modification Prevents Single-Cycling With SCR Motor Drive

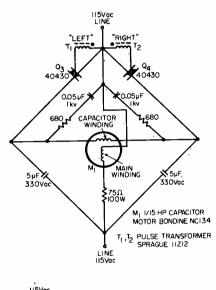

- 37....High-Voltage Triacs Reverse Capacitor Motor

- 38.... Variable Control for Automobile Windshield Wiper

#### Section Two-REGULATOR CIRCUITS

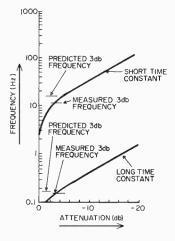

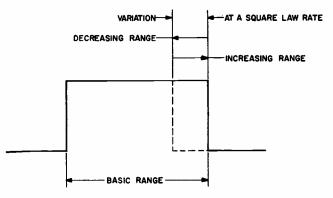

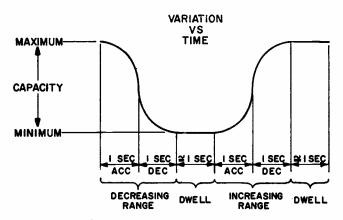

- **39....A Time-Variant Attenuator**

- 40....Servo-Motor Winding Stabilizes Power Amplifier Operating Point

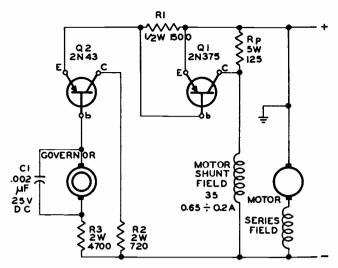

- 40....Motor Speed Control

- 41....Zener Diode Regulator

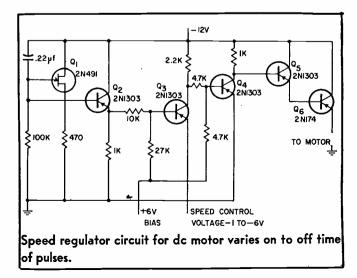

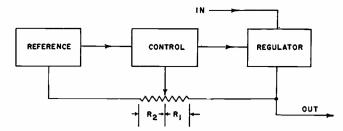

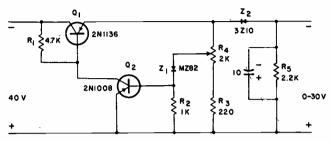

- 41....Transistorized Speed Regulator

- 42....Snap Action Level Switch

- 42....Low-Voltage Transistor Series Regulator

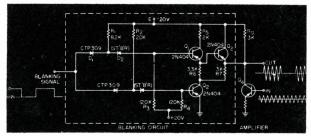

- 43....Blanking Circuit Clamps to DC Level

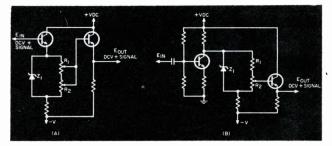

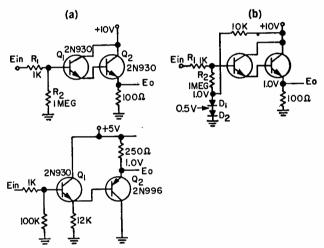

- 43....Non-Attenuating Voltage-Control Circuits

- 44....Temperature-Stabilized Darlington

- 44....Low Cost Transistor Voltage Regulator

- 45....Transistor Voltage Regulator

- 45....AGC Amplifier

- 46....High Frequency DC Restoration With Gain

- 46....Zero Impedance Voltage Regulator

- 49....Two-Terminal Constant-Current Device

- 47....Regulator Makes Two Power Supplies Out of One

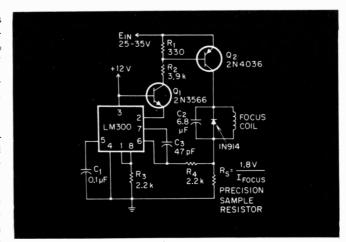

- 48....An Efficient Focus-Current Regulator Using the LM300

- 49....CRD Simplifies Design of Voltage Regulators

- 50....FET Improves Voltage Regulation and Allows Current Limiting

- 50....Temperature-Stabilized Constant-Current Source

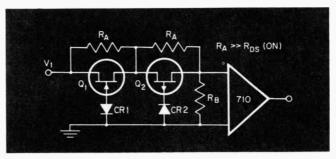

- 51....MOS-FET Provides 60-DB Dynamic Range Low-Frequency AGC Circuit

- 52....An Inexpensive Bipolar Current Limiter

- 52....High-Efficiency Series Regulator

- 53....Modulated DC Voltage Regulator

- 53....High-Efficiency Series Regulator

- 54....Spare IC Gate Serves as Regulator

- 54....Short-Protected Current Limiter Ignores Inrush Currents

#### Section Three—PROTECTION CIRCUITS

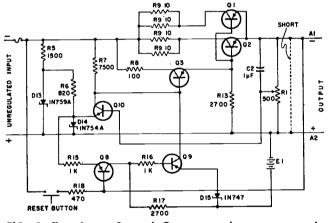

- 55.... High Voltage Power Supply Protective Circuit

- 56....Automatic Overload Circuit

- 56....Capacitor Discharger

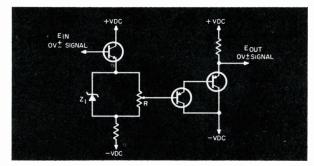

- 57....Differential Voltage Circuit Protector

- 57....An Electronic Circuit Protector

- 58....Short-Circuit Protection of Regulated Power Supply

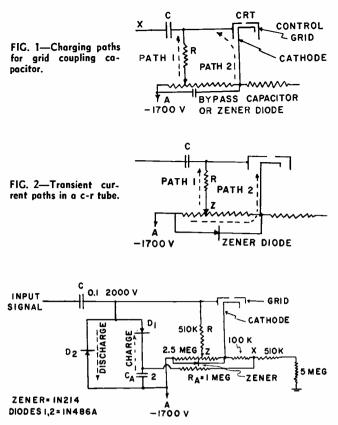

- 58....Cathode-Ray Tube Grid Protection Circuit

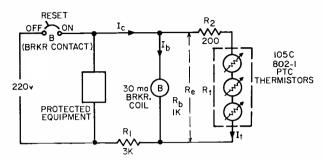

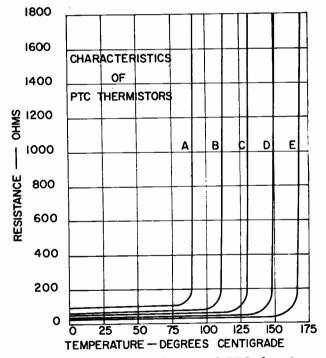

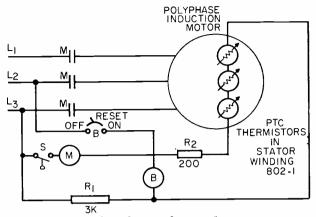

- 59.... PTC Thermistors Trip 50 Amp Contact at Limiting Temp

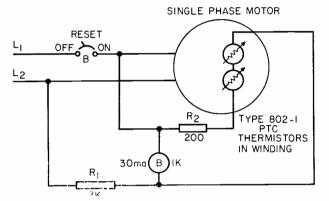

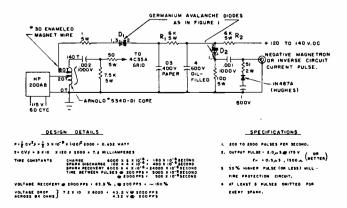

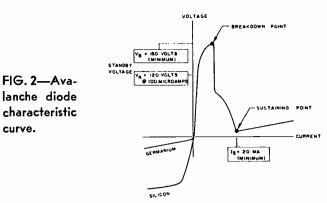

- 61....A Novel Magnetron Protection Circuit

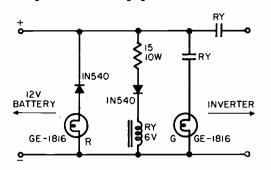

- 61....Inverter Control

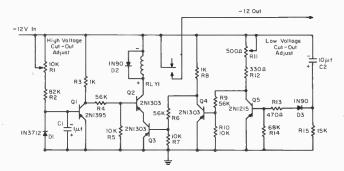

- 62....Low-Voltage Cutoff Circuit

- 62....Overload Protection

- 63....Lifesaver Circuit

- 63....High Input Impedance Meter-Protection Circuit

- 64....Single-Transistor Short-Circuit Detector

- 64....Inexpensive Short-Proof Voltage Regulator

- 64....Reduced-Power Overload Protection

- 65....Simple Reverse-Phase Protection

- 65....Duty-Cycle Limiter

- 66....Zener-Gated SCR Protection for Power Transistors

- 66....Zener Stabilizes Phase-Shift Oscillator

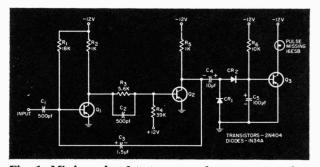

- 67....Current Transformer Gives Fast Overload Protection

- 67....FET Provides Automatic Meter Protection

- 68....Solid-State Relay-Circuit Breaker

- 69....Overvoltage-Protection Circuit for IC Power Supplies

- 69....Adjustable-Overvoltage Circuit Breaker

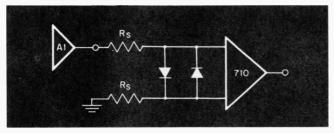

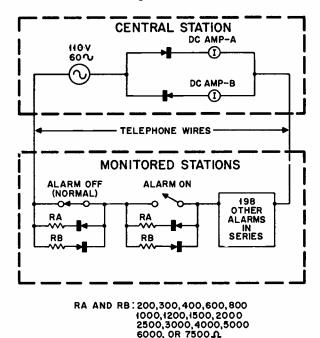

- 70.... Modified 710 Maintains Accuracy at High Input Voltages

- 70....FET Protection for op Amps

#### Section Four-FILTER & SUPPRESSION CIRCUITS

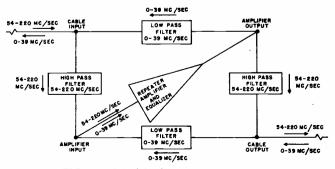

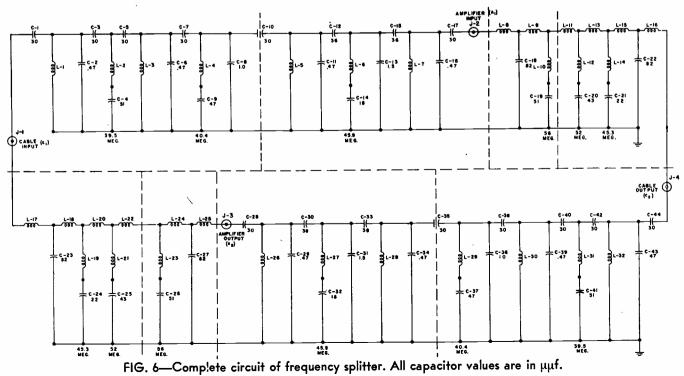

- 71....Directional Frequency Splitter Filter

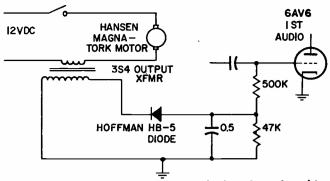

- 73....Muting System for Motor-Tuned Receivers

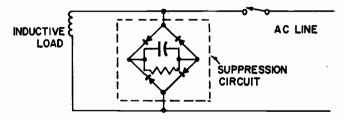

- 73.... Transient Suppressor for AC Circuits

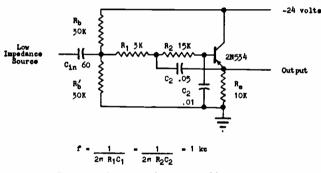

- 74....Active Second Order Filter

- 74....Variable Rejection Band Filter

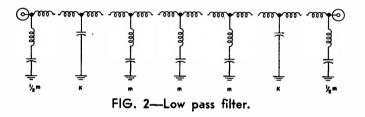

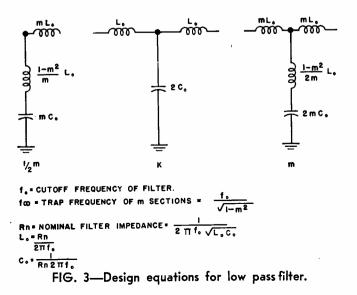

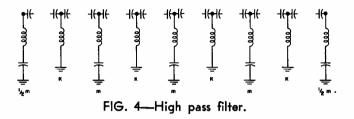

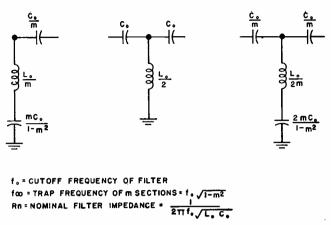

- 76....Low-Pass Filters for Wide-Band Harmonic Suppression

- 76....Transistors As Reactive Filter Elements

- 77....Rectifier Transient Protection Circuit

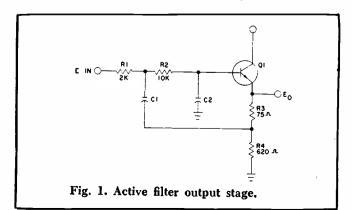

- 77....Output Stage With Active Filtering

- 78....Spike Suppressor for Power Converters

- 78....Surge-Current Limiter Gives Fast Turn-Off

- 78....Base-Emitter Protection in Monostable Multivibrators

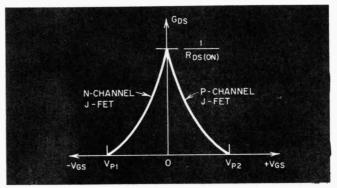

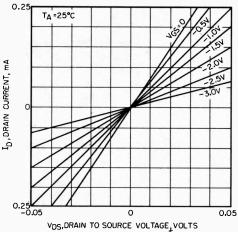

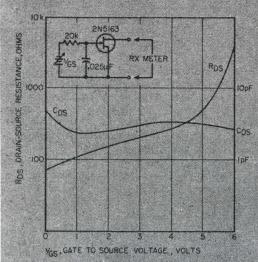

- 79....The FET as a Voltage-Controlled Resistor

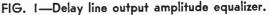

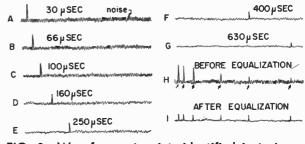

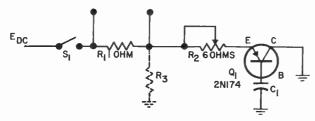

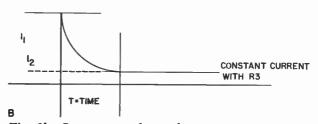

- 79....Delay Line Output Amplitude Equalizer

- 80.... Transient Load With Exponential Decay

- 80....Stable Q Multiplier

- 81....Active Bandpass Filter With Adjustable Center Frequency and Constant Bandwidth

- 81.... Optimum Zener Decoupling

- 82....Digital ICs Serve as Audio Filters

- 83....Simple Solid-State Noise Filter for Industrial Logic Systems

- 83....A Novel Active Filter

- 84.... High-Efficiency, Miniature Decoupler

Section Five—PULSE CIRCUITS

- 85....Fast Recovery Monostable Multivibrator

- 85....Fast Monostable Multivibrator

- 86....Current Switching Astable Multivibrator

- 87....Current Fall Time Control

- 88....Variable One-Shot for Counter Display Time

- 88....Monostable 50-Millisecond Multivibrator

- 88....High Square, Variable Frequency Multivibrator

- 89.... Magnetic Control of Pulse Width

- 90....Self-Starting Multivibrator

- 90....Noise-Free Pulser

- 91....Simple Intervalometer

- 91....Free-Running Transistor Multivibrator

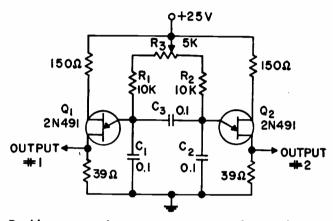

- 91....SCR Parallel Inverters in Correct Timing Sequence

- 92.... Ultra-Long Monostable Multivibrator

- 93....Square Wave Chopper

- 93....Redundant MSMV Retrigger Any Time

- 94....Tunnel Diode Trigger

- 95....Fast Turnoff Monostable Multivibrator

- 95....Positive Pulser

- 96....High-Duty Cycle Monostable Multi

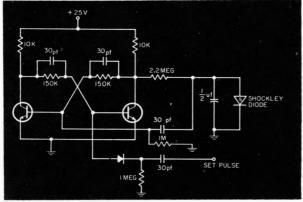

- 96....Electronic Chopper

- 96....A Pulse Width Modulator

- 97....Self-Resetting Pulse Stretcher

- 98....A One Microsecond Delay

- 98....Monostable Circuit With Negative Recovery Time

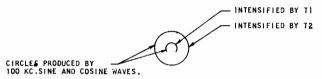

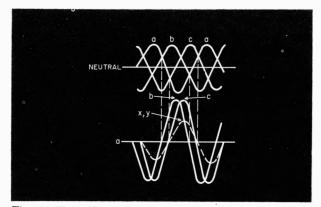

- 99....Double Pulsed Sine Wave Circuit

- 100....Wide-Range Constant Symmetry Multivibrator

- 101....Pulse Generator for High-Speed Computers

- 102....Double Pulser

- 103....Low-Impedance Multivibrator Output Circuit

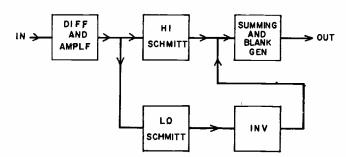

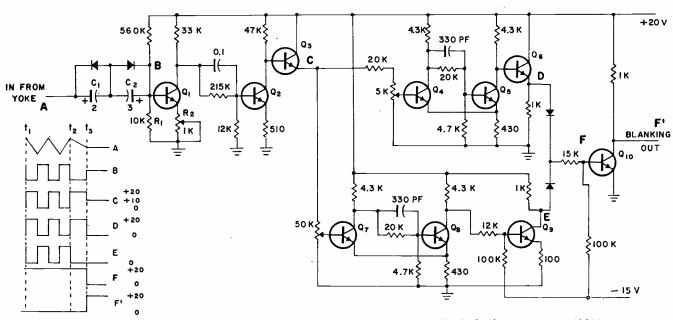

- 104....Blanking Pulse Generator With Linear Pulse Width Control

- 105.... Square Wave Generator With Variable On and Off Times

- 105.... Magnetic-Core Sequential Pulser

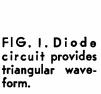

- 106....Transient-Protection Of Monostable Multivibrators

- 106....Stable-Fast Recovery Transistorized Multivibrator

- 107....Astable High Power Multivibrator

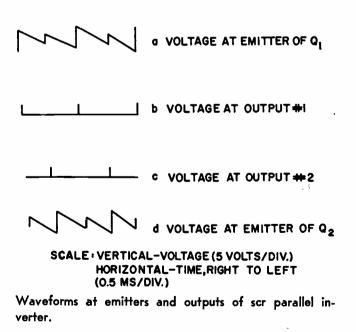

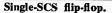

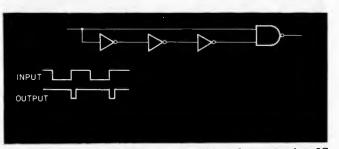

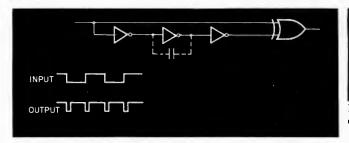

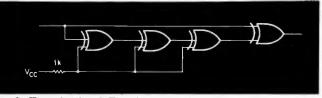

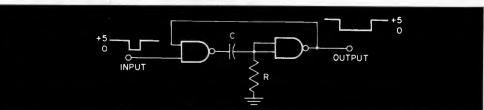

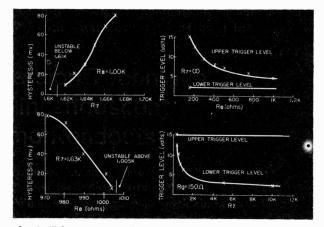

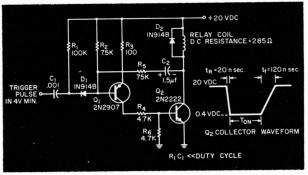

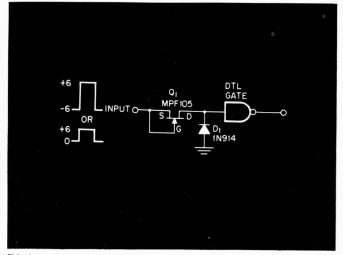

107....Pulse Generator Low-Frequency 108....Zero-Hysteresis Schmitt Trigger 108....Voltage-Controlled Ramp-Trigger Generator 108....Low-Cost Pulse-Length Controller 109....Scope-Trace Intensification Converter 109....Single-SCS Flip-Flop 109....Variable Time, Power One-Shot Multivibrator 110....Astable Multi Has Microsecond Fall 110.... Unijunction Adds PWM Mode to S-R Flip Flop 111....Trigger Circuit Gives Less Pdiss, More Vout 111....Combination Schmitt Trigger-Monostable Multivibrator 112....Delayed Pulse Generator 112....Frequency Divider With Independent Pulse-Width Control 113.... PW Modulator as Multiplier and Bang-Bang Amplifier 113....Narrow Pulses with DTL Integrated Modules 114....Coaxial Cable Driver Circuit 114....Wide Range Monostable Multivibrator 114....Fast-Recovery One-Shot Multi Gives 10:1 Width Control 115....Pulse Amplitude Modulator 115....High-Gain, Long-Pulse Monostable 116....Wide-Range Monostable, PRF Discriminator 116....Improved One-Shot Output Circuit 117....Eliminating False Triggering in Monostable Multis 117....Pulse-Width Discriminator 118....Pulse Integrator Gives Constant Slopes 119....Improved Monostable Multivibrator Allows Wide Range of Pulse-Width Control 120....Sensistor Stabilizes Pulse Width of Monostable Multivibrator 120....Tunnel Diode Speeds Word-Line Driver 121....Current Source Improves Immunity of One-Shot 121....Simplified Schmitt Yields Fast Rise Time 122....Resonant Clock-Line Driver for MOS ICs 123....High Speed Saturated-Mode One-Shot 124....Two-Pulse Monostable 125....Extra Transistor Provides Noise Immunity for Monostable Multivibrator 125....Zero (Quiescent) Power One-Shot 126....IC One-Shot Needs No External Resistors or Capacitors 126....An Inexpensive Frequency Doubler 127....Single NAND Package Improves One-Shot 127....Versatile One-Shot 128....Simple One-Shot has Complementary Outputs 128....Resettable One-Shot with High Noise Immunity 129....Ultralow-Duty-Cycle Pulser 129....Schmitt Trigger Uses Two Logic Gates 130....Optically Driven Pulse Stretcher 130....High-Speed, One-IC One-Shot 130....Wide-Range Variable Pulse-Width Monostable Section Six—COMPARISON CIRCUITS

- 131....Transistor Go-No Go Voltage Comparator

- 131....A Phase Discriminator

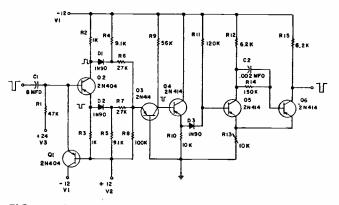

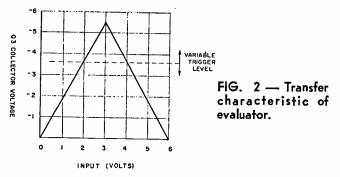

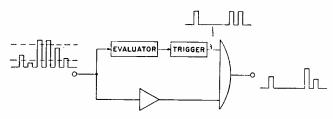

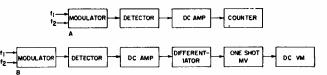

- 132....Pulse Amplitude Evaluator

- 133....Frequency Comparator Detects Coincidence Within 10<sup>-6</sup>

- 134....Phase-Sensitive Demodulator With Pulse Reference

- 135....Comparator Uses Bilateral Transistor

- 135....Differential Voltage Comparator

- 136.... Variable Schmitt, Amplitude Comparator

- 136....Frequency Comparator Uses ICs

- 137....IC Voltage Comparator With Adjustable Threshold and Hysteresis

- 138....Voltage Comparator With Visual Readout

- 139.... Op-Amp Comparator With Latching Function

- 139....Low-Power Multiple-Input Comparator for AC-DC Inputs

- 140....Low-Components-Count Digital Comparators

#### Section Seven—AMPLIFIER CIRCUITS

- 141.... "Power-Less" Pulse Amplifier

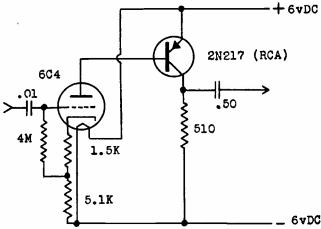

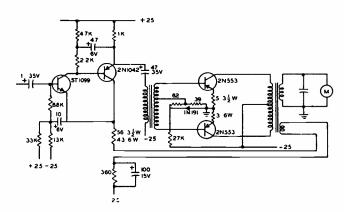

- 141.... Hybrid Tube-Transistor Amplifier

- 142....Driver Amplifier for 3½ and 6-Watt Servo Motors

- 142....Hybrid Amplifier

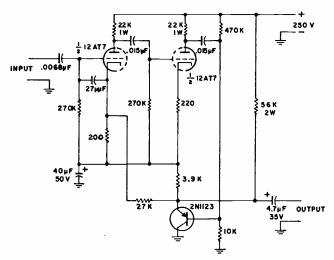

- 144....Constant Output AC Amplifier

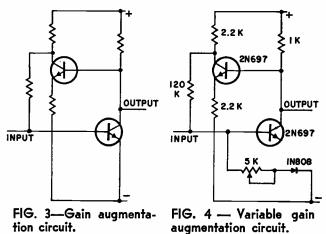

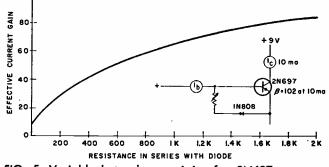

- 145....Additional Gain Circuit

- 145....Grouping Amplifier

- 146....High-Impedance Preamplifier

- 146.... DC Amplifier Has Infinite Input Impedance and 80 db Power Gain

- 147....Failure-Proof Amplifier

- 148....Adjustable Temperature Compensation

- 149....Simplified Operational Amplifier

- 150....Sensitive Relay Control Amplifier

- 151....Time Amplifier

- 152....High Input-Impedance, Unity-Gain FET Amplifier

- 152....DC Drift Voltages Reduced With Ungrounded Supply

- 153....Amplifier With DC Controlled Gain

- 154.... Opposed Collector Audio Amplifier

- 154....Minimum-Interaction Summing Amplifier

- 155....High-Level Wide-Band Video Amplifier

- 155....Logarithmic Amplifier for Radar Signals

- 155....Starved DC Amplifier Has Low Noise, High Z

- 156....Amplifier With Remote Gain Control

- 156.... One Transistor, 50-db Dynamic Range Compression Amplifier

- 157....Non-Inverting Pulse Amplifier Uses One Power Supply

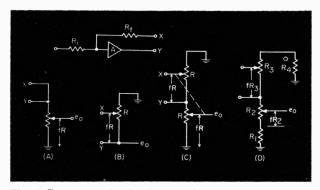

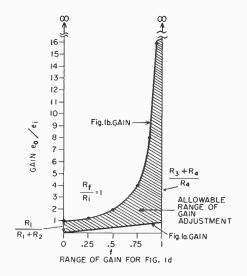

- 157.... Operational Amplifier Gain Control from Zero to Infinity

- 158....400-Volt Output Transistor Amplifier

- 158....Photocell Threshold Circuit

- 159....Low-Noise Preamplifier Uses FET

- 159....Current Sources Improve Amplifier Slew Rate

- 160....Non-Linear Function Amplifier

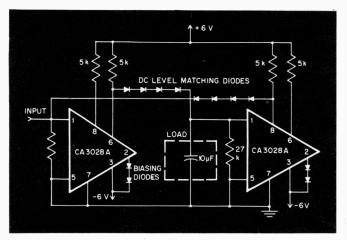

- 161.... Higher Speed, Gain, Output From IC Diff Amp

- 161....Current Boosters for IC Op Amps

- 162....Isolated Line Driver With Short Protection

- 162....Gain-Programmable Amplifier

#### Section Eight—OSCILLATOR CIRCUITS

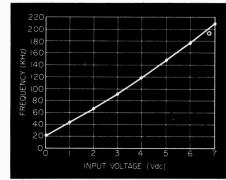

- 163....Voltage Controlled Oscillator

- 163....Wide Range Variable Multivibrator

- 164:...Stable Oscillator Circuit

- 164....Low-Frequency C-Coupled Oscillator

- 165....Even Duty Cycle Blocking Oscillator

- 165....A Synchronized Oscillator Circuit

- 166....A 0.01 Microwatt Multivibrator

- 167....Wide-Range, Voltage-Controlled Oscillator

- 167....Voltage-Controlled Variable-Frequency Oscillator

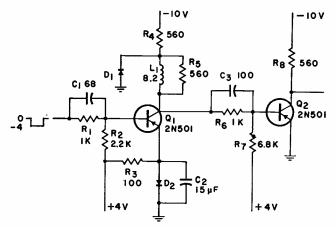

- 167....Inductor Raises Useful Sawtooth Frequency

- 168....Transistor Mixer Crystal Oscillators

- **169....RC Plate-Tuned Oscillator**

- 169....Pulsed Audio Oscillator

- 170.... Unusual Emitter Follower RC Oscillator

- 171....Quasi-Sinusoidal Relaxation Oscillator

- 171....Improved Multi With Continuously Variable Rep Rate

- 172....High Efficiency Relaxation Oscillator

- 172....Voltage-Controlled Oscillators

- 173.... Modified UJT Oscillator Has No Timing Error

- 173....Modified Unijunction Oscillator Reaches 500 kHz

- 174....Simplified One-Shot Multivibrator

- 175....Cascade UJT Oscillator Generates Linear Frequency Sweeps

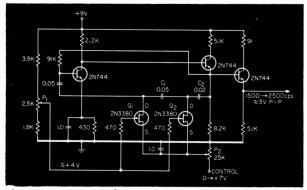

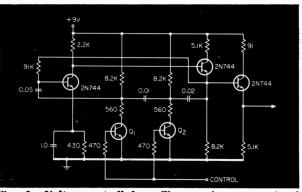

- 176....Linear VCO Generates Sawtooth and Square Waveforms

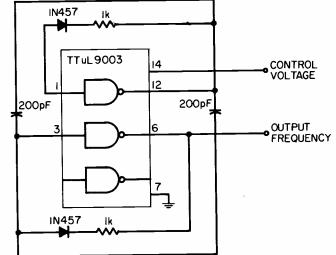

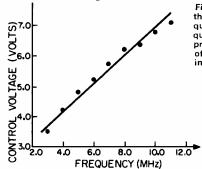

- 177....Wide Range VCO Uses IC

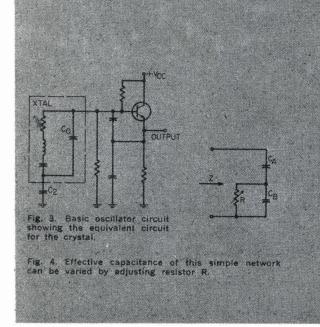

- 177....FET Controls Crystal Oscillator

- 179....FET and IC Make Syncable Oscillator

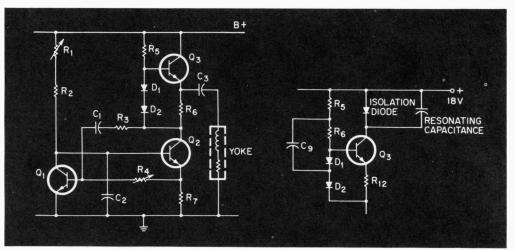

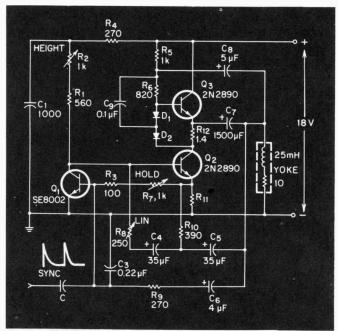

- 179....Higher-Efficiency Chokeless Vertical Sweep

- 180....Improved VCO Uses TTL IC

- 181....Gated Delay-Line Oscillator Eliminates Range Error

- 182....Improved One-Shot Multivibrator Using ICs Only

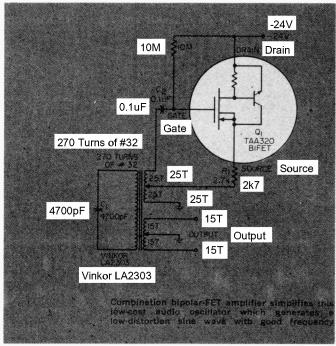

- 183....Low-Cost Audio Oscillator With Stable Amplitude

- 183....UJT Oscillator Reconstructs Clock Signals

- 184....Low-Frequency Sine-Wave Oscillator

- 184....A 5000:1 Frequency-Range Oscillator

- 185.... LF Oscillator With Direct Digital Control

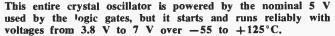

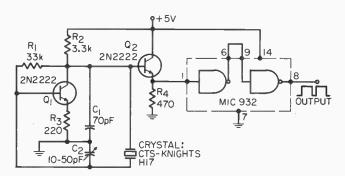

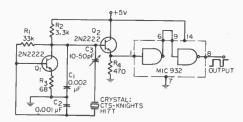

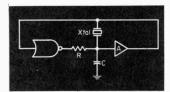

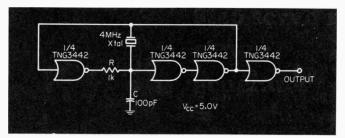

- 186....Crystal Oscillator Uses Logic Gates

#### Section Nine—INDICATOR & ALARM CIRCUITS

- 187....Missing Pulse Detector

- 187....Malfunction Indicator

- 188....High-Impedance Voltage Circuit

- 188....Varying-Frequency Warning Alarm

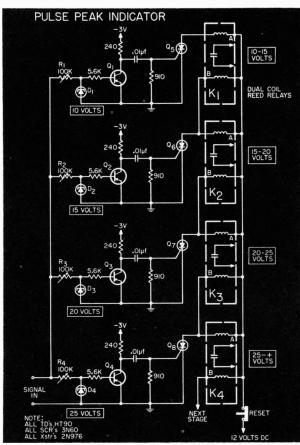

- 188....Pulse-Peak Indicator

- 189....Phase Indicator

- 189....Exciter Lamp Failure Indicator

- 190.... Tone Decoder, Pulse Discriminating

- 190....Differential-Voltage or Current Alarm Circuit

- 191....Relay Arc Failure Detector

- 191.... Target Bearing Indicator

- 192.... Overvoltage Indicator

- 192....Multiple Station Diode Detection System

- 193....Flying Spot Scanner Sweep Alarm

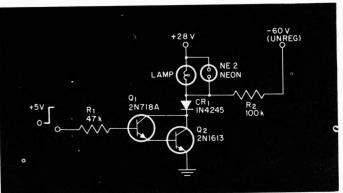

- 194....Neon Indicator for Surgistor Points

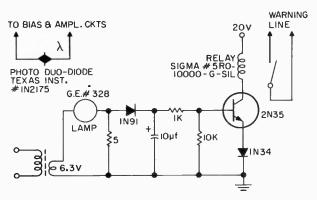

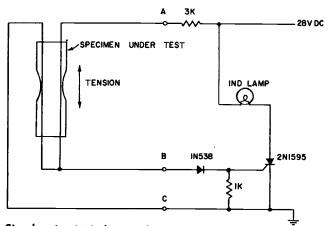

- 194....Photocell Lamp Burnout Warning Circuit

- 194....Short-Circuit Alarm

- 195....Pulse-Level Discriminator and Fault Indicator

- 195....Gated Filter and Sample-Hold Circuit

- 196....Combination Lamp Driver and Failure Indicator

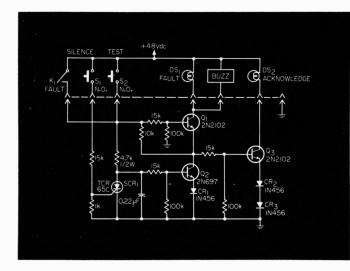

- 196....Fault Alarm Circuit

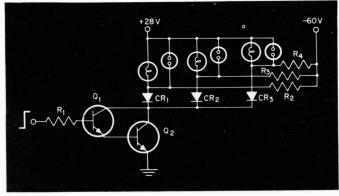

- 197....Low Voltage Transistors Drive Neon Indicators

- 197....Automatic Back-Up Lamp Circuit

- 198....Simple, Low-Cost Time Indicator

#### Section Ten—COUNTING & TIMING CIRCUITS

- 199....Transistorized Intervalometer

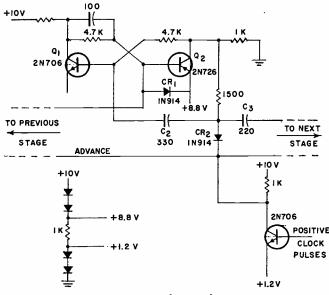

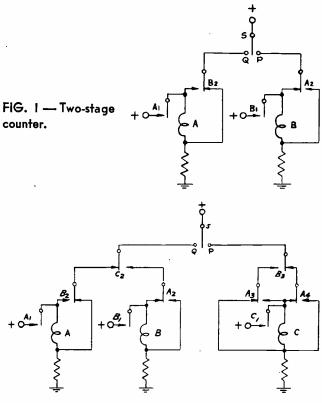

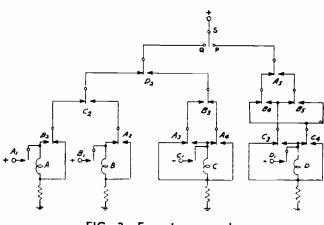

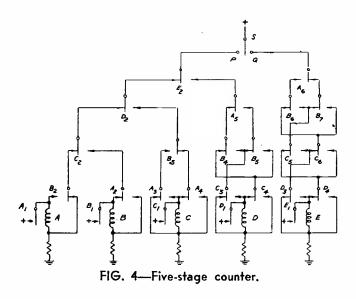

- 201....Counter Uses Complementary Transistors

- 201.... Transistor Time Delay Switch

- 202....Differentiating Clipper Circuit

- 202.... Inexpensive Pulse-Time Telemeter

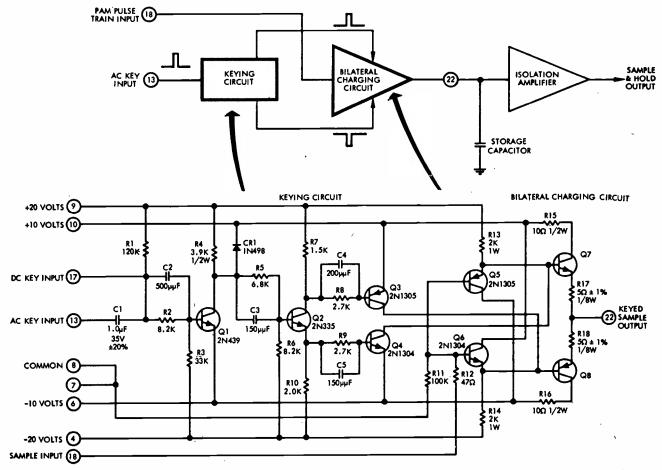

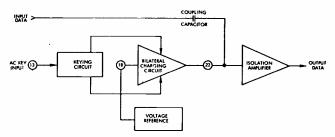

- 203....Sample and Hold Circuit With Bilateral Charging

- 204....Low Power Binistor Action Ring Counter

- 205.... Stable, Sensitive Pulse Height Discriminator

- 206....Digital Memory Display

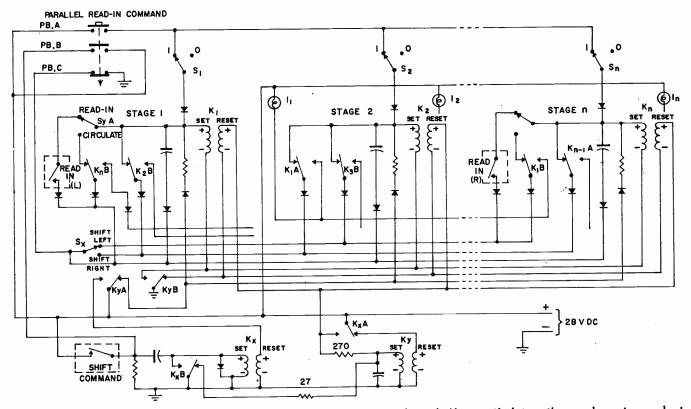

- 207.... Universal N-Bit Shift Register Uses N-Plus-Two-Pole Relays

- 208....Stepping-Switch Decimal Counter

- 209.... Time Delay Relay

- 209....Sample and Hold Circuit With Long Memory

- 210....Wide Range Timing Circuit

- 210....Relay Binary Counter Module

- 211....Simple Current Integrator

- 212....Zero-Order Data Hold

- 212.... Precision Solid-State Delay Circuit

- 213....Interval Timer

- 213....Accurate Time Delays Up to Four Minutes

- 214....Relay Chain Counts Consecutive Pulses

- 214....Relay Counters

- 215....Relay Flip Flop

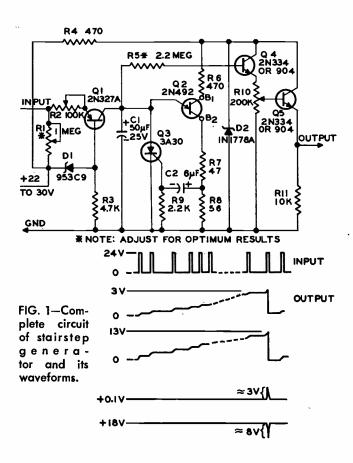

- 216....Low-Frequency Stairstep Generator and Timing Circuit

- 217....Simple FET Timer

- 217....Recycling Timing With Variable Duty-Cycle

- 217....Reversible Linear Counter

- 218....Inexpensive UJT-SCR Intervalometer

- 218....Stable Clock Oscillators Are DTL-TTL Compatible

- 219....Low-Power Timer Drives Stepping Relay

- 219....Versatile Timer

- 220....Wide-Range Programmable Clock for Low-Voltage Logic

- 221....Single Capacitor Converts TTL Gates Into One-Shot

- 221....Simple Analog Delay

- 222....Voltage- or Pot-Variable 400-Hz Delay

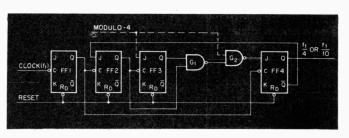

- 223.... Module -4 or -10 Counter

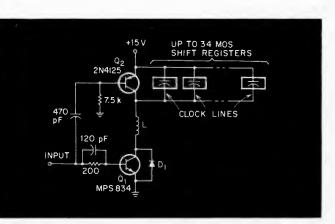

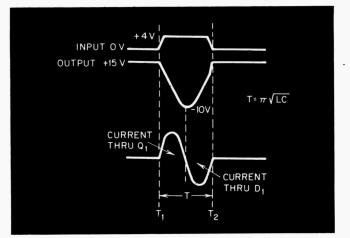

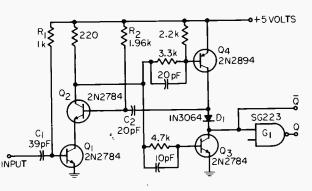

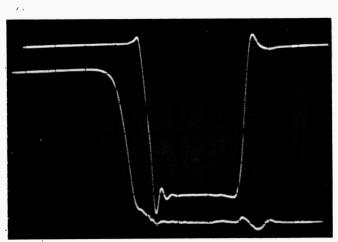

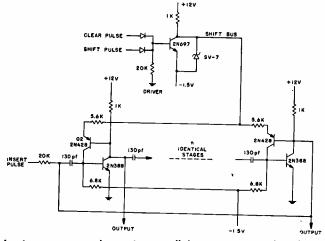

- 224....Combined Shift-Register Clock Driver and Power Supply

- 224....Long-Delay Timer

#### Section Eleven—TEST & MEASUREMENT CIRCUITS

- 225....Accurate Engine Tachometer

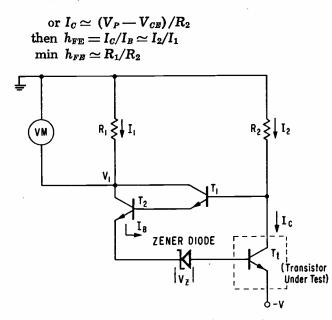

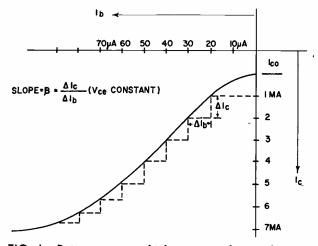

- 225....Direct-Reading DC Beta Tester

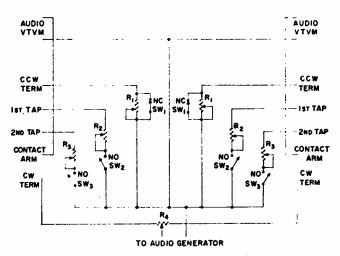

- 226....Checking Tracking of Stereo Controls

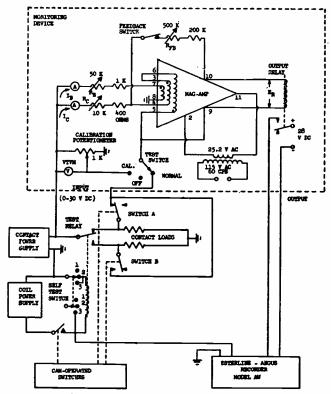

- 227.... Relay Life Tests Monitored With Magnetic Amplifiers

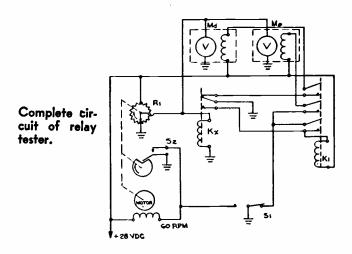

- 228....Relay Tester

- 228....Relay Chatter Detector

- 229....Fast Acting Sub-Audio Frequency Meter

- 230....Beta Tester

- 231....Standardized AC Voltage Reference Source

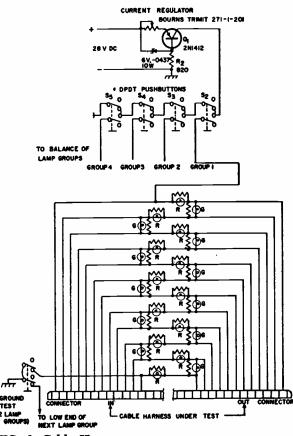

- 231....Cable Harness Tester

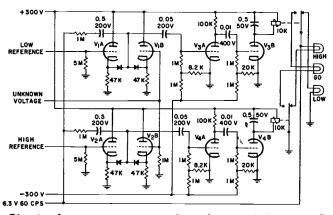

- 232....A High-Stability Differential Voltmeter

- 233....Anti-Coincident Detector

- 233.... Transistorized Tachometer

- 234....Relay Life Failure Indicator

- 234....A Variable Beta Transistor

- 235....A Go No-Go Vacuum Tube Voltmeter

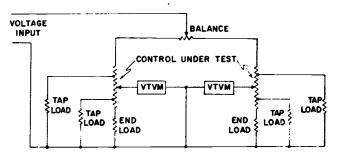

- 237....Feedback Method of Checking Tracking of Dual Potentiometers

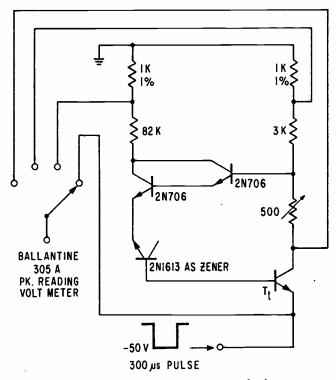

- 238....Low Current Transistor Beta Checker

- 239....Component Vibration Test Monitor

- 239....Electronic Squib Simulator

- 240....Engine Tachometer

- 240....Simple Transistor Tester

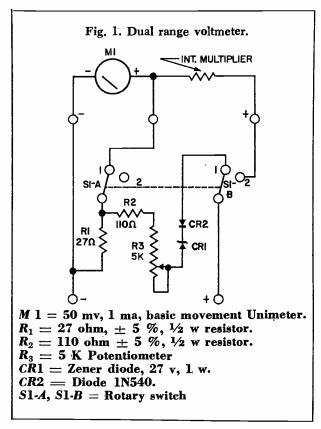

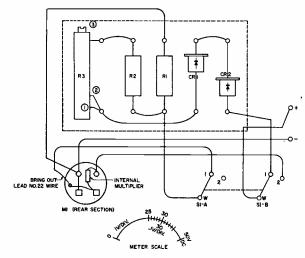

- 241....Dual Range DC Voltmeter

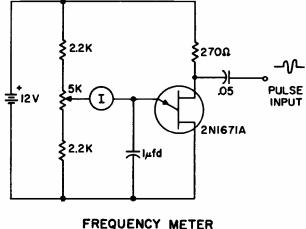

- 241....Frequency Meter-Tachometer Amplifier

- 242....Simple Scope Setup Measures Differential Microvolts

- 242....Simple Test Anticipates Transistor Failures In Complex Equipment

- 243....Pulse Amplifier For Beam Intensity Modulation

- 243....Schmitt Triggers on Nanoamp Inputs

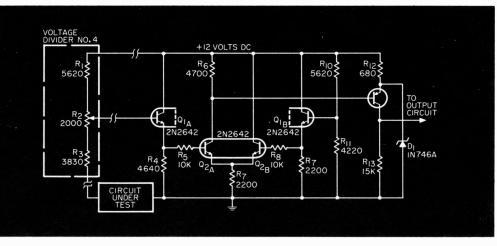

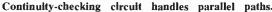

- 244....Parallel-Path Continuity-Checking Circuit

- 244....Automatic Scaling Circuit Uses ICs

- 245....Plug-in Squaring-Unit For Signal Generator

- 245....Differentiating Amplifier Intensifies Scope Trace

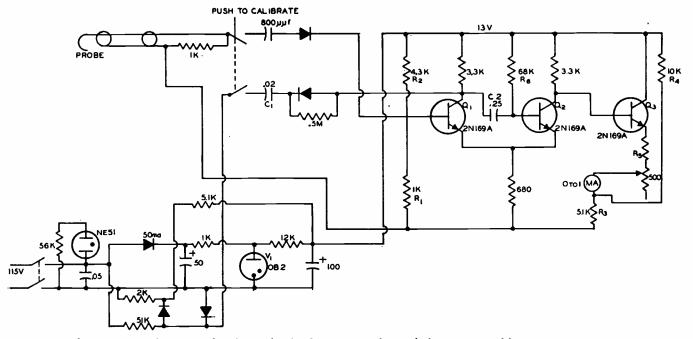

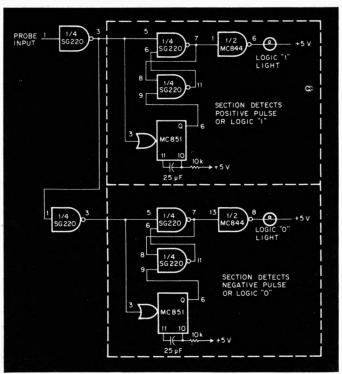

- 246....Pulse-Catching Probe

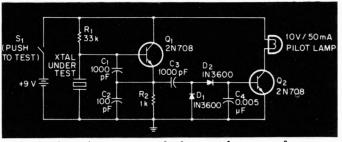

- 246....Self-Contained Crystal Tester

- 247....Direct Reading Period Meter

#### Section Twelve—GENERATOR & SIMULATOR CIRCUITS

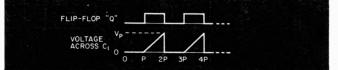

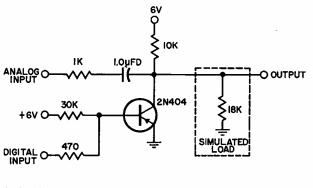

- 249....Inexpensive Load Simulator

- 249.... Ultra Linear Ramp Generator

- 250....Constant Amplitude Sine Wave Source

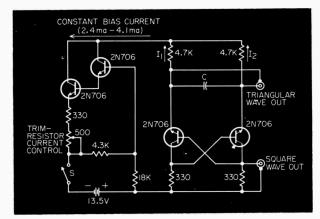

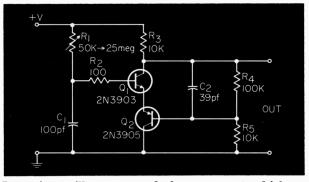

- 251....Simple Triangular Waveform Generator

- 252....Transistorized All-Waveform Generator

- 252....Triggered Sawtooth Generator

- 253....Temperature-Compensated Constant Current Generator

- 253....Linear Sweep Generator

- 254....Radar Target Acceleration Simulator

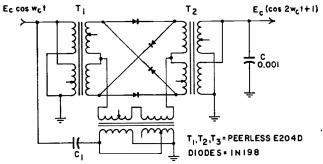

- 256.... Efficient Even Harmonic Generator

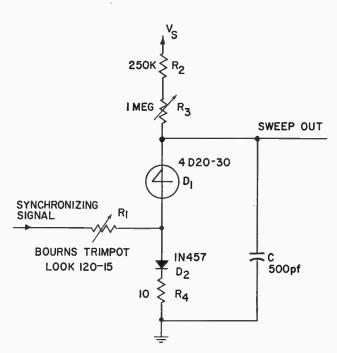

- 256....4-Layer Diode Sweep (Synchronous)

- 257....Fast-Rise, Long-Width Pulse Generator

- 257.... Variable Pulse Generator

- 258....Rectangular Waveform Generator

- 259.... Gated-Beam Tube Square-Wave Generator

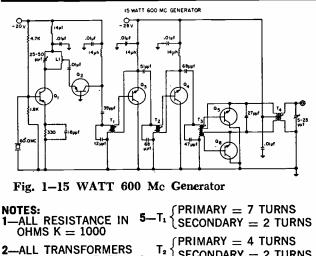

- 260....Transistorized 15 Watt 60 Megacycle Generator

- 260....High-Duty-Cycle Pulse-Width Generator

- 261....One-Stage Semiconductor Noise Generator

- 261....Improving Linearity in Transistorized Sweeps

- 261.... Unijunction Triangular Wave Generator

- 262....Synthesis of Ignition Noise in the VHF Band

- 263....Portable Pulse Generator

- 263.... Transistorized Linear Staircase Generator

- 264....Single Shot Square Wave Pulse Generator

- 264....A One Transistor Sawtooth Generator

- 265....Positive or Negative Slope Generator

- 265....Wide-Range Voltage-Controlled Pulse Generator

- 266....MOS FETs Give Long Time-Constant Ramps

- 266....Low-Cost UJT Raster Generator

- 267....Simple Variable Width, PRR Pulse Generator

- 267.... Variable-Voltage Current Sink

- 268....Improved Circuit For Constant-Current Source

- 268....Trigger Generator Sweeps From Audio Frequency To DC

- 269....Seesaw Circuit Gives Sine-Wave Power

- 269.... Crystal Controls Rep Rate of Simple IC Pulse Generator

- 270.... Unijunction Transistor Simplifies Trigger Sweep Generator

- 271.... IC One Shot Generates Short-Duration Pulses and Eliminates Switch Noise

- 272.... Trigger-Diode Simplifies Efficient Generation of Sawtooths and Pulses

- 273....Sequential Bipolar Multivibrator

- 274....Single IC Forms Wide-Range Triangle Square-Wave Generator

- 275....Keyed Multivibrator Produces Symmetrical AC Output

- 275....FET Converts a Triangle Generator To a Sawtooth Generator

- 276....A Digital Boxcar Generator

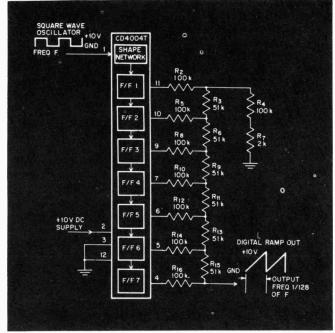

- 277....Digital Ramp Generator

- 277....Long Duration Variable Linearity Ramp Generator

- 278....Step-Servo Motor Slew Generator

- 278....Wide Range Square-Wave Generator Uses One IC

- 279....Simple, Wideband AM Noise Generator

- 279....Low-Cost 60-Hz Sync

#### Section Thirteen—CONVERTER & INVERTER CIRCUITS

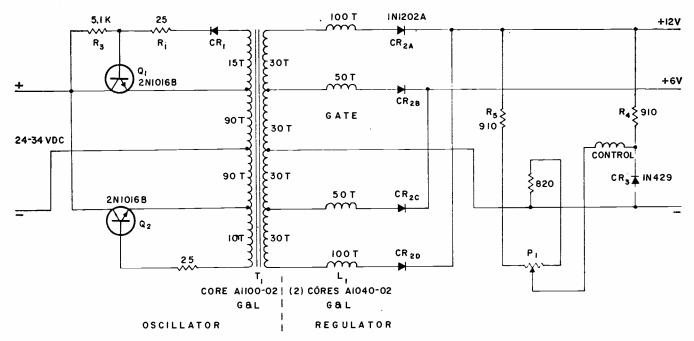

- 281.... Mag-Amp Regulates Static Converter

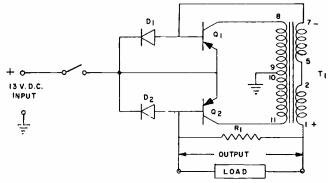

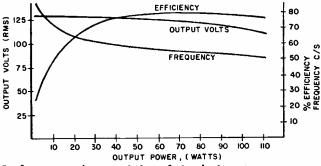

- 282....60-Cycle Inverter

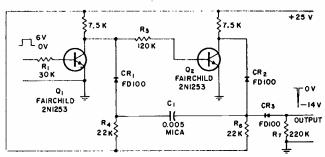

- 283....Positive Square Wave To Negative Spike Converter

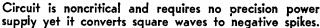

- 283....DC To Frequency Converter

- 284....Converts Sine Waves To Sawtooth or Square Waves

- 284....High Power, Variable Frequency Inverter

- 285....DC-DC Converter Diode-Starting Network

- 285.... Unbalanced To Balanced Lever-Shifter

- 286....Linear Period-To-Voltage Converter With Low Ripple

- 286....Starting Network for Transistor Inverters

- 287.... New Line-Operated Inverter Offers Fast Switching and High Efficiency

- 288....Simple Circuit Converts Pulse Duty Cycle Into Analog

- 289....Passive DC Converter for Geiger Counter

- 289....Signal-Powered Sine-To-Square Wave Converter

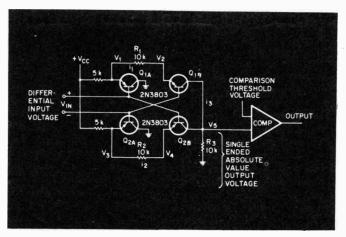

- 290....Differential to Absolute Value Converter

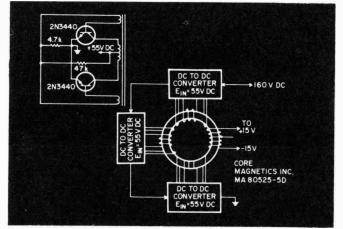

- 291....High Voltage DC-To-DC Converter

#### Section Fourteen—POWER SUPPLY CIRCUITS

- 293.... Full-Wave Control With One Trigger And One Control Rectifier

- 294....Regulated Low Voltage Power Supply

- 294....Zener Diode Bias Clamp

- 295....Reference Voltage Polarity Reversing Circuits

- 295....High-Efficiency Power Supply Regulation

- 296....Variable High Current Remote Power Supply

- 297....Automatic Chassis Ground Circuit

297....VHF Balanced Parametric Doubler

298....400-Volt SCR Constant-Current Source

298....Low-Loss Biasing Circuit

299....Constant-Voltage Current Sink

299....AC Power Interlock

299....Combined Battery Converter-Regulator Power Source

300....Backward-Diode Power-Supply Reference Elements

301....Second Breakdown Gives Fast Pulses

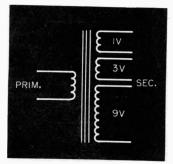

301....Universal Transformers

302.... Precision Full-Wave Rectifier Uses Only One Op Amp

#### Section Fifteen—DETECTION & SENSING CIRCUITS

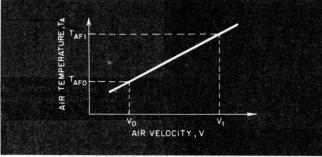

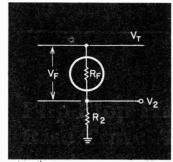

303....In-Phase, Out-Of-Phase Sensor 304....High-Speed Threshold Device 305....Large Slope Frequency Discriminator for Low Frequencies 306.... Photo Diode Pickoff Gives Accurate Angular Reference 306....Video Switch For Radar 307....Sampling Circuit 307....Pulse Coincidence Detector 308....Pulse Absence Detector 308....Pulse and DC Monitor Circuit 309....Absolute-Value Phase Comparator 310....Pulse Detection Circuit 311....Peak Follower 311....Transient Spike Pulse Detector 312....Hi-Lo Voltage Cut-Off Circuit 312....Missing-Pulse Detector for Narrow Pulses 313....Square-Wave Symmetry Detector 313....Current Amplitude Detector 313....Boxcar Envelope Detector 314....Automatic Search and Control Circuit for Servo Loop 314....PRF Discriminator 315....Tunnel-Diode Pulse-Height Discriminator 315....Accurate DC-Level Detector 315.... Phase-Locked Frequency Discriminator 316....Sine-Wave Zero Crossing-Detector 317....Product Detector Uses FET Tetrode 317....Pulse-Train Detector and Counter 318....Adjustable Level-Detector 318....Time-Delayed Schmitt Sensor 318....Noise-Rejecting SCR Trigger Circuit 319....Buffered Detector 319....Boxcar Circuit Uses FETs 320....Threshold Detector Uses IC 320....Sample-and-Hold Circuit Is Fast Yet Accurate 321....An Improved FET Sample-and-Hold Circuit 322.... Thermistor Circuit Senses Air Temperature and Velocity 323....Fail-Safe Temperature Sensor 324....Pulse-Width Discriminator 324....Change-Of-Slope Detector 325.... Peak Detector For Very Narrow Pulse 326.... Tunnel Diode Minimum Pulse-Width Detector 326.... Optical Tape-Marker Detector 326....High-Speed Synchronous Detector

#### Section Sixteen—DISPLAY & READOUT CIRCUITS

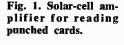

- 329.... Photo Reader for Perforated Tape

- 330....Inversion Technique for Incandescent Lamp Readouts

- 330....Low-Voltage Transistors Drive Neon Readout

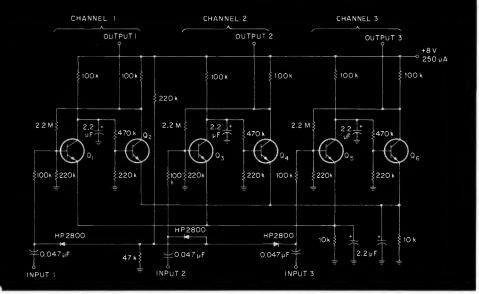

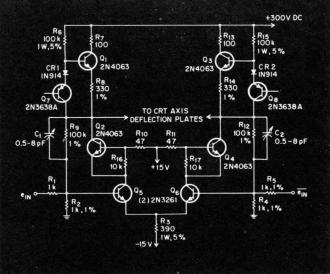

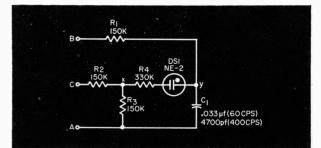

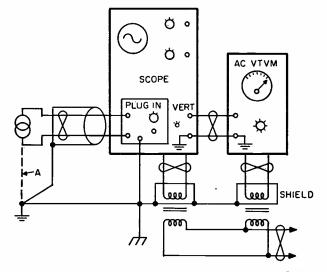

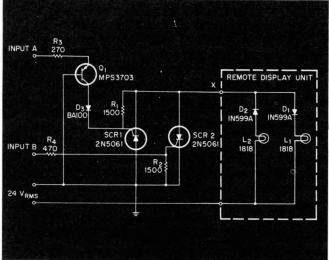

- 331.... Multitrace Display Device

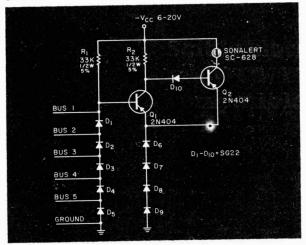

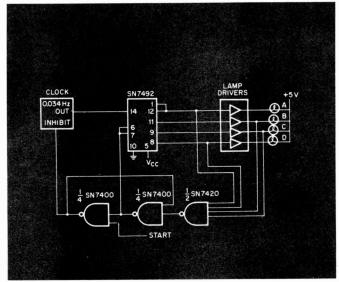

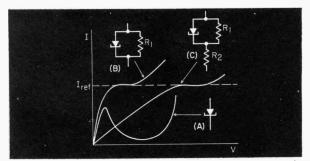

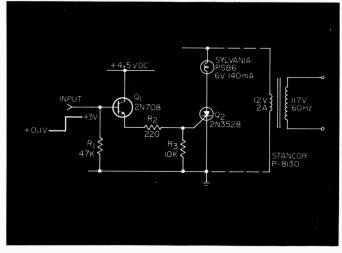

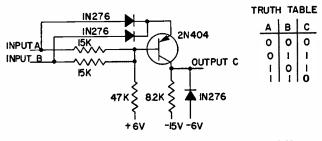

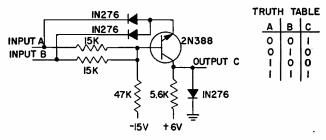

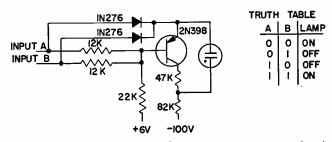

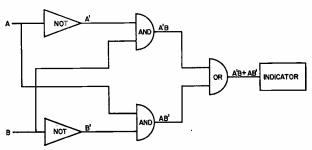

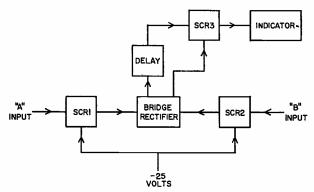

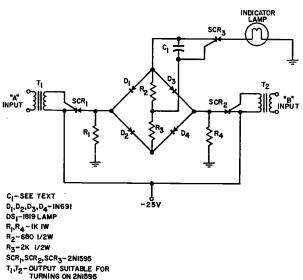

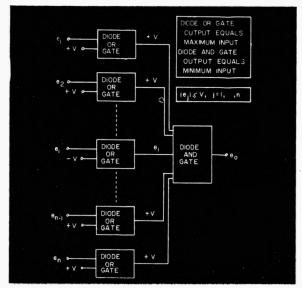

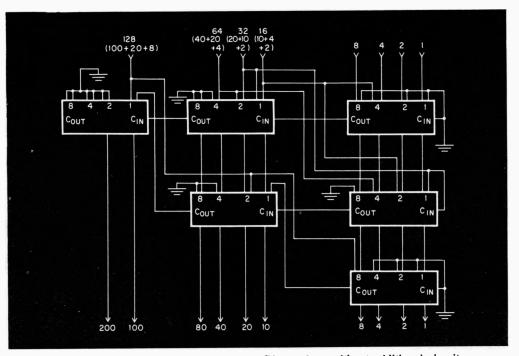

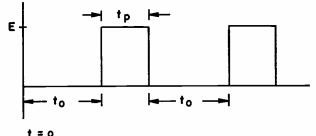

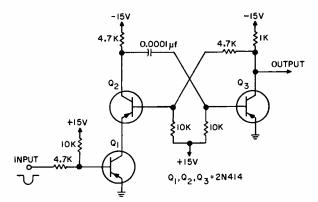

- 331....Transistor Matrix for BCD-to-Decimal Indicator

- 332.... Multi-Aperture Solar Cell Amplifier

- 333....Readout Circuit for Digital ICs

- 333.... Three-State Indicator

- 333....Lamp Driver Minimizes Lines To Remote Display Unit

- 334....Electronic Dipstick

#### Section Seventeen—GATING & LOGIC CIRCUITS

- 335....Gating With Varicaps

- 336.... Power Control by Digital Pulses

- 337.... Exclusive OR Uses One Transistor

- 337....Non-Stalling Flip-Flop for Capacitive Load

- 338....Binary Flip-Flop Turns On

- 338.... Phase Locked, Gated Oscillator With Amplitude Regulation

- 339....XY Code Converter

- 339....Anti-Coincidence Detector

- 340....Positive Transmission Gate

- 341....Logic-Level Converter

- 341....Added Transistor Reduces One-Shot Recovery Time

- 341....Temperature-Compensated One-Shot

- 342....Analog-Voltage Selection Switch

- 342....High Duty-Cycle One-Shot

- 343....Crystal Controlled Multivibrator

- 344.... Variable-Hysteresis Schmitt Trigger

- 344....Power One-Shot

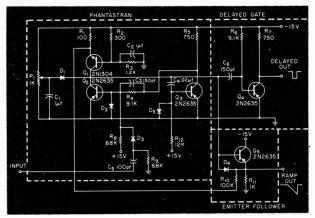

- 344.... Phanastran Delayed Gate

- 345....Flip Flop Operated by Input Signal NOR

- 345....Sample-Hold Circuit

- 346....Flip Flop Has Improved Rise Time and Stability

- 347.... Emitter-Coupled Astable with Saturated Output

- 347....One-Shot Has Improved Temperature Stability

- 348....Long-Duration One-Shot Uses Integrated Circuit

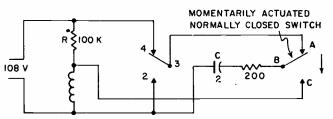

- 348....Low-Cost Manual Pulser

- 348....High-Speed Pulse Transmission Gate

- 349....TTL-DTL Interface to FET Analog Switch

- 350....IC NOR Gate Detects Zero-Axis Crossing

- 350....IC Functions as Sampling Amplifier or Tone-Burst Gate

- 351....Fast Logic Circuits With High Noise-Immunity

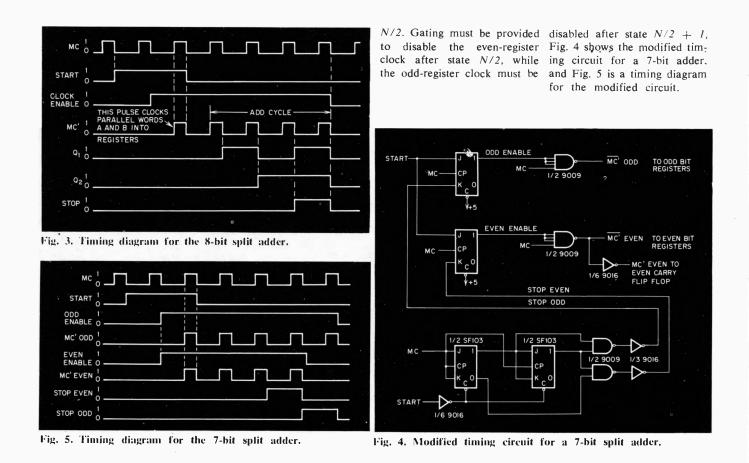

- 352....Split Serial Adder Is Fast Yet Simple

- 353....A Broadband Low-Noise Gate Using Hot-Carrier Diodes

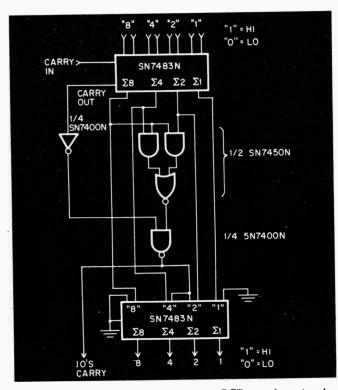

- 354....Fast Binary-to-BCD

- 355....Inexpensive Video Distribution Amplifier Converts Logic Signals For TV Displays

- 355....Simple Circuit For Division By 8, 9, 10

- 356.... Three-State Logic Circuit

- 357.... Universal Digital Interface

- 357....Fast BCD-to-Binary Converter

#### Section Eighteen—RELAY & SWITCHING CIRCUITS

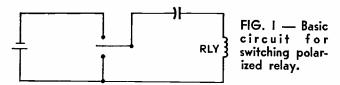

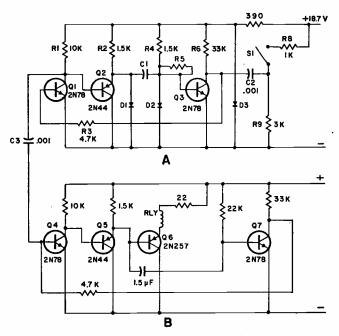

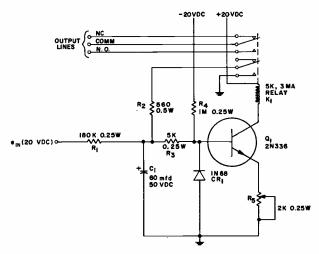

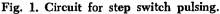

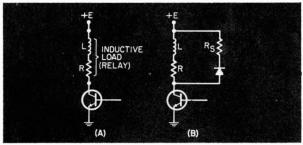

359.... Precision-Timed Short-Interval Relay Switch 360....SCR Switch Eliminates Amplifier for Photoelectric Readers 361.... Step Switch Pulser 361....Relay Circuit Compares Successive Binary Numbers 362....Frequency Selective Transistor Switch 363....Solid State Latching Relay 364.... Magnetic Latching Relay Flip-Flop 365....Simple Servo Follow-Up System 366.... Integrated Pulses Control DC Output 367....Starter Circuit for Flip-Flop 367....High-Impedance Diode Chopper System 368.... Variable-Speed Stepping Switch Control 369....Solid State Variable Time Delay Relay 370....Relay Control Circuit 370.... Phototransistor Operated Relay 371.... Voltage Controlled High Voltage Switch 372....Solid-State DPDT Relay 372....Relay Lock-Release Circuit 373....Relay or Switch Driven Pulse Generator 373....AC Operation of a DC Relay 373.... Stepping Switch Synchronizer 374....Low Voltage, Fast Current Rise Inductive Load Driver 374.... One-Step Function on Switch Closure 375....UJT-Relay Circuit Gives Delayed Release 375.... Transistor Driven AC Relay 376....Simple, Drift-Free Voltage Comparator 376....High-Power One-Shot Multi 377....Latching-Relay Driver Requires No Standby Power 377....Rate Circuit 378.... High Power AC Static Switch 378....Forced-Switching Emitter Follower 379....Fast Recycling Time-Delay Relay 379....Single-SCS Flip-Flop 379.... High-Current Switch Has High On-Off Z Ratio 380....Normal and Calibrate Mode Switching Circuit 380....Simplified 120 VAC Latching Circuit 381....Versatile Tunnel-Diode Discriminator 381....Audio On-Off, Phase-Reversing Switch 382....Minimizing Inductive Kick and Fall Times 382....DC to DC One-Shot Starting Circuit 383....Integrator Clearing Circuit 383.... Motor Transient Anticipator 383....Light-Activated Latching Relay 384....Low-Cost Bistable Relay Circuits 384....Solid-State Relay 385.... Added Transistors Reduce Capacitor Size for Relay Pull-in Delay 386.... Improved Tunnel-Diode Threshold Circuit Has Adjustable Hysteresis 387....An Improved Rotary-Switch Interlocking Circuit 387..., Remote-Controlled Solid-State Switch 388....Slowed Solenoid Driver Circuit Eliminates Noise Spikes

388....Simple Zero-Crossing Solid-State Switch

#### Section Nineteen—MISCELLANEOUS CIRCUITS

- 389....Impedance Matcher for Magnetic Amplifiers

- 390.... Point-Contact Transistor Multiplier

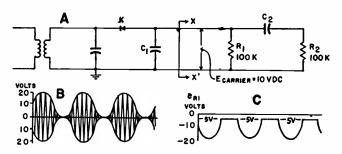

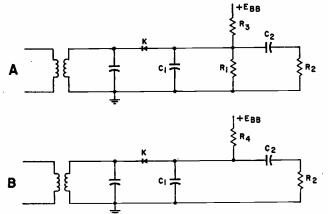

- 390....Eliminating Peak Clipping from Diode A-M Detectors

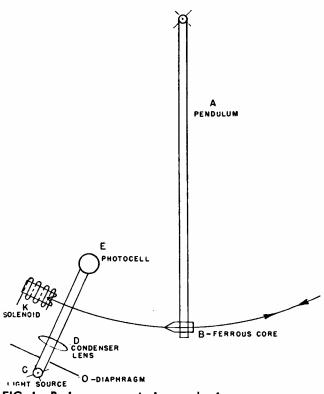

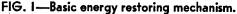

- 391....Relay-Operated Energy Restoring Mechanism

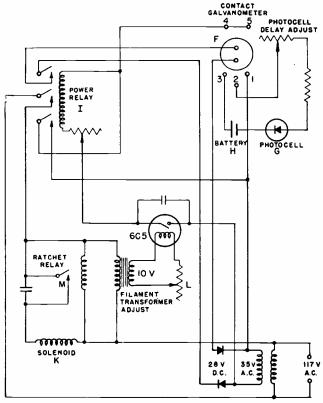

- 392....Pushbutton Decade Box

- 392....Passive Frequency Doubler

- 393.... Phast Shift Network with Third Harmonic Suppression

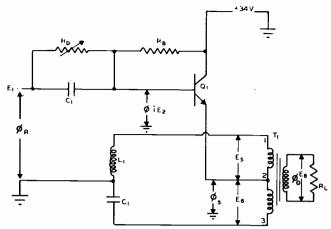

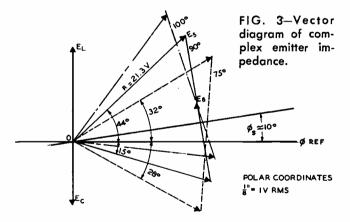

- 394.... Emitter Follower Transmission Matching

- 395.... Averaging Circuit Has Equal Charge and Discharge Time Constants

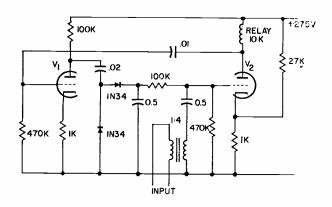

- 396.... Combination DC Amplifier, Pulse Operated Relay and Pulse Stretcher

- 396....Linear Limiter

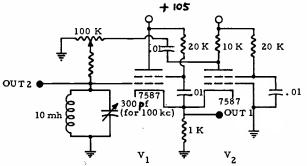

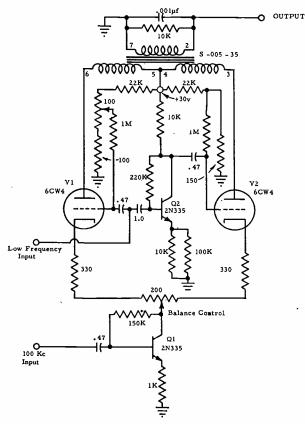

- 397....Hybrid Balaced Modulator for 100 Kc

- 397....DC Input Trigger Circuit

- 397....Dynamic Range Compressor

- 398....Plate-Cathode Follower Wien-Bridge Oscillator

- 398....A Chatter Jammer Circuit

- 398....Complementary Emitter Follower Offers High Isolation

- 399....FM Limiter

- 399....Low Frequency Switching Circuit

- 400....Simple Wailing Siren Circuit

- 401.... Modified Emitter Follower Has No Offset

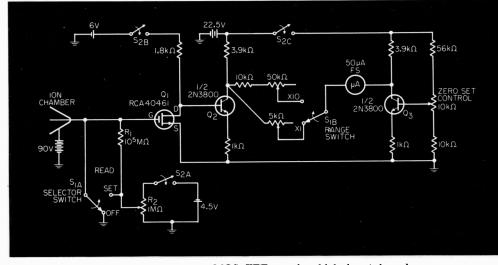

- 401....Radiation Meter Uses MOS FET

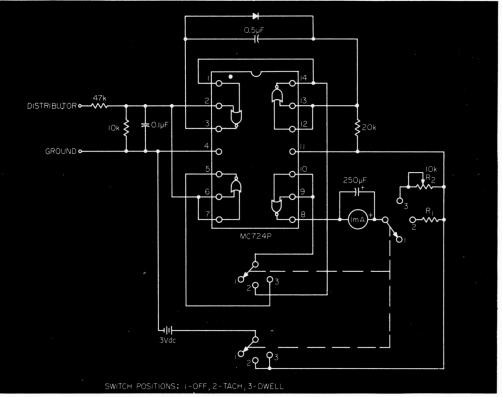

- 402....Combined Tachometer and Dwell Meter

- 402....SCRs Simplify Monostable Coil-Driver

- 403....Double-Balanced Diode Mixer

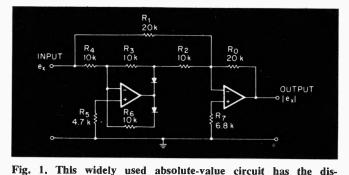

- 404....Improved Absolute-Value Circuit

- 405.... Phase Indicator for AC Tachometer

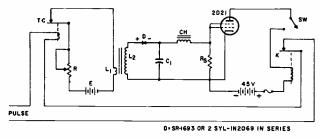

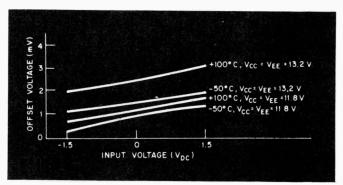

- 405....Linear Modulator Has Excellent Temperature Stability

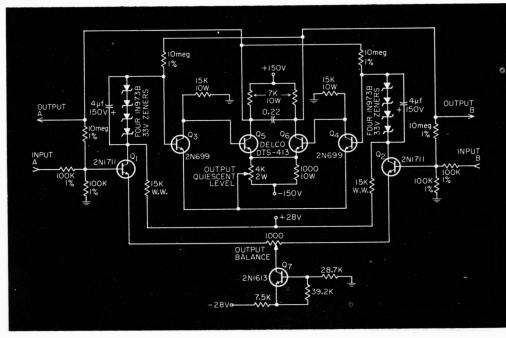

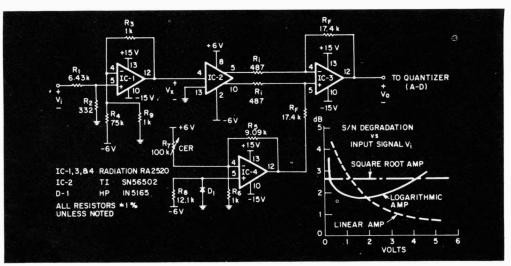

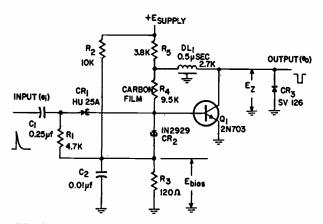

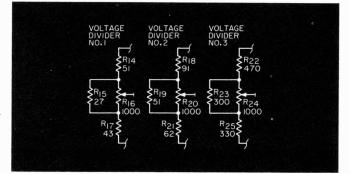

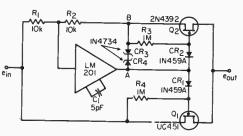

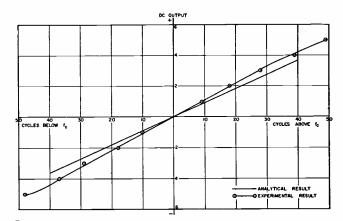

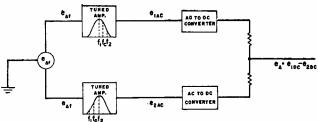

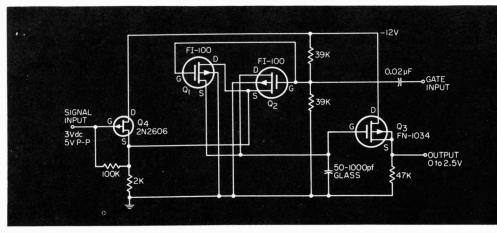

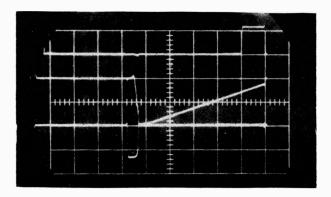

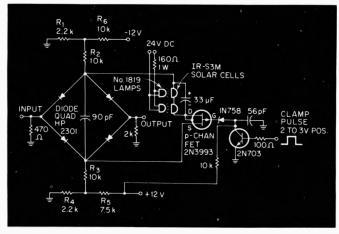

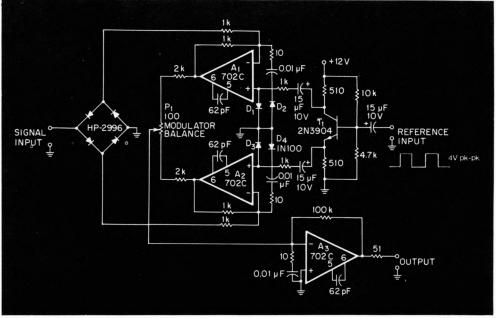

- 406....Pulse-Height Modulator Multiplies Voltage By Frequency

- 406....Delayed-Action Data Receiver

- 407....FETs Program Op-Amp Gain

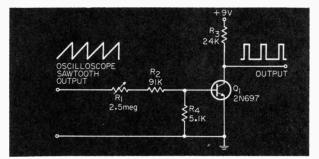

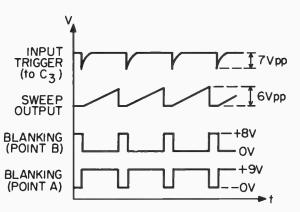

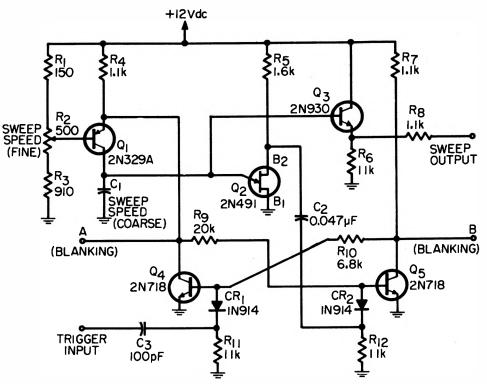

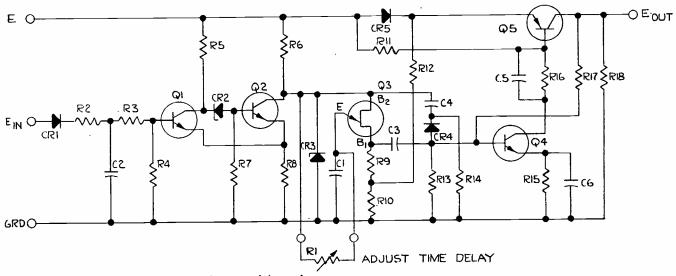

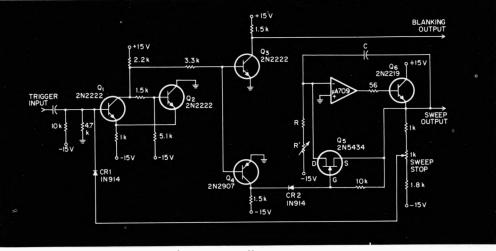

- 408....Triggered Sweep Features Low DC Offset

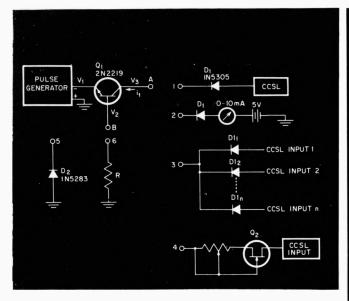

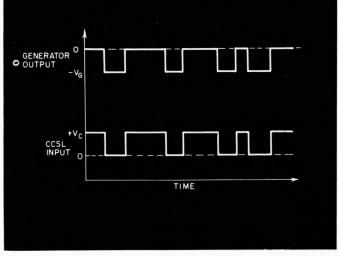

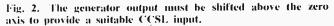

- 408....Pulse Generator-to-CCSL Interface

- 409....Fixed Bias Extends Zener Range

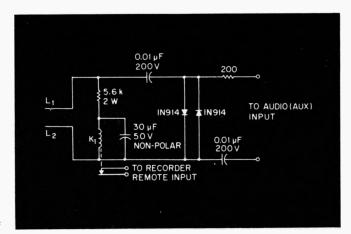

- 410....Automatic Telephone Recorder

- 410....Constant-Amplitude Phase Shift

- 411.... Adjustable, Low-Impedance Zener

- 411....Fast-Recovery Integrator With Adjustable Threshold

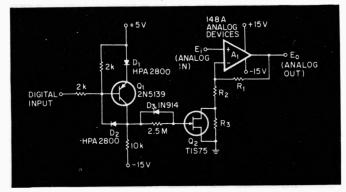

- 412....Bipolar Analog-Digital Interface For Servos

- 412....Transformerless Ring Modulator

- 4r3....Simple EIA Phone Level DTL Interface

- 413....Simple Gyrator For L From C

- 414....An Error-Stabilizer Analog Divider

- 414....60-Hz Frequency Discriminator

- 415.... Steering Diodes Insure SCR Commutation

- 415.... The Ideal Voltage Follower

# Section 1 CONTROL CIRCUITS

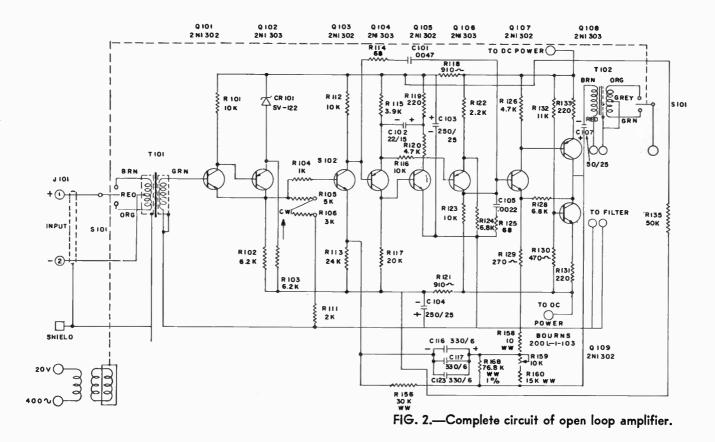

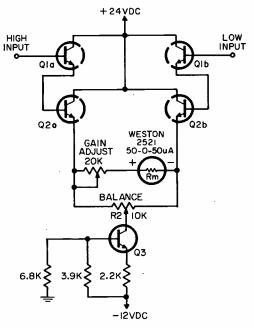

### A Reliable Open Loop Amplifier

**B**Y REPLACING the conventional closed loop with a semi-open loop configuration, the reliability of this differential dc amplifier has been greatly increased. In a semi-open loop approach, the active elements of the circuit are controlled by individual closed loops, permitting the gain characteristics to be determined by passive elements. Further improvement in reliability has been accomplished by reducing the number of components normally required for circuitry to provide the operating characteristics of this type of instrument.

The semi-open loop approach provides important features not possible with the closed loop method: isolation of the input from the output and a higher degree of filtering. The isolation of the input from the output offers several advantages including constant impedance level independent of the slewing rate of the amplifier and the absence of a unidirectional input current. Multipole filters with limiting slopes greater than 12 db per octave can be inserted internal to the amplifier and are completely isolated from the signal source and load effects.

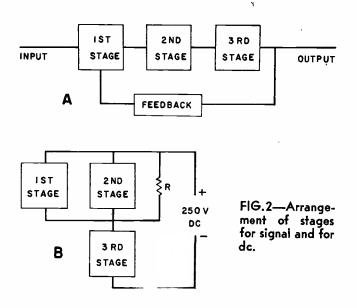

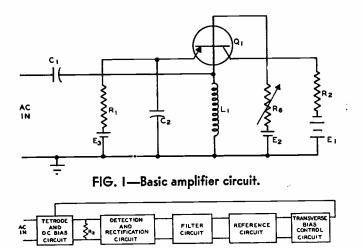

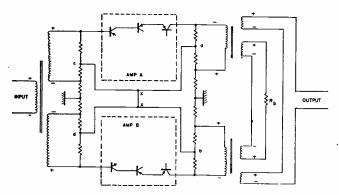

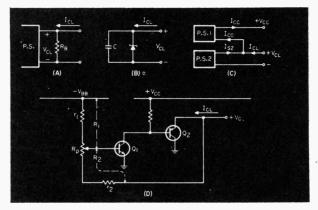

The amplifier circuitry involved in the semi-open loop approach is shown in block diagram form in Fig. 1.

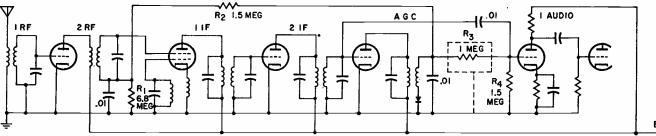

FIG. I—Arrangement of stages of open loop amplifier.

As shown in Fig. 2, input switch  $S_{101}$  is driven at a sampling rate of 400 cps. The input signal is impressed between the switch arm and the center tap of the input transformer. The modulated input signal is magnetically coupled to the ac carrier amplifier by the secondary of  $T_{101}$ , and is referenced to the amplifier common. Isolation necessary to achieve high common mode rejection is established at the input by transformer coupling and electrostatic shielding.

The unity gain amplifier  $Q_{101}$ ,  $Q_{102}$ , effects a high impedance transformation ratio to prevent loading of the input transformer, and provides a low source impedance to the gain attenuator  $S_{102}$ .

The loading of the unity gain amplifier, referred to the primary of the input transformer, is negligible; therefore, the input impedance of the total amplifier is determined by the half-primarv impedance of the input transformer at the carrier frequency of 400 cps. This value is always greater than one megohm and is independent of the amplifier's operating condition. Thus, the input circuitry provides a well isolated true differential input at a constant impedance level.

The gain attenuator  $S_{102}$  varies the overall gain of the instrument in fixed steps. Stability is assured by precision wire wound resistors.

A fixed gain amplifier  $(Q_{103}-Q_{108})$  is completely enclosed in feedback to insure gain stability.

A multi-turn, high resolution trimming potentiometer  $R_{159}$  is provided in the feedback network to serve as a fine gain vernier. This control is accessible through the front panel for screwdriver adjustment and allows the user to trim the amplifier gain to a high degree of precision. The output of the fixed gain amplifier is transformer coupled to the second section of switch  $S_{101}$  to achieve synchronous demodulation. The demodulated signal is presented to an appropriate filter and appears at the filter output as an accurate reproduction of the input signal. This signal is presented to the dc amplifier to terminate the filter and provide ample power gain and output characteristics consistent with the loads commonly incurred in data acquisition systems.

### Zero-Crossing Sync Circuit For SCRs

WHEN SCRS are used to control the ac power delivered to a load it is necessary to fire the SCRs at some selected point on the input sine wave. To do this, the SCR firing circuit must be synchronized with the zero crossing points of the sine wave to initiate a new timing cycle at each zero crossing. This synchronization can be done with the circuit shown.

#### Zero-crossing sync circuit.

$C_2$ ,  $Q_2$ ,  $R_5$ ,  $R_6$ , and  $T_2$  comprise the usual SCR firing circuit. Resistor  $R_5$  may be any control device, from a simple potentiometer to a servo control system.

To synchronize  $Q_2$ 's timing cycle so that it will start from each zero crossing, capacitor  $C_2$  must be discharged at each crossing. This is achieved as follows. Transformer  $T_1$  and rectifiers  $CR_1$  and  $CR_2$  form the zero-crossing reference by doubling the 60-cps line frequency to 120-cps pulsating dc.  $C_1$  differentiates this reference voltage and  $R_1$  discharges  $C_1$  at the end of each cycle. Zener diode  $CR_3$  conducts in the forward direction during the negative portion of the differentiated reference cycle, reverse biasing  $Q_1$ . As long as  $Q_1$  is reverse biased its effect on the UJT circuit is negligible, allowing  $Q_2$  to cycle at a frequency determined by its circuit values.

However, when the differentiated reference voltage starts to swing positive,  $CR_3$  ceases to conduct and then supplies a positive pulse when its zener voltage is reached. At this point  $Q_1$  becomes forward biased thus effectively shorting  $Q_2$ 's bases. This causes  $Q_2$  to fire (regardless of the amount of accumulated charge on  $C_2$ ) thus discharging  $C_2$ .  $R_4$  is adjusted so that the breakover point of  $CR_3$  is at the peak of the reference voltage (zero crossing point of the ac sine wave).

The polarities of  $CR_1$  and  $CR_2$  are so arranged that the sharp peaks of the reference voltage are positive after being differentiated by  $C_1$ . This provides a precise zero crossing sync pulse at each crossing.  $R_3$  serves as a current limiting resistor to protect  $CR_3$  and  $CR_4$  provides a small emitter bias so that  $Q_1$  will remain in its cut-off state until  $CR_3$  conducts in its reverse direction.

In a-temperature control system, this circuit maintained the temperature of a liquid within  $0.001^{\circ}$ C of the set point within a range of ambient to  $100^{\circ}$ C.

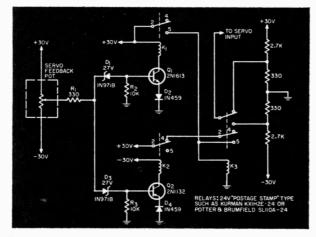

### Instrument Servo Cycling Circuit

IT OFTEN IS DESIRABLE to cycle servo units from stop to stop for extended lengths of time to determine such things as wear characteristics and friction level changes. Limit stop switches can be incorporated on larger units, but on instrument servos, this is not practical. However, most of these servos use a potentiometer as the feedback element, and this can be utilized, as shown, to supply the required reversing signal.

With the servo positioned midway between its stops, motor drive is applied so that the pot arm is driven toward +30 v. When the breakdown voltage of  $D_1$  (27 v) is exceeded, it conducts, turning on  $Q_1$ .  $K_1$  pulls in, energizing  $K_3$ , and the motor drive reverses. As the pot arm travels toward -30 v,  $Q_1$  turns off, and  $K_1$  drops out, but  $K_3$ remains energized through holding voltage applied to contacts 2 and 5. As -30 v is approached by the pot wiper arm,  $D_3$  conducts and turns on  $Q_2$ .  $K_2$  pulls in, de-energizing  $K_3$ , and motor drive again reverses. As the pot arm moves back toward +30 v,  $Q_2$  turns off,  $K_2$  drops out, and the cycle repeats.

Instrument-servo cycling circuit.

As shown, relay  $K_3$  reverses a dc servo input signal, but it could just as easily reverse the actual motor drive if desired. Similarly, the use of variable supplies and/or zeners with different breakdown voltages allows one to cycle the servo over any portion of its travel continuously.

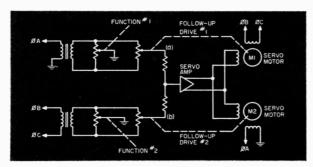

### Double-Channel Servo Controls Two Motors

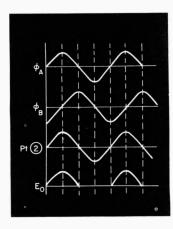

WITH ONLY ONE servo amplifier driving two channels of servo control, the number of electronic parts can be reduced 50 percent. In the block diagram, if the shaft position representing the first signal changes, then a difference will occur between the signal position and its follow-up position. This difference will appear as a voltage at point (a) which is in phase with  $\phi_A$ . This signal voltage will be amplified and appear across the control windings of both  $M_1$  and  $M_2$ . However, since  $M_2$  has its fixed-phase excitation from phase A, it will not respond to the signal.  $M_1$ , however, is referenced to  $\phi_B$  and  $\phi_C$  which is 90 degrees out of phase with the signal. The two-phase servo motor  $M_1$  will, therefore, respond to the signal while  $M_2$  will not. In a similar manner,  $M_2$  will respond only to signals generated at (b) by the second signal circuit because of the phase relationships.

This system serves best for servo loops with low dynamic

Two-channel servo system.

response since some quadrature voltage is generated in the amplifier when one channel is disturbed. This quadrature voltage, if large enough, can cause a slight shift in the null position of the other channel during the disturbance. In a servo loop with low dynamic response this quadrature voltage is negligible.  $\blacklozenge$

### Unijunction Latchup for SCR's Driving Inductive Loads

WHEN AN SCR, controlled by a unijunction transistor, is driving an inductive load, it may not turn on. When the unijunction fires, a pulse appearing at the scr gate begins to turn it on. The rate of current rise through the scr is limited by the inductance of the load so there is the possibility that the pulse at the gate may disappear before the load current rises above the holdon current level of the scr. If this happens, the scr will never turn on.

The unijunction latchup circuit for scr's turning on inductive loads and circuit waveforms.

A resistor across the inductor can eliminate the problem but this wastes power and it may call for a larger scr. A better circuit appears in the figure. When voltage is applied to the circuit,  $C_1$ , begins to charge through  $R_1$ . When the voltage at the emitter of the unijunction (point 1) reaches  $\eta V_x$  (where  $\eta$  is the intrinsic standoff ratio of the unijunction and  $V_z$  is the Zener voltage), the emitter is forward biased and  $C_1$  discharges into  $R_3$ . The unijunction turns on and the voltage at the base of  $Q_2$  (point 3) drops instantaneously.

This change in potential turns  $Q_2$  on, forcing a large current into the unijunction emitter. This action holds the unijunction in saturation, causing the voltage at the gate of the scr to be continuous rather than pulsating.  $R_1$  and  $C_1$  are chosen to give the desired time delay from

$$f \approx \frac{1}{R_1 C_1 \ln \left(\frac{1}{1-\eta}\right)}$$

$R_2$  depends on the desired temperature compensation. It is approximately 0.4  $V_{bb}/\eta V_s$ , where  $V_{bb}$  is the initial voltage between points 2 and 3.

### Simple Intervalometer

AN INTERVALOMETER, as applied to the control of aerial cameras, generates pulses which cycle the camera at a rate such that the terrain is photographed with a constant overlap. The expression which defines the required rate is as follows:

Rate = 1.69 V/H

$$\frac{f}{F} \times \frac{1}{1-0.01 \text{ (overlap)}}$$

where, V = velocity of aircraft in knots; H = altitude in feet; f = lens focal length in inches; F = format size in inches; and overlap is in percent.

Although there are several techniques which could be utilized to produce the pulses, it was found that a simple relaxation oscillator would generate the required pulse rate over a wide range to an accuracy of better than 3 percent.

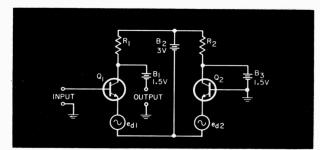

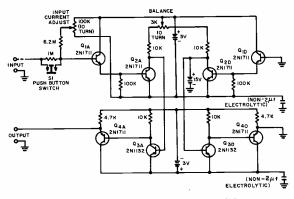

The basic circuit is shown in Fig. 1. The circuit as applied to aerial photography is shown in Fig. 2. A

Fig. 1. Basic pulse circuit.

Fig. 2. Actual circuit employed for aerial photography.

dc reference voltage is applied to a potentiometer whose arm would be rotated proportionately to the V/H ratio of the aircraft. This voltage is then added to a bias voltage which is set at just below the minimum firing level of the diode. Resistor  $R_2$  is made inversely proportional to the ratio of f/F, and C is set as a direct function of the factor: 1-0.01 (overlap).

The values given in Fig. 2 for  $R_2$  and C are the ranges within which reliable operation is assured. The magnitude of the reference voltage can be changed to set the scaling of the circuit.

The following experimental data is useful in working out the initial design of this type of intervalometer for a specific application: At a total input of 300 v, an R of 1 meg, and a C of 1  $\mu$ f, the pulse rate was found to be 3 cps. The frequency change as a function of the input voltage was 0.0133 cps/v. Based on the above data, the following equation for pulse rate is obtained:

Rate =

$$0.0143 \frac{V - V_o}{RC}$$

pulses/sec;

where, R = resistance in ohms; C = capacitance in farads; V = total input voltage; and  $V_o = bias$  voltage (approx. 140 for the NE96).

## SCR-Zener Combination Senses Voltage Limits

HERE IS A CIRCUIT that can be used when an automatic switch is required to turn a circuit on or off as a result of changes in supply voltage above or below a predetermined value.

The circuit shown turns on at 12 v and turns off at 8 v. When the supply voltage reaches 12 v, the zener diode goes into its avalanche region, and the SCR receives gate power to turn on. The relay then is energized, providing on-off control for the circuit connected through the relay contacts.

When the supply voltage goes down to 8 v, the zener draws only leakage current, which is not sufficient to turn on the SCR. Also, the current through the SCR is below its holding current, and, consequently, the SCR is non-conducting. The relay is thus de-energized, turning the controlled circuit off. Rectifiers can be used for isolation between two controlled circuits.

This circuit is versatile and has many uses. The controlled circuit might be a battery charger which is automatically connected to the supply battery when the battery voltage drops to 8 v and is disconnected when the battery voltage reaches 12 v.

Voltage-limit sensing circuit.

The circuit can be adapted to suit any supply and controlled-circuit voltages within the limits of semiconductor devices, and can be made to sense supply voltage changes as low as 0.5 v. To change the operating point of the circuit it is only necessary to use a different zener diode.

### Transistorized Phase Shifter

**O** FTEN IN SERVOS or other systems employing phase sensitive detectors or phase relationships to convey intelligence, a method of bucking out residual phase shift of the associated circuitry is required. In this circuit we have a simple, straight forward method of continual phase adjustment through nearly 180 deg. (in this case, greater than 170 deg). The transistor acts only as a phase splitter, offering complementary outputs. Phase shift at point A is 180 deg., at point B-0deg. By adjusting  $R_1$  through its range, proportional amounts of A and B are offered at the out-

FIG. I—Simple transistorized phase shifter, 0-180 deg. continuous.

put, determined by the specific setting of  $R_1$ , and the phase of the output relative to input is approximately in proportion to these relative amplitudes.

This particular circuit is optimized in the range of 1.0 kc and operates satisfactorily from 600 cps to 4.0 kc. An adjustment of  $C_1/R_1$  ratio will shift this range. The transistor is a TI 2N1306.

### SCR Voltage Sensitive Time Delay Switch

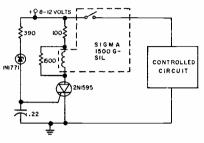

FTEN, IN MISSILE circuit applications, a designer is required to mechanize a series of switched events initiated by a reference voltage level and separated by accurate time delays. A device for this purpose-simple, yet reliable, is presented here. The circuit in Fig. 1 can best be described as a voltage sensitive trigger which initiates sequenced thermal time delay relays. The relays used are Network Electronics' type M779, available normally open or normally closed, singlepole-single-throw, which operate on the fuse burnout principle. That is, when sufficient current passes through the relay fuse to burn it open, a spring loaded plunger is released which performs the required switching action. The time delay between rectifier firing and switch actuation is controlled by the resistance value  $(R_3, R_4, or R_5)$  in series with each separate relay fuse. The smaller the resistance, the shorter the delay time. Delays from 10 msec to 1.0 sec.  $\pm$  10 per cent are readily obtainable with high reliability.

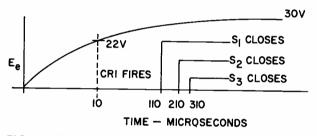

Applied voltage,  $E_e$ , is exponential and can be obtained from a standard type capacitor charging circuit. When voltage at point A reaches 22 v, the Zener diode conducts and applies the triggering

FIG. I—Voltage sensitive trigger circuit initiates sequenced time delays.

"signal" to the silicon controlled rectifier (SCR),  $CR_1$ , which "fires" and increases the currents through thermal elements of  $S_1$ ,  $S_2$  and  $S_3$ . Resistors  $R_3$ ,  $R_4$  and  $R_5$ , in this example, are chosen such that  $S_1$  closes 100 msec after  $CR_1$  fires,  $S_2$  at 200 msec and  $S_3$  at 300 msec. As the last fuse burns open, power is removed from the circuit thus eliminating unnecessary load on the missile power supply. The sequence of events is shown in Fig. 2.

Although, in the circuit shown, 22v at point A causes breakdown of the Zener diode, this voltage for breakdown can be varied along the exponential curve of Fig. 2 as long as there is sufficient power available at the SCR gate for firing. The resistance values in voltage divider  $R_2/R_1 + R_2$  are selected to insure necessary gate voltage and gate current to fire the SCR at lowest and highest temperature extremes. Actually, in the example given, the anode-to-cathode saturation voltage of the SCR is practically independent of ambient temperature at the operating current level. Thus, the voltage across the three relays will be essentially constant. This constant voltage with temperature is reflected in extremely accurate time delays from -65 to +100 C.

FIG. 2—Timing sequence as applied voltage,  $E_{\rm e_1}$  builds up.  $CR_1$  fires after 10 msec.  $S_{11}$   $S_2$  and  $S_3$  close at 100 msec intervals thereafter.

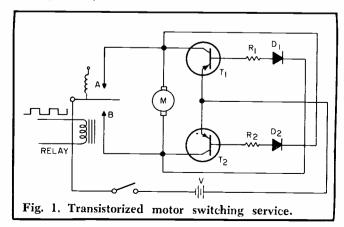

### Transistorized Motor Switching Circuit

**THE CIRCUIT SHOWN** in Fig. 1 was developed as a pulsed motor control circuit. This circuit offers the advantage of requiring only one voltage source, and eliminates non-simultaneous contact closing problems of dpdt relays.