PUBLICATION

21081

# how to use INTEGRATED CIRCUIT LOGIC ELEMENTS

by Jack W. Streater

How to Use

## INTEGRATED-CIRCUIT LOGIC ELEMENTS

by Jack W. Streater

World Radio History

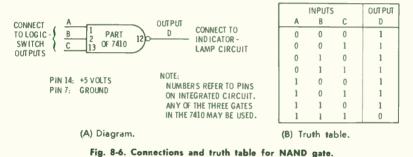

## SECOND EDITION

### FIRST PRINTING-1974

Copyright © 1969 and 1974 by Howard W. Sams & Co., Inc., Indianapolis, Indiana 46268. Printed in the United States of America.

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein.

International Standard Book Number: 0-672-21081-9 Library of Congress Catalog Card Number: 70-99803

## Preface

There have been two revolutions in electronics in the past twenty years. The transistor provided the first; the integrated circuit provided the second.

Ten years ago, it was clear that most electronic engineers and technicians were fast approaching technical obsolescence unless they had become familiar with the operation of transistors and transistor circuitry. Today, integrated circuits present another challenge. The integrated-circuit revolution which began several years ago is still gathering momentum, and nearly every branch of electronics has seen or will see radical changes before this revolution is over.

Integrated circuits can be classified broadly as linear or digital devices. But don't be mislead. The domain of digital circuits is widening; it now intrudes into what once was the domain only of linear circuits. The integrated circuit has so reduced the cost and size of digital functions that even engineers and technicians who have in the past worked exclusively with linear circuits ( amplifiers, filters, etc.) must now frequently consider whether a job can be done better by digital techniques. Thus, not only must these men learn what they can do with the new linear integrated circuits, but they must also keep abreast of what they might do with digital circuits. For many, this will require tackling a branch of electronics previously belonging to the computer technologists—logic systems.

Electrical and electronic service technicians are another group who will be affected by the integrated-circuit revolution. Logic devices will soon be found in appliances, automobiles, and probably in television and hi-fi, too, as well as in many other places at home, in commerce, and in industry. Although integrated circuits hold promise of higher reliability than electronics has ever known, sheer volume of usage will create a demand for a large number of technicians who can service logic circuits containing these devices. Forward-looking service technicians should prepare themselves to meet this demand.

This book will give such people a broad general introduction to integrated-circuit logic technology. The necessary mathematics is developed first. This mathematics, Boolean algebra, does not require knowledge of higher mathematics to understand it. The gate circuit and combinations of gates are discussed. Flip-flops are also covered. Then logic families are introduced and are compared. Finally, the use of off-the-shelf logic elements is considered. A glossary is given in Appendix 2.

The explanations of circuit operation in this book are based on the assumption that current is in the same direction as the flow of electrons—from negative to positive. This is in keeping with what is being taught today in many technical schools and the armed services. Engineers and others who have learned to think in terms of "conventional current," from positive to negative, should have no difficulty in adapting to this newer assumption. The explanations can readily be restated by experienced persons in their own terms, using the conventionalcurrent direction.

If you are an electronic hobbyist or experimenter, you will also find this book interesting and understandable. Fascinating logic circuits can now be assembled quickly and at very modest cost. The day may not be far off when home computers are almost as common as TV sets, or when building a home computer is a reasonable project for the experimenter.

JACK W. STREATER

## Contents

| INTRODUCTION |  | • | • | • | • |  |  |  | • |  |  |  |  | • | • | - 7 | ľ |

|--------------|--|---|---|---|---|--|--|--|---|--|--|--|--|---|---|-----|---|

|--------------|--|---|---|---|---|--|--|--|---|--|--|--|--|---|---|-----|---|

## CHAPTER 1

## CHAPTER 2

## CHAPTER 3

## **CHAPTER 4**

## GATE COMBINATIONS

Logic-Circuit Design—The Inhibit or Enable/Disable Gate —Transfer Circuits—The Comparator and the ExcLUSIVE OR—Translators, Encoders, and Decoders—MSI ROM's and PROM's—Using NAND and NOR Logic Elements— Positive Logic vs Negative Logic 51

## CHAPTER 5

| BISTABLE ELEMENTS AND THEIR U | SES.     |      |     |     |    | 78 |

|-------------------------------|----------|------|-----|-----|----|----|

| The R-S Flip-Flop—The R-S-T   |          |      |     | Fli | p- |    |

| Flop—The Shift Register—The   | Language | Prob | lem |     |    |    |

## CHAPTER 6

| HOW | LOGIC FAMILIES COMPARE                                                                                       | 93 |

|-----|--------------------------------------------------------------------------------------------------------------|----|

|     | Classification by Families—Diode Logic—Resistor-Transis-                                                     |    |

|     | tor Logic—Diode-Transistor Logic—Transistor-Transistor<br>Logic—Emitter-Coupled Logic or Current-Mode Logic— |    |

|     | Complementary-Transistor Logic—Metal-Oxide-Semicon-<br>ductor Logic                                          |    |

|     |                                                                                                              |    |

## CHAPTER 7

| USING OF | F-THE           | -She | LF | LOGIC ELI        | EMENTS    |     |      |     |      |   | 112 |

|----------|-----------------|------|----|------------------|-----------|-----|------|-----|------|---|-----|

|          | ces of<br>ing—T |      |    | Integrated oting | Circuits- | -Br | eadt | oar | ding | · |     |

## CHAPTER 8

| EXPERIMENTING WITH                                         | $\mathbf{L}$ | OGI  | IC E | LE   | MEN | TS |   |   |   |   |   | 125 |

|------------------------------------------------------------|--------------|------|------|------|-----|----|---|---|---|---|---|-----|

| Logic Demonstrato<br>Operation of NANE<br>Segment Numerica | G            | late | T—   | he J |     |    |   |   |   |   |   |     |

|                                                            |              | AF   | PE   | ١DI  | X 1 |    |   |   |   |   |   |     |

| CONVERSION TABLE .                                         |              |      |      | •    | •   | •  | • | • | • | • | • | 143 |

|                                                            |              | AF   | PE   | ١DI  | X 2 |    |   |   |   |   |   |     |

| GLOSSARY                                                   |              | •    | •    |      |     | •  | • | • | • |   |   | 145 |

World Radio History

## Introduction

This is a practical book. Its purpose is to help you use devices you can readily obtain today from nearly any electronic distributor. These same devices are already being used by the millions in computers, machine control systems, process control systems, data transmission systems for warehousing and transportation, and in a myriad other ways, ranging from the simplest logic circuits to elaborate controls in space vehicles and aircraft.

There is a certain minimum theoretical background without which you cannot take full advantage of the potential of integrated-circuit logic elements. If you are already familiar with the binary number system and the elements of Boolean algebra, use the first two chapters for review or skip them entirely. Otherwise, study these chapters before going on.

To get the most out of this book you should have at least a basic understanding of elementary electronics and simple transistor circuits. If you do not have this background, obtain one of the many books available on these subjects and read it along with this book.

The mathematics presented here includes an introduction to binary arithmetic and Boolean algebra. If these subjects are new to you, do not be afraid of them; most certainly do not be afraid of the names. Neither is really very difficult to understand. You do not have to delve deeply into either to gain sufficient background for understanding digital logic devices and simpler systems. The mathematics included here was carefully selected; it has been kept to a minimum for the benefit of those technicians, servicemen, and experimenters who might otherwise be frightened away by a more thorough presentation. Engineers who enjoy the mathematics can find numerous books treating Boolean algebra in more detail.

In learning a new subject, you must learn a new vocabulary. In fact, it is often the vocabulary that can hinder you if the study material is derived from trade magazines, technical papers (including manufacturers' application notes), and device data and specifications. For this reason, your vocabulary development is an important secondary objective of this book. As an additional aid, a glossary of terms frequently encountered in technical literature is included as an appendix.

You need a foundation upon which to build further knowledge. But all learning is not step-by-step, despite what some authors would lead you to believe. Much learning is like going around in a circle. The early chapters are not completely meaningful until you have read the later chapters, and you cannot understand the later chapters until you have finished the early ones. So a good way to learn a new subject is to move along, not spending too much time where you have difficulty, and then when you are finished go back and start again. The next time around new concepts are clarified and the overall picture comes more into focus while you gain a broader perspective.

If you possibly can, experiment with actual integratedcircuit devices. Buy an assortment and see them work. Build some of the combinations shown in Chapters 4 and 5 and compare their operation with the Boolean equations used in their design and analysis. Measure the voltages and observe their ranges and their values under different conditions. Chapter 7 contains suggestions for "breadboarding" logic circuits to help you along.

When you study, try restating the ideas in your own words. Do not be satisfied to say, "I understand it but I cannot explain it." To be able to state something is the only proof that you know it and understand it. Learning fast and well requires active participation on your part. Ask yourself questions and try to answer them, but do not get bogged down. If you cannot immediately answer a question, write it down and perhaps the answer will be found later. Be discontent until you know the answers but be patient enough to keep moving forward, confident that the answers will come.

## Chapter 1

## **Binary Numbers**

In the binary number system all numbers are formed from only two symbols: 0 (zero) and 1 (one). Any two distinct symbols could be used, but 0 and 1 are employed almost universally. Electronic digital computers use binary numbers because electrical switches and gates, the basic elements in these systems, are two-state (on-off) devices.

## **Counting Numbers**

Counting numbers in any system begin with zero and increase in a definite *order*. In our familiar decimal system we count:

## 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, . . .

After each of the ten decimal symbols has been used alone, larger numbers are formed by combining the symbols in a specific orderly pattern. In these larger numbers the meaning of each decimal digit depends on its place in the sequence. For example, in the number 37,357 the first 3 does not mean the same as the second one, nor do both sevens stand for the same amount. The symbols 3 and 7 are called *decimal digits*, but their value depends on their place in the sequence. The total value of the group of decimal digits is the sum of each individual digit value. In the preceding example the total value is

## 30,000 + 7000 + 300 + 50 + 7

The 7 at the far right is called the *least significant digit*, while the left-most 3 is called the *most significant digit*.

#### World Radio History

In binary numbers a similar structure is used. Here there are only two digits: 0 and 1. Thus,

Decimal Digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 Binary Digits: 0, 1

Sometimes the term *bit* is used for binary digit (from the term *binary* digit).

Larger binary numbers require a sequence of 0's and 1's. Beginning with zero, here are some of the lower binary counting numbers in order.

| Binary          | $Equiv. \ Decimal$ |

|-----------------|--------------------|

| Counting Number | Counting Number    |

| 0               | 0                  |

| 1               | 1                  |

| 10              | 2                  |

| 11              | 3                  |

| 100             | 4                  |

| 101             | 5                  |

| 110             | 6                  |

| 111             | 7                  |

| 1000            | 8                  |

Notice that the sequence of binary numbers can be generated by counting in our familiar decimal system but by skipping all numbers containing symbols other than 0 and 1.

Like decimal numbers, binary whole numbers have an order; that is, given any binary whole number, there is a next larger and a next smaller one, except for zero.

In both the decimal and binary number systems the place in the sequence determines the value of each symbol. In the decimal system the place value of an integer, counting from the far right, increases in powers of tens:

| most right-hand<br>2nd from right<br>3rd from right | •   | •  |   | • | • |   | • | 100  | ×<br>× | value<br>value<br>value | of<br>of | digit<br>digit |

|-----------------------------------------------------|-----|----|---|---|---|---|---|------|--------|-------------------------|----------|----------------|

| 4th from right                                      |     | •  | • | • | • | • | • | 1000 | ×      | value                   | 01       | digit          |

| In the binary syste                                 | m:  |    |   |   |   |   |   |      |        |                         |          |                |

| most right-hand                                     | dig | it | • | • | • |   | • |      |        | value                   |          |                |

| 2nd from right                                      | •   |    |   |   |   | • | • |      |        | value                   |          |                |

| 3rd from right                                      | •   | •  | • | • | • | • | • |      |        | value                   |          |                |

| 4th from right                                      |     |    |   |   |   |   |   | . 8  | ×      | value                   | of       | digit          |

. . . . . . . . . . . 16  $\times$  value of digit

10

5th from right

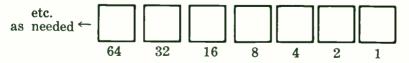

The multipliers increase from right to left by the sequence 1, 2, 4, 8, 16, 32, etc., each being twice the previous one.

Here you see that we may talk about the binary system using decimal numbers. We do this because we are so familiar with decimal numbers; we feel more at home with them and we have a better feeling for their magnitudes. If we had grown up with the binary number system, we would have less need to "translate" to decimal numbers. Then it would not seem strange to write ourselves a note to buy 1100 No. 110 screws, or a No. 10010 drill (translation: 12 No. 6 screws, a No. 18 drill).

We often want to translate back-and-forth between number systems. Of course, a large table could be used (a short one is provided in the appendix of this book). However, if no table is available, the translation is not difficult, as is shown in the following examples.

Example 1: What is the decimal equivalent of 1011010?

Solution: Taking the binary digits from right to left, multiply each by its decimal place value, then add all resulting terms.

binary digits (right to left) -£ decimal place value least significant place  $\rightarrow 0 \times 1$ = 0 $1 \times 2$ =2 $0 \times 4$ = 0 $1 \times 8 = 8$  $1 \times 16 = 16$  $0 \times 32 = 0$ most significant place  $\rightarrow 1 \times 64 = 64$ decimal sum = 90 = decimal equivalent of 1011010

Do yourself: What is the decimal equivalent of 1101010? (Answer: 106.)

Example 2: What is the binary equivalent of 39?

Solution: Fill in the boxes with 1's and 0's, so that the total value adds to 39.

The decimal value of each box is given below the box. Obviously, the 64 box and any box to the left of it must contain 0,

11

since 39 cannot be the sum of numbers which include 64, 128, etc.

However, 32 can be one of the numbers adding to 39, so place a 1 in that box. The remaining 7 counts (39 minus 32) must be the sum of values from the remaining boxes. Now, 16 and 8 cannot be among those numbers, as each is larger than 7, so put 0's in those boxes. Of the remaining three boxes, inspection shows that 7 is made up from the sum of 4 plus 2 plus 1, so 1's must be placed in each of the boxes having these values. The final result is 39 = 0100111, or simply 100111. Left-hand zeroes may be omitted, as in the decimal system, where 039 is usually written simply as 39.

The answer may be checked by converting back to the decimal system using the method in example 1.

Do yourself: Find the binary equivalent of 73. (Answer: 1001001.)

### Negative and Fractional Binary Numbers

Negative and fractional binary numbers are not normally used in logic systems, but they must be handled by computers in performing mathematical calculations.

Negative numbers are formed by prefixing a positive number with a negative sign. The sign of a number can be indicated with a 0 or 1 placed before it. The calculating system is then constructed to "recognize" the first digit as the sign, and to "know" whether 0 is minus and 1 is plus, or vice versa.

Fractions represent division. Fractions can be written in the binary system with a numerator and denominator separated by a fraction bar:

$\frac{5}{6}$  (decimal) is equivalent to  $\frac{101}{110}$  (binary)

In the decimal system certain fractions can be written with a decimal point. Examples are:

$$\frac{2}{10} = .2$$

$\frac{21}{100} = .21$

Certain binary fractions can be written similarly, although it is more appropriate to call the dot a "binary point" instead of a "decimal point." In the binary system:

12

.1 (binary) =  $\frac{1}{10}$  (binary) =  $\frac{1}{2}$  (decimal) .01 (binary) =  $\frac{1}{100}$  (binary) =  $\frac{1}{4}$  (decimal) .11 (binary) =  $\frac{11}{100}$  (binary) =  $\frac{3}{4}$  (decimal)

Example: What is the decimal equivalent of 101.11? Answer: Now 101 = 5 and

$$.11 = \frac{11}{100} = \frac{3}{4}$$

Therefore, the answer is  $101.11 = 5\frac{3}{4}$  or 5.75.

## **Binary-Coded Decimal**

There is a "hybrid" or mixed binary-decimal system in common use in computers called *binary-coded decimal* or *BCD*. The difference between "pure" binary numbers, such as we have just discussed, and BCD is illustrated as follows:

| Decimal Number | "Pure"<br>Binary Equivalent | BCD Equivalent             |  |

|----------------|-----------------------------|----------------------------|--|

| 39             | 100111                      | $\underbrace{0011}_{}1001$ |  |

| 27             | 11011                       | 3 9<br>0010 0111           |  |

|                |                             | 2 7                        |  |

In BCD, groups of four binary digits are used to represent decimal digits.

|              | Represents    |

|--------------|---------------|

| Binary Group | Decimal Digit |

| 0000         | 0             |

| 0001         | 1             |

| 0010         | 2             |

| 0011         | 3             |

| 0100         | 4             |

| 0101         | 5             |

| 0110         | 6             |

| 0111         | 7             |

| 1000         | 8             |

| 1001         | 9             |

There are some groups of four binary digits which are not used in BCD and which, accordingly, do not translate to decimal digits; that is, they do not represent any decimal digit at all. These groups are:

## 1010 1011 1100 1101 1110 1111

Notice that in pure binary these would be equivalent to 10, 11, 12, 13, 14, and 15. In the BCD representation, numbers larger than decimal 9 are represented by more than one group of four binary digits.

## Comparison of Decimal, Binary, and BCD Numbers

Until you get used to them, binary numbers seem strange. After a while they lose their unfamiliarity and become almost as easy to work with as decimals. However, you have surely already noticed that binary numbers are longer than corresponding decimal numbers. Even after you have become quite used to binary numbers, it will still be difficult to handle large binary numbers in your mind—to compare magnitudes, remember them, and perform mental arithmetic. Look at these numbers:

### 1968 and 11110110000

The first is certainly easier to remember. Perhaps the mind is better adapted to remembering the greater variety of symbols used in the decimal system, rather than the long string of 0's and 1's used in the binary system. If this is true, the human mind is quite different from the modern digital computer, which is far more easily designed to use binary numbers.

BCD numbers are even longer than pure binary. For example,

## 1968 (decimal) = 0001 1001 0110 1000 (BCD)

However, with very little practice, translation back and forth between BCD and decimal can be done quickly and accurately in your head, and the magnitudes and relative sizes of large BCD numbers are more recognizable than those of binary numbers. Large BCD numbers are hard to remember, but conversion to decimal is so easy that their magnitudes are easily recognized by quick mental translations. A string of binary digits (often abbreviated to "bits") can be thought of as a "code." Besides having equivalent decimal numbers, they can stand for almost any information at all. You only need a "codebook" or table to translate their meanings. If they represent codes in equipment someone else has designed, you need a codebook prepared by the designer in order to understand the code. If you are designing a logic system, you can let a string of bits stand for anything you choose, as long as in a single system or in two or more compatible systems the same string of bits stands for the same thing.

A string of bits is often used to stand for letters of the alphabet and also punctuation marks. Another common use is as "instructions." In a computer, applying one code may "tell" the computer to perform addition, while another code will tell it to subtract.

The size of the codebook depends on the number of bits used. A single bit allows only two codes. For example, 0 could mean "add," and 1 could mean "subtract." There is no way to include instructions to multiply or divide in this simple code without expanding it to a two-bit code.

The number of possible distinct codes increases with the number of bits used.

|                | Number of               |

|----------------|-------------------------|

| Number of Bits | Possible Distinct Codes |

| 1              | 2                       |

| 2              | 4                       |

| 3              | 8                       |

| 4              | 16                      |

| n              | $2^n$                   |

The use of codes will become clearer as your familiarity with logic systems increases.

## **Binary Addition**

Addition requires that an addition table be defined for any pair of digits. To add larger numbers the digits for corresponding places are added, according to the table, with carries to the next higher-value place as required.

The addition table for binary digits is much simpler than for decimal digits:

| 0 | + | 0 | = | 0  |

|---|---|---|---|----|

| 0 | + | 1 | = | 1  |

| 1 | + | 0 | = | 1  |

| 1 | + | 1 | = | 10 |

Sometimes this list is written in the form:

| + | 0 | 1  |

|---|---|----|

| 0 | 0 | 1  |

| 1 | 1 | 10 |

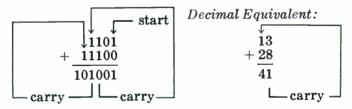

The addition of two binary numbers of more than one bit each is illustrated below. Add the least-significant digits first (at right unless otherwise stated). Then proceed a place at a time toward the higher significant places. "Carries" add to the next more significant column. If the addition of two 1's and a carry is required: 1 + 1 + 1 = 11, or 1 with a carry.

Example: Add 1101 and 101001 in the binary system.

Do yourself: Add 101110 and 110011 in the binary number system. (Answer: 1100001.)

## **Binary Multiplication**

The binary multiplication table is given in either of the following two forms:

| $\begin{array}{l} 0 \times 0 = 0 \\ 0 \times 1 = 0 \end{array}$ |    |

|-----------------------------------------------------------------|----|

| $1 \times 0 = 0$                                                | or |

| $1 \times 1 = 1$                                                |    |

| × | 0 | 1 |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

There are several ways to multiply larger numbers. One of these, illustrated below, follows the same pattern as our usual method for decimal multiplication.

16

Example: Multiply 1011 by 101.

```

\times \underbrace{\begin{array}{c} 1011 \\ 1011 \leftarrow 1 \times 1011 \\ 0000 \leftarrow 0 \times 1011, \text{ shifted left once} \\ 1011 \leftarrow 1 \times 1011, \text{ shifted left twice} \\ \hline 110111 \leftarrow \text{sum (answer)} \end{array}}

```

You will recognize the similarity to decimal multiplication.

Try these binary multiplications yourself:

1. 110 × 1101. (Answer:1001110.) 2. 100 × 1001. (Answer: 100100.)

Did you notice that when the multiplier is 1 followed by n zeros, you can simply add n zeros to the multiplicand and get the correct answer?

In the decimal system :  $1000 \times 39 = 39,000$ .

In the binary system :  $1000 \times 1101 = 1101000$ .

Adding a zero at the right (least significant) end of a binary number doubles its value. Of course, it follows that taking a zero away from the same end halves the value.

1010 is twice as large as 101.

1101 is half as large as 11010.

(Translate these numbers to decimal numbers, as a check. Can you see why this must always be true?)

For much larger numbers than those used in the preceding examples it becomes necessary to add long columns of binary digits. In doing this it is very easy to make errors in the carries. A variation of the foregoing method of multiplication permits addition of only two binary numbers at a time, often simplifying the carries considerably.

| 110101<br>× 101001 |                                      |

|--------------------|--------------------------------------|

| 110101             | ← 1 × 110101                         |

| 110101             | ← shift left until a 1 is encoun-    |

|                    | tered in multiplier                  |

| 111011101          | ← add                                |

| 110101             | ← shift left to next 1 in multiplier |

| 100001111101       | ← sum (answer)                       |

The intermediate sums require additional writing, but eliminate an addition of 1 + 1 + 1 + 1 = 100; that is, a carry two columns to the left. Of course, the carries are still more complex when the numbers are still larger.

Da yaurself: Multiply 1110101 and 100111 both ways. (Answer: 1000111010011.) Which way was easier for you?

## **Binary Subtraction and Division**

Since this book deals primarily with logic circuits rather than computers, we will not examine techniques for subtraction and division. These operations are described in many books on binary mathematics. They are not difficult, but are not required in order for the reader to understand the material in the remainder of this book.

## Chapter 2

## **Boolean Algebra**

Named after its inventor, the mathematician George Boole, Boolean algebra is a special kind of mathematics used to analyze and design logic systems. It is a complete "self-contained" mathematical system, with its own symbols and rules. You will find certain similarities to ordinary algebra; in fact, many rules for handling ordinary algebraic equations and expressions also apply to Boolean equations and expressions. But there are additional rules that work only for Boolean algebra.

Logic systems are composed of electric switches or electronic gates, both of which are two-state devices. Switches are either open or closed. Gates have high or low outputs and inputs (voltages or currents). Corresponding to these conditions, all quantities in Boolean algebra have only two possible values, symbolized as 0 or 1.

The relationship between the binary number system and Boolean algebra is often puzzling when the two are first encountered. Despite the facts that both use the binary symbols 0 and 1 and are associated with digital computers, they are separate subjects. Binary numbers are used in computers for calculating, in place of our familiar decimal numbers. Boolean algebra is used to design logic systems and digital control systems. However, instruction codes used in logic systems may sometimes be identified with the binary number which has the same sequence of binary digits.

Letters of the alphabet, capital or lower case, are used in Boolean algebra to stand for "variables," quantities whose values (0 or 1) may be assigned, or whose values are not known.

There are three basic "operations" in Boolean algebra. These are listed below along with their symbols and the way the symbols are read aloud.

| Operation                    | Symbol                                                      | Pronounced                             |

|------------------------------|-------------------------------------------------------------|----------------------------------------|

| OR (logical addition)        | A + B                                                       | A or B                                 |

| AND (logical multiplication) |                                                             |                                        |

|                              | $[A \times B]$                                              |                                        |

|                              | $ \begin{cases} A \times B \\ A \cdot B \\ AB \end{cases} $ | A and $B$                              |

| NOT (negation or             |                                                             |                                        |

| complementation)             | $\left\{ egin{array}{c} ar{A} \ A' \end{array}  ight\}$     | not A (or)<br>"the complement<br>of A" |

To "perform an operation," we determine a third quantity from two other quantities. To find this third quantity, tables and rules are used. For example, in conventional arithmetic, if we are given any two numbers we may perform the operation of addition with the help of rules for addition and the addition table. In this case, the third number is called the *sum*.

Since Boolean quantities can have only two values, 0 or 1, tables defining the three basic operations are short and easy to learn. You should memorize them thoroughly if you expect to be working with logic systems. These tables are given in the following sections.

## The OR Operation (Logical Addition)

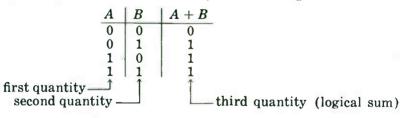

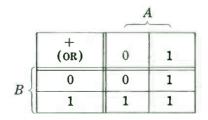

The OR operation is defined by the following table:

Every possibility for A and B is listed in the four lines above. The same information is sometimes presented in this form:

20

The two possible values of A head the two columns. The two possible values of B identify the two rows. The intersection of the column and row gives the third quantity defined by the OR operation, sometimes called the *logical* sum of A and B.

Example: Find A OR B for A = 0, B = 1.

Answer: In the first form of the OR table the answer is on the second line, where we read that A + B = 1. In the second form of the table, the answer is in the square under the column A = 0, and on the line B = 1. Again, we read that the logical sum of 0 + 1 is 1.

Notice that A + B = 1 if either A OR B is 1. Also from the table we see that A + B = B + A, for all values of A and B. In mathematical terms the OR operation *commutes*; in everyday language we can simply say that the order of the terms does not affect the answer.

The OR table is not the same as the binary addition table. The two tables do not refer to the same subject, nor to the same mathematical systems.

OR (logical addition): 1 + 1 = 1 (say, "one OR one equals one") binary addition: 1 + 1 = 10 (say, "one plus one equals one-zero")

There is no such quantity as ten in Boolean algebra.

## The AND Operation (Logical Multiplication)

The AND operation is defined by the following table:

|                  | A        | B   | AB  |

|------------------|----------|-----|-----|

|                  | 0        | 0   | 0   |

|                  | 0        | 1   | 0   |

|                  | 1        | 0   | 0   |

|                  | 1        | 1   | 1   |

| first quantity - | <b>_</b> | Í ↑ |     |

| second quantit   | ty—      |     | L t |

third quantity (logical product)

A

where AB denotes A AND B. An alternate form of the table is:

|          |            |   | <b></b> |

|----------|------------|---|---------|

|          | ×<br>(AND) | 0 | 1       |

| B        | 0          | 0 | 0       |

| <b>b</b> | 1          | 0 | 1       |

Notice that AB = 1 only if both A AND B are 1. Also the order of the terms does not matter; that is, AB = BA. (Mathematicians say that the AND operation "commutes.") This is quickly confirmed from the table, which shows that  $1 \times 0 = 0 \times 1 = 0$ .

Although the logical multiplication table and the binary multiplication table appear the same, each is really part of its own mathematical system.

## The NOT Operation

The NOT operation has only one "input" quantity instead of two, and in this sense is a different kind of operation from the OR and AND operations. However, this property is of no special significance to us. The defining table is:

The complement of 0 is 1. The complement of 1 is 0. Stated in another way, if A = 0, then NOT A (or  $\overline{A}$ ) = 1, and vice versa.

### **Boolean Algebra and Electric Switch Circuits**

We are going to take a brief "time out" from the theory of Boolean algebra, in order to be introduced to its relationship to logic circuits. When we return to more abstract mathematics, this glimpse of its practical use should make the theory more palatable.

In this introduction we will use switches as our "logic elements" rather than electronic gates. Two or more interconnected switches will be called a *logic circuit*. Each switch can be either open or closed. When a switch is moved (by hand or by applying a voltage to a relay coil) to its closed position, we will say it has an *input* of 1. When it is open we will call its input 0. A voltage at the output of the switch is a 1 output; no voltage is a 0 output.

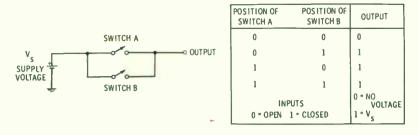

Fig. 2-1 shows an OR logic circuit consisting of switches A and B connected in parallel. With the circuit is a table which tells us for which combinations of switch positions there is an output voltage.

The table in Fig. 2-1 is the same as the OR table (logical addition) defined earlier. Thus, the Boolean OR operation symbolizes two switches connected in parallel. Conversely, parallelconnected switches are called an OR logic circuit. The Boolean

Fig. 2-1. OR logic circuit using switches.

equation for the circuit shown is: Output = A + B, where A designates the closed state of switch A = 1, and B = 1 the closed state of switch B.

There is no limit to the number of switches that can be connected in parallel. For n switches the equation becomes  $A_1 + A_2 + A_3 + \cdots + A_n =$  output. Notice that the order of listing the terms does not matter, any more than does the order of switches in the schematic. There is an output if  $A_1$  OR  $A_2$  OR  $A_3$ , etc., is closed.

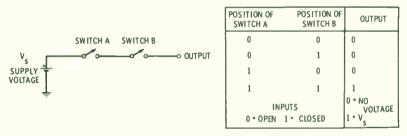

Fig. 2-2. AND circuit using switches.

Now look at the circuit in Fig. 2-2, where two switches are connected in series. Again, we can make a table showing the output for every switch combination. As before, there are four possible situations where switches A and B are open or closed (0 or 1). This table, you will notice, is the same as the Boolean AND table, and accordingly switches in series are called a logical AND circuit. The Boolean algebra equation which represents this circuit is output =  $A \times B$ , or simply output = AB, where A = 1 designates the closed state of switch A, and B = 1 the closed state of switch B.

We can connect any number of switches in series, but there is a 1 output only if all the switches are closed. In this case, the Boolean equation becomes

$$Output = A_1 A_2 A_3 \cdot \cdot \cdot A_n$$

where n is the number of switches.

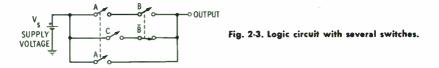

In Fig. 2-3, a more complex switching circuit is shown. Switches A and B are shown twice. They are switches with two poles, where operating a single "handle" operates two sets of contacts at once. The dotted lines show that the contacts act together. If we say that A = 1, we mean that both pairs of contacts labeled A are closed; if A = 0, both are open. Switch B has two poles too, but whenever one is open the other is closed, and vice versa. We can represent this by calling one condition of these pairs of contacts B and the other condition  $\overline{B}$  (NOT B). In this case, it becomes necessary to redefine slightly the 0 and 1 switch positions, in terms of the switch handle position. The handle position for which contact B is closed is 1, while 0 is the handle position for which contact  $\overline{B}$  is closed.

Since there are three switches (inputs), there are eight lines in the table summarizing the output for each possible set of switch conditions (Table 2-1). Notice that there are five conditions for which there is a voltage output.

We can write a Boolean algebra equation describing the operation of the logic circuit of Fig. 2-3. Since there are three *parallel* branches, the equation will be of the form

$$Output = () + () + ()$$

| Table 2-1. Output f | or All Switch | Positions for | Logic | Circuit o | of Fig. | 2-3 |

|---------------------|---------------|---------------|-------|-----------|---------|-----|

|---------------------|---------------|---------------|-------|-----------|---------|-----|

| Position of<br>Switch A | Position of<br>Switch B | Position of<br>Switch C | Output |

|-------------------------|-------------------------|-------------------------|--------|

| 0                       | 0                       | 0                       | 0      |

| 0 .                     | 0                       | 1                       | 1      |

| 0                       | 1                       | 0                       | 0      |

| 0                       | 1                       | 1                       | 0      |

| 1                       | 0                       | 0                       | 1      |

| 1                       | 0                       | 1                       | 1      |

| 1                       | 1                       | 0                       | 1      |

| 1                       | 1                       | 1                       | 1      |

In the upper branch switches A and B are connected in series. The term for this branch to be a closed circuit is AB, so we substitute this in the first pair of parentheses. The term describing the middle branch is  $\overline{BC}$ , which we substitute in the second set of parentheses. In the last branch there is only one switch, so we place A inside the third pair of parentheses. The complete Boolean algebraic equation becomes

$$Output = AB + BC + A$$

If we let the output be represented by D, then we can write

$$D = AB + \overline{B}C + A$$

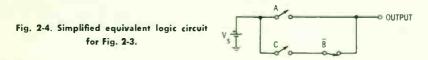

Notice that the upper branch could be left off without affecting the logic of this particular circuit; that is, the circuit in Fig. 2-4, which is simpler, will do the same job, because it has the same logic table.

In designing logic circuits, especially more complicated ones, it nearly always happens that there are many different circuits which will accomplish the desired objective. One of the problems of the circuit designer is to find the simplest, often lowest cost, way of achieving a certain logic function. It often is not obvious just what circuit this is. Writing Boolean equations and then rearranging and simplifying the equations following the rules of Boolean algebra is one technique for finding simpler circuits.

Notice that not only can we write the equation for a logic circuit from the circuit diagram, but we can also do the reverse—we can draw the circuit if we are given the Boolean equation. Each group of factors separated by a + (OR) sign stands for a parallel branch. The factors themselves (such as AB, BC, etc.) represent conditions of switches in series along that particular branch.

The tables we have constructed for the various circuits are called *truth tables* or *logic tables*. They are used extensively in analysis and design, alone or hand in hand with the Boolean equations. To illustrate one use of these tables, look at Table 2-1 and observe that the output is 1 whenever switch A is closed (A = 1), or if switch C is closed (C = 1) at the same time that switch B is open (B = 0). When switch B is open (B = 0),

switch  $\overline{B}$  is closed ( $\overline{B} = 1$ ), so we could alternately say that the output is 1 if A is 1 or if both C and  $\overline{B}$  are 1. The equation for this is

$$Output = A + CB$$

From this equation we can draw the circuit of Fig. 2-4 directly. Thus, had we not noticed the simplified circuit otherwise, we might have discovered it by examining the truth table.

In Fig. 2-4 you may be confused because the contacts of switch B are drawn closed and labeled  $\overline{B}$ . This representation resulted from an arbitrary decision when we drew Fig. 2-3. Switch B consists of two opposite-acting poles—one is open whenever the other is closed—it was clear enough that one should be labeled B and the other  $\overline{B}$ . When we eliminated one pair of contacts (one pole), it happened to be those called B, and we were left with only switch  $\overline{B}$  in the circuit. In a practical situation such an assignment of symbols might have been based on the positions of the handle of a toggle switch, "1" meaning the handle is up and "0" meaning the handle is down. If the switch were relay operated, contacts which are open when the relay coil is unenergized would be labeled B, and the normally closed contacts  $\overline{B}$ .

In all branches of engineering the problem of analysis (finding how something works) is quite different from the problem of design or synthesis (putting elements together to work in a particular way). In general it is much easier to determine how something works. This is as true in the field of logic systems as in other areas of electronics. However, the two tools we are studying in this chapter—truth tables and Boolean algebra are useful for both analyzing and synthesizing logic circuits.

With these glimpses into the applications of Boolean algebra, we now return to learn more about it. So far we have learned the basic operations, how these correspond to parallel and series-switching circuits, and how Boolean expressions can represent these circuits. The next step is to study ways to rearrange and simplify these expressions, keeping in mind that the equations so obtained represent equivalent circuits for performing the same logic function.

## Basic Relations and Laws of Boolean Algebra

The following basic relations are easily verified from the truth tables of the OR and AND operations. From the OR truth table:

$$A + 0 = A$$

$$A + 1 = 1$$

$$A + A + A + \cdots + A = A$$

$$A + \overline{A} = 1$$

You will find that the equations are valid whether A = 0 or whether A = 1.

From the AND truth table you can prove that:

$$A \times 0 = 0$$

$$A \times 1 = A$$

$$A \times A \times A \times \cdots \times A = A$$

$$A \times \overline{A} = 0$$

As before, let A = 1 and you will see that each equation is true; then let A = 0 and the equations will again be true.

A rather obvious, but frequently useful, relation is

$$(\bar{A}) = A$$

That is, if a Boolean quantity is complemented, then complemented again, the original quantity is obtained.

Arithmetic addition, arithmetic multiplication, logical addition (OR'ing), and logical multiplication (AND'ing) are all called *binary operations*. The word *binary* in this case does not refer to binary numbers, but rather means that the operations take *two* quantities to get an answer. Recall that the OR table gives the result of operating on or combining *two* quantities, just as the arithmetic addition table gives the *sum* of two quantities. The *law of association* tells us how to combine three or more quantities. We first take any two of the quantities and replace them by the quantity obtained by performing the operation on them. The law is written in symbolic shorthand by these equations:

$$A + B + C = (A + B) + C = A + (B + C)$$

$ABC = (AB)C = A(BC)$

The first equation is for the OR operation; the second is for the AND operation. The parentheses indicate that the quantities inside are to be combined first and the result substituted in their place. The fact that the pairs of parentheses can enclose different quantities means that it does not matter which two quantities we choose to combine first—we get the same answer in any order we take them.

Table 2-2 shows a truth table which proves the law of association for the oR case. The eight lines contain the eight possible combinations of states that A, B, and C can have. For each combination, the quantities (A + B) and (B + C) are computed. Then each of these results is combined with C and A, respectively, to form the last two columns. The quantities (values) in the last two columns are the same, for each possible set of values for A, B, and C. Therefore, we can say it is always true that

$$(A + B) + C = A + (B + C)$$

Do yourself: Construct a truth table to prove that  $(AB)C \equiv A(BC)$ .

The law of distribution is written as follows:

$$A\left(B+C\right) = AB + AC$$

| Α | B | С | A+B | B+C | (A+B)+C | A+(B+C) |

|---|---|---|-----|-----|---------|---------|

| 0 | 0 | 0 | 0   | 0   | 0       | 0       |

| 0 | 0 | 1 | 0   | T   | 1       | 1       |

| 0 | 1 | 0 | 1   | 1   | 1       | 1       |

| 0 | 1 | 1 | 1   | 1   | 1       | 1       |

| 1 | 0 | 0 | 1   | 0   | 1       | 1       |

| 1 | 0 | 1 | 1   | 1   | 1       | 1       |

| 1 | 1 | 0 | 1   | 1   | 1       | 1       |

| 1 | 1 | 1 | 1   | 1   | 1       | 1       |

Table 2-2. Truth Table for Law of Association With OR Operation

This is, of course, familiar to you from ordinary algebra, and it is equally valid for Boolean algebra. Working this law backwards, we perform the process of *factoring*; that is,

$$AB + AC = A(B + C)$$

More than one common factor may be "removed" from each term in a series of OR'ed terms and placed outside the parentheses. For example:

$$ABC + ABD = AB(C + D)$$

$$AB\overline{C}D + A\overline{C}D = A\overline{C}D(B + 1)$$

Once again, we can use a truth table to prove equivalency of two Boolean expressions, in this case those expressions illustrating the law of distribution. Look at Table 2-3. As always, where three variables are involved, there are eight lines to the truth table. For each possible set of values of A, B, and Cwe can readily "compute" (B + C). This result is AND'ed with A, giving the logical product A(B + C) and forming the fifth column. In the sixth and seventh columns we compute AB and AC. Finally, for each pair of values for AB and AC we find (AB + AC) and place this quantity in the last column. Now compare the fifth and eighth columns: They are identical. We therefore can conclude that no matter what values A, B, and C have, it is always true that

$$A\left(B+C\right)=AB+AC$$

Another useful relation is this:

$$A + AB = A + B$$

The equivalency of these two expressions is easily proved by using a truth table, and it is suggested that you construct a table and satisfy yourself that the expressions are equivalent.

| Table 2-3. Truth Table for Law of Distribution With OR | Operation |

|--------------------------------------------------------|-----------|

|--------------------------------------------------------|-----------|

| A | В | с | B+C        | A(B+C) | AB | AC | AB+AC |

|---|---|---|------------|--------|----|----|-------|

| 0 | 0 | 0 | 0          | 0      | 0  | 0  | 0     |

| 0 | 0 | 1 | 1          | 0      | 0  | 0  | 0     |

| 0 | 1 | 0 | 1          | 0      | 0  | 0  | 0     |

| 0 | 1 | 1 | , <b>1</b> | 0      | 0  | 0  | 0     |

| 1 | 0 | 0 | 0          | 0      | 0  | 0  | 0     |

| 1 | 0 | 1 | 1          | 1      | 0  | 1  | 1     |

| 1 | 1 | 0 | 1          | 1      | 1  | 0  | 1     |

| 1 | 1 | 1 | 1          | 1      | 1  | 1  | 1     |

Two very useful relations are called *De Morgan's laws*:

(1)

$$\overline{AB} = \overline{A} + \overline{B}$$

(2)  $\overline{A + B} = \overline{A}\overline{B}$

Their greatest value arises in designing circuits containing electronic gates, as you will see in a later chapter. Some people find the following statements help them remember these laws:

- "The complement of the product equals the sum of the complements."

- "The complement of the sum equals the product of the complements."

Do yourself: Construct truth tables to prove De Morgan's laws. This will give you practice in making truth tables and will help you remember the two laws.

Although the main subject of this section has been the fundamental rules and relations in Boolean algebra, notice the part played by the truth table. By expanding it from the simple form which defines the AND and OR operations, we have used the truth table as a means of proving that two expressions are equivalent for all values of the variables. This is practical because the number of possible combinations of variable quantities is finite—four combinations for two variables, eight combinations for three variables,  $2^n$  combinations for *n* variables. Of course, when *n* is large, there will be a great number of lines in the truth table. In our ordinary number system, such an approach to proving equivalence of two expressions could not work, as each variable can have an infinite number of possible values.

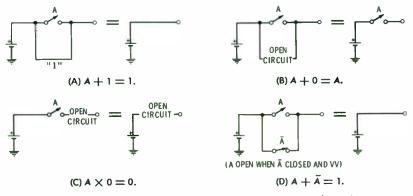

Each of the basic relations in this section represents an electric switch circuit. Whenever a zero (0) appears, it is equivalent to no connection at all—a permanent "open circuit." A one (1) represents a switch that is always closed; a piece of wire will do as well and costs less. Fig. 2-5 contains a number of examples of basic Boolean expressions and equivalent switch circuits.

## Simplifying Boolean Expressions

We evaluate Boolean expressions by substituting numbers (0 or 1) for the variables and performing the operations. We have been evaluating expressions right along in making up truth tables. Almost any two expressions, when evaluated for certain sets of numbers, will produce the same answer. For example, if A = 1, B = 0, and C = 1,

$$AB + BC = (1 \times 0) + (1 \times 1) = 0 + 1 = 1$$

$ABC + A = (1 \times 0 \times 1) + 1 = 0 + 1 = 1$

However, if we evaluate these expressions for A = 1, B = 0, and C = 0 we do not get the same answer from both.

Equivalent expressions are those which, when evaluated for any set of numbers, give the same result. They represent circuits of interconnected switches or electronic gates which perform the same logic function, even though like the Boolean expressions, they may appear quite different. The equals sign is used to show that two Boolean expressions are equivalent:

$$AB + B = A + B$$

This is a correct Boolean statement of equivalency.

Boolean expressions connected by an equals sign have the appearance of an algebraic equation. However, it is not correct in Boolean algebra to "solve" these equations as we would in ordinary algebra. For example,

$$A\overline{B} + B = A + B$$

$$A\overline{B} = A$$

$$\overline{B} = 1$$

*is not correct.* In ordinary algebra, the above procedure involves the operations of subtraction and division. Neither of these operations are a part of Boolean algebra.

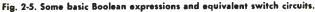

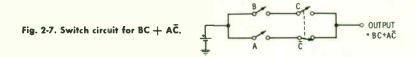

In Fig. 2-6, circuits 2-6A and 2-6B and their Boolean expressions are equivalent logically, even though both the schematic diagrams and the Boolean expressions are different. However, circuit 2-6A contains only three single-pole switches while circuit 2-6B contains two single-pole and one double-pole switches. Therefore circuit 2-6A is simpler and would probably cost less to construct. The object of simplifying Boolean expressions is to discover alternate logic schematics, usually for

Fig. 2-6. Logically equivalent switch circuits.

the purpose of minimizing the number and complexity of switches and gates.

We will now examine several Boolean expressions and see how the basic relations and rules can be applied to find simpler equivalent expressions.

Example No. 1: Simplify (A + AB). Reason factor A + AB = A(1 + B) $= A \times 1$ 1 + B = 1= A $A \times 1 = A$ Example No. 2: Simplify AB + AB. Reason  $AB + A\overline{B} = A(B + \overline{B})$ factor  $B + \overline{B} = 1$  $= A \times 1$ = A $A \times 1 = A$ Example No. 3: Simplify A(A + B). Reason law of distribution  $A\left(A+B\right) = AA + AB$  $A \times A = A$ = A + AB= A(1 + B)factor  $= A \times 1$ 1 + B = 1 $A \times 1 = A$ = AExample No. 4: Simplify (A + B) (A + C). Reason law of (A+B) (A+C) = AA + AC + BA + BCdistribution = A + AC + BA + BC $A \times A = A$ = A (1 + C + B) + BCfactor  $= (A \times 1) + BC$ 1 + anyquantity = 1= A + BC $A \times 1 = A$ Do yourself: Simplify: (1)  $(A + \bar{B})B$ (2)  $(A + B)(A + \overline{B})$ (3)  $\overline{A}BC + A\overline{B}\overline{C} + AB\overline{C} + ABC$

Answers: (1) AB; (2) A; (3) BC  $+ A\overline{C}$ .

In the third problem, you may have noticed that simplification can proceed along more than one route. Sometimes one route will lead to a simpler expression than will another route. It may be necessary to try several routes to arrive at the simplest expression, even though all routes lead to expressions which are less complex than the original one.

If in the third problem above you began by factoring B out of the first and third terms, you obtained

$$B(\overline{A}C + A\overline{C}) + A(\overline{B}\overline{C} + BC)$$

This does indeed have fewer terms, and therefore requires fewer switches to implement. However, if you begin by factoring BC from the first and last terms you get instead

$$BC(\overline{A} + A) + A\overline{C}(\overline{B} + B) = BC + A\overline{C}$$

since  $\overline{A} + A = 1$  and  $\overline{B} + B = 1$ .

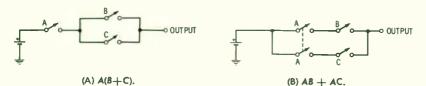

The switch circuit that accomplishes the logic of problem 3 is shown in Fig. 2-7. You can check this circuit by making a truth table for both the original expression and for the simplified circuit and expression.

## Design Procedure Using Truth Tables and Boolean Expressions

In designing a logic system, the engineer usually begins with a word problem—a verbal description of what the system is to accomplish. From here he must progress to the final design, which will include a schematic showing how to interconnect certain logic elements to satisfy the logic requirements.

An approach, which is more and more useful as the complexity increases, consists of the following steps:

- 1. Word description of problem.

- 2. Truth table.

- 3. Boolean expression.

- 4. Simplified equivalent Boolean expression.

- 5. Schematic.

To illustrate this procedure, suppose we are to design a logic system where an electric motor is to operate from three switches.\* The 1 condition of each switch is with its handle up. The motor is to operate if:

- (1) Switch C is up and switches A and B are down.

- (2) Or, if switches A and B are up and C is down.

- (3) Or, if all three switches are up.

From this description, make a truth table. Try it yourself, then compare your table with the one in Table 2-4.

After the truth table, the next step is to write a Boolean expression. There is more than one way to do this, but the method which follows, sometimes called the *minterm method*, is usually the easiest.

From the truth table you can see that there are three ways to get a 1 at the output (motor running).

- (1) If  $\overline{A}$  and  $\overline{B}$  and C are all 1's.

- (2) Or, if A and B and  $\overline{C}$  are all 1's.

- (3) Or, if A and B and C are all 1's.

Notice how we have given a "different twist" to the problem. Instead of saying "if A is 0," we say "if  $\overline{A}$  is 1." These are equivalent statements.

It is now easy to write the Boolean expression. Every place we have said "or" we use the OR sign (+), and every place we have said "and" we indicate the AND operation. Our expression is

$$\overline{A}\overline{B}C + AB\overline{C} + ABC$$

| A | В | с | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 0      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1      |

Table 2-4. Truth Table for Electric Motor Problem

\*Switches are used as logic elements for examples in this chapter because they illustrate logic concepts even to those not familiar with electronic gates. This expression will have a value of 1 if the values of A. B. and C correspond to those on lines two, seven, or eight in the truth table (Table 2-4). For any other values (other lines in the truth table) the value of the expression is 0.

Using a more mechanical procedure we could have written down a pair of blank parentheses for each line in the truth table having an output of 1. We would then have connected these with OR signs, and have filled in each pair of parentheses with the logical product of the variables-complemented when the corresponding line shows a zero for the variable and uncomplemented when that line shows a *one* for the variable. That is, first write

$$() + () + ()$$

$\uparrow \uparrow \uparrow a$  term for each line

where the sutput is 1

where the output is 1

Next fill in the parentheses.

Example: The first pair of parentheses correspond to the second line of the truth table (Table 2-4), where A = 0, B = 0, and C = 1. Therefore fill in the parentheses with  $\overline{A} \times \overline{B} \times C$  or. more simply,  $\overline{ABC}$ . (Use the same rules for filling in the other two pairs of parentheses. The resulting expression will, of course, be the same as before.)

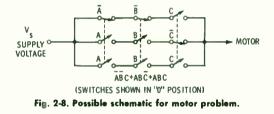

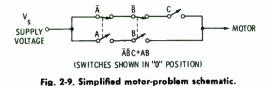

From the earlier discussion of the relation between electric switch connections and Boolean expressions, you will note that we can now draw a schematic (Fig. 2-8.) However, we should examine the expression to see if we can find an equivalent one which is simpler. Especially, we should look for common terms which may be factored, leaving expressions that can be replaced by 1. Try this yourself before reading on.

The correct simplification is:

$$\overline{ABC} + AB\overline{C} + ABC = \overline{ABC} + AB(\overline{C} + C)$$

$$= \overline{ABC} + AB$$

No further simplification is possible, because each factor appears complemented or uncomplemented just one time.

We can now draw the simpler switch connection diagram of Fig. 2-9, the solution to the problem. Remember that the OR sign indicates parallel paths; the logical multiplication (AND operation) indicates series connections. Chapter 3

# Gates

Gates are the basic building blocks of electronic logic systems. In some ways, a gate functions like one or more electric switches. A gate has an output terminal, where the voltage can have approximately one of two nominal values. These two values can be called the "0" and "1" output states. A gate has two or more inputs, in the form of voltages or currents, and each input can be called either a "0" input or a "1" input. Like two or more switches, a gate can be equivalent to an OR logic circuit or an AND logic circuit. But that is about as far as we can go in finding similarities. The *differences* between electronic gates and electric switch circuits underlay the phenomenal growth in the usage of gates in digital logic systems.

The modern solid-state, integrated-circuit gate is characterized by:

- 1. High speed—The output changes from one state to the other in as little as 2 nanoseconds ( $2 \times 10^{-9}$  second) following a signal change applied to the input.

- 2. Small size—Hundreds of gates, the equivalent of 500 or more switches, can be built on a silicon "chip" smaller than your little fingernail.

- 3. Low power—These same hundreds of gates may require less than 200 milliwatts of electric power.

- 4. Low cost—In large volumes the cost per gate may be as low as 5 cents.

Fig. 3-1. Typical transistor amplifier inputoutput relation.

## Gates Are a Special Class of Amplifiers

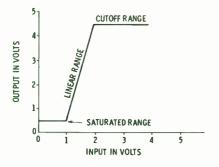

Except for diode gates which we will consider briefly later, electronic gates are really special forms of direct-coupled amplifiers. As amplifiers they are intended to be operated not in their "linear" operating range, but rather in their extreme bias conditions. Fig. 3-1 shows a typical relationship between the input voltage and output voltage in a transistor amplifier. (The same general relation also holds true for a vacuum-tube, direct-coupled amplifier, except that the voltage scales are different. However, there are very few vacuum-tube gates in use today, and those few that remain will nearly all be replaced eventually by equipment using smaller, more efficient, and more dependable solid-state gates.)

Amplifier input-output curves (Fig. 3-1) have a nearly linear section, normally used for signal amplification. Operating in this linear range an amplifier produces minimum distortion. The two end sections are often called the *saturated* and *cutoff* regions. However, in logic terminology the word "saturation" may also have a slightly different meaning, as we will see when we consider saturated logic versus nonsaturated logic.

Gates are not intended to be operated in the linear region of their input-output transfer curves. They are normally biased at either one end of the curve or the other. The in-between region is a logic "no-man's land." The two horizontal sections of the curve represent the 0 and 1 states of the gate.

Except for the NOT gate, or *inverter*, each gate has more than one input. In the case of OR gates the transfer curve applies to any input, but once one input is "high," the states of the other inputs make no difference in the output state. For AND gates the curve applies to any input when all other inputs are 1's.

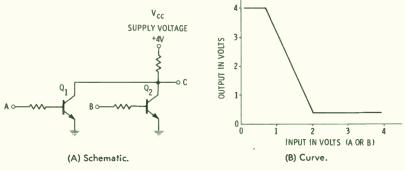

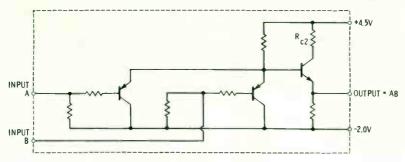

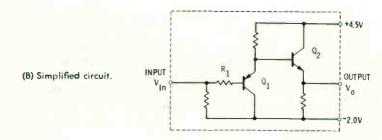

Fig. 3-2A shows the schematic for one kind of a two-input gate. The inputs are at A and B and the output is at C. When the input voltages at A and B are both zero, or nearly so, no

base current flows in either transistor. With no base current there is also no emitter-collector current, except for a small and negligible leakage current, and therefore essentially no current flows through the common collector resistor. With no current through the resistor, the output voltage at C is equal to the supply voltage. If sufficient voltage is applied to either input A or B, base current flows, collector current flows, and the voltage at C drops to about a quarter of a volt, the transistor "saturation" voltage. The input-output curve is shown in Fig. 3-2B, and you will notice that although it is reversed from the curve of Fig. 3-1, it nevertheless has the same flat high and low regions with a steep but nearly linear transition region between. We will consider this difference in more detail later.

Fig. 3-2. Schematic and input-output curve for one kind of gate.

Although only two inputs are shown in Fig. 3-2, you can see we could add many more inputs simply by adding one transistor and one resistor for each additional one. The common collector resistor continues to serve all the transistors. There is, of course, a point where the total leakage current of many transistors can no longer be ignored, especially at higher temperatures where leakage currents increase. However, gates with up to eight inputs are quite common, and even here the limit is due more to such practical restrictions as the number of terminals available in standardized integrated-circuit packages.

# Kinds of Gate Logic

Digital integrated circuits can be classified in a number of ways. The gate in Fig. 3-2 is called an RTL NOR gate and was one of the earliest kinds available in integrated-circuit form. "RTL" means *resistor-transistor logic* and refers to the details of the circuit—the types of electrical components and the way they are interconnected. "NOR" refers to the logic function performed, and is a contraction of NOT-OR, meaning a combination of an OR function with a NOT (or inverting) function. Other circuit-type classifications such as DTL, TTL, and ECL will be considered in more detail in a later chapter. In this section we will be concerned with the logic function performed by the gate.

It is sometimes helpful, but seldom completely necessary, to know just what *is* inside a gate that you plan to use. One advantage of integrated-circuit gates is that the gate circuitry is all designed for you. You can use the gates by simply following the rules set forth by the manufacturer, along with a knowledge of the capabilities and limitations of the gates, which are provided in the manufacturers' published technical data.

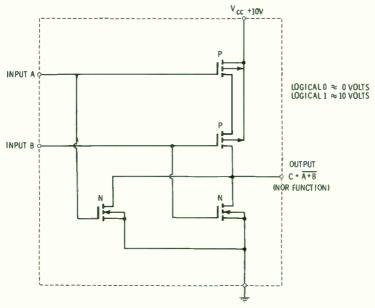

Gates are classified by logic function as OR, AND, NOR, and NAND gates. Table 3-1 gives the truth table defining these four functions for two- and three-input gates. You have already become familiar with the OR and AND functions in the last chapter. From the truth table you will notice that the NOR function is equal to an OR function followed by an inverter (NOT function). Similarly, the NAND function is equivalent to an AND gate followed by an inverter.

| Outputs For Different Kinds of Two-Input Gates |        |               |               |               |       |      |  |  |  |  |

|------------------------------------------------|--------|---------------|---------------|---------------|-------|------|--|--|--|--|

| In                                             | puts   |               | Gate          |               |       |      |  |  |  |  |

| A                                              | В      |               | OR            | AND           | NOR   | NAND |  |  |  |  |

| 0                                              | 0      |               | 0             | 0             | 1     | 1    |  |  |  |  |

| 0                                              | 1      |               | 1             | 0             | 0     | 1    |  |  |  |  |

| 1                                              | 0      |               | 1             | 0             | 0     | 1    |  |  |  |  |

| 1                                              | 1      |               | 1             | 1             | 0     | 0    |  |  |  |  |

|                                                | Outp   | outs For Diff | erent Kinds o | f Three-Input | Gates |      |  |  |  |  |

|                                                | Inputs |               | Gate          |               |       |      |  |  |  |  |

| A                                              | В      | С             | 0             | R AND         | NOR   | NAND |  |  |  |  |

| 0                                              | 0      | 0             | (             | ) 0           | 1     | 1    |  |  |  |  |

| 0                                              | 0      | 1             | ו             | 0             | 0     | 1    |  |  |  |  |

| 0                                              | 1      | 0             | 1             | 0             | 0     | 1    |  |  |  |  |

| 0                                              | 1      | 1             | ו             | 0             | 0     | 1    |  |  |  |  |

| 1                                              | 0      | 0             | ו             | 0             | 0     | 1    |  |  |  |  |

| 1                                              | 0      | 1             | ו             | 0             | 0     | 1    |  |  |  |  |

| 1                                              | 1      | 0             | ו             | 0             | 0     | 1    |  |  |  |  |

| 1                                              | 1      | 1             | 1             | 1             | 0     | 0    |  |  |  |  |

Table 3-1. Truth Tables for Several Kinds of Logic Gates

It is a characteristic of all four types that the output is at one state for *all except one* of the possible input conditions (see Table 3-1). For example, the OR gate has a 1 output unless all inputs are 0; the NAND gate has a 1 output unless all inputs are 1. This is true for any number of inputs.

By comparing the description of operation of the RTL NOR circuit in Fig. 3-2, with the OR columns in Table 3-1, you will see why the circuit is classified as NOR logic.

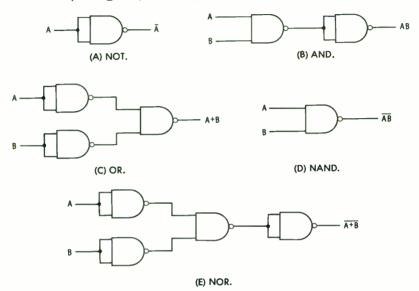

# Schematic Symbols for Gates

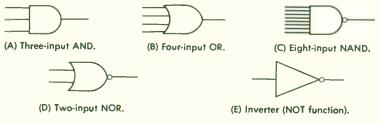

There is no need to draw the internal circuit of each gate in most logic system schematics. Such a procedure might make an impressively complex schematic, but definitely does *not* help others to understand how the system operates. Certain simplified symbols have come into common use, although they are not completely standardized. The most common symbols are shown in Fig. 3-3, for the various gates. Usually there are either two, three, four, or eight inputs to a gate, the number of inputs being shown by the number of "wires" extending from the input side. There is always just one output.

The small circle at the output end of a gate is frequently used to symbolize inversion (negation), as shown here. Occasionally you may see the circle placed at the input of a gate, but in this book inversion at a gate input will be represented by a separate inverter symbol.

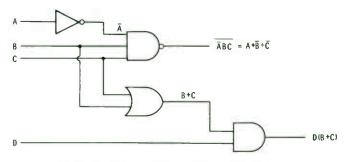

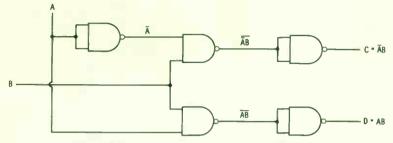

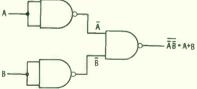

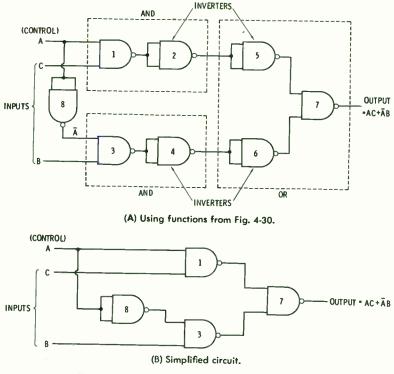

Fig. 3-4 illustrates a schematic showing several interconnected gates. The Boolean expressions are written over the wires to indicate the logic. Notice that the "system" in this example has two outputs, although each gate alone has only one. For the upper output, De Morgan's rules have been applied to give two equivalent Boolean expressions.

NAND and NOR gates are sometimes used as inverters by tying all inputs together. Study Table 3-1 to prove to yourself that this will work.

Fig. 3-3. Commonly used gate symbols.

Fig. 3-4. Logic diagram showing interconnected gates.

#### Signal Ranges

Referring back to Fig. 3-1, you will observe that there is a range of voltages near zero that can be applied to the input without any effect on the output. In the curve of Fig. 3-1 this range is approximately 0 to 0.7 volt. Any input voltage within this range is assigned a binary symbol, either 0 or 1. For the present, we will call this range the logical 0 input voltage range, which is the most common assignment.

At the other extreme, any input voltage over 1.5 volts has about the same effect on the output, causing the output to become about 4.5 volts. Therefore any voltage in the range of 1.5 volts or higher can be called a logical 1 signal. Of course, there is an upper limit to the input voltage; too much voltage will cause permanent damage to any gate. Practically speaking, the power supply voltage, often 4 or 5 volts, is usually considered the upper limit of the 1 input.

There are many different gate designs, and each has its own ranges of voltages which are acceptable 0's and 1's. When the range nearest 0 volts is assigned the symbol "0," and the higher range is assigned the symbol "1," we say we are using *positive logic*. The opposite assignment is called *negative logic*, and is less common, but nevertheless sometimes very useful. In this book, unless we specify otherwise, we will always use positive logic. We will, however, briefly examine the uses of negative logic later.

Most often, gates are used in groups, with the output of one gate driving the input of one or more other gates. This requires that the input and output voltage ranges be compatible. It would not do to have the output of a gate at 0.8 volt in its 0 state, when a 0 input must be 0.6 volt or less, because then we could not connect the output to another gate of the same type and expect the second gate to perform properly. As a general rule, therefore, the 0 and 1 states represent the same ranges of voltages, whether we are speaking of the input or the output of a gate. A *compatible family* consists of a set of different gate types which have the same 0 and 1 voltage ranges and can be interconnected to form a logic system.

#### Loading and Fan-Out

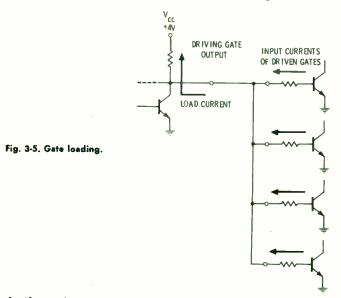

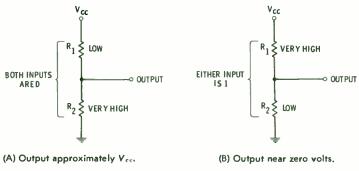

Because of its simple internal structure, we will use the RTL gate of Fig. 3-2 to illustrate the loading limits of gates. Part of that schematic is redrawn in Fig. 3-5. There the collector resistor of the gate is shown, and we have added a load to the gate—in this case the input circuits of four more gates. Now assume the output of the first gate is in the "high" or 1 state.

Although there is no current in any of the collectors of the transistors in the first gate, current flows into the first gate output terminal from the input terminals of each of the four gates connected to it. This output current causes a voltage drop across the collector resistor, so that the output voltage is not 4 volts at all, but quite a bit less. If too many gates are connected, the output voltage will fall low enough that it is no longer in the logical 1 range. Not being high enough, it cannot properly operate the gates connected as a load. The gate has been loaded too heavily. We say that its *fan-out* has been exceeded.

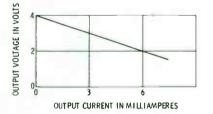

Fig. 3-6 shows the relationship between output voltage and output current. The actual numbers are for a typical RTL gate, but do not represent any particular manufacturer's design. Assume that for the gate represented by Fig. 3-6 a logical 0 is any voltage between 0 and 0.6 volt, and a logical 1 is any voltage between 2 and 4 volts. From the curve, we see that the logical 1 output will be 2 volts or higher as long as the output current does not exceed 6 mA. Now suppose we were given the additional information that when 2 volts is applied to the input of one of these gates, the current into it will be no greater than 2 milliamperes. We can see that we should not connect more than three gate inputs to the output if we want to be sure the 1 state output voltage does not fall below the minimum allowable 2 volts. The maximum fan-out is three.

Fig. 3-6. Typical output characteristic of RTL gate.

Some manufacturers, instead of giving a curve such as in Fig. 3-6 along with the input currents of various gates that are compatible with one another, will give fan-out data in terms of a *loading factor*. Load factors are relatively small whole numbers that simplify the estimation of fan-out limits. For example, for a particular gate, the output load factor might be specified as 10. If this gate drives three other gates with input loading factors of 2, 2, and 3 respectively, we can check to see if the load capability of the driving gate has been exceeded by simply adding the three input loading factors:

$$2 + 2 + 3 = 7$$

Since seven is less than ten, the load is acceptable.

# AC Loading

In the example of Fig. 3-5 the load is assumed to be a pure resistance. In actuality there is always some capacitance to ground at a gate input, as well as stray circuit capacitance from each conductor to ground. These capacitances do not affect steady-state voltages, but they do slow down the transition

44

speed. Some bistable elements (flip-flops) require a fast transition time in order to change state. Too much capacitance at a driving gate output will prevent these bistable elements from "triggering." Ac loading refers to limits imposed by gate input capacitances on the ability of a gate to drive compatible bistable devices. Usually these capacitances are taken into consideration in the gate design and in the specifications, so that the dc and ac load factors or fan-outs are the same.

# Buffers, Drivers, Expanders, and Translators

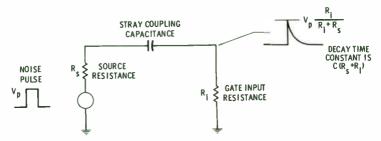

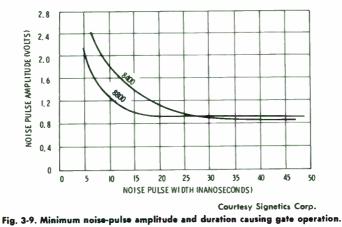

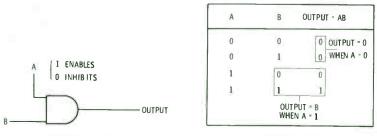

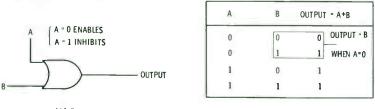

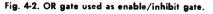

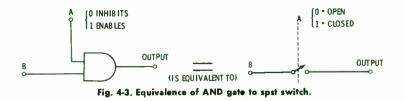

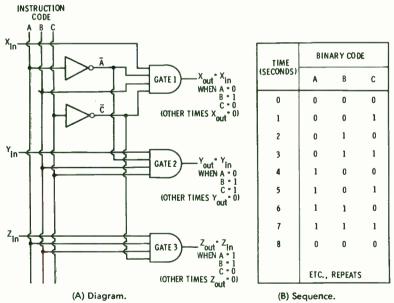

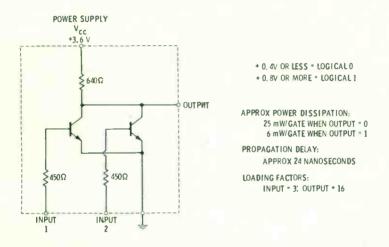

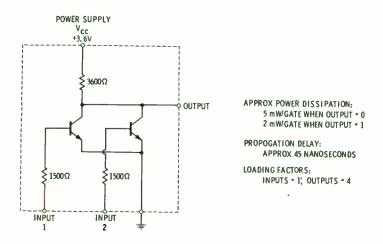

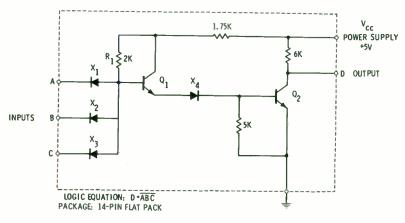

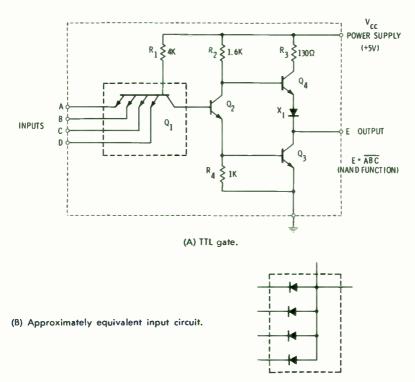

Certain special gate designs are intended to extend the capabilities of the more standard gates, either by increasing fan-out where many gates must be driven simultaneously, or by increasing the number of inputs to a gate. *Buffers* and *drivers* increase fan-out; *expanders* increase fan-in, the number of inputs.