ISBN 0-916688-04-6 \$11.95

### The Best of Volume I

Edited by David H. Ahl and Carl T. Helmers, Jr.

### The Best of Byte Volume 1

Edited by David H. Ahl and Carl T. Helmers, Jr.

**Creative Computing Press**

Morristown, New Jersey

#### OTHER BOOKS FROM CREATIVE COMPUTING PRESS

The Best of Creative Computing - Volumes 1 and 2 101 BASIC Computer Games Artist and Computer The Colossal Computer Cartoon Book Amazing, Thrilling, Fantastic Computer Stories

### **THE EDITORS**

David H. Ahl is the Founder of *Creative Computing* Magazine and Creative Computing Press. He was one of the early proponents of computers in education and has written numerous books and articles on the subject. He has also been associated with AT&T, Digital Equipment Corp., and Management Science Associates.

**Carl T. Helmers, Jr.** is and has been Editor of *Byte* Magazine since its founding in mid 1975. Prior to that he published *ECS* Magazine, a "home brew" hobbyist computer magazine. He is a well-rounded expert in all aspects of hobbyist computers hardware, software, and applications.

First Printing — March 1977

ISBN 0-916688-04-6 Library of Congress Catalog Card Number: 77-71270 Printed in the United States of America Copyright © 1977 by Creative Computing (Portions previously copyright © 1975, 1976 by Byte Publications, Inc.) All rights reserved.

Preface

On a recent Saturday I invited a group of some twenty associates and friends to my house to discuss the future direction of hobbyist computing (Naturally, my objective was to determine how Creative Com*puting* magazine and press should be positioned in the market). These people represented a diverse spectrum of the hobbyist computer movement -people from a major manufacturer which 18 months before consisted of two people in a basement workshop, representatives from a large 500-member computer club that two years earlier did not even exist, a department chairman from an lvy League University which had just graduated their first group of Computer Education majors, a salesman from a retail computer store which had just moved for the second time in six months to larger quarters, hobbyists from virtually every walk of life, and, of course, people from the publishing side of things.

What becomes quickly apparent is that the hobbyists who jumped in two years ago, or one year ago, or even six months ago are much further along than people entering today. Nevertheless, vast hordes of people continue to enter the hobby daily. Thus the magazines in the field are caught between a rock and a hard place — should a magazine progress along and continue to present challenging material to its earlier and technically more sophisticated subscribers? Or should it endeavor to bring the newcomer up to speed with primer-type material and risk losing its more knowledgeable readers? The magazine that attempts to do both is a bit like the boy in the Charles Addams cartoon who is sliding down a bannister that at the bottom of the stairs turns into a razor blade. However, before long it became apparent that hobbyists look at their computers as much more than just a toy; *Byte* is now dubbed "The Small Systems Journal" which better reflects the comprehensive scope of home computerists.

Under the direction of Editor Carl Helmers and Publisher Virginia Peschke, *Byte* not only reflects and responds to the enormous diversity of computer hobbyists, but sets the pace in innovation and new development. Naturally most hobbyist's first concern is getting a system built and running — the sections on "Computer Kits" and "Hardware" address this need. However, without software a computer might as well be a boat anchor, hence there is an equally large section on "Software." The questions of what's coming, how does it work, and what do you do with it are covered in the sections on "Opinion", "Theory", and "Applications".

Volume 1 of *Byte* magazine includes sixteen issues from the charter issue in September 1975 through December 1976. This book includes material from the first twelve issues. (Does this mean there will be a Volume 1.5? Quite probably.)

One solution to this dilemma is to offer back issues to later subscribers so they can get a quick cram course of what transpired before they subscribed. Better yet is a book, like this one, of the best material from previous issues of the magazine.

For those readers who don't know *Byte* magazine, it was one of the earliest entries in the hobby computer field. Some early issues carried the notation on the cover: "Computers - The World's Greatest Toy".

It's an impressive collection. Although I was a charter subscriber to *Byte* there were many articles I didn't read until I put them together in this volume. I couldn't help but be awed with how far hobbyist computing progressed in one short year. One can only wonder what the future holds in store. In my mind computers are truly different from any other hobby. First of all, they are not an end in themselves but rather a tool for accomplishing literally thousands of things. Second, computers are an intellectual tool, not simply a hammer or a lathe however useful they might be, but a fascinating, powerful, creative, mindexpanding, tool. The cliche is that "the sky is the limit", but I look beyond that. The cybernetic revolution has begun.

March, 1977 Morristown, New Jersey David H. Ahl

V

### **Table of Contents**

### **OPINION**

| The Shadow, Buck Rogers, and the Home Computer — Gardner | 2  |

|----------------------------------------------------------|----|

| The State of the Art — Helmers                           | 5  |

| Could a Computer Take Over — Rush                        | 8  |

| THEORY AND TECHNOLOGY                                    |    |

| A Systems Approach to a Personal                         | 14 |

| Microprocessor — Suding                                  |    |

| Frankenstein Emulation — Murray                          | 17 |

| Programming for the Beginner — Herman                    | 22 |

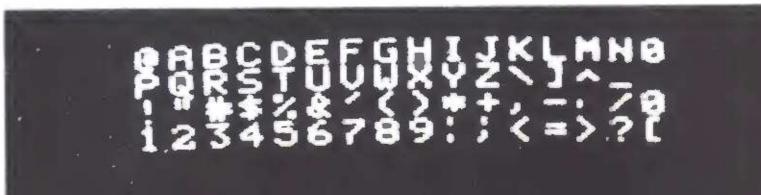

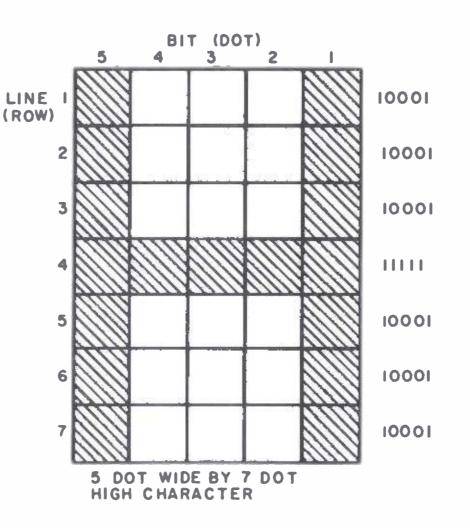

| What is a Character — Peshka                             | 27 |

| Friends, Humans, and Countryrobots:                      | 36 |

|                                                          |    |

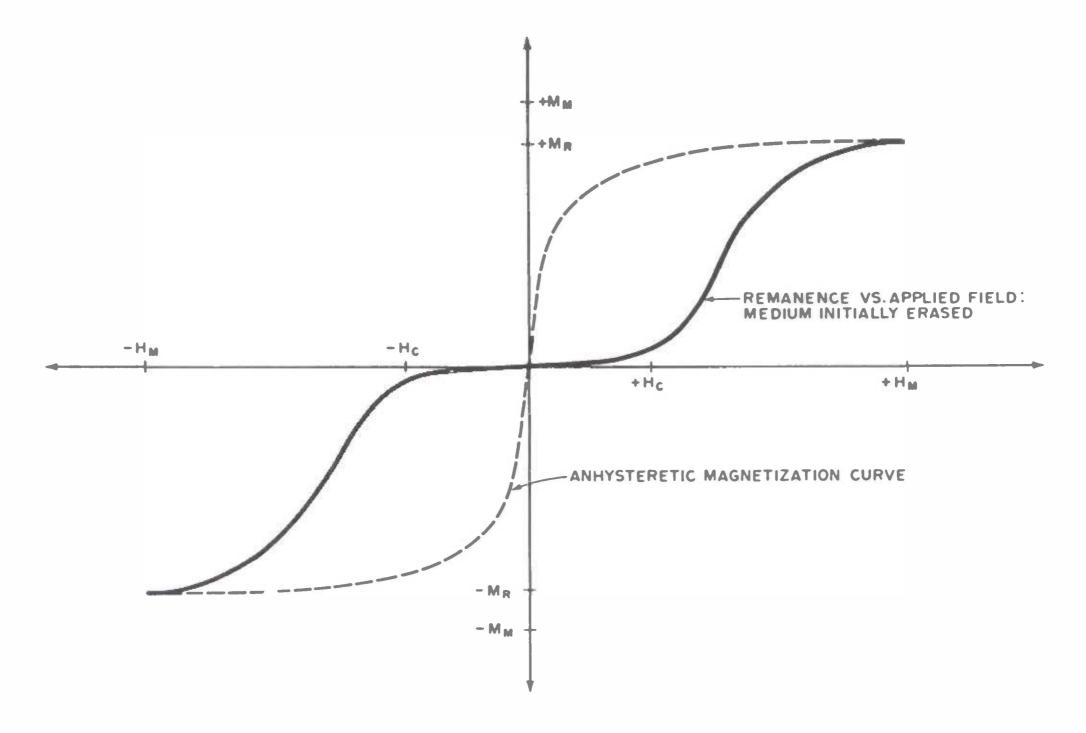

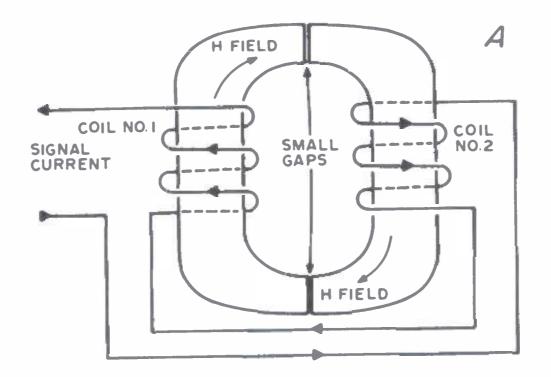

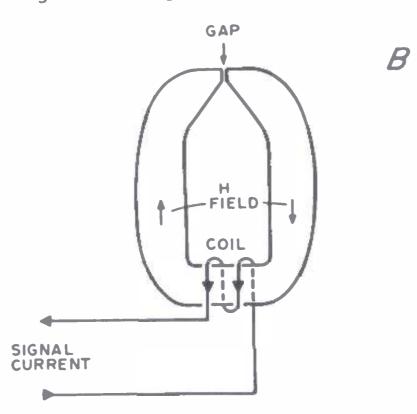

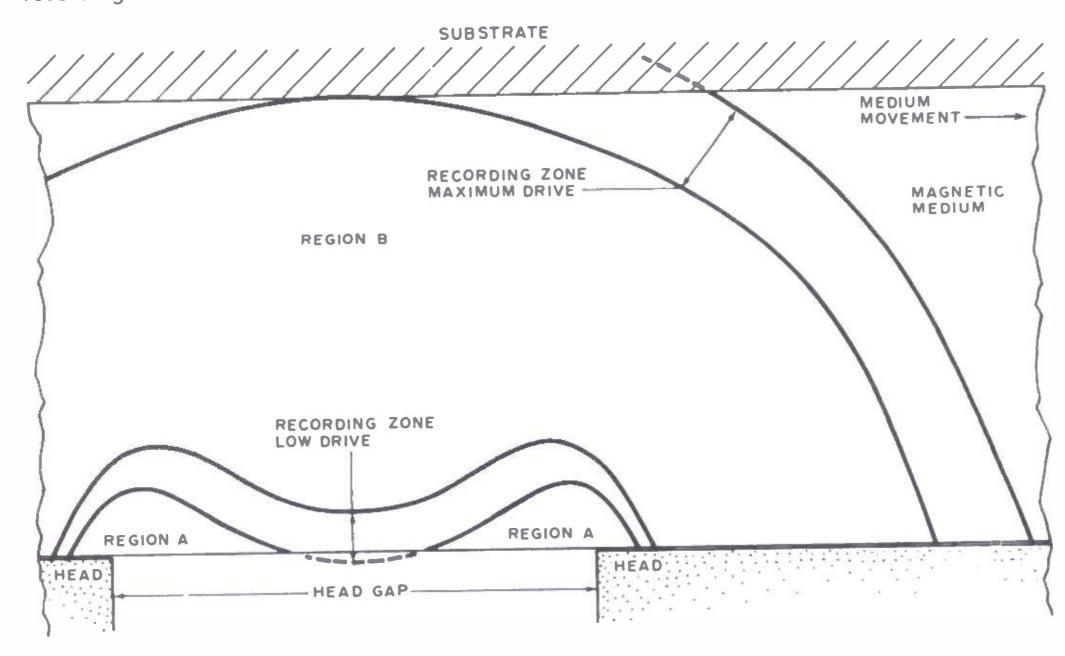

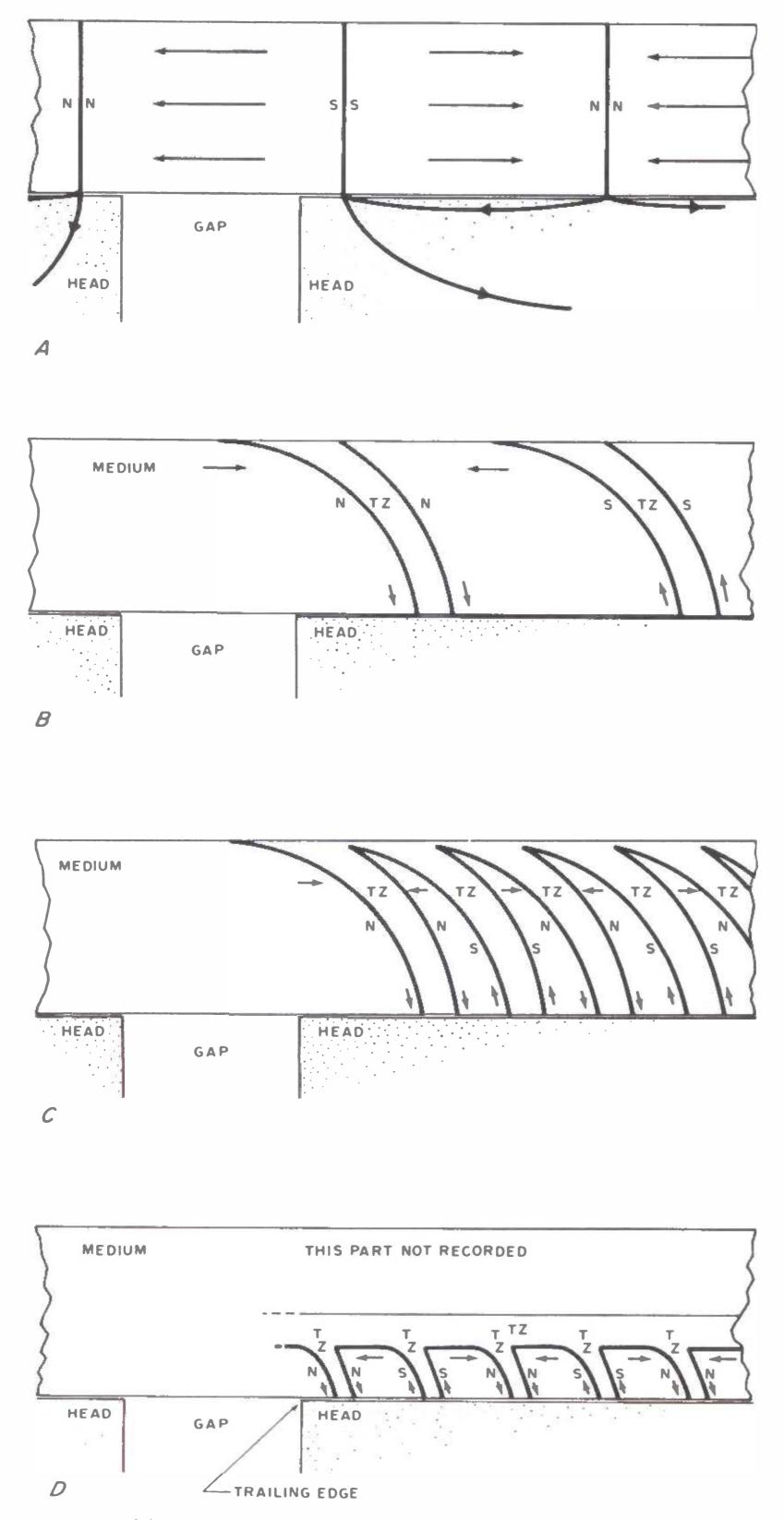

Lend me your Ears - Rice Magnetic Recording for Computers — Manly

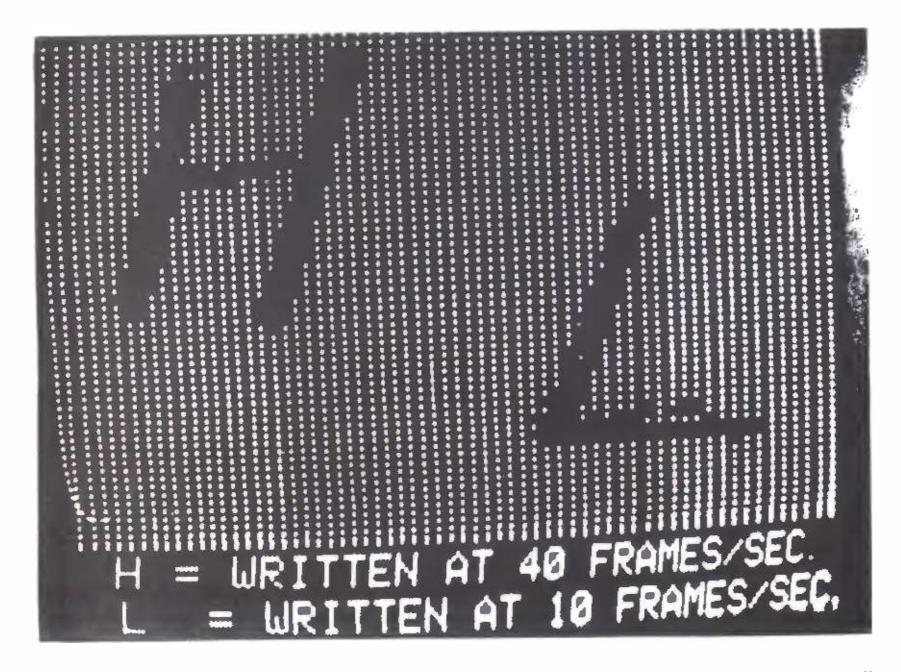

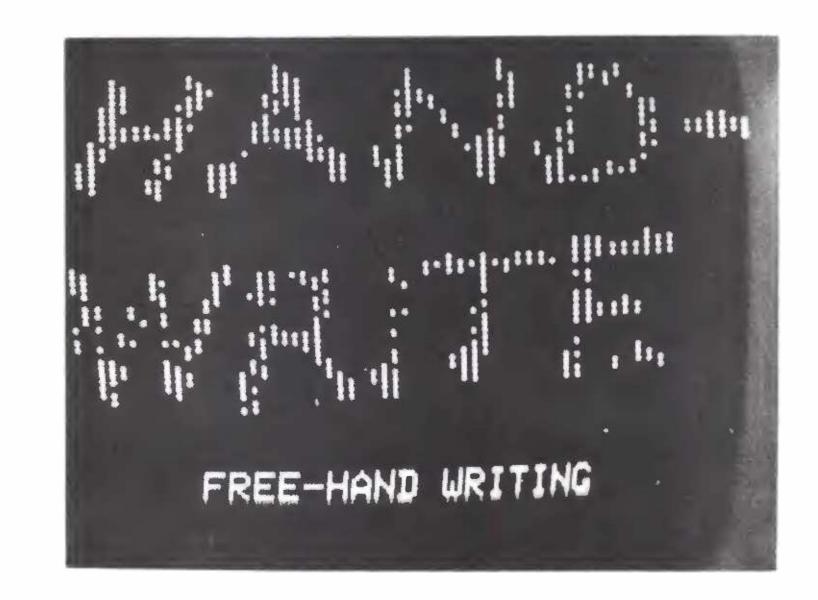

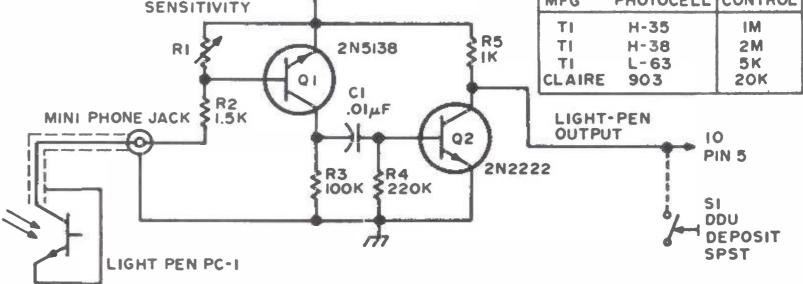

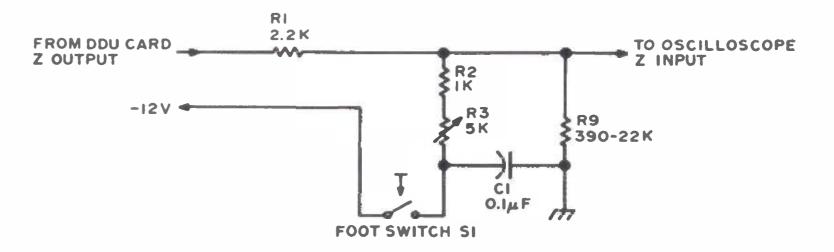

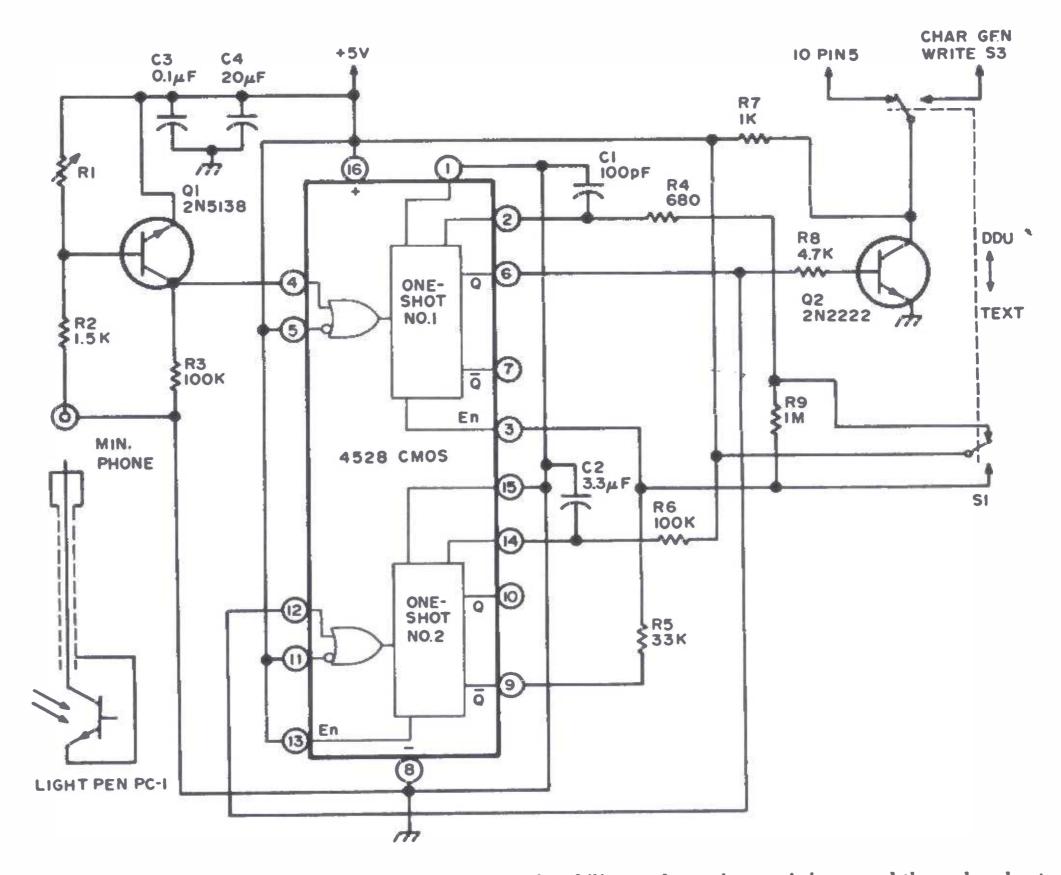

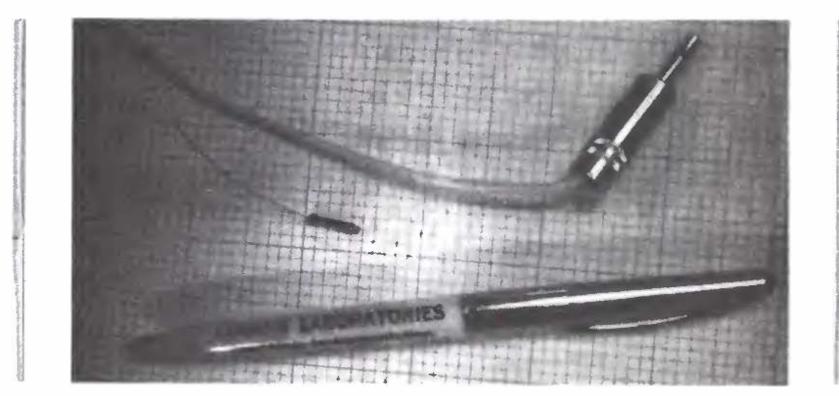

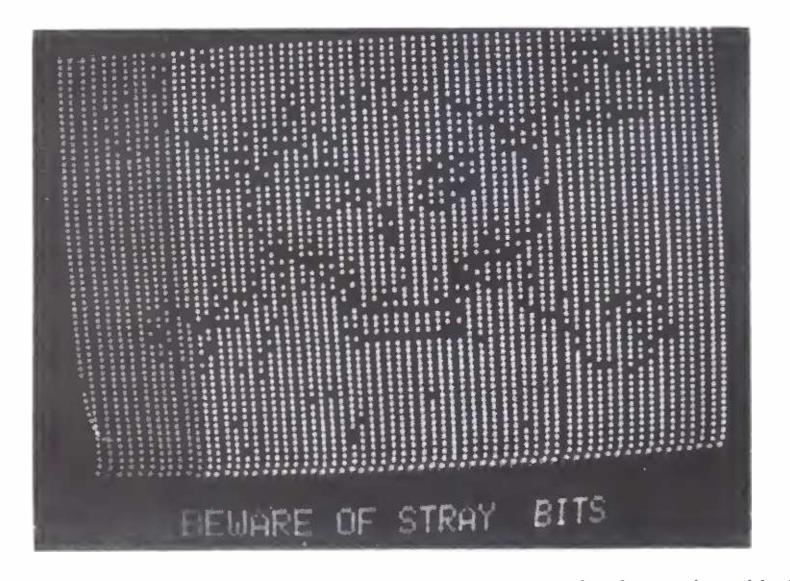

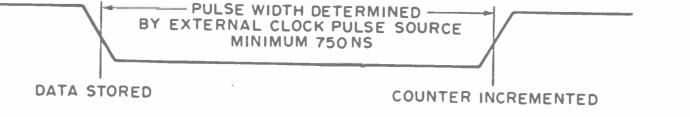

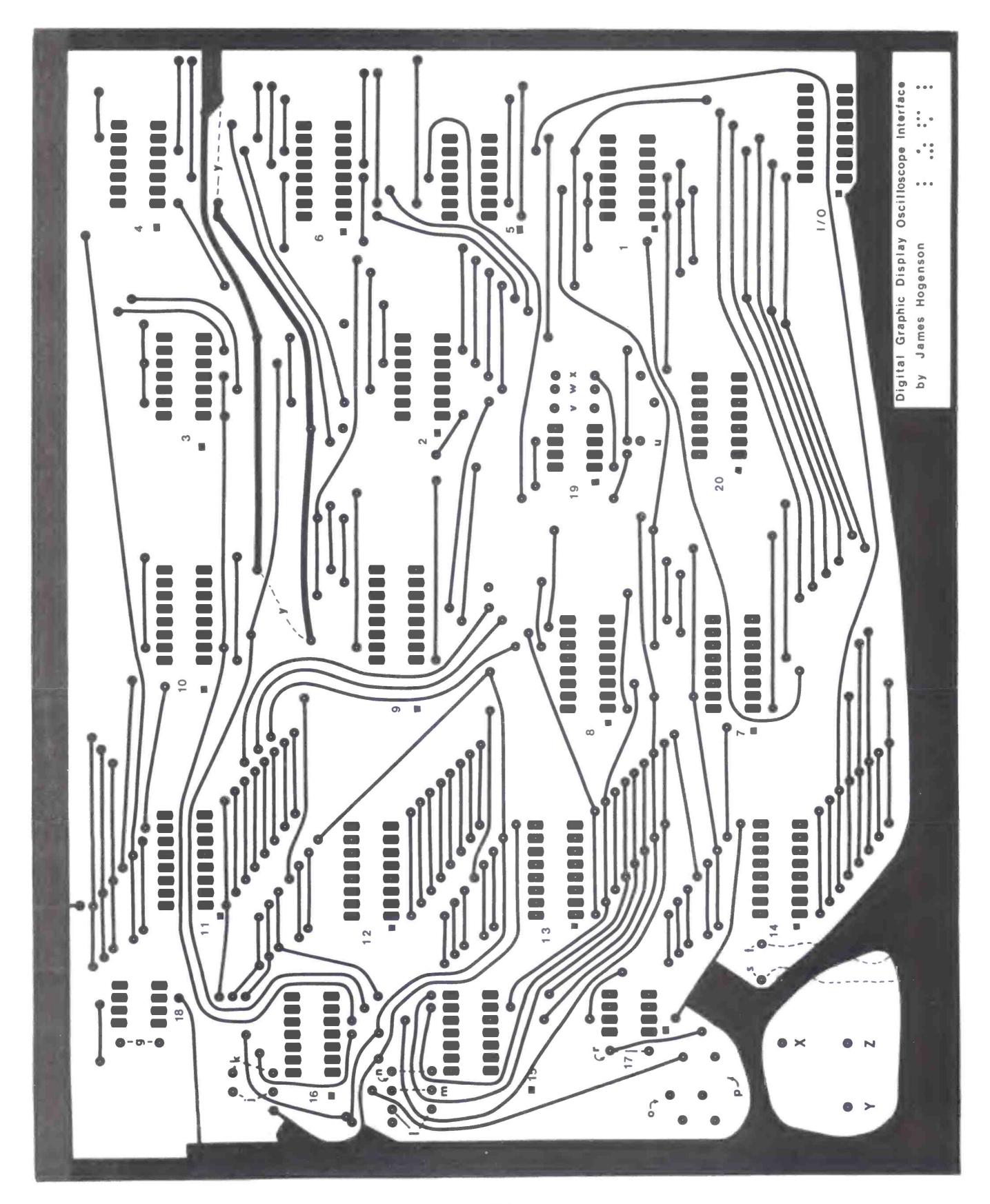

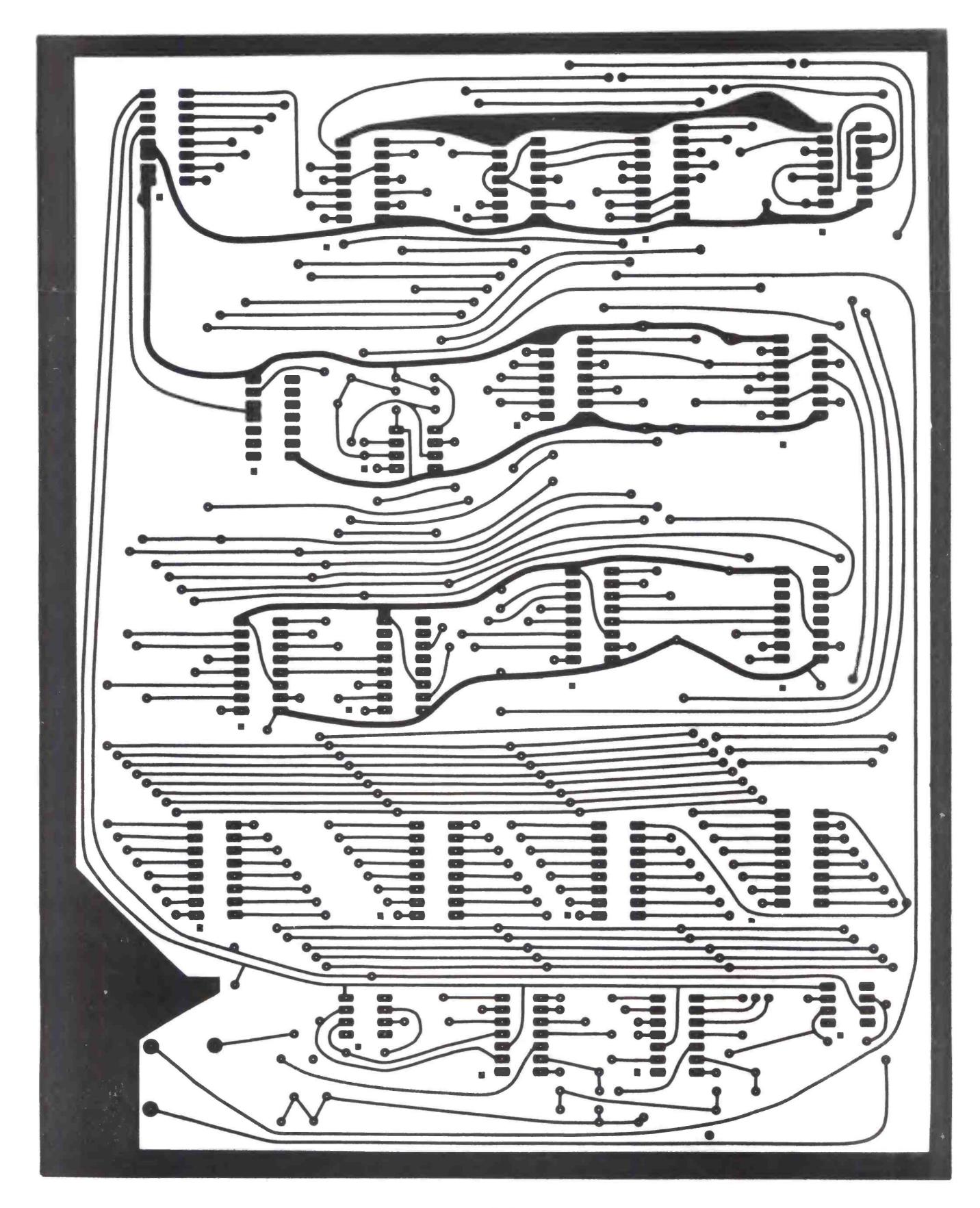

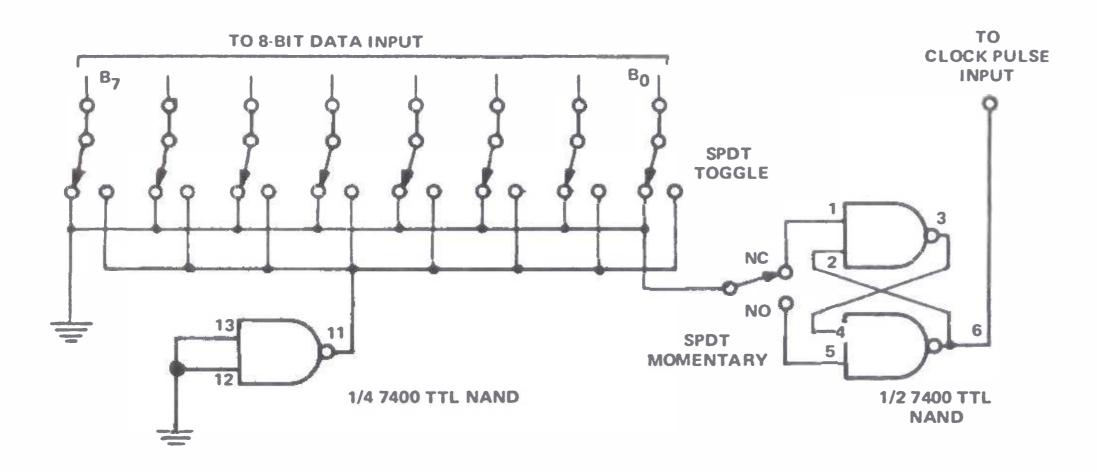

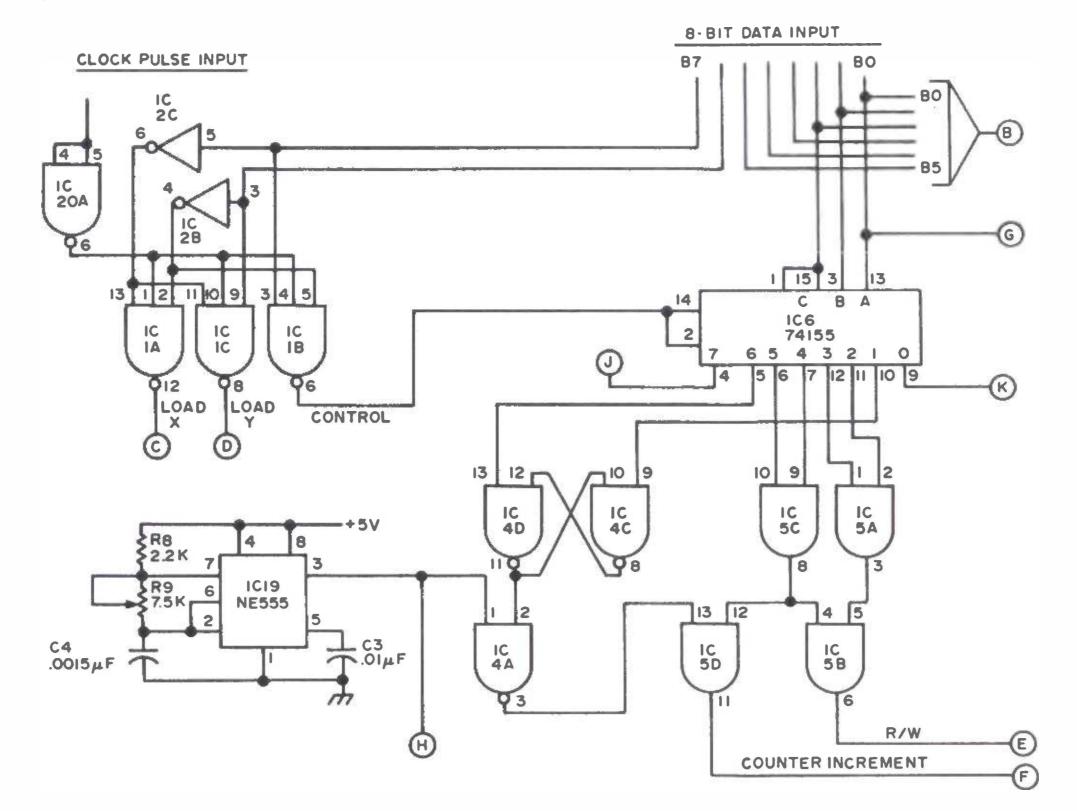

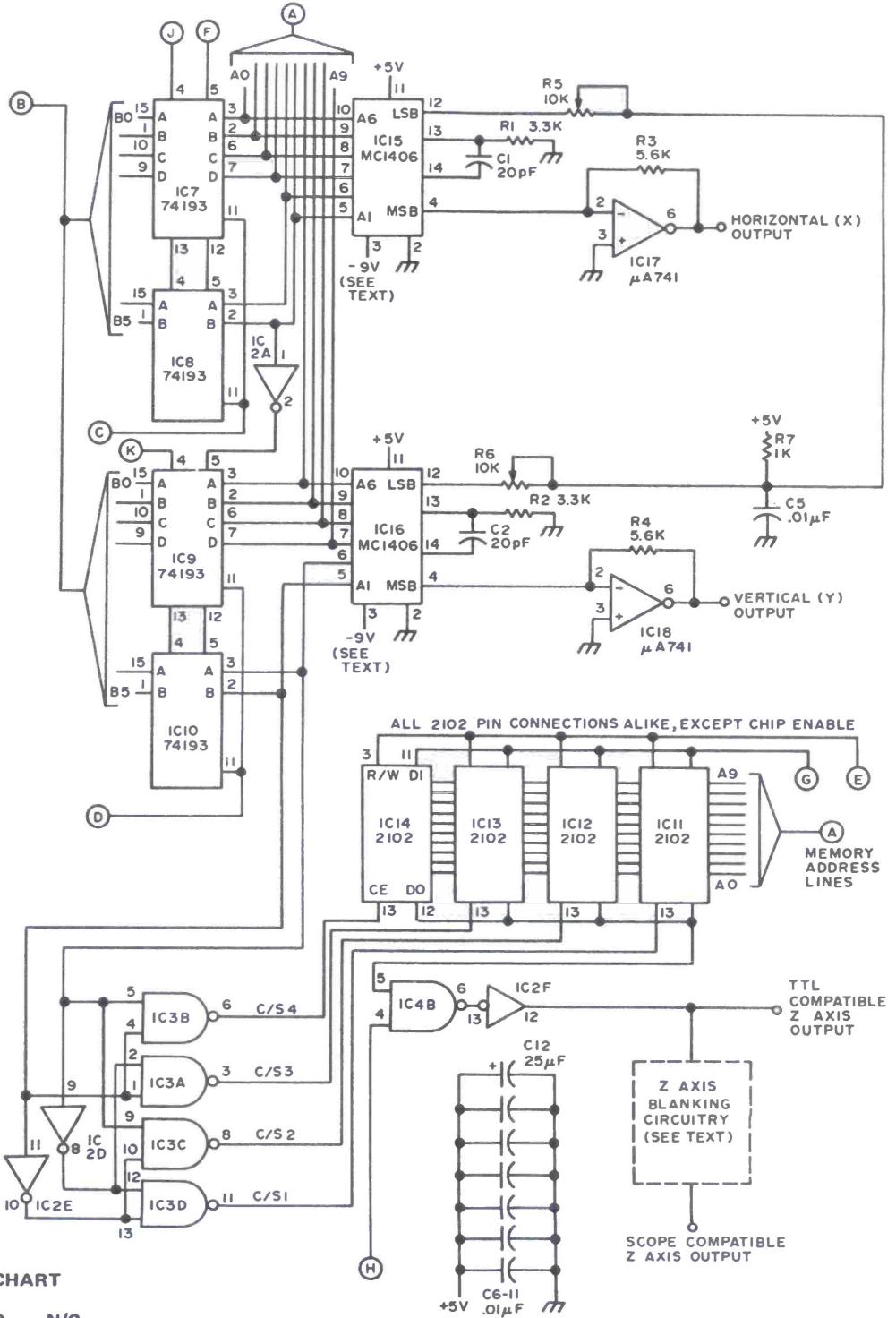

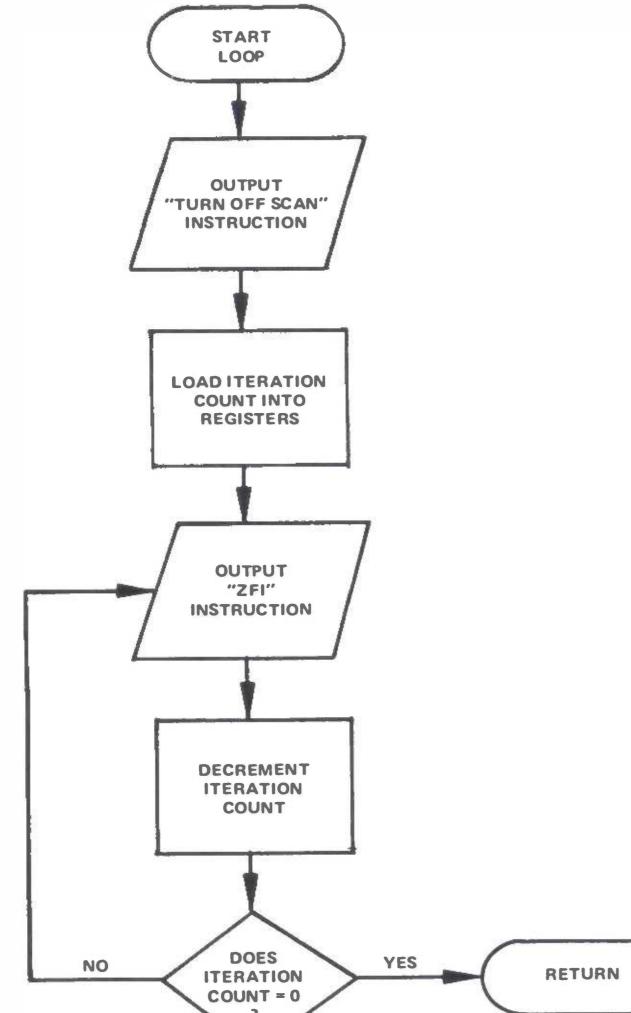

| Let There Be Light Pens — Loomis<br>Build an Oscilloscope Graphics Interface — Hogenson | 153<br>158 |

|-----------------------------------------------------------------------------------------|------------|

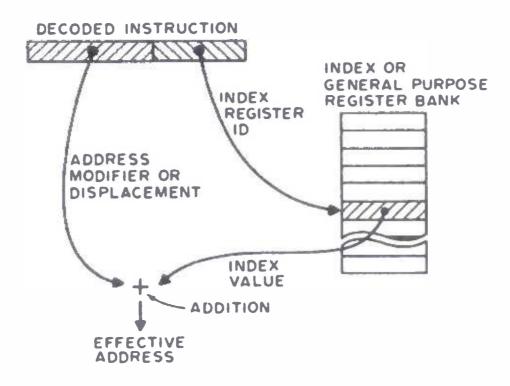

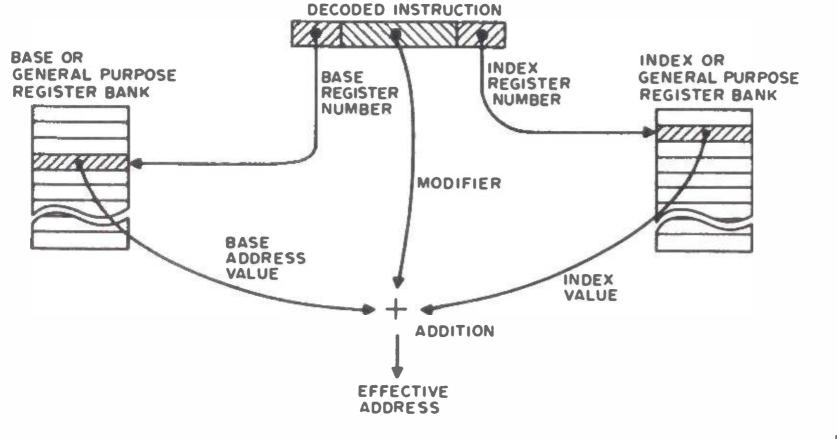

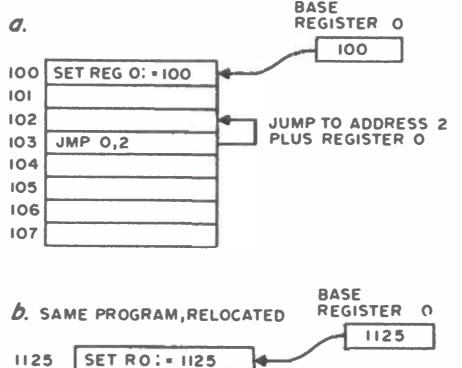

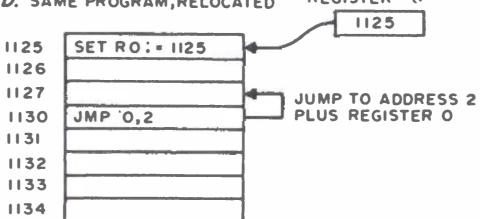

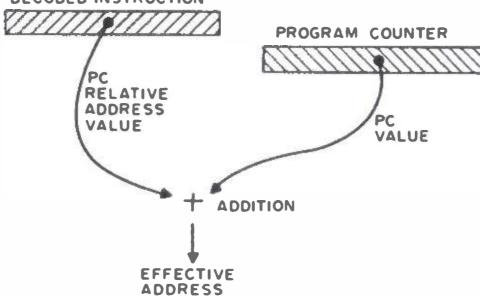

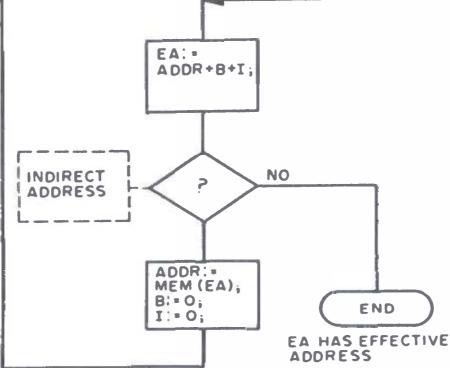

| An Introduction to Addressing Methods — Zarrella                                        | 169        |

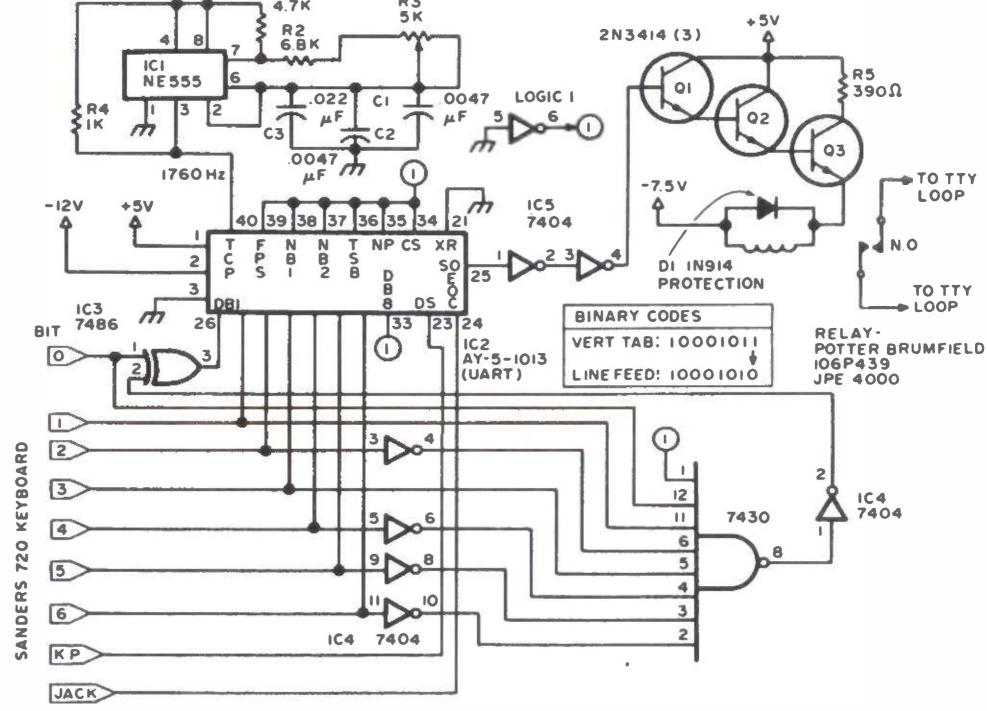

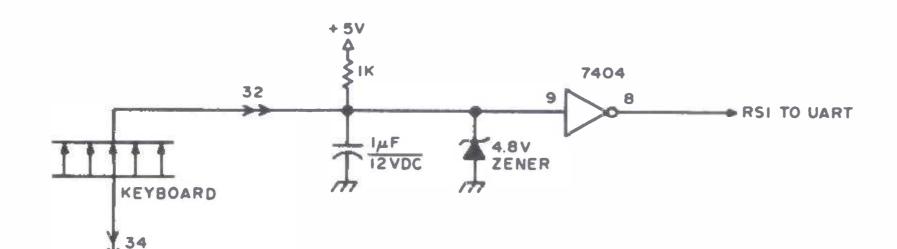

| Interface an ASCII Keyboard to a 60mA                                                   | 174        |

| TTY Loop — Cotton                                                                       |            |

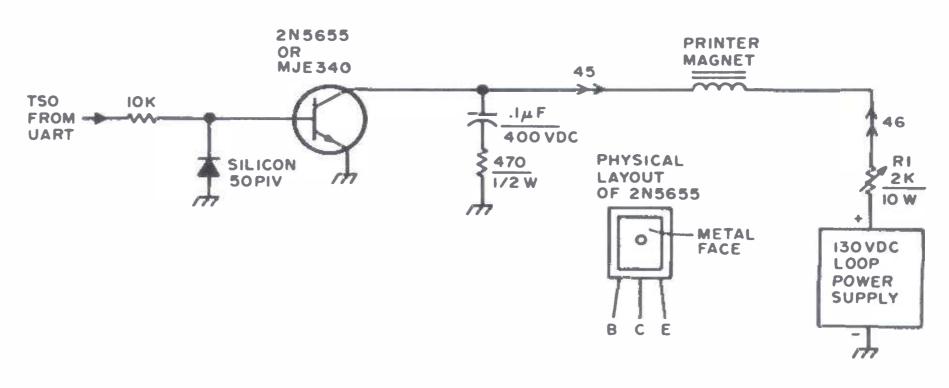

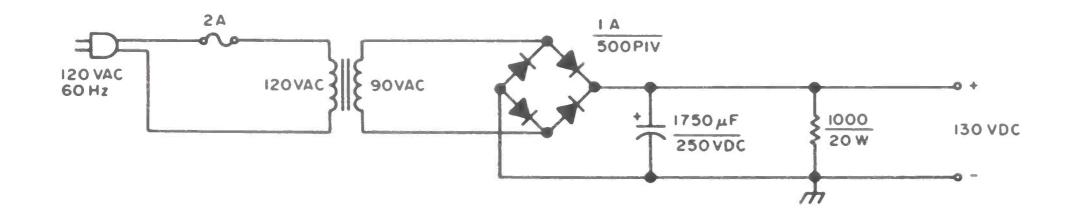

| Interfacing the 60 mA Current Loop — King                                               | 175        |

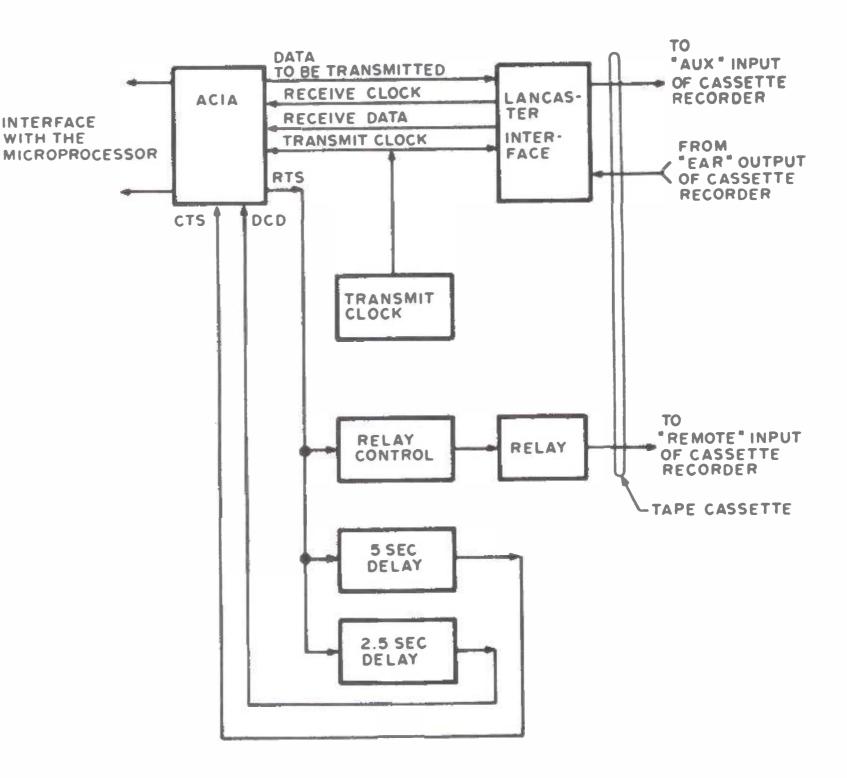

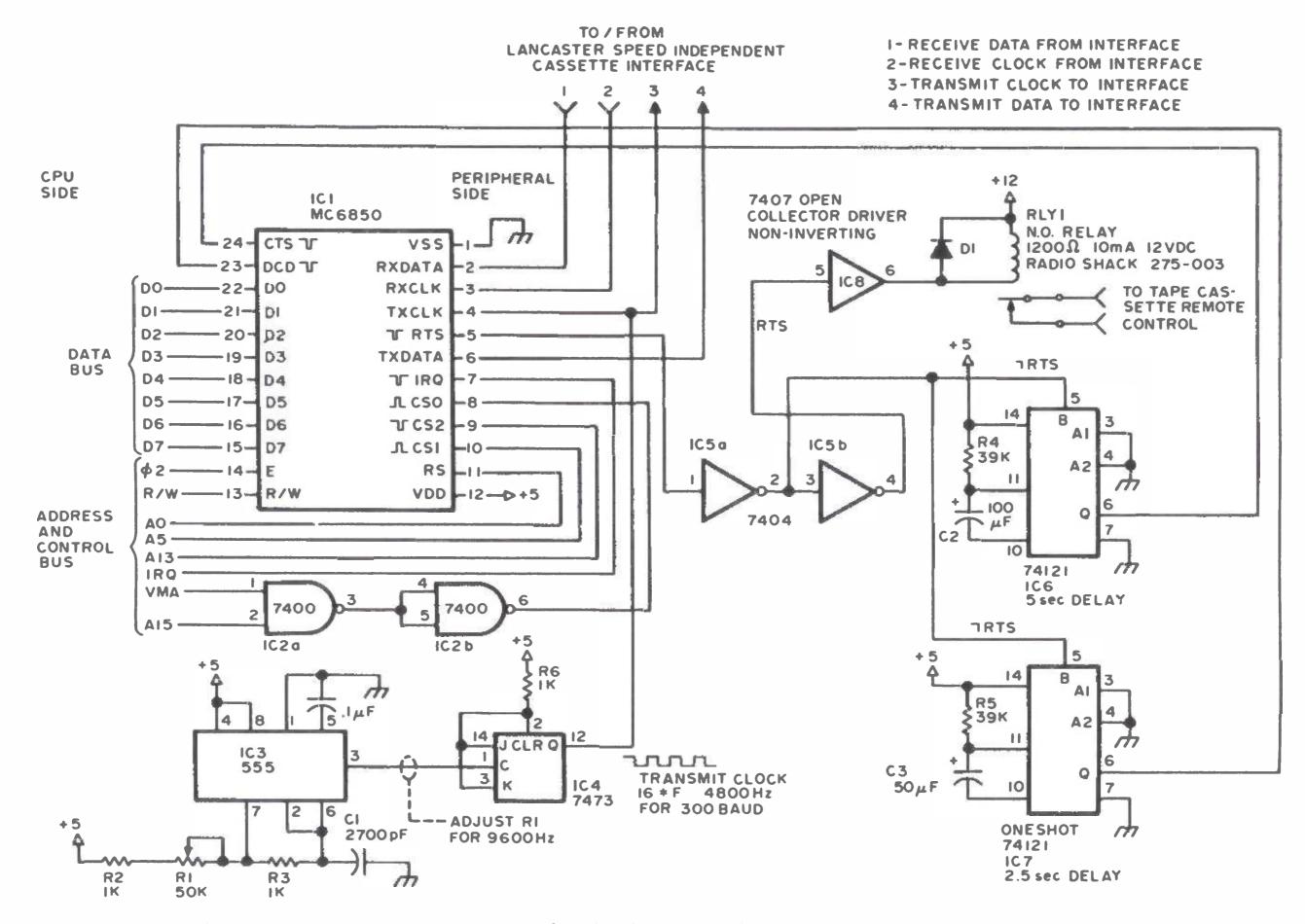

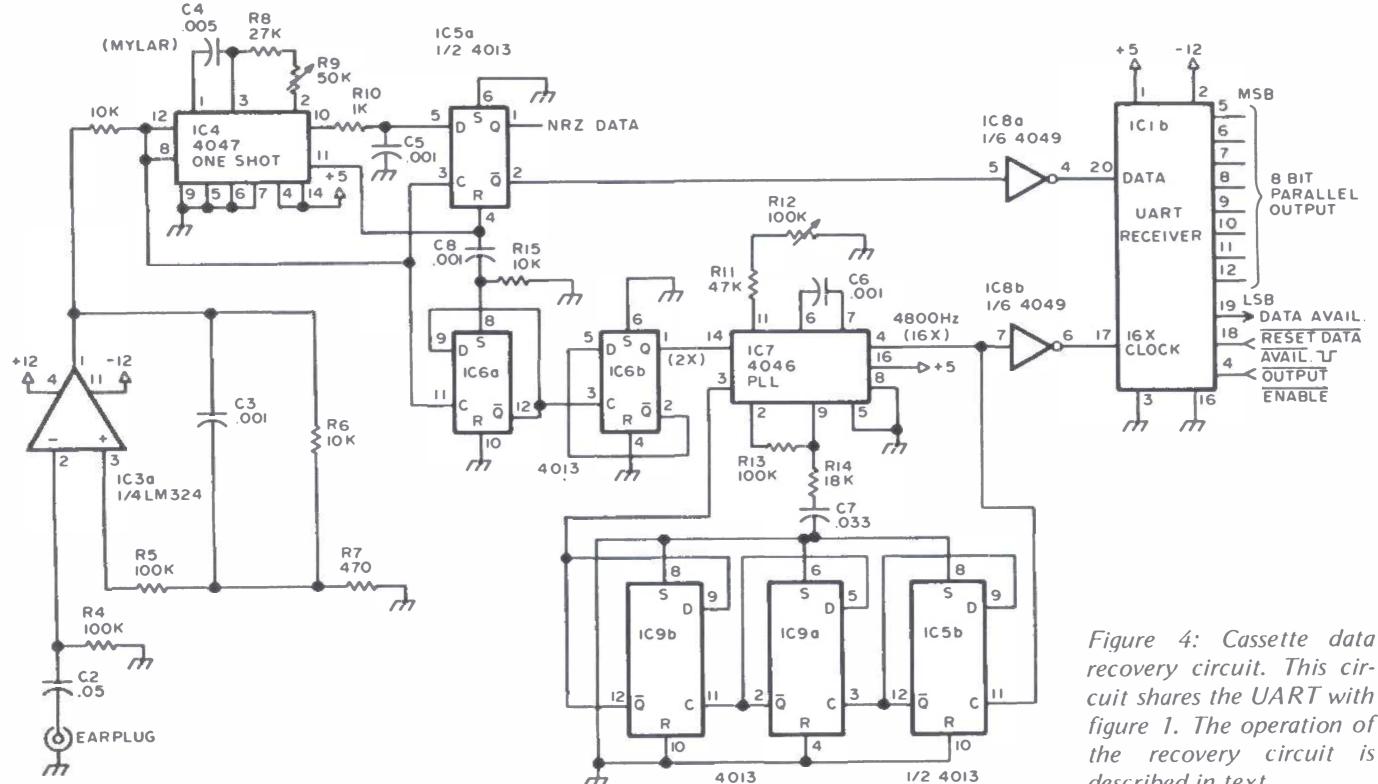

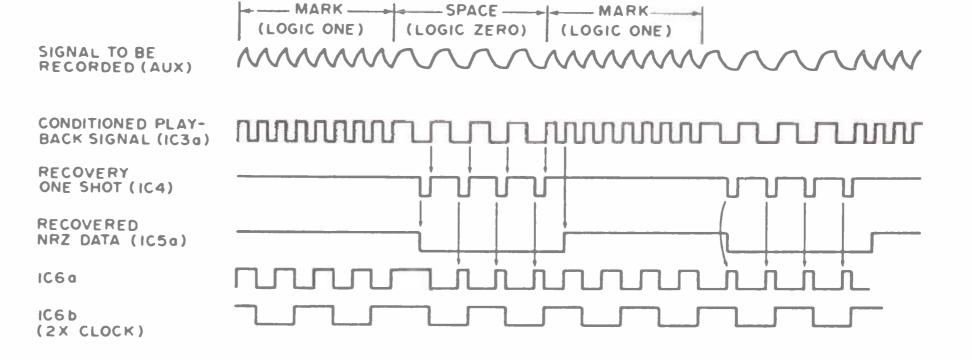

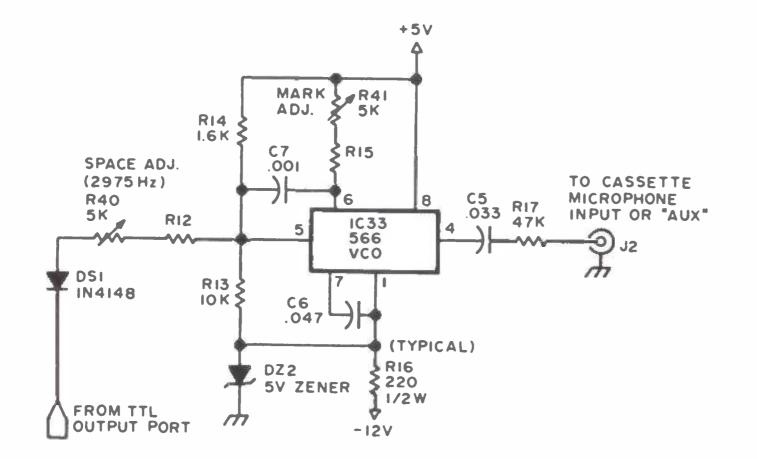

| The Complete Tape Cassette Interface — Hemenway                                         | 177        |

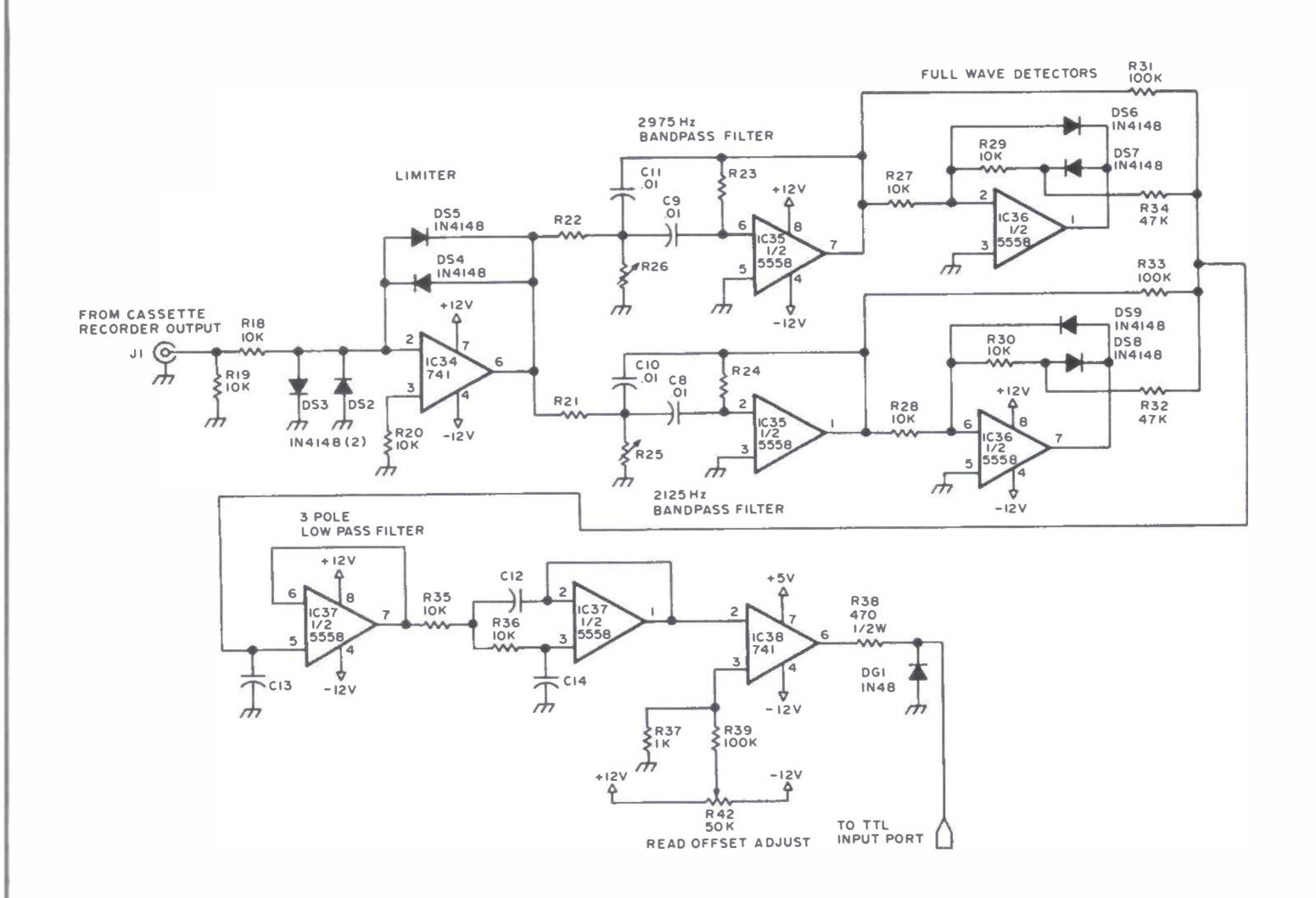

| Digital Data on Cassette Recorders — Mauch                                              | 184        |

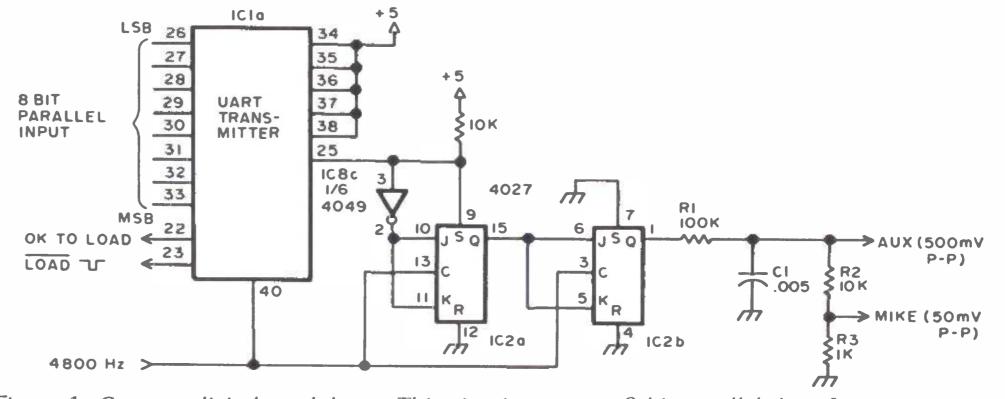

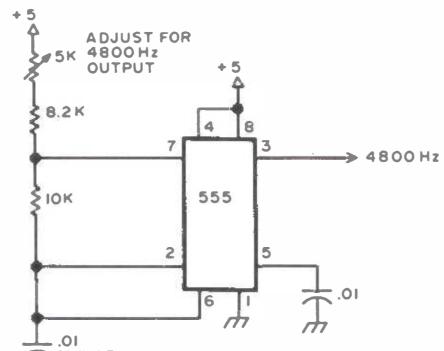

| Build a Fast Cassette Interface — Suding                                                | 190        |

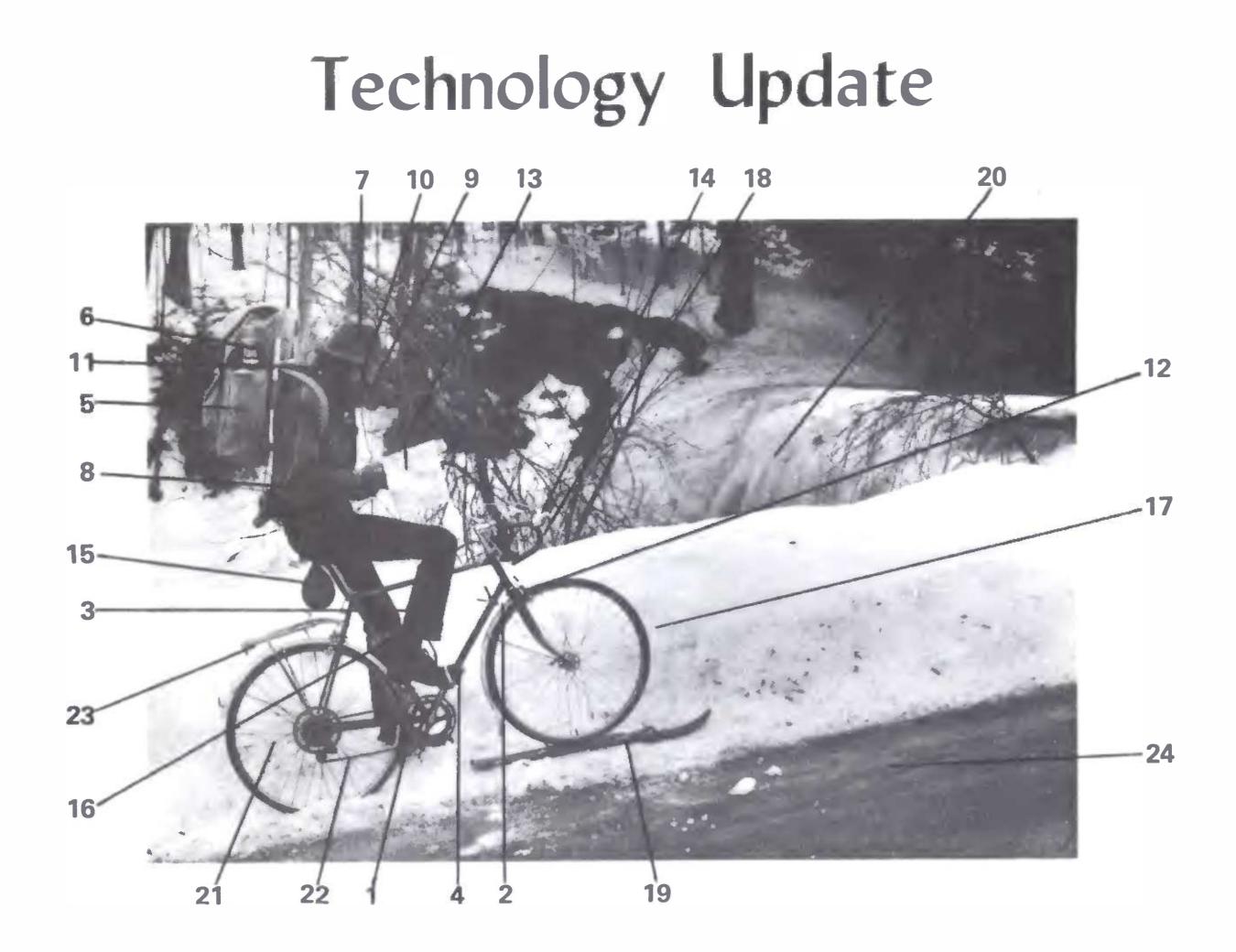

| Technology Update                                                                       | 197        |

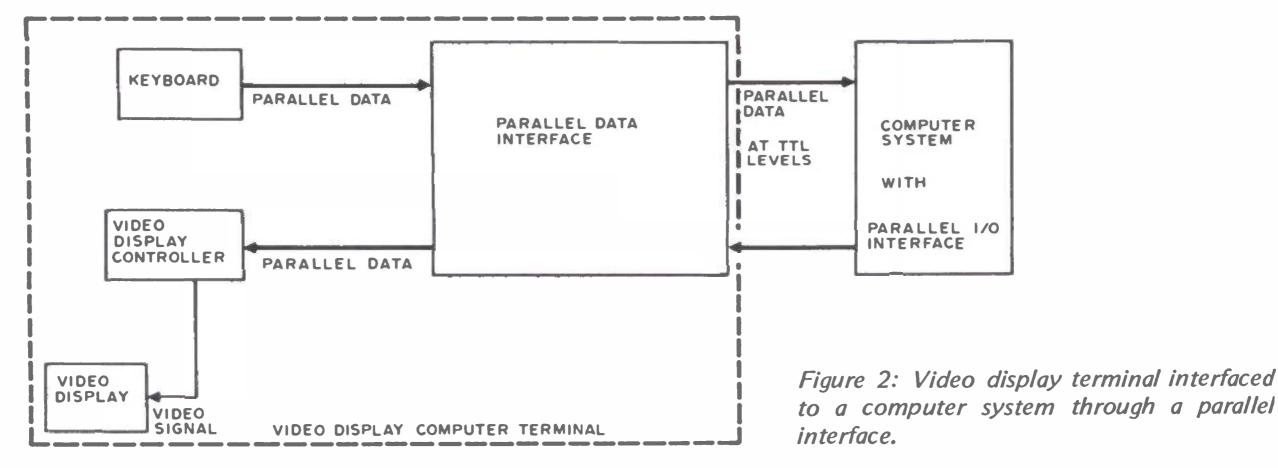

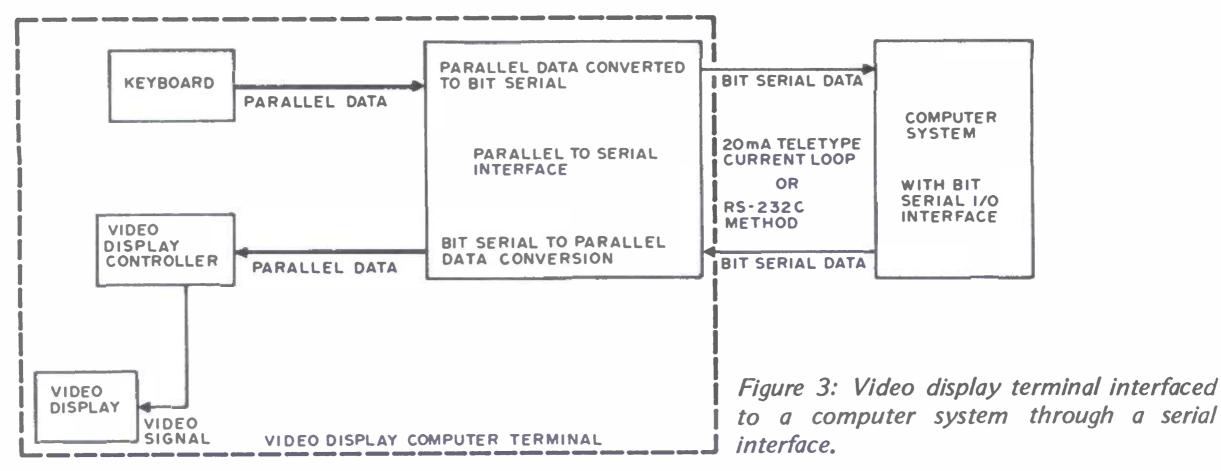

| What's In a Video Display Terminal? — Walters                                           | 198        |

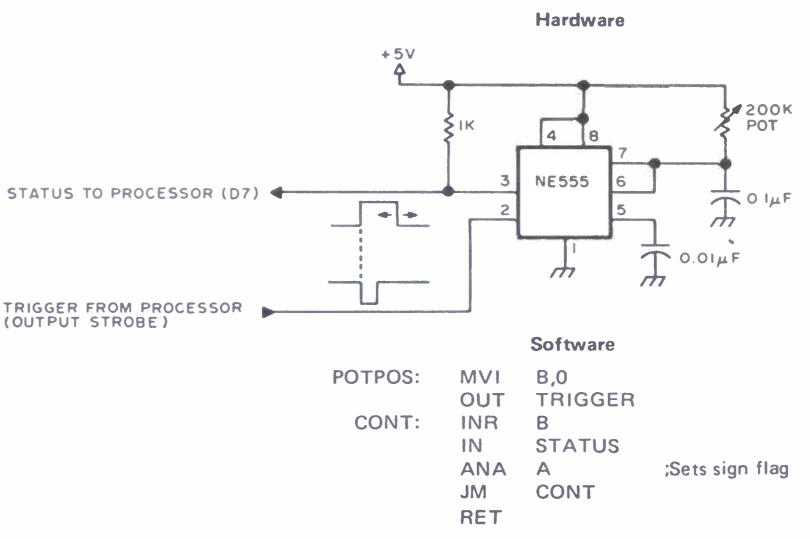

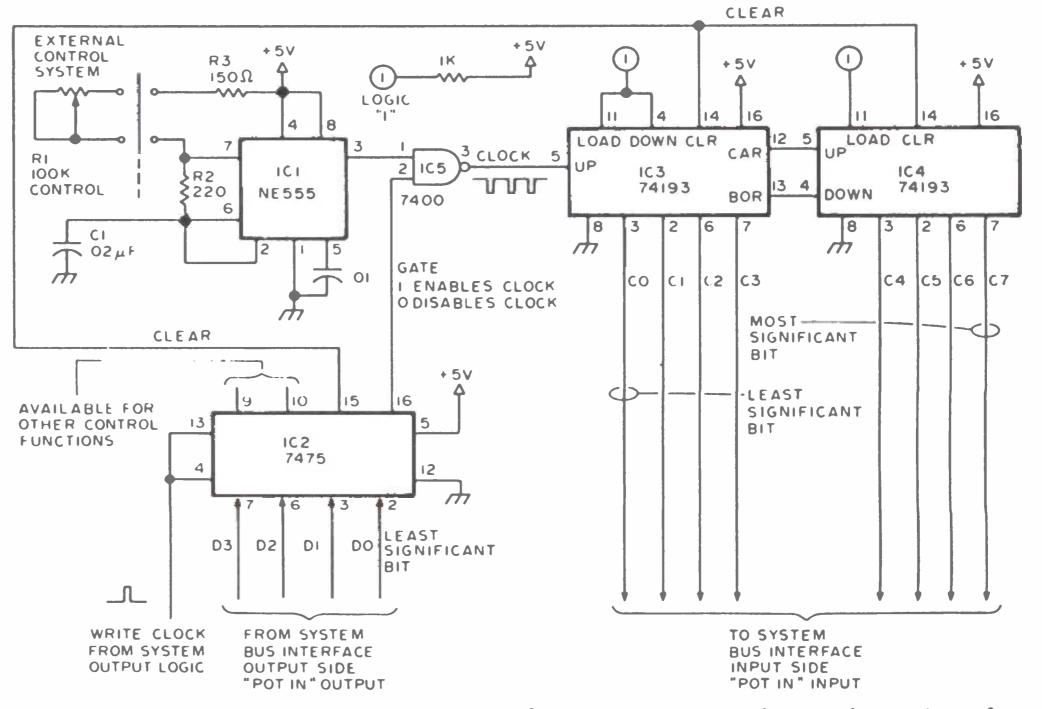

| Pot Position Digitizing Idea — Schulein                                                 | 199        |

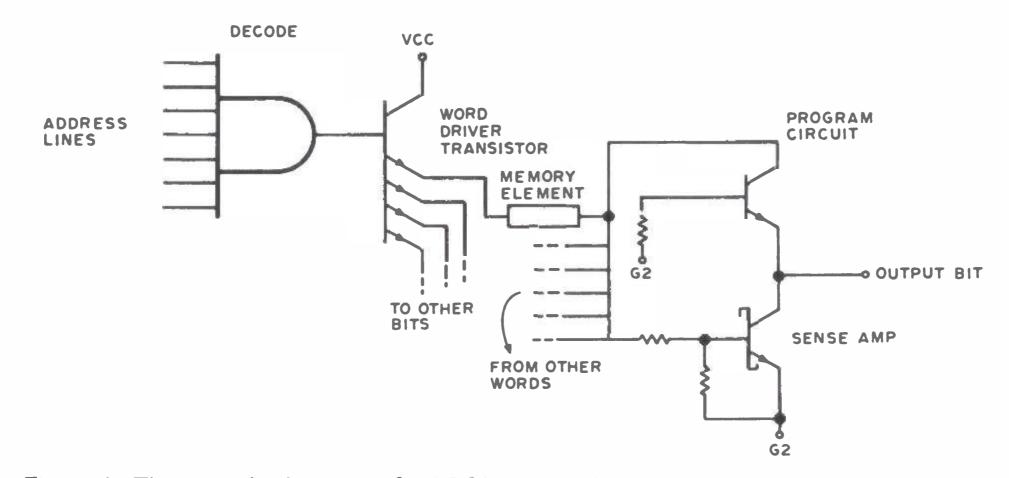

| Read Only Memories in Microcomputer Memory                                              | 200        |

| Address Space — Eichbauer                                                               |            |

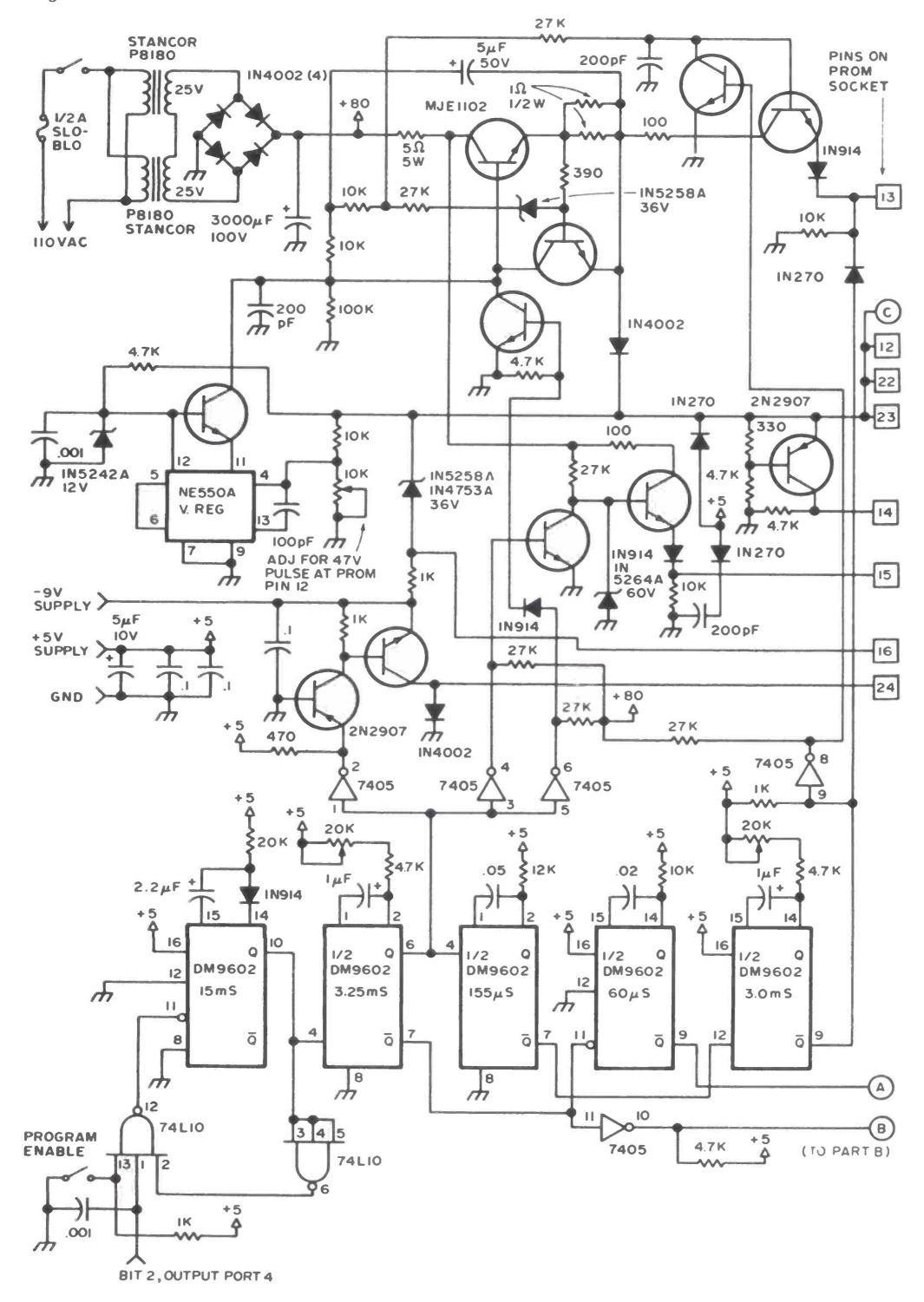

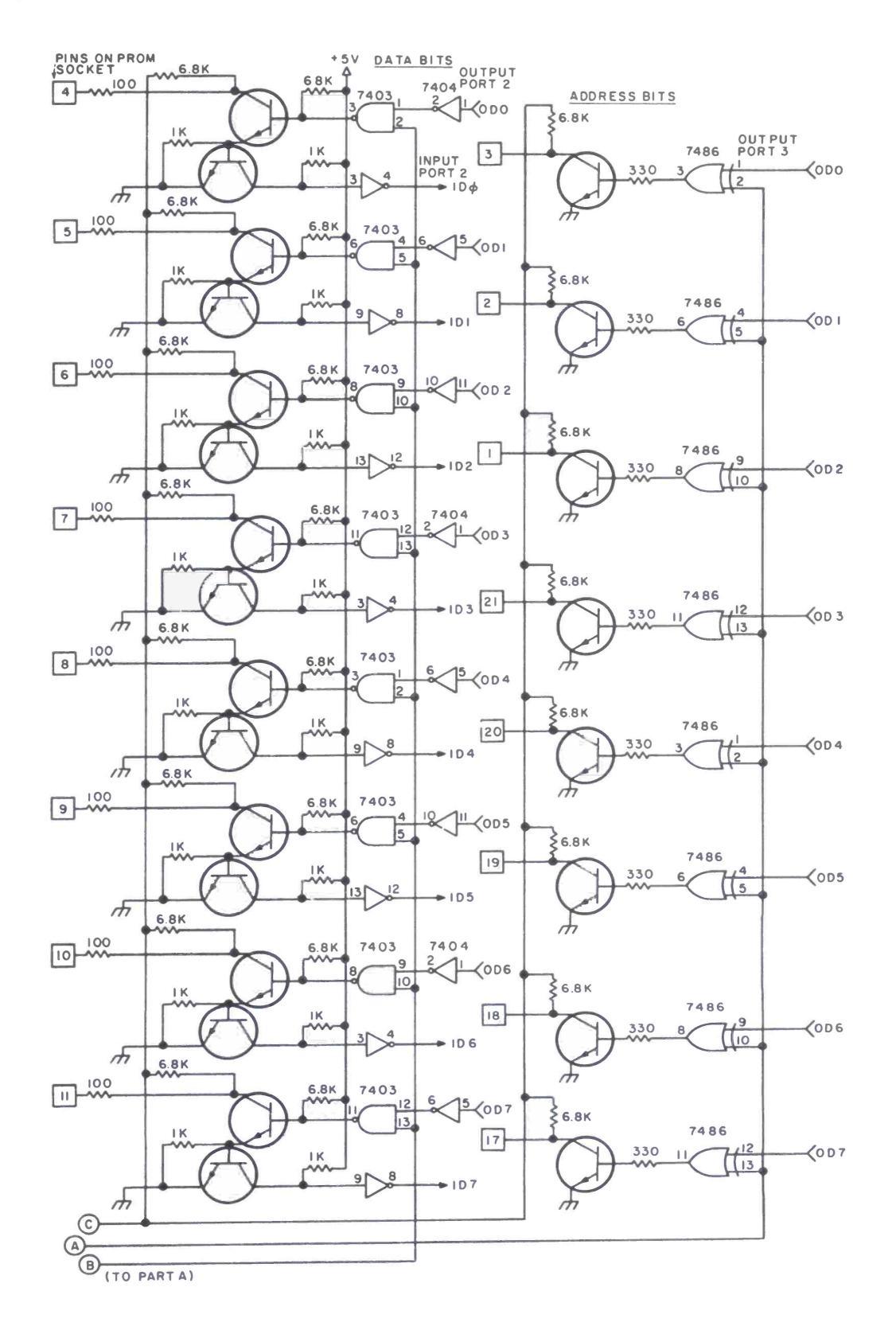

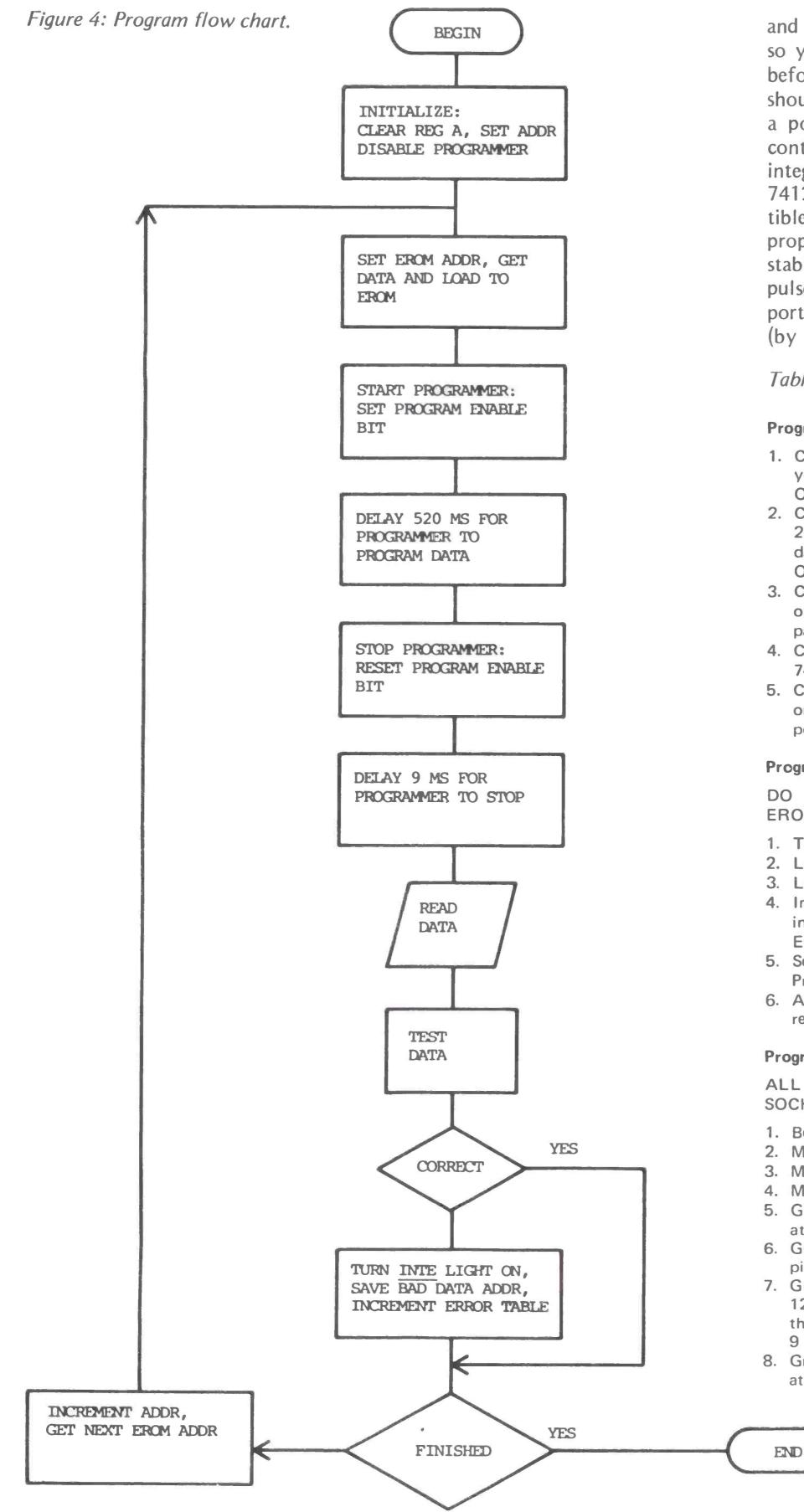

| More Information on PROMs — Smith                                                       | 203        |

| Getting Input from Joysticks and Slide Pots — Helmers                                   | 210        |

|                                                                                         |            |

| magnotio nooonani; | 9 |  | · · · · · · · · · · · · · · · · · · · |

|--------------------|---|--|---------------------------------------|

|--------------------|---|--|---------------------------------------|

### **COMPUTER KITS**

| Assembling an Altair 8800 — Zarrella          |

|-----------------------------------------------|

| Build a 6800 System With This Kit — Kay       |

| More on the SWTPC 6800 System — Kay           |

| The New Altair 680 — Vice                     |

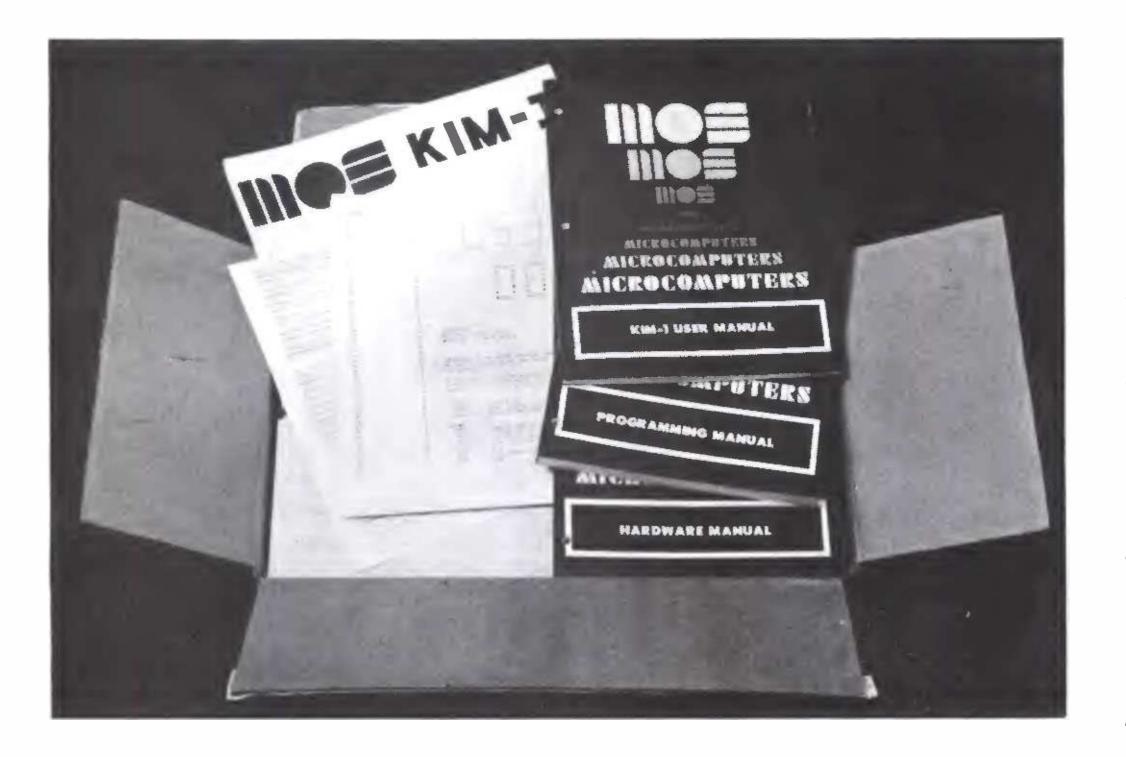

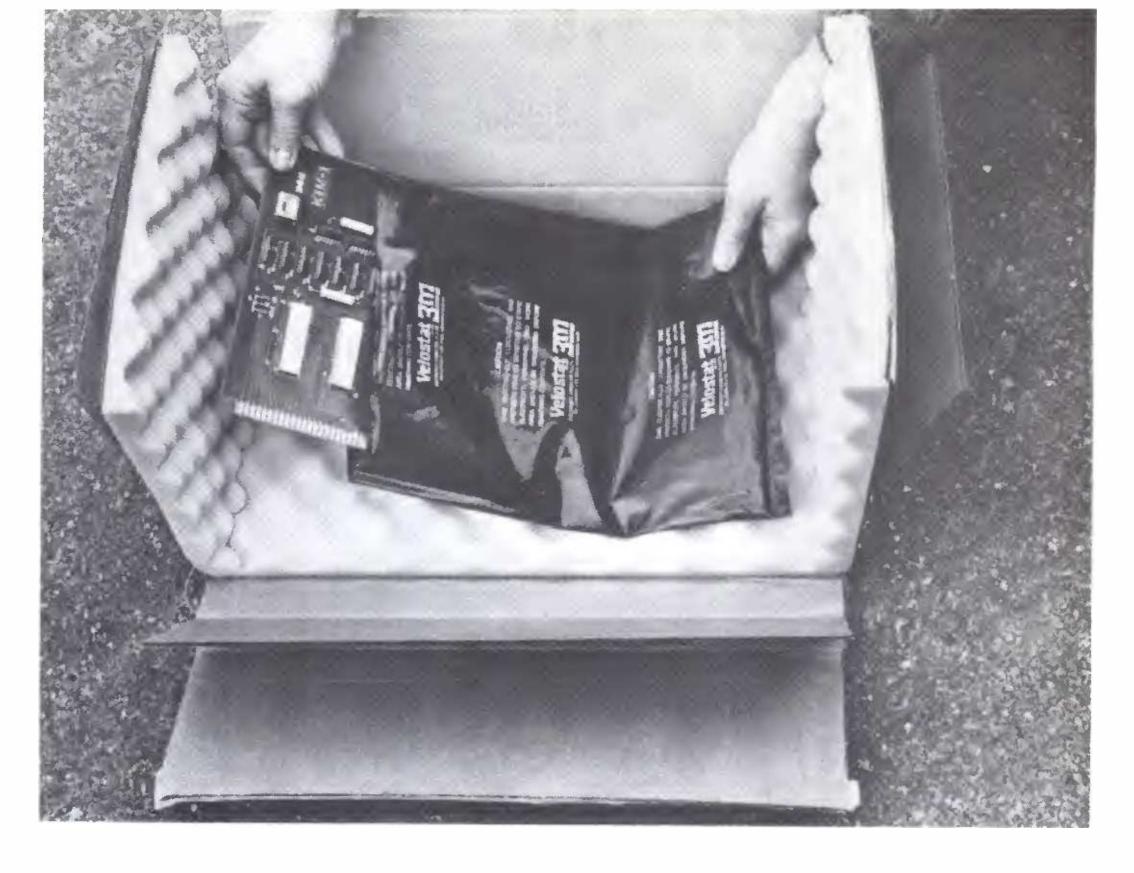

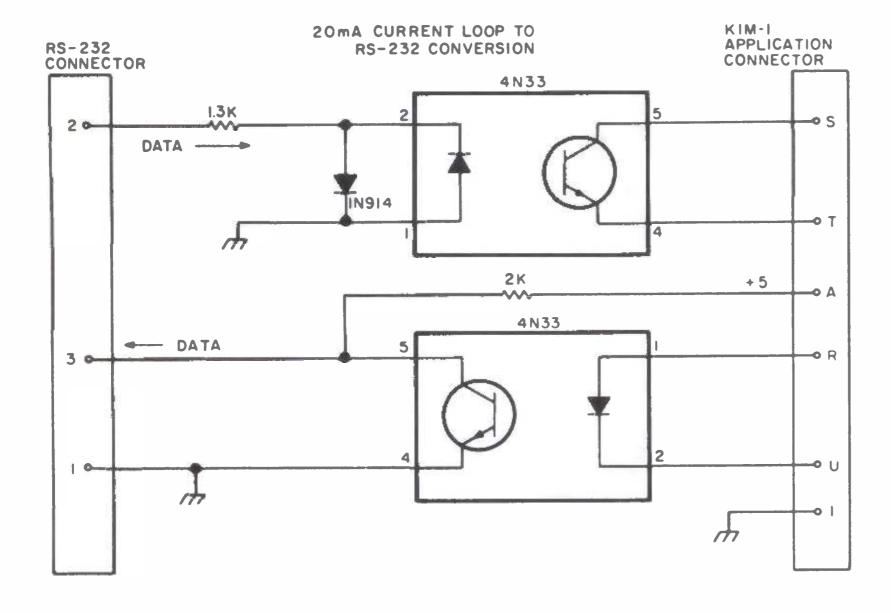

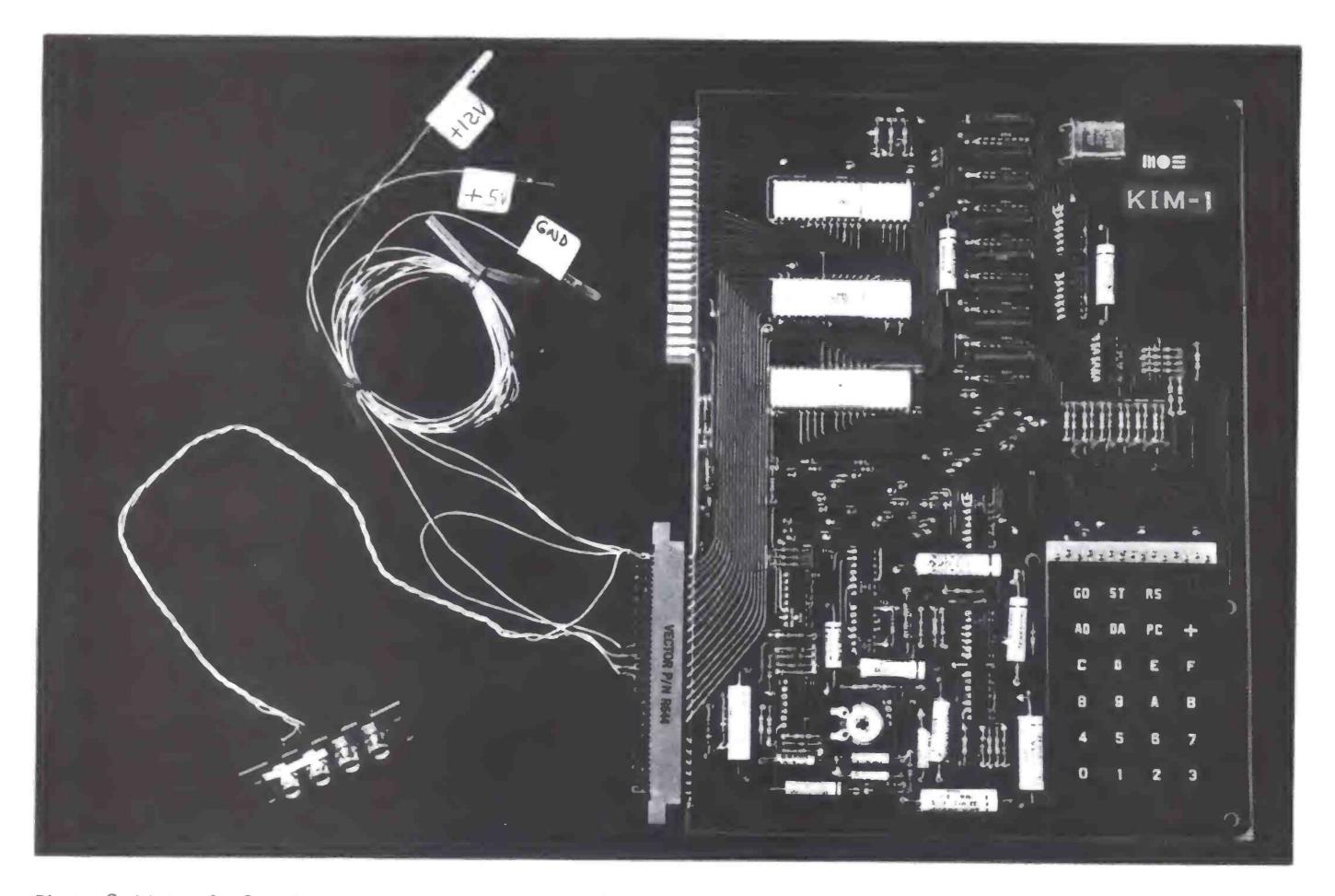

| A Date With KIM — Simpson                     |

| True Confessions: How I Relate to KIM — Gupta |

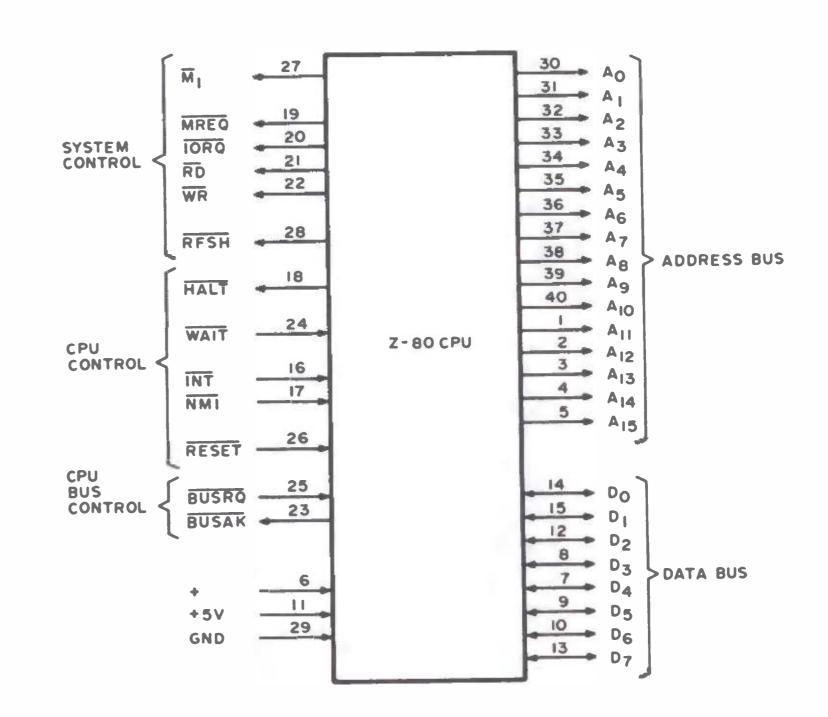

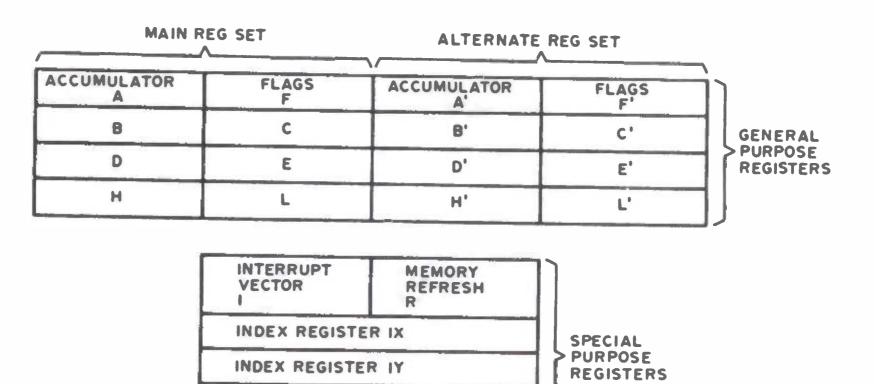

| Zilog Z80 — Hashizume                         |

| The Digital Equipment LSI-11 — Baker          |

| Cromemco TV Dazzler                           |

#### HARDWARE

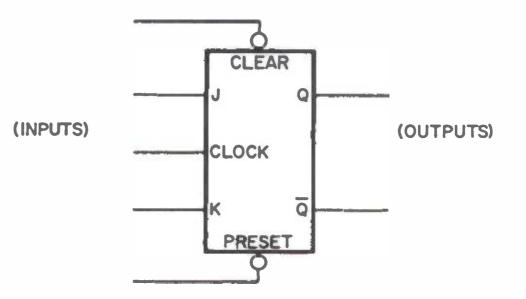

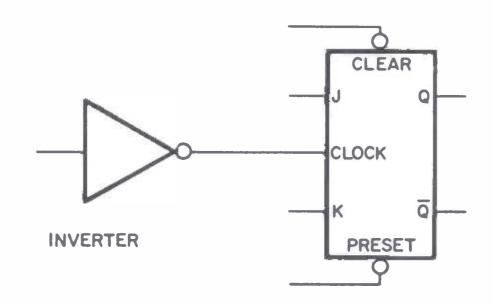

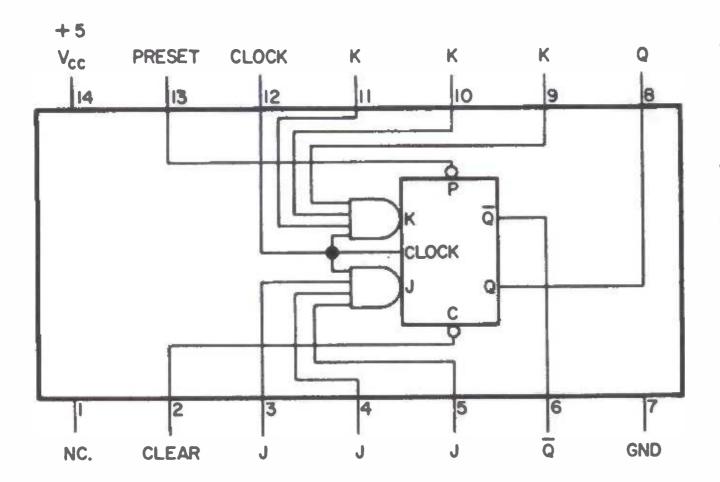

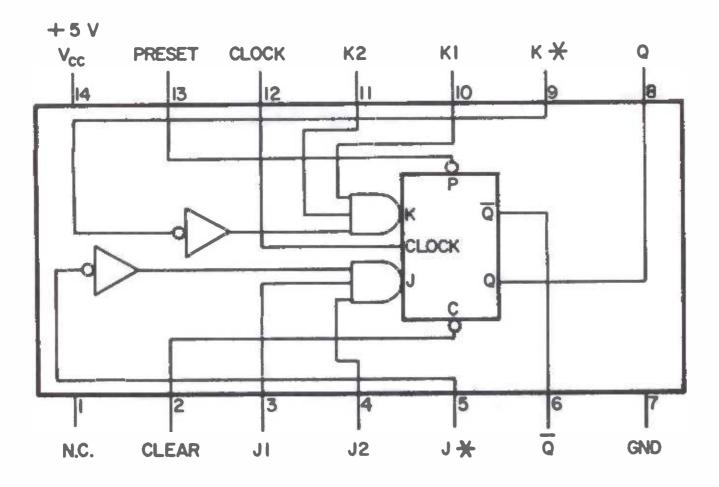

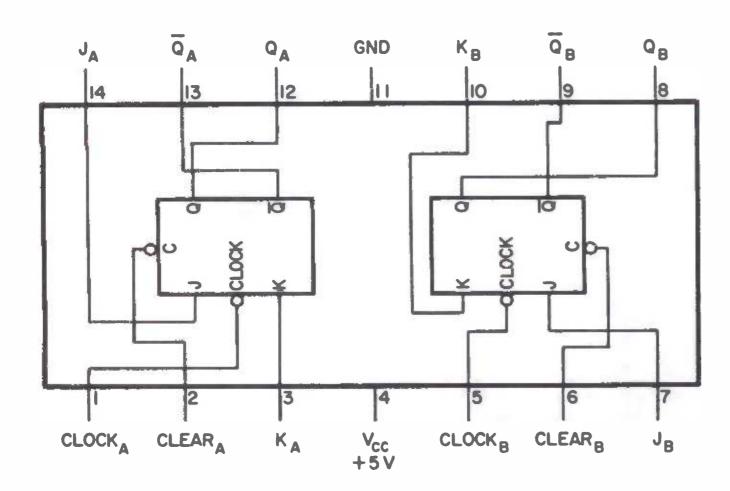

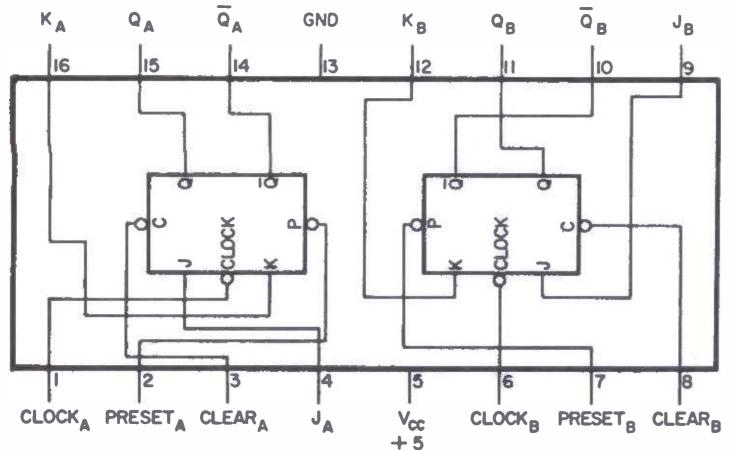

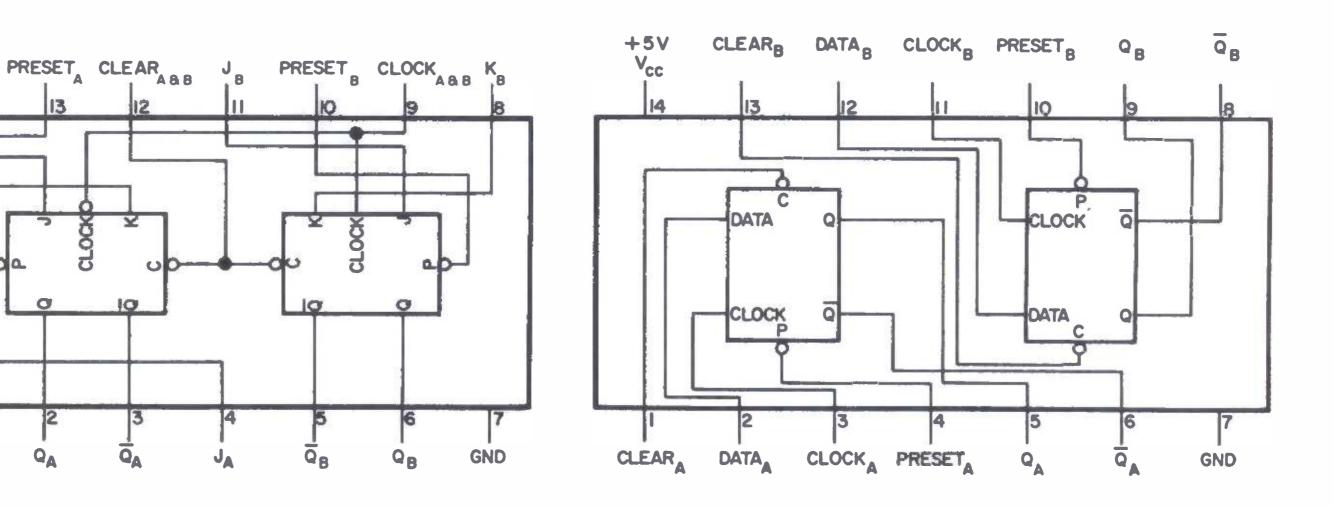

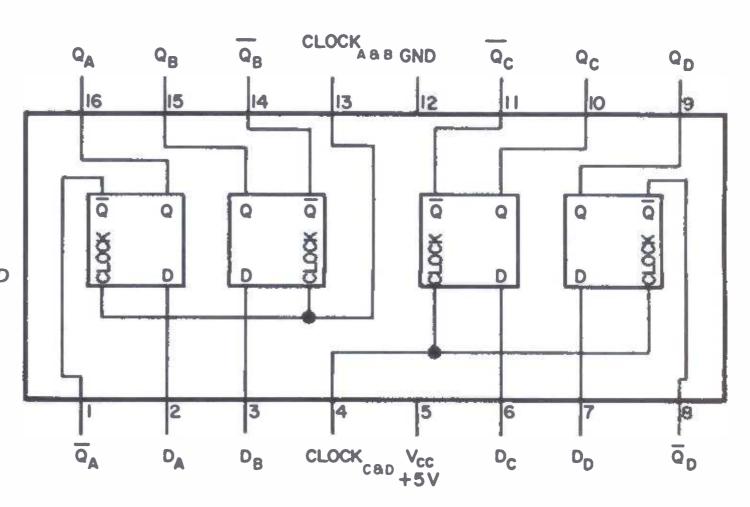

| Flip Flops Exposed — Browning             | 98  |

|-------------------------------------------|-----|

| Recycling Used ICs — Mikkelsen            | 102 |

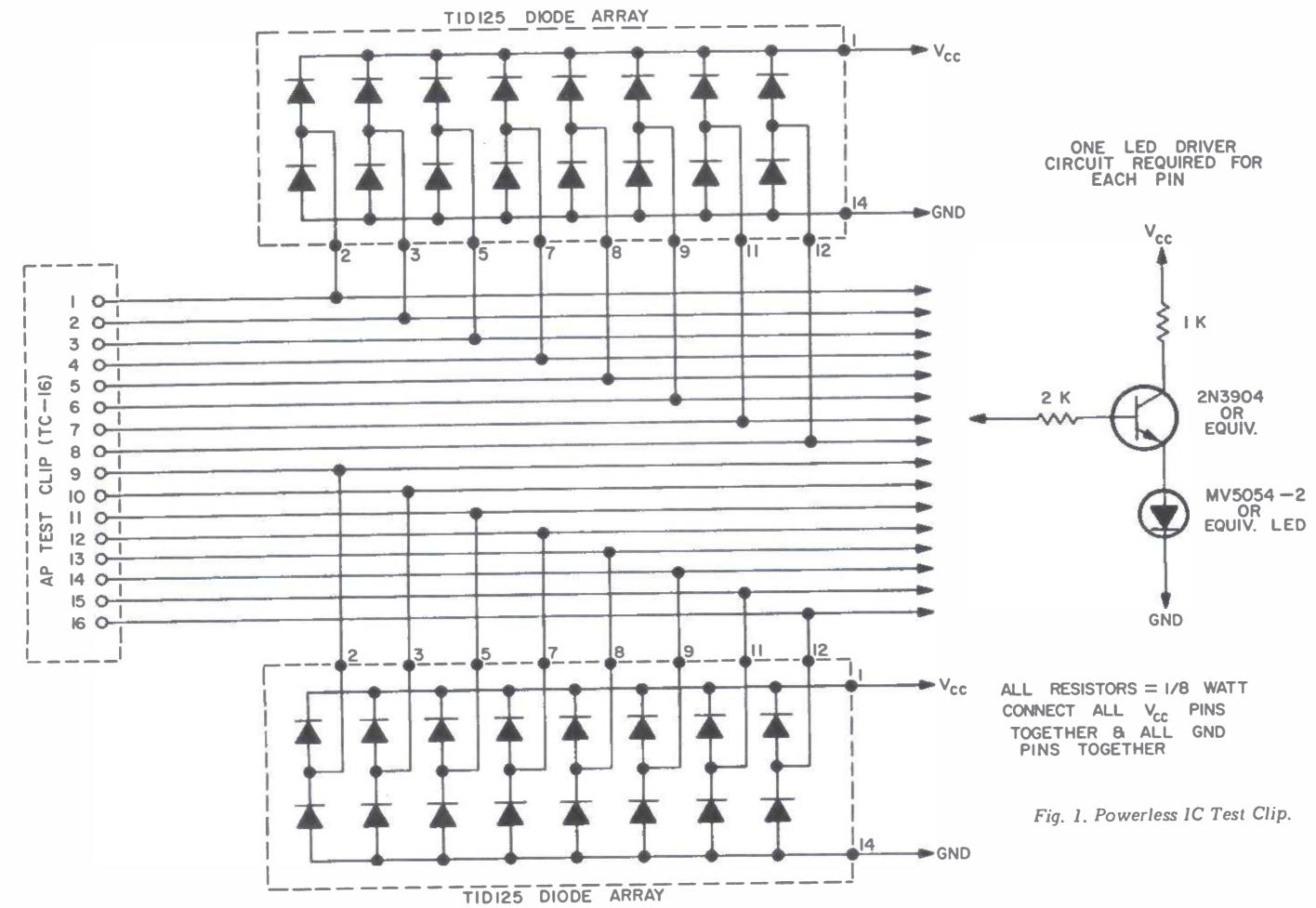

| Powerless IC Test Clip — Errico and Baker | 104 |

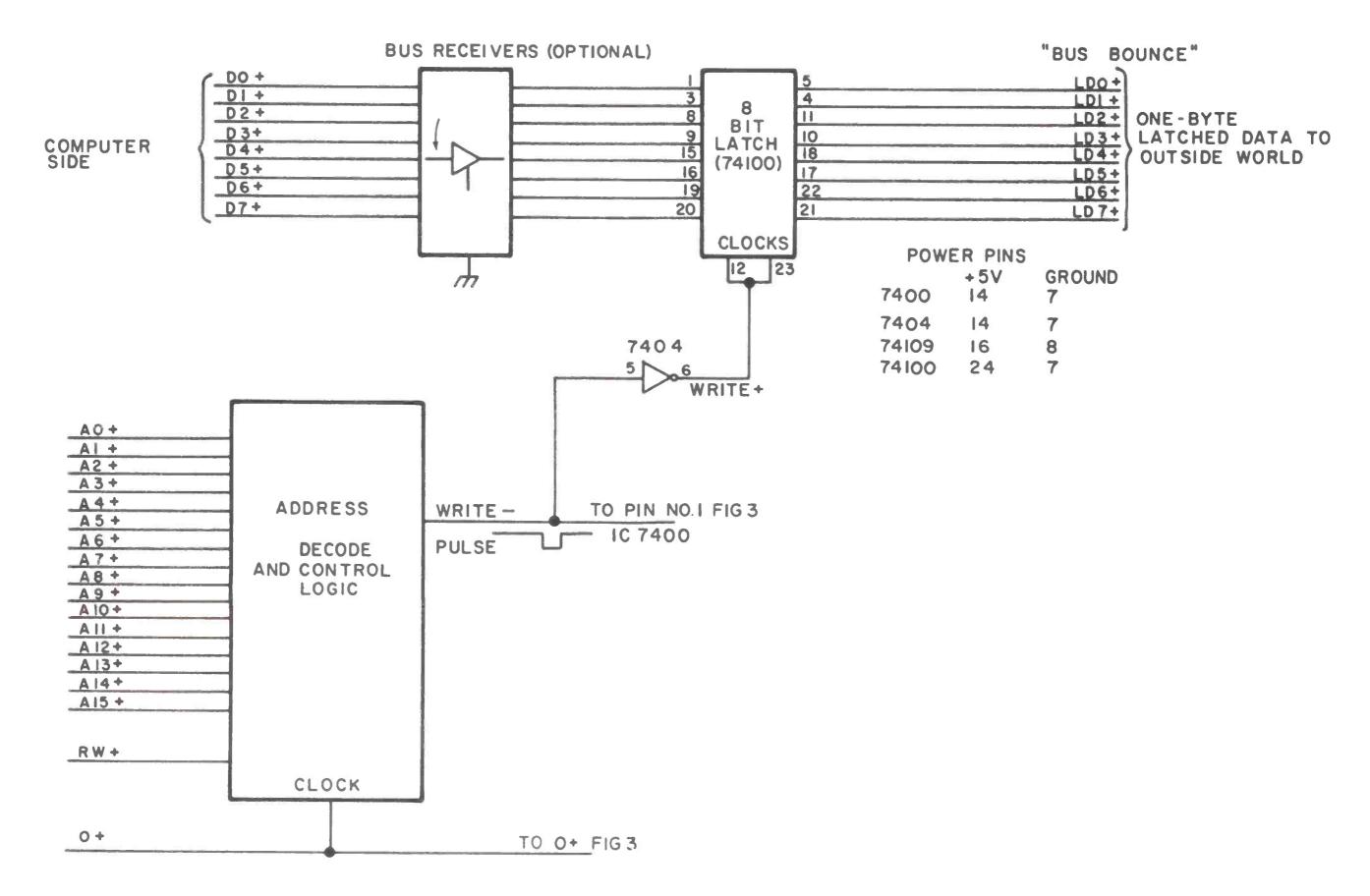

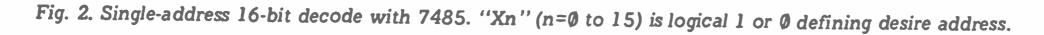

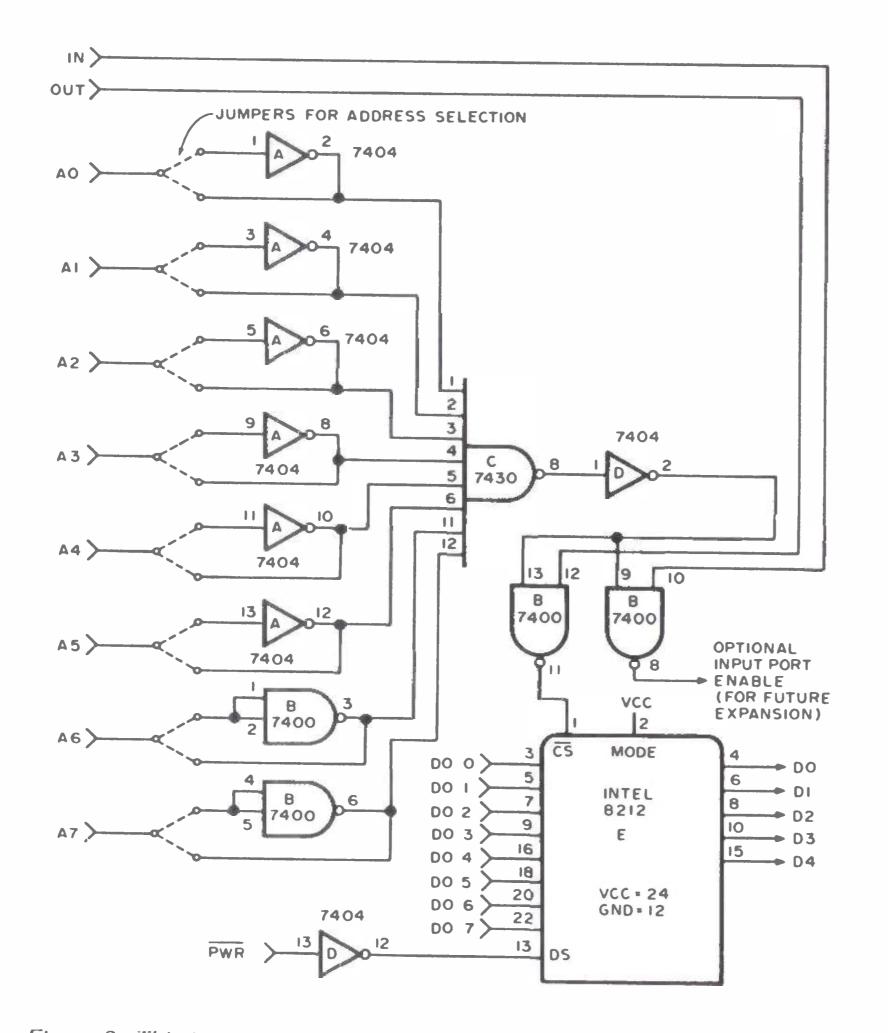

| Parallel Output Interfaces in Memory      | 106 |

| Address Space — Helmers                   |     |

| Son of Motorola — Fylstra                 | 110 |

| Data Paths — Liming                       | 117 |

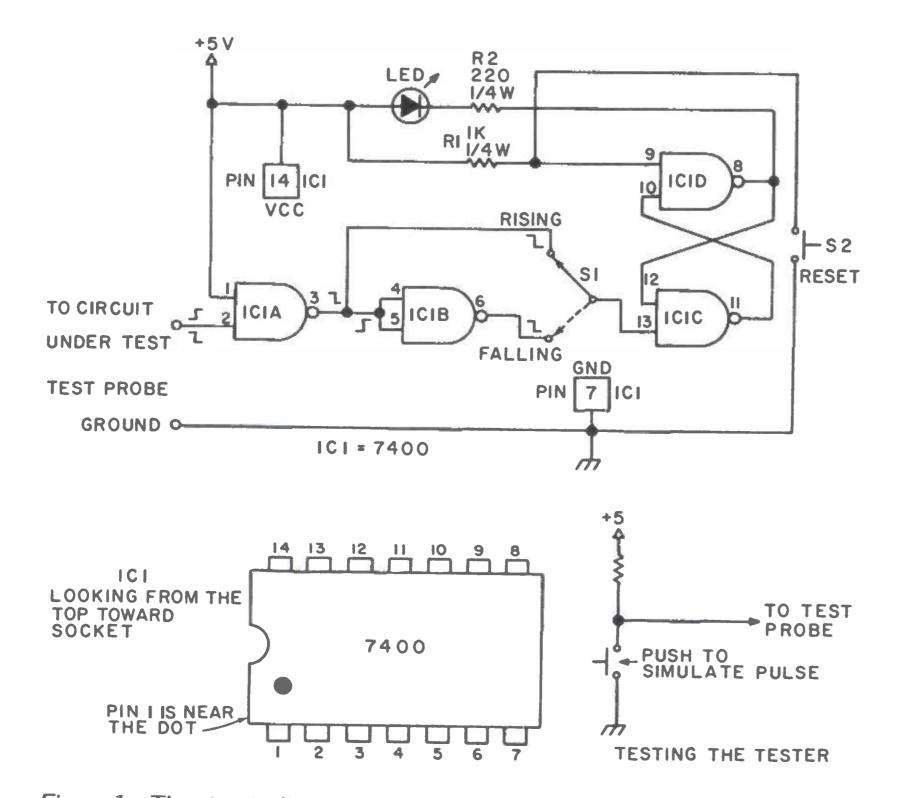

| Build a TTL Pulse Catcher — Walde         | 124 |

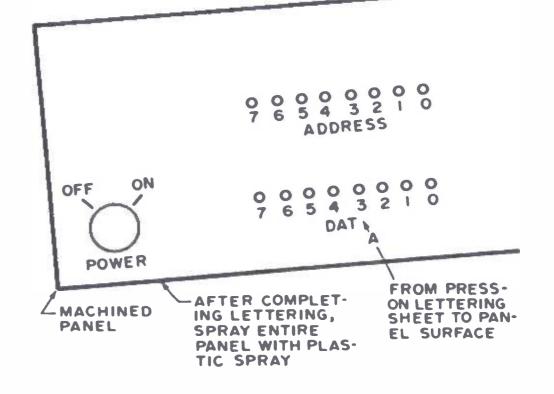

| Dressing Up Front Panels — Walters        | 125 |

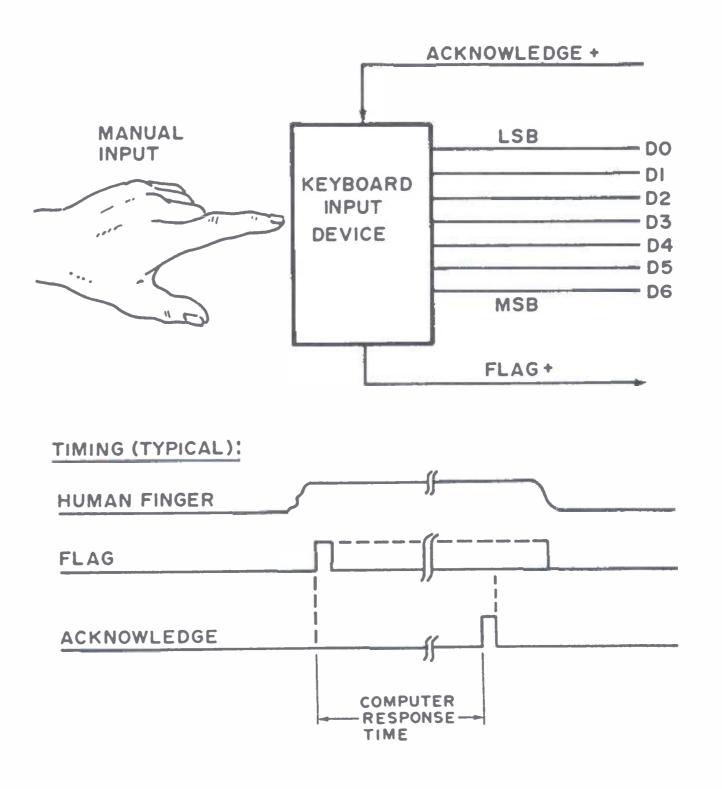

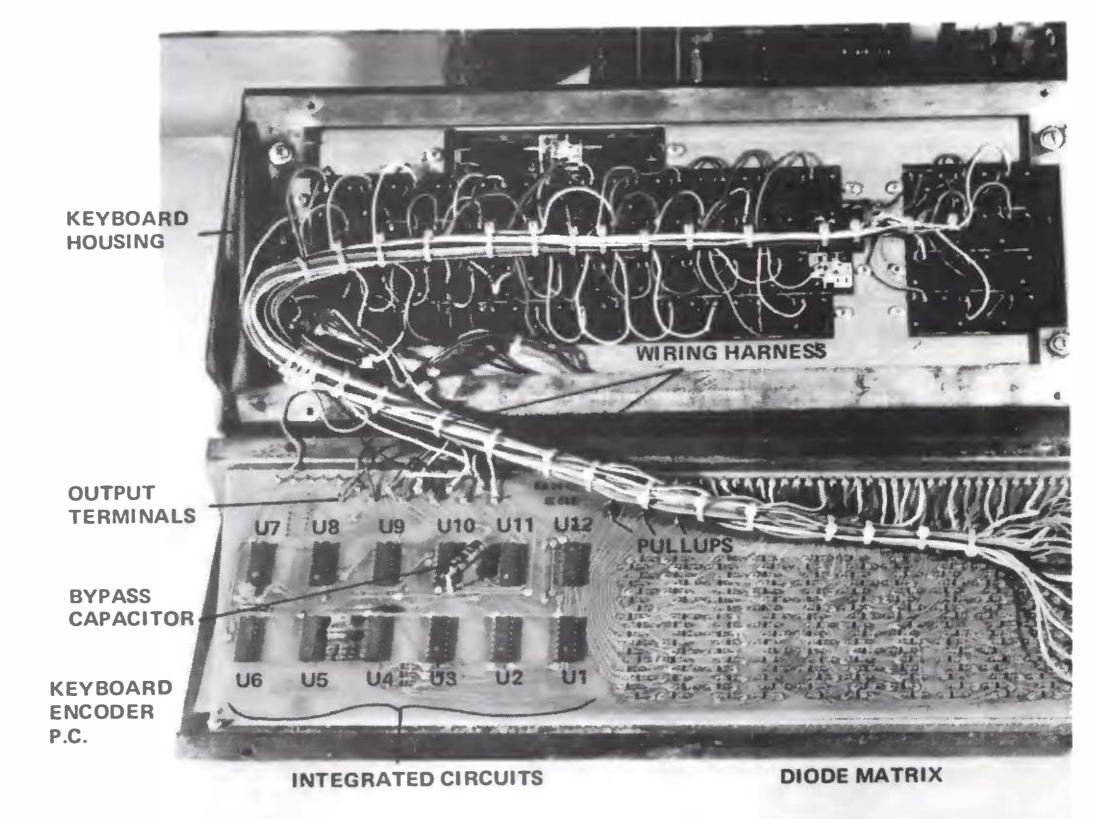

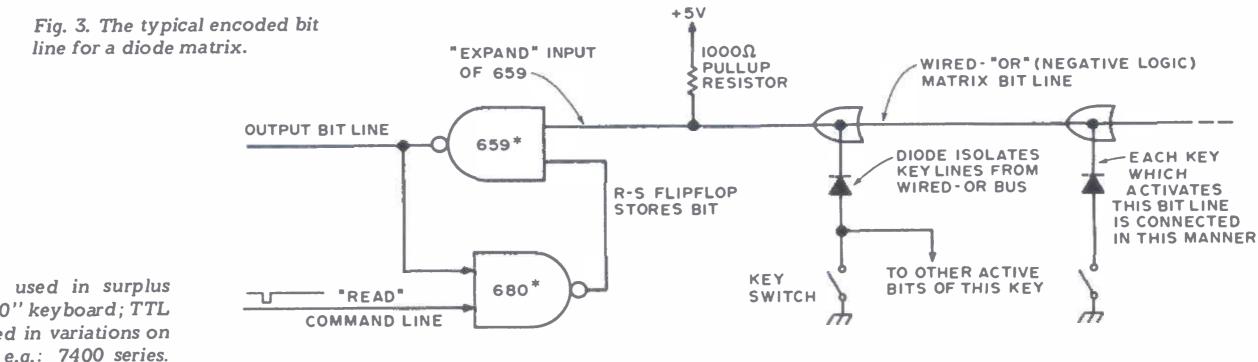

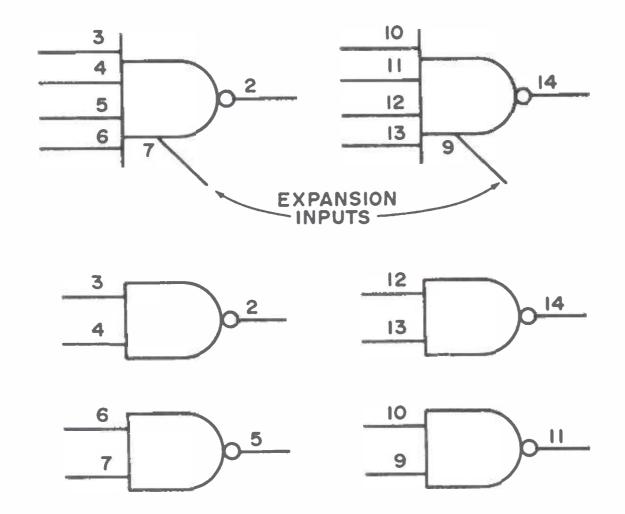

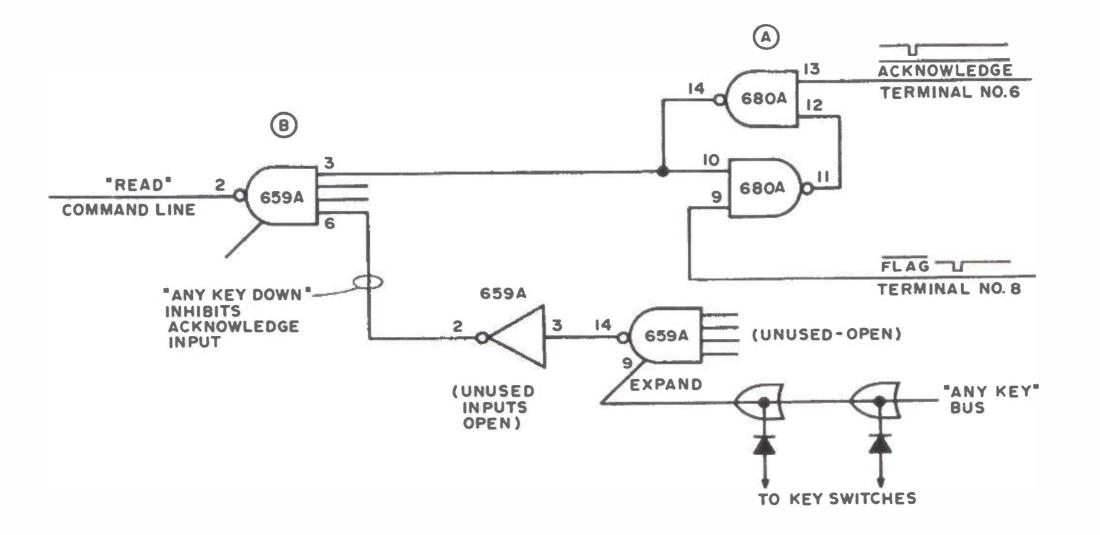

| Deciphering Mystery Keyboards — Helmers   | 126 |

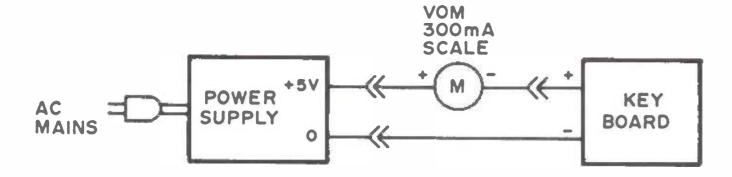

| A Quick Test of Keyboards — Walters       | 134 |

| Keyboard Modification — Macomber          | 135 |

| Serialize Those Bits From Your            | 136 |

| Mystery Keyboard — Halber                 |     |

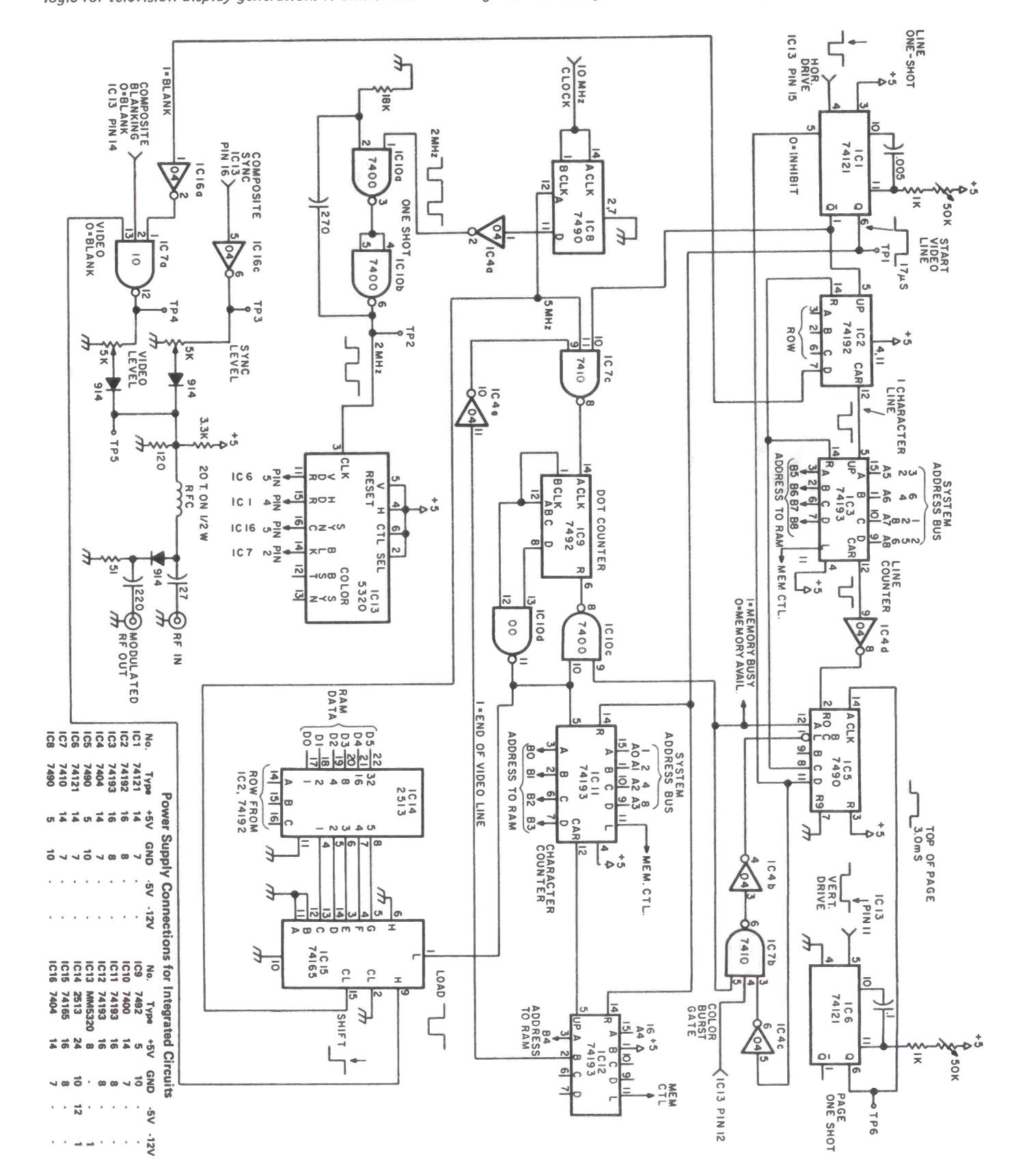

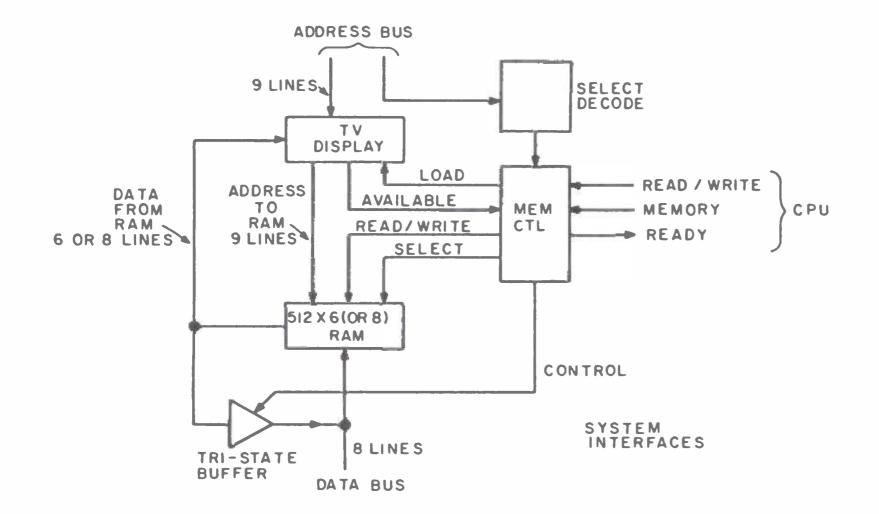

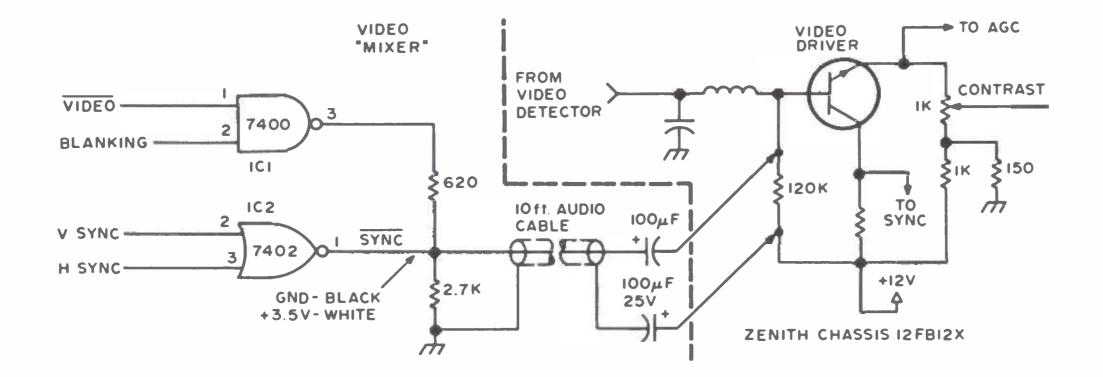

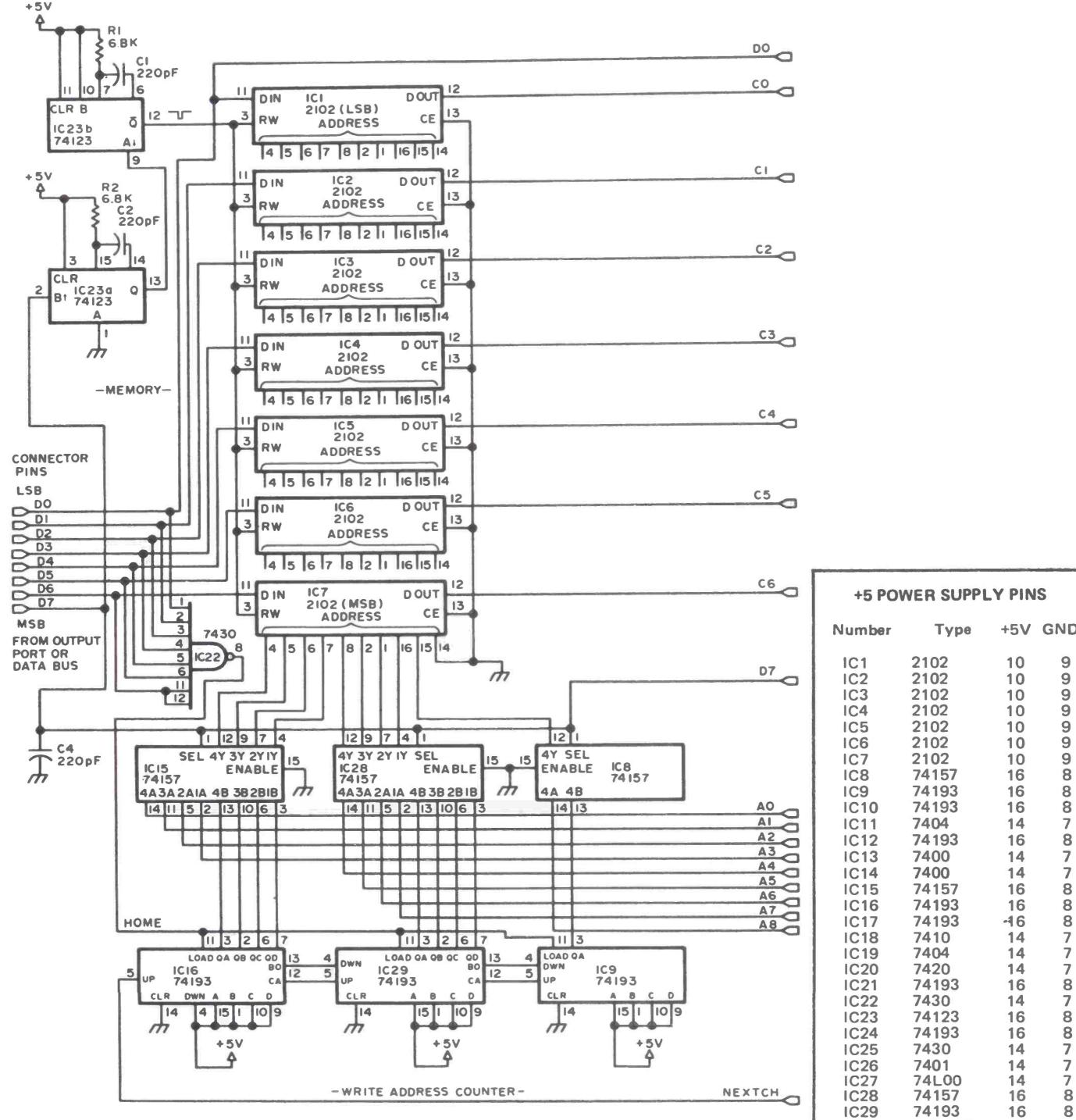

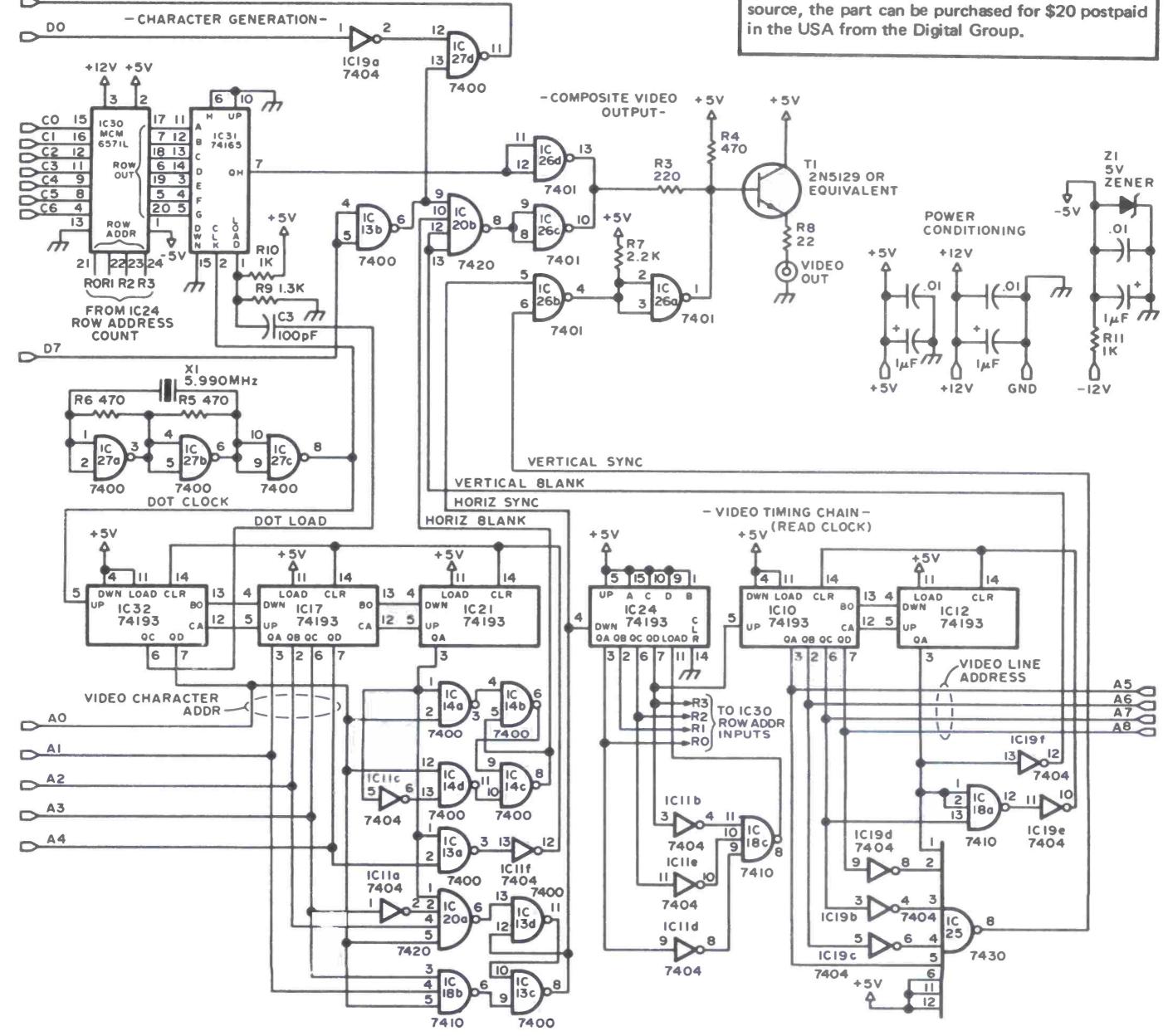

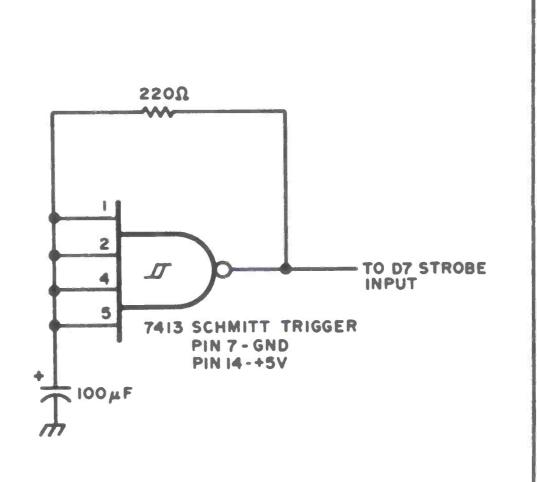

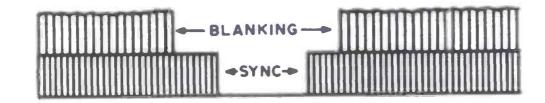

| Build a Television Display — Gantt        | 138 |

| The "Ignorance Is Bliss" Television Drive | 144 |

| Circuit — Barbier                         |     |

| Build a TV Readout Device for Your        | 145 |

| Microprocessor — Suding                   |     |

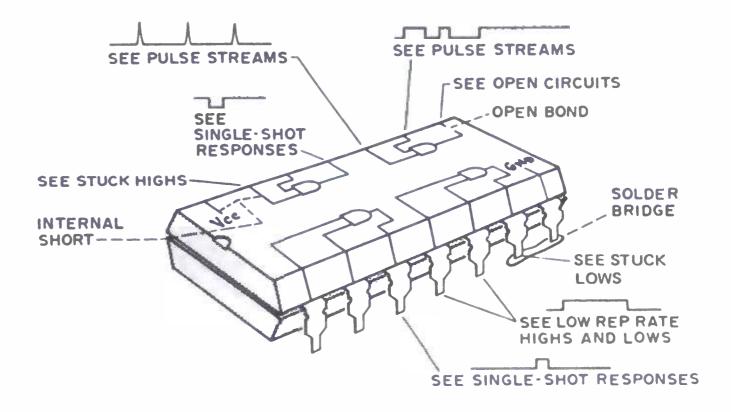

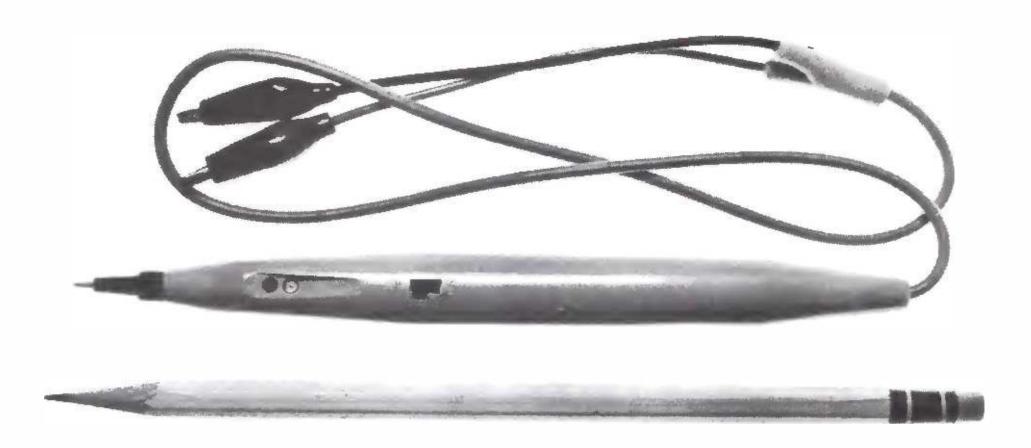

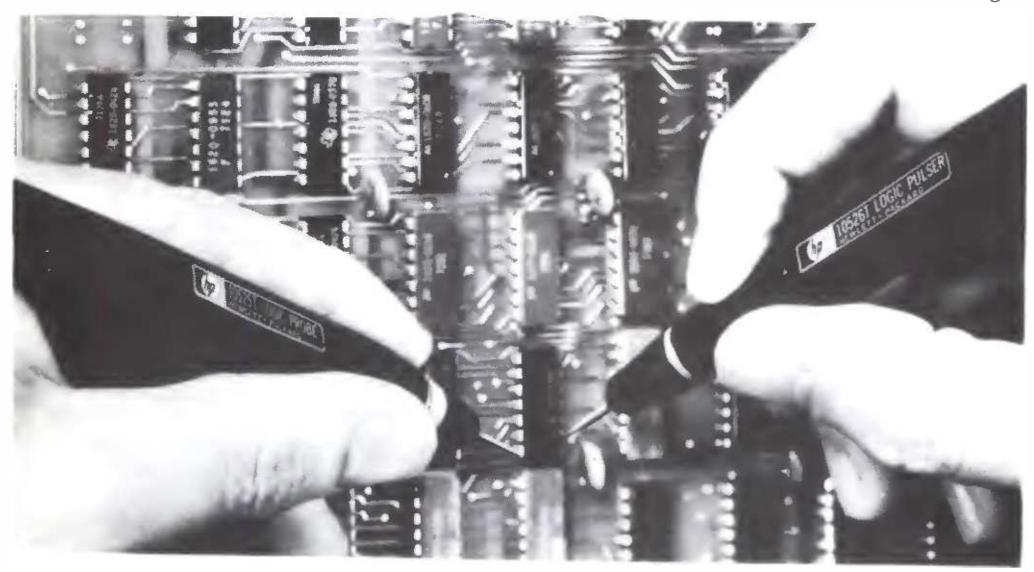

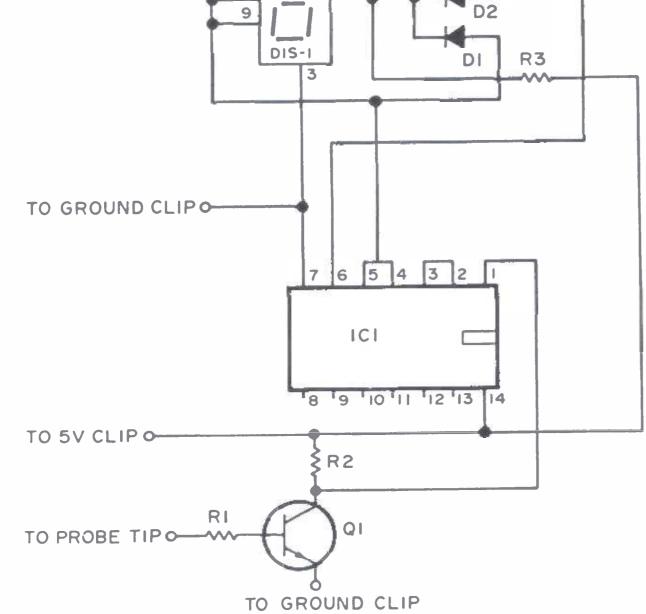

| Logic Probes — Hardware Bug Chasers — Burr       | 213 |

|--------------------------------------------------|-----|

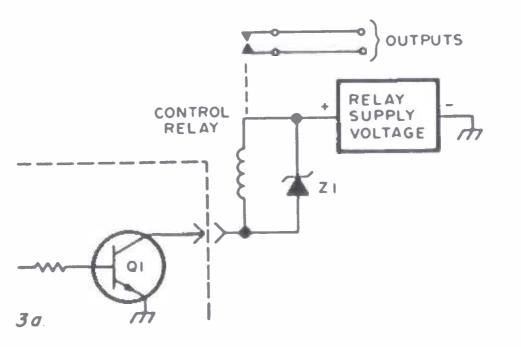

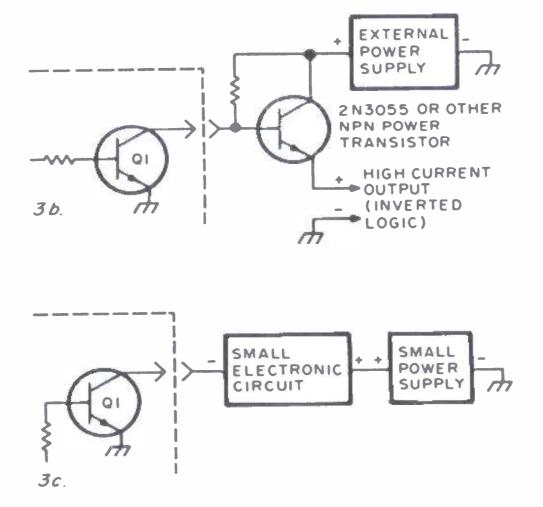

| Controlling External Devices With Hobbyist       | 218 |

| Computers — Bosen                                |     |

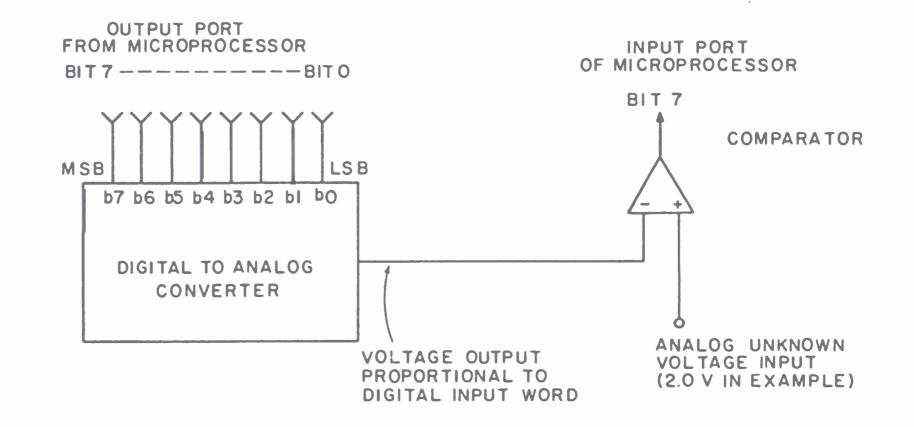

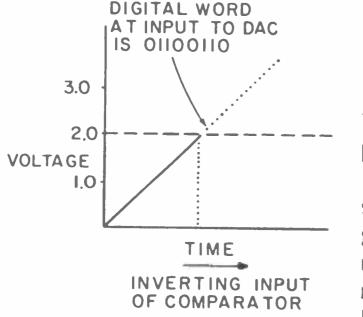

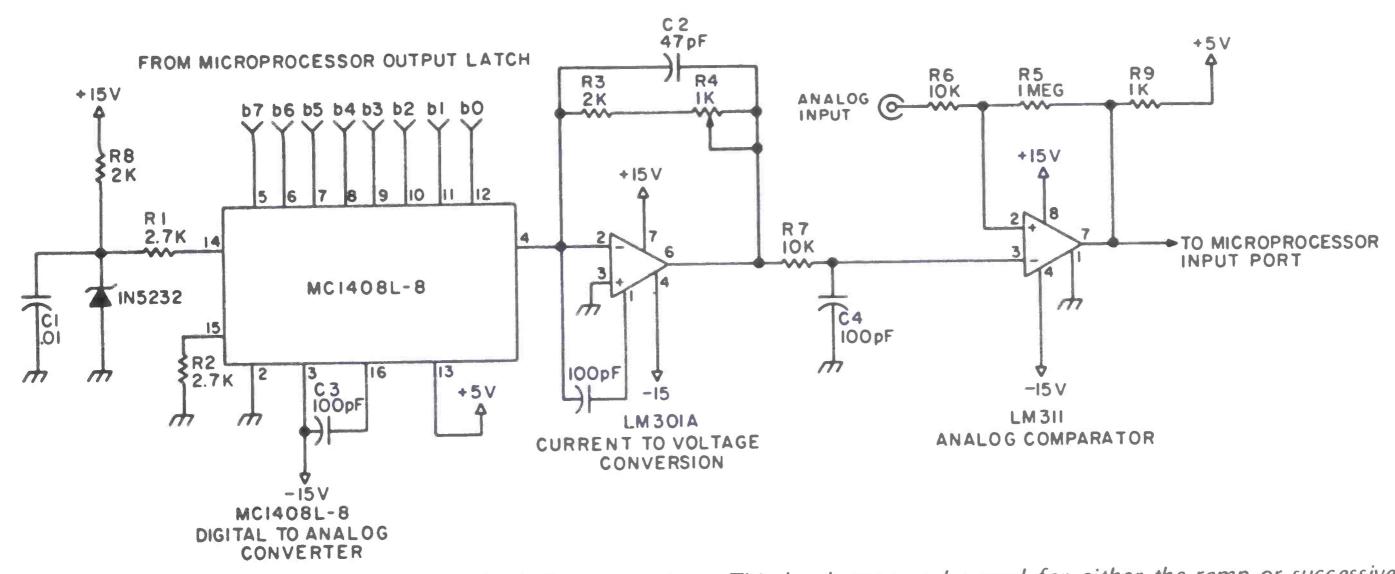

| Microprocessor Based Analog/Digital Conversion — | 222 |

| Frank                                            |     |

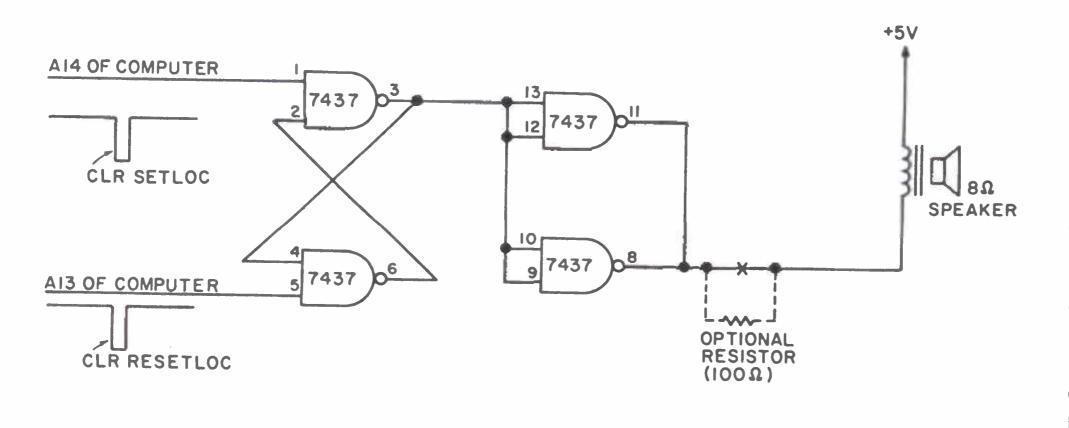

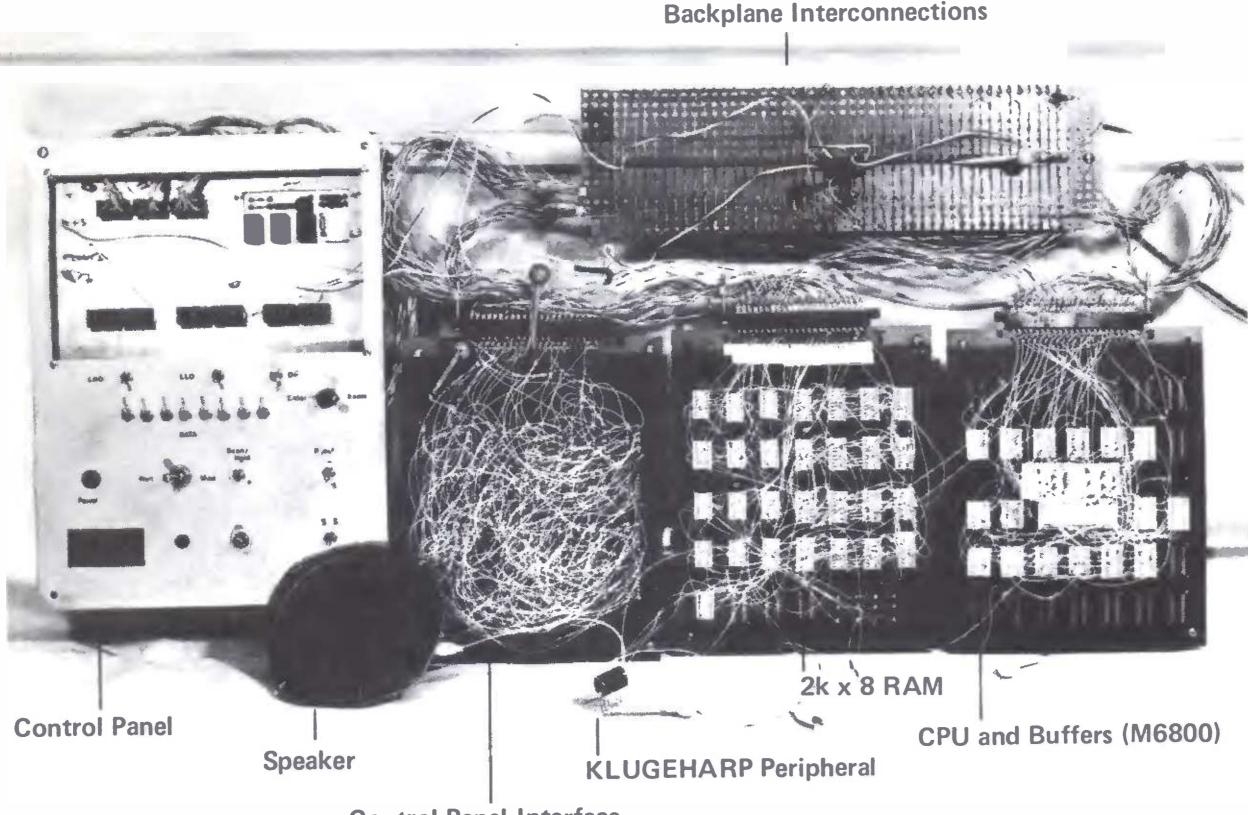

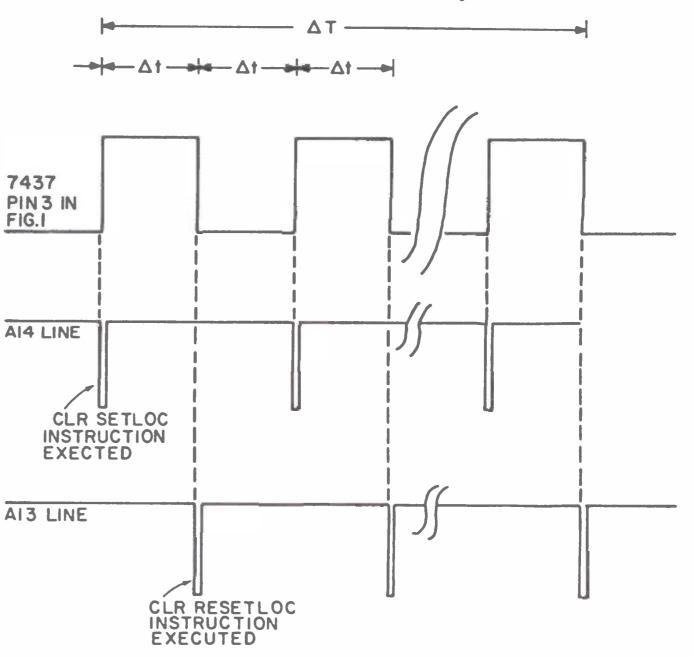

| Add a Kluge Harp to Your Computer — Helmers      | 226 |

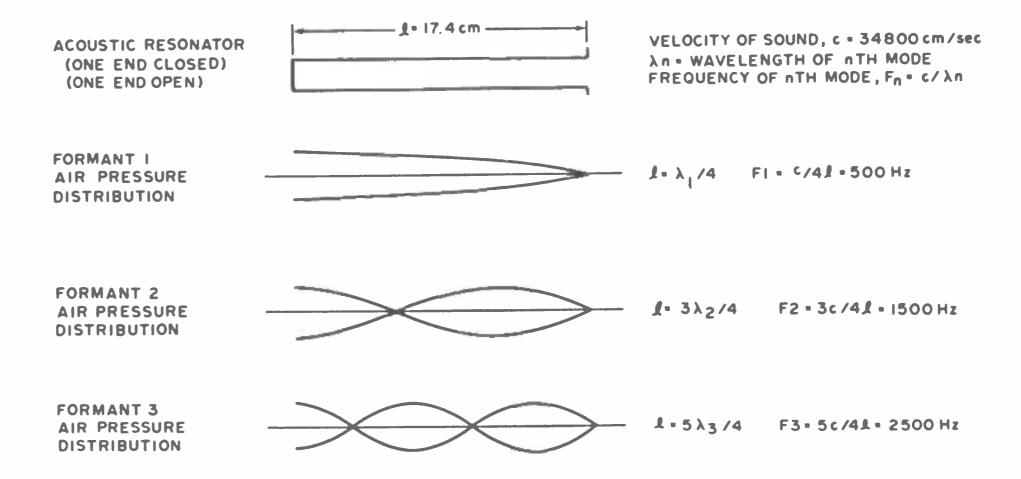

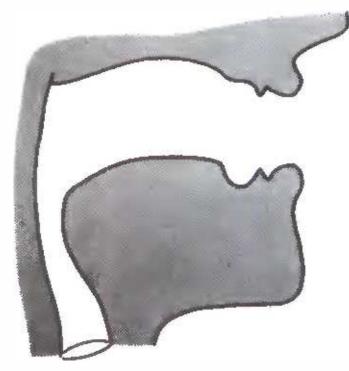

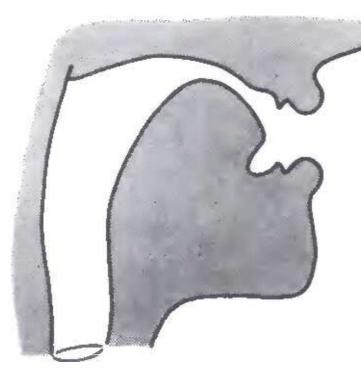

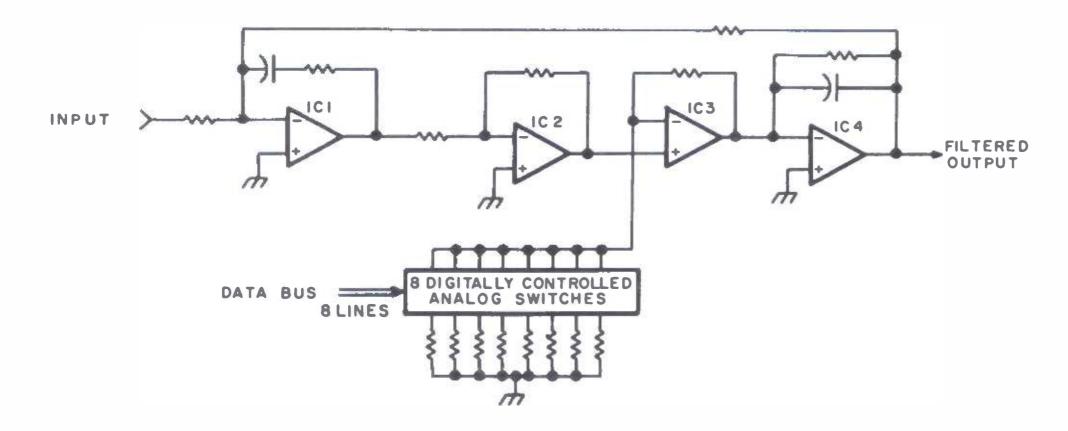

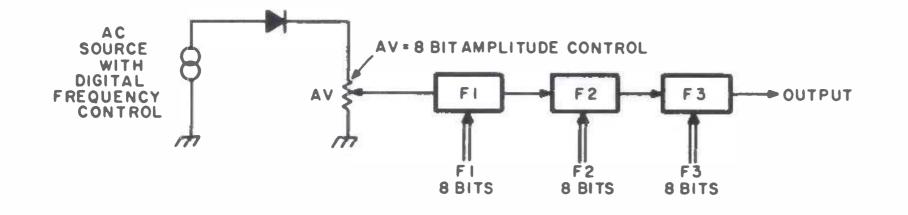

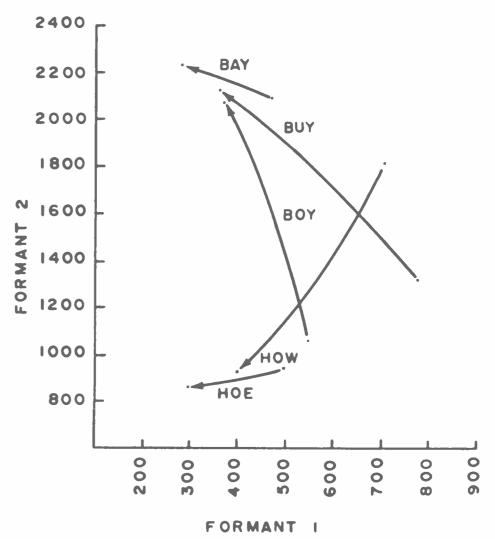

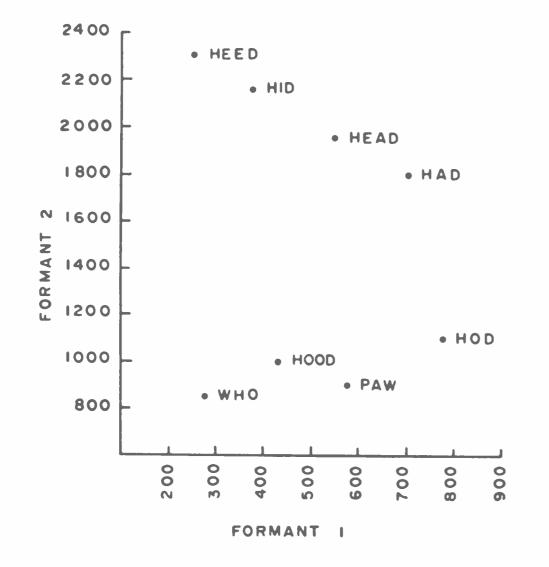

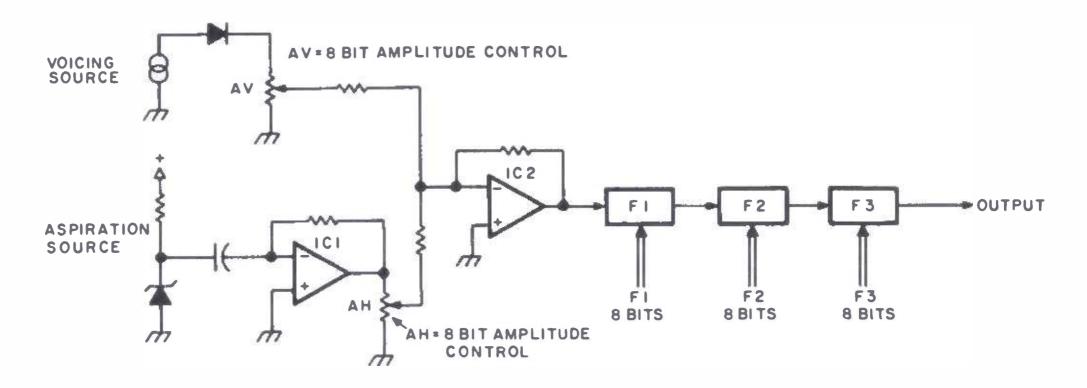

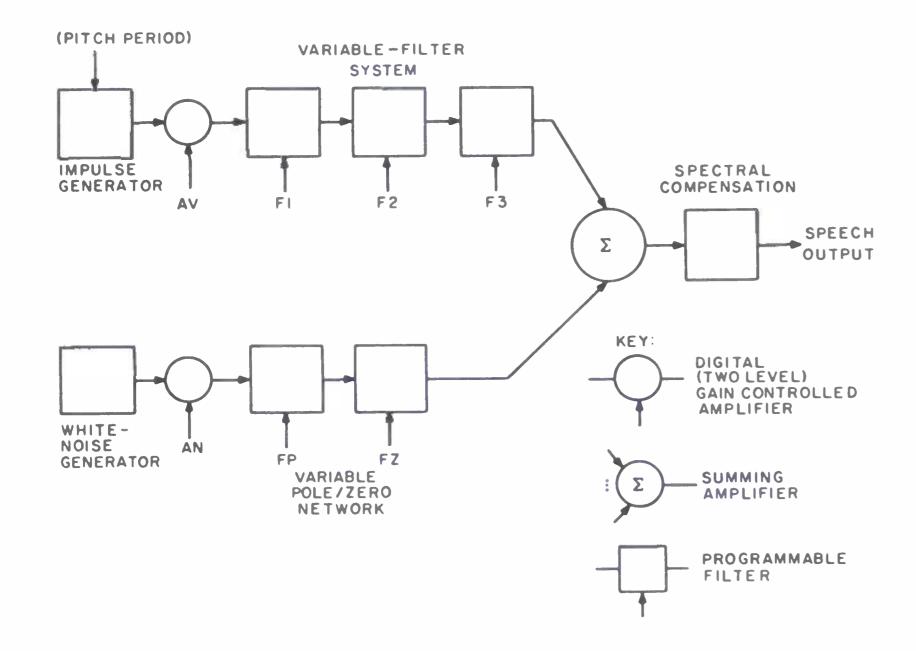

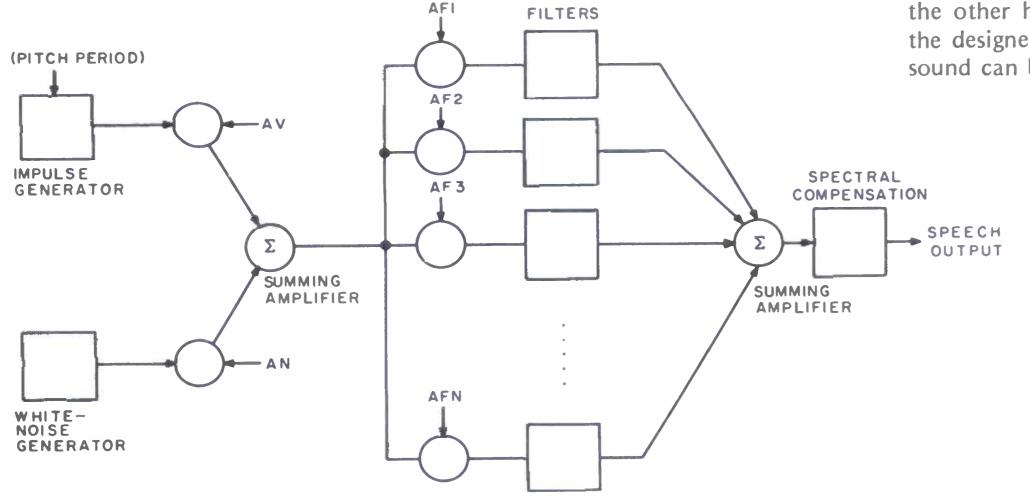

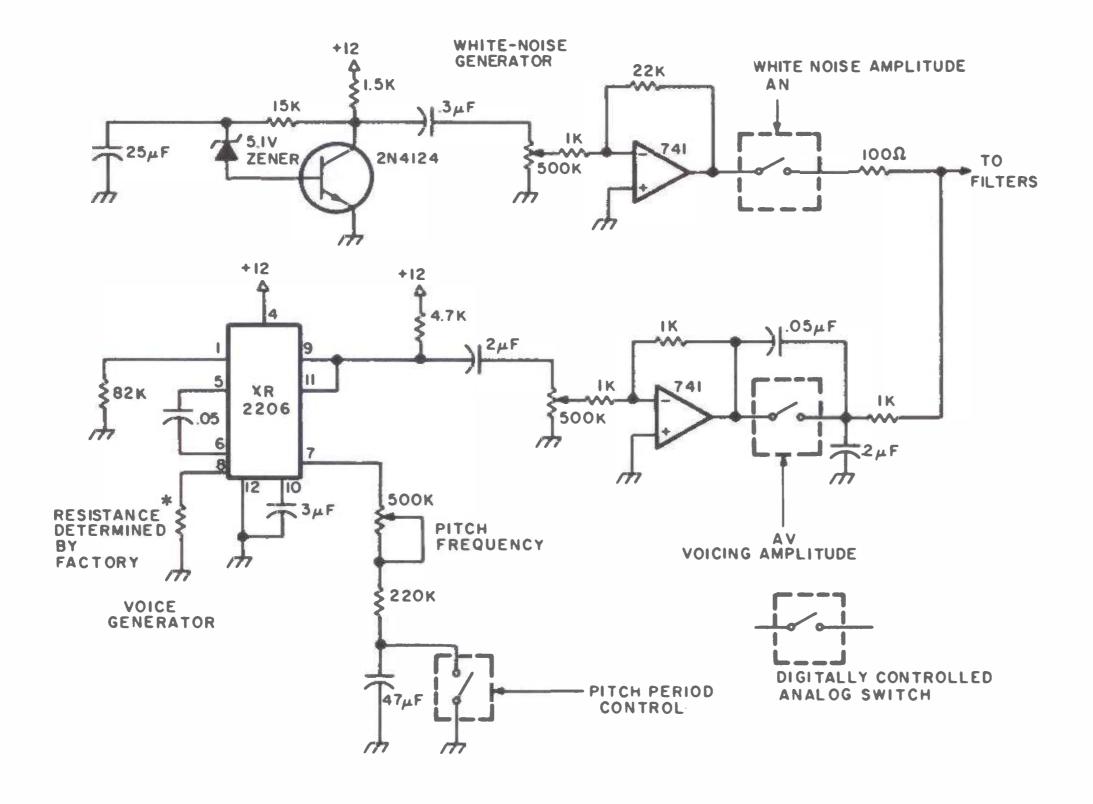

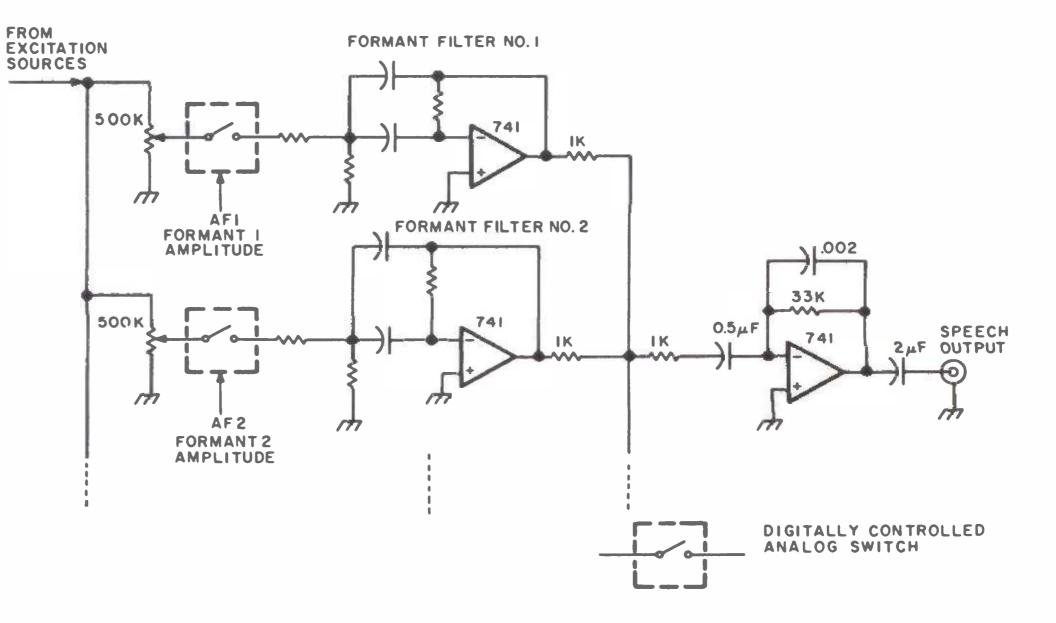

| The Time Has Come to Talk — Atmar                | 231 |

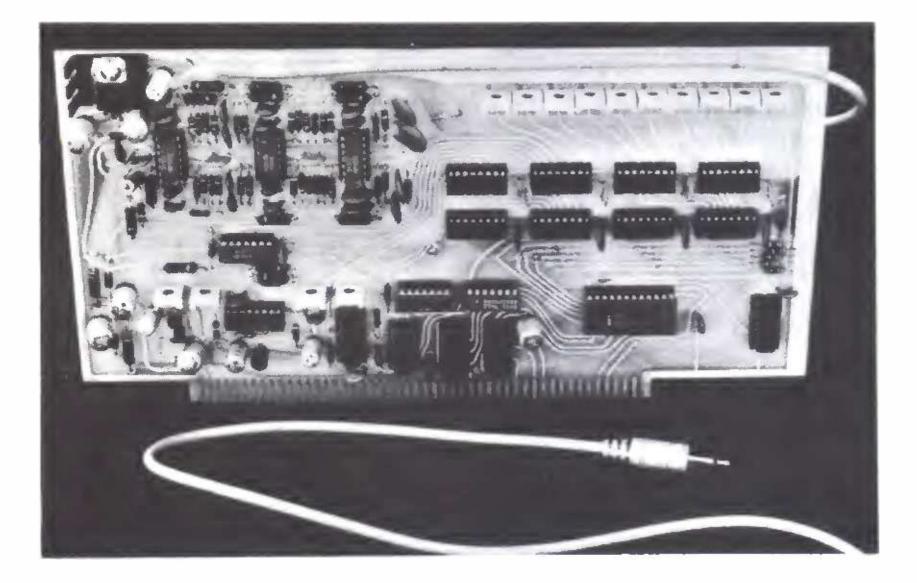

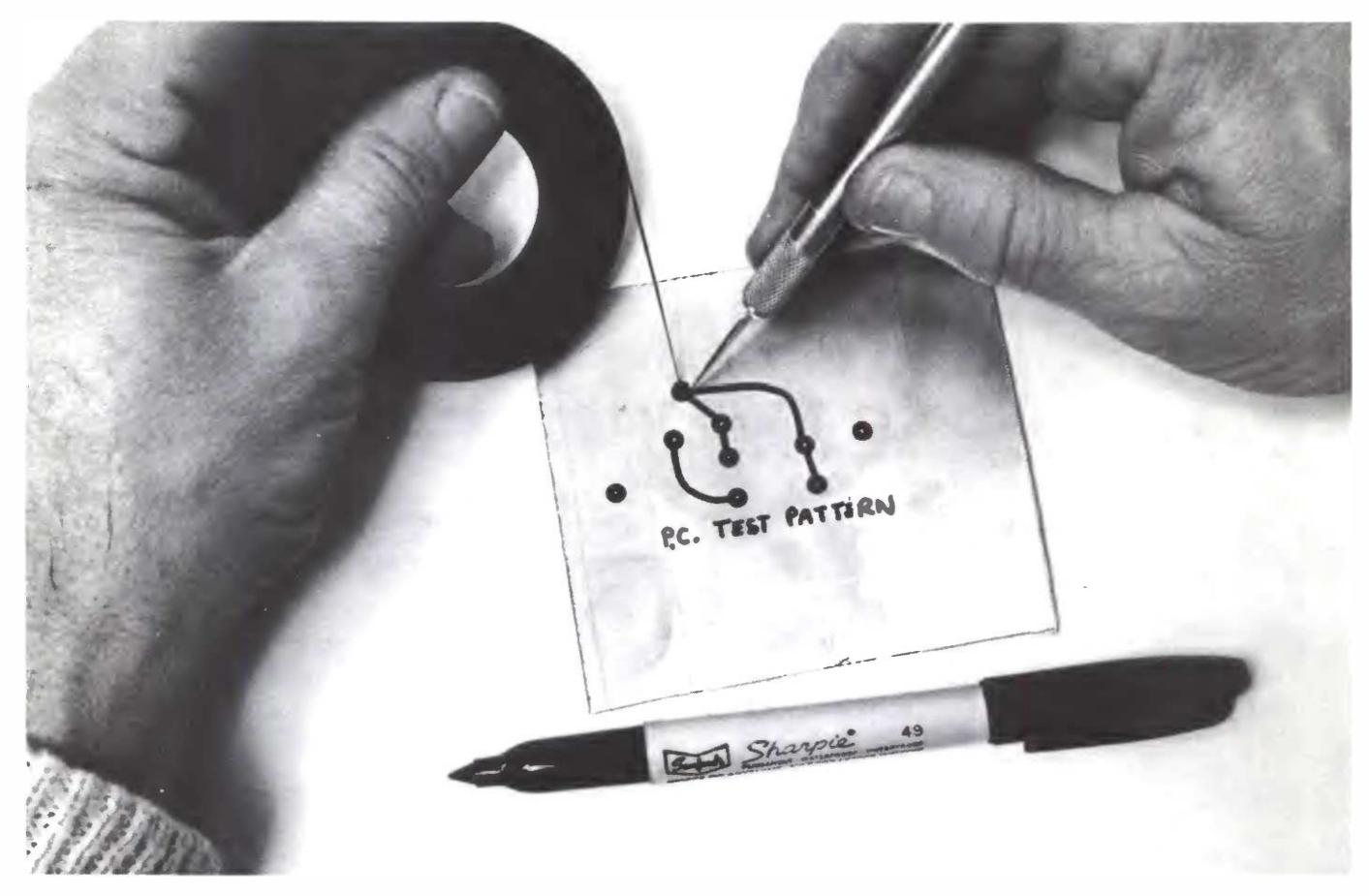

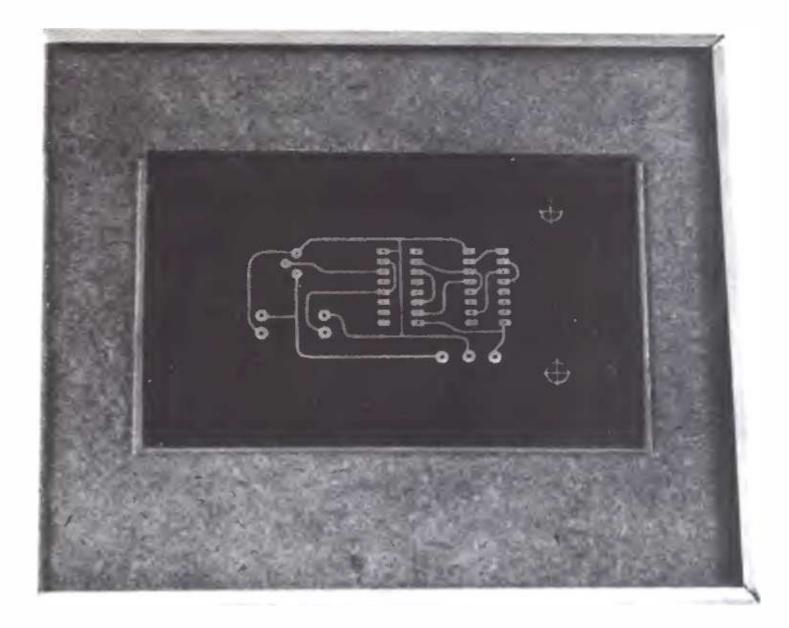

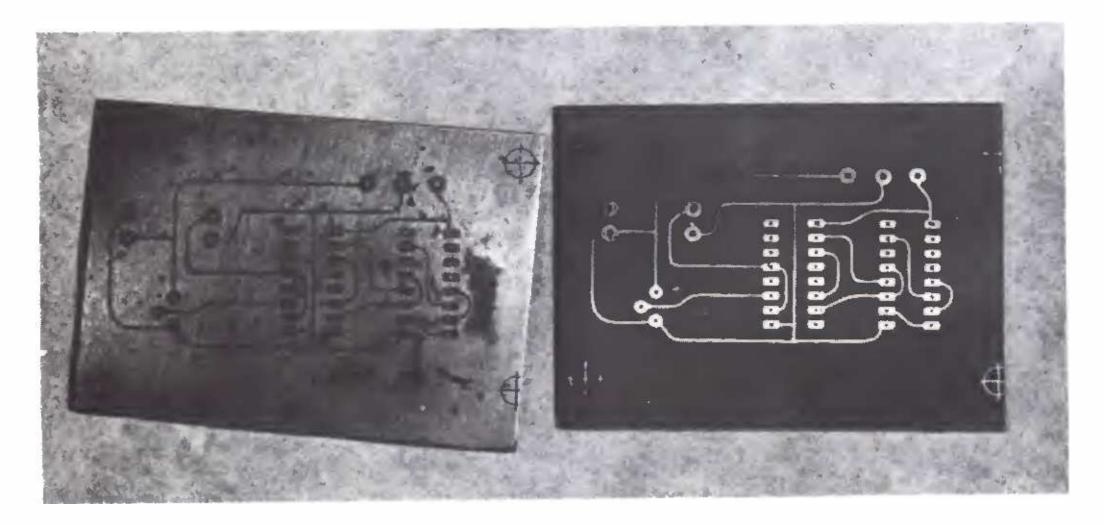

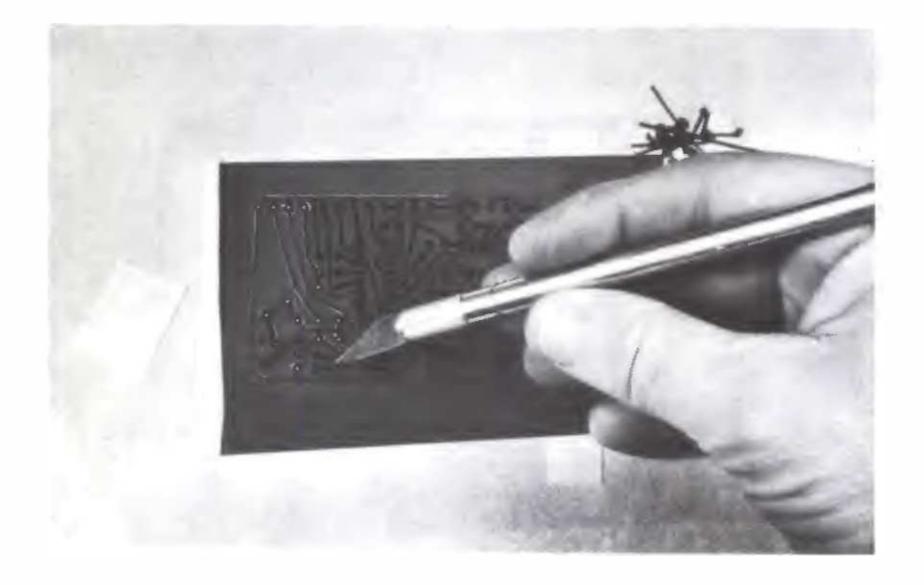

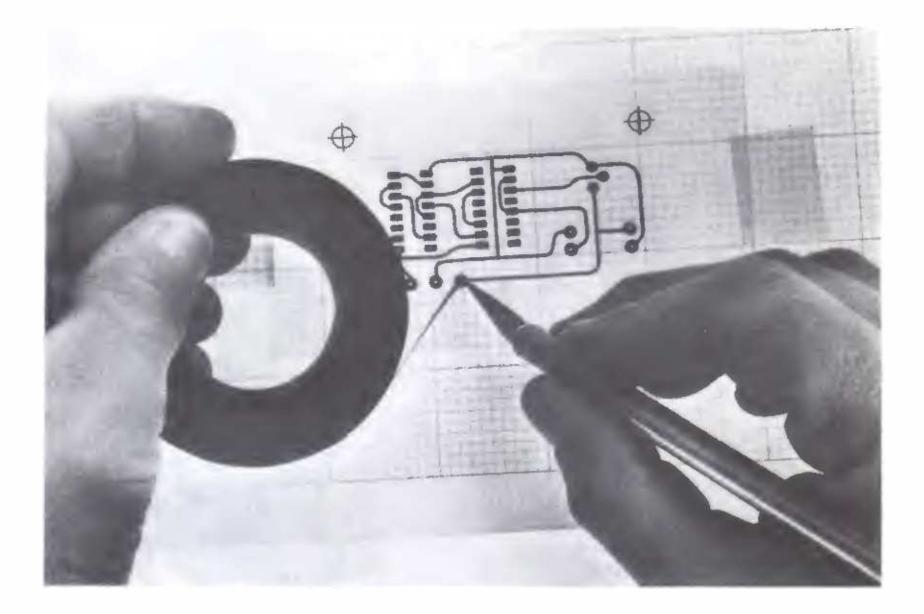

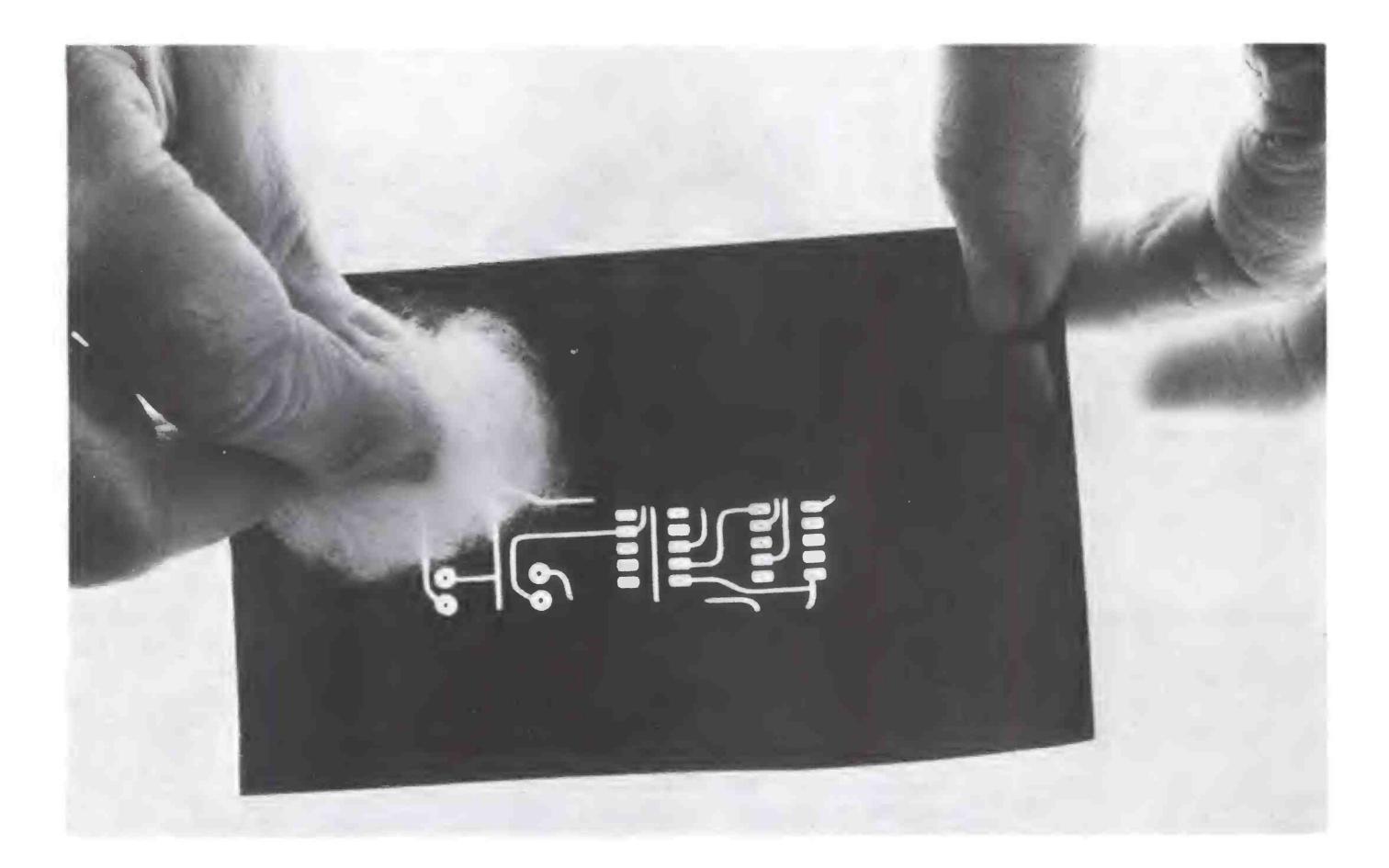

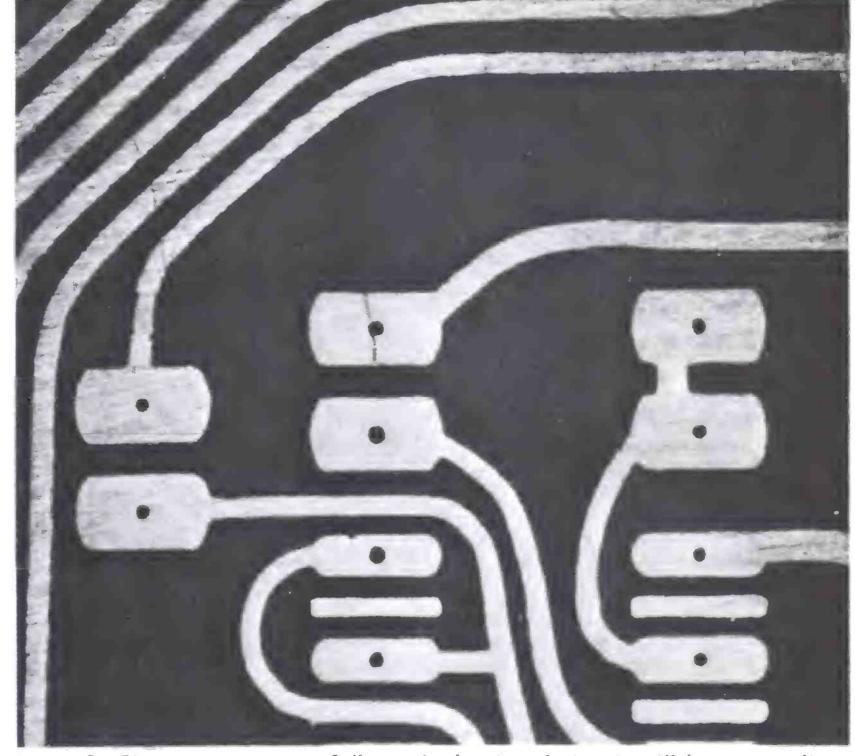

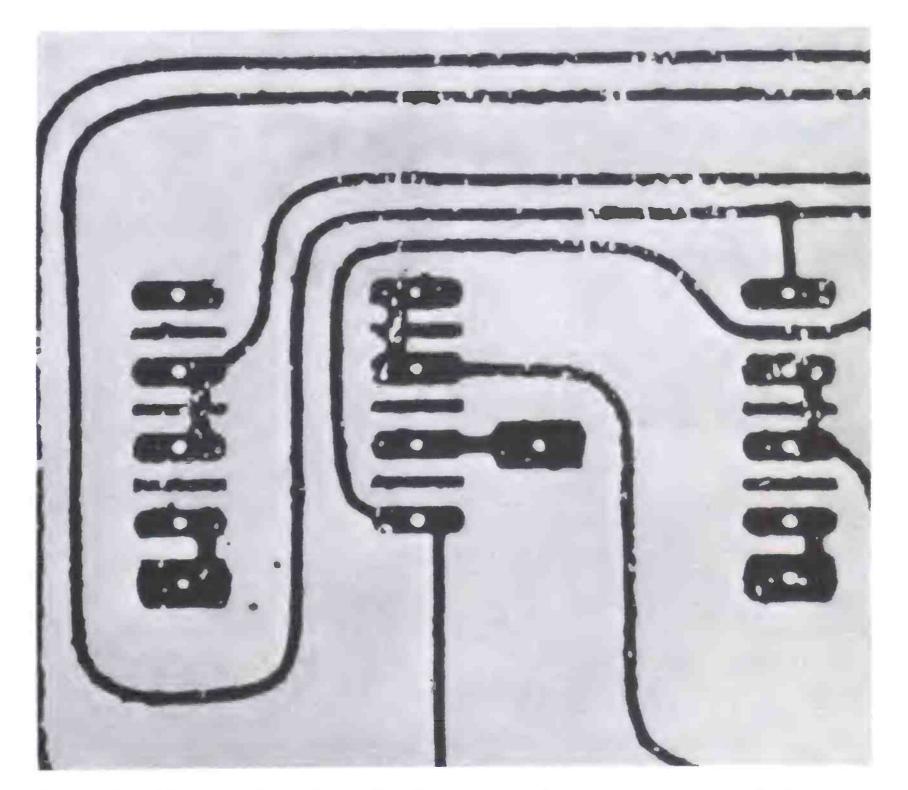

| Make Your Own Printed Circuits — Hogenson        | 238 |

### SOFTWARE

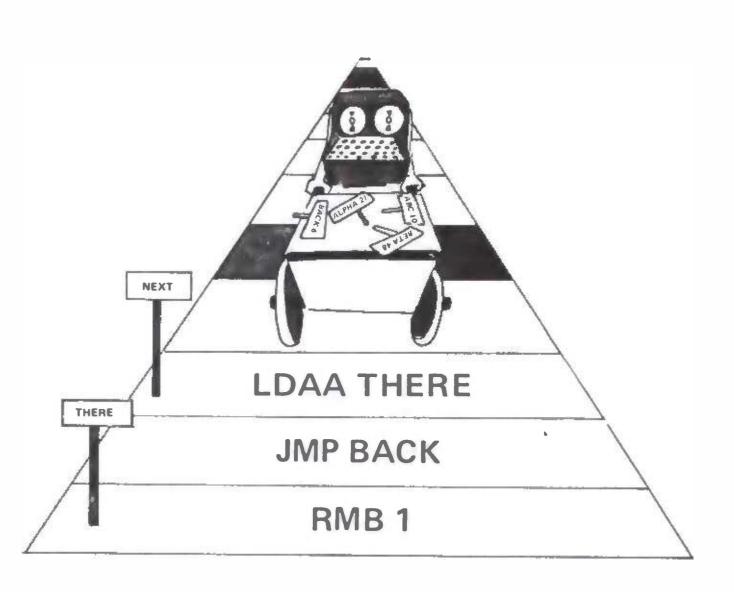

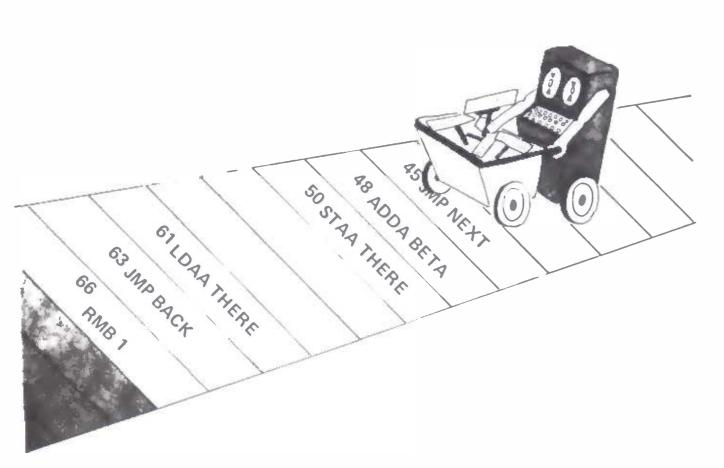

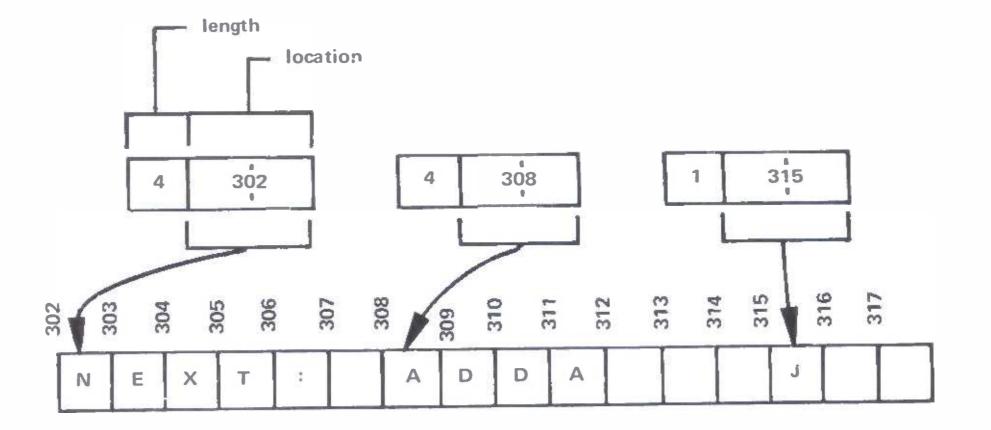

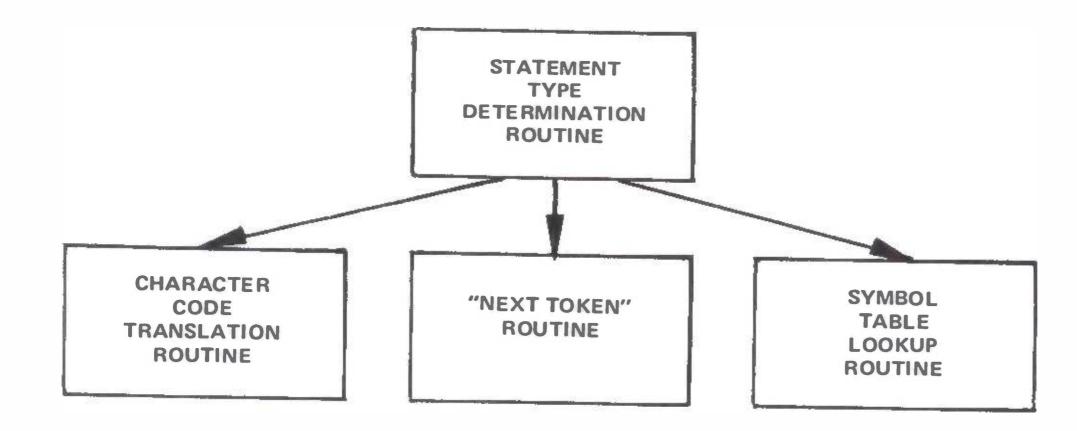

| Write Your Own Assembler — Fylstra                                | 246 |

|-------------------------------------------------------------------|-----|

| Simplify Your Homemade Assembler — Jewell                         | 255 |

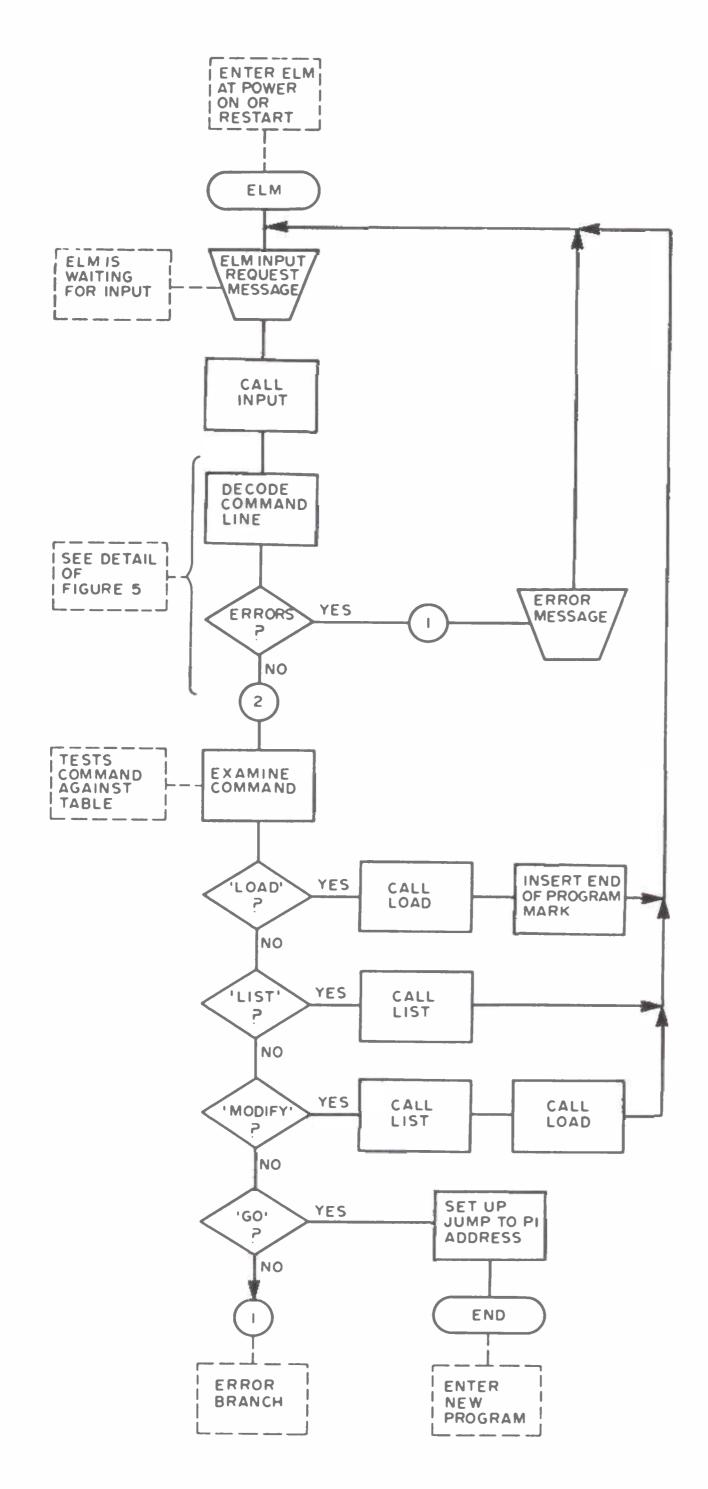

| Interact With an ELM — Gable                                      | 261 |

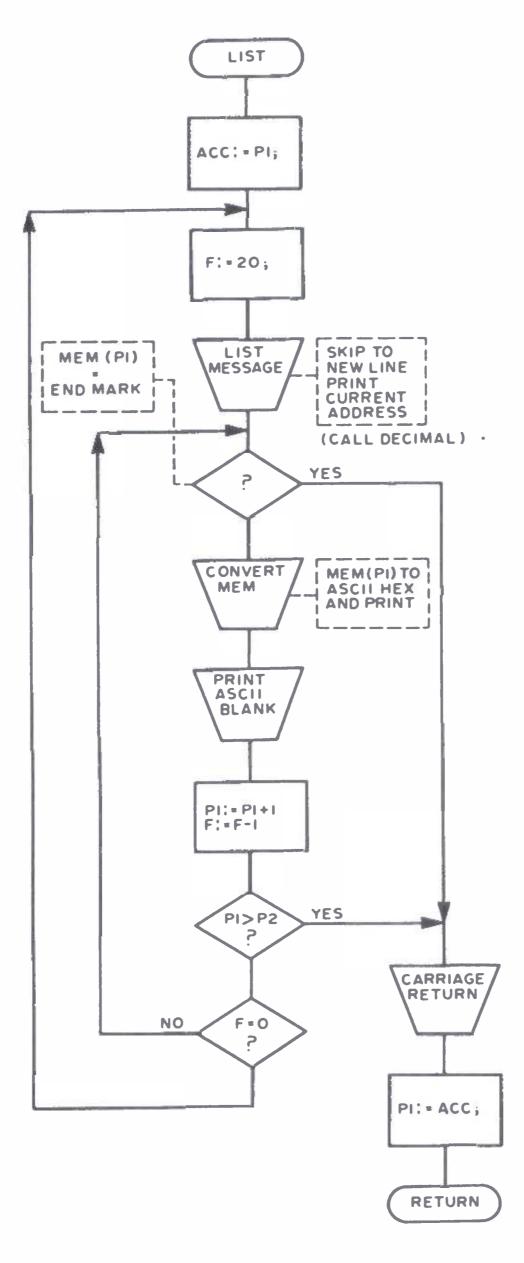

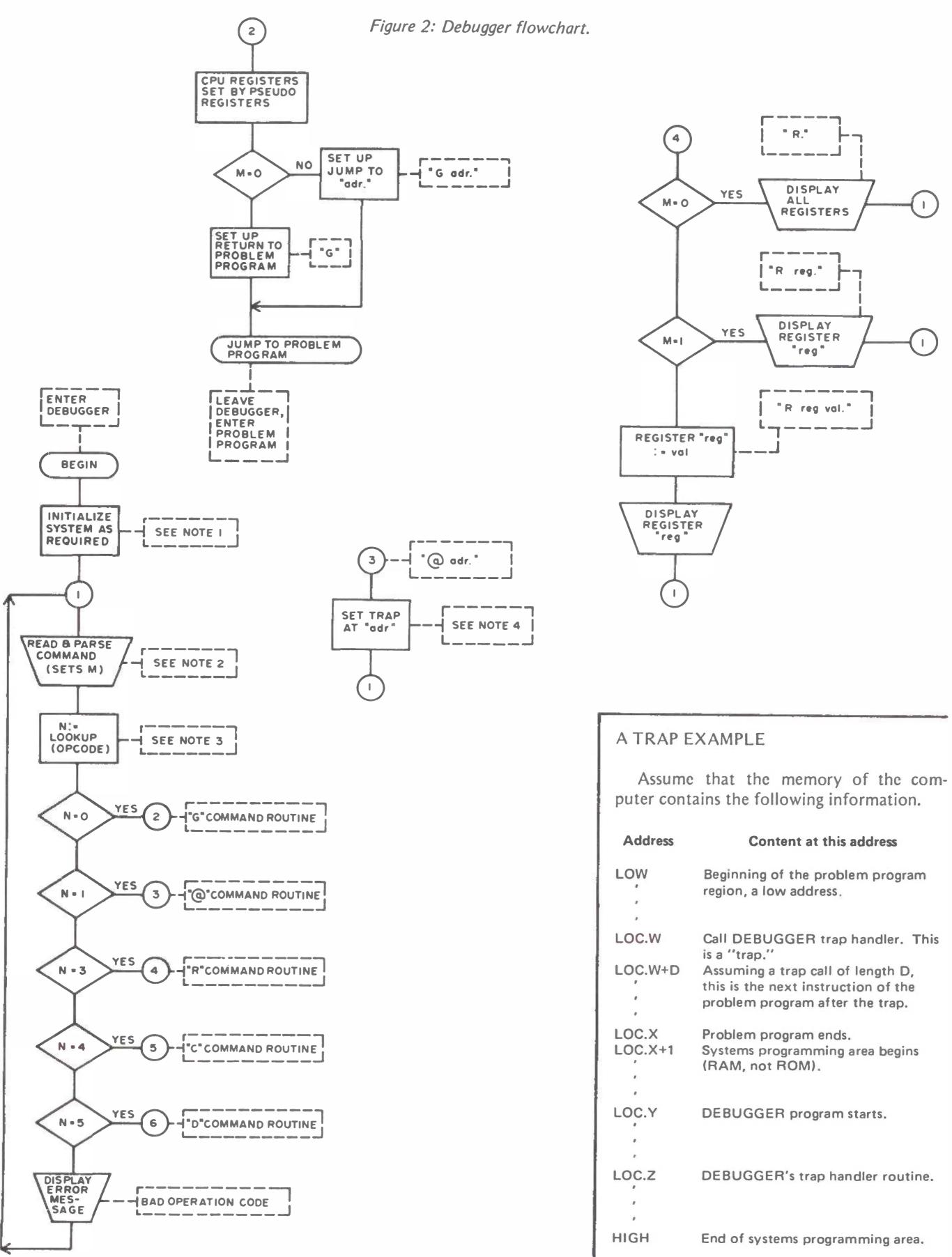

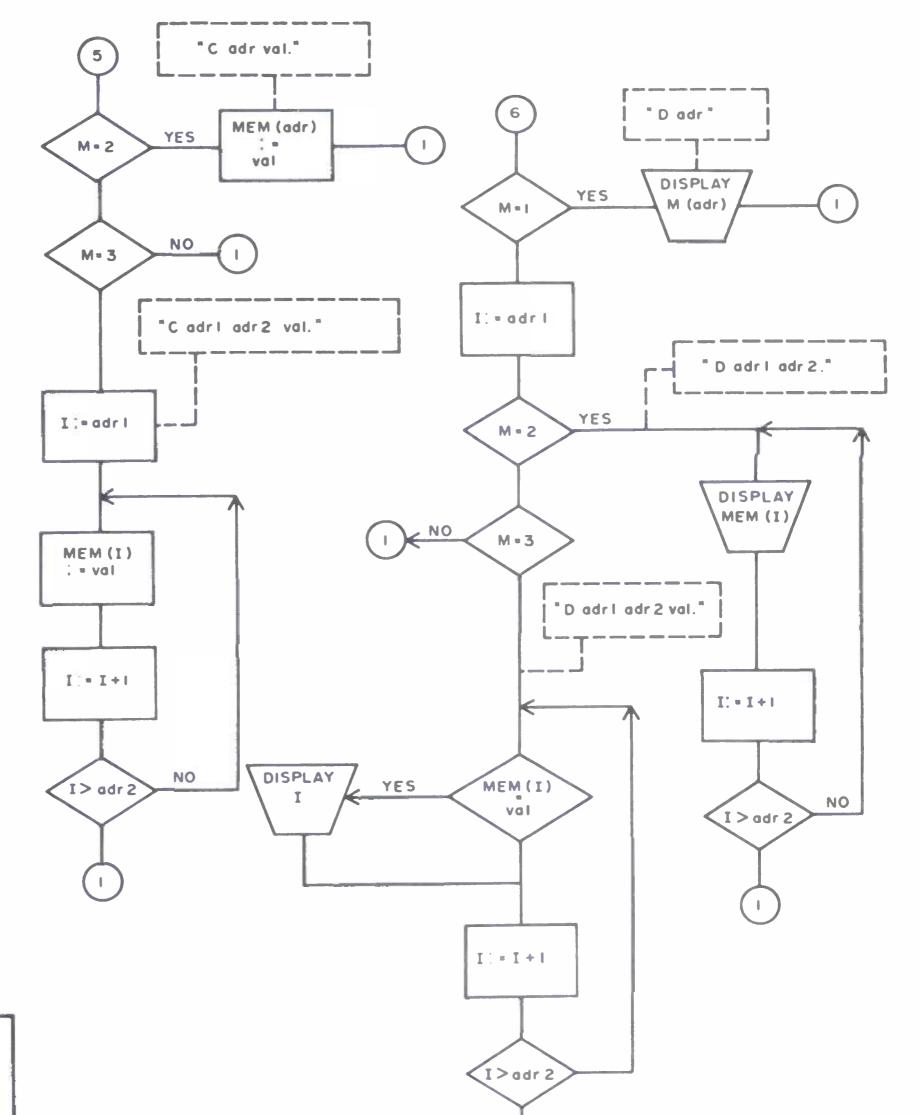

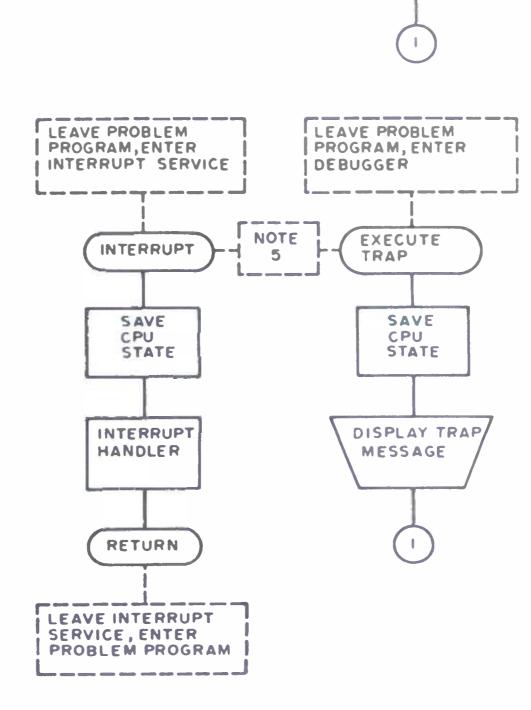

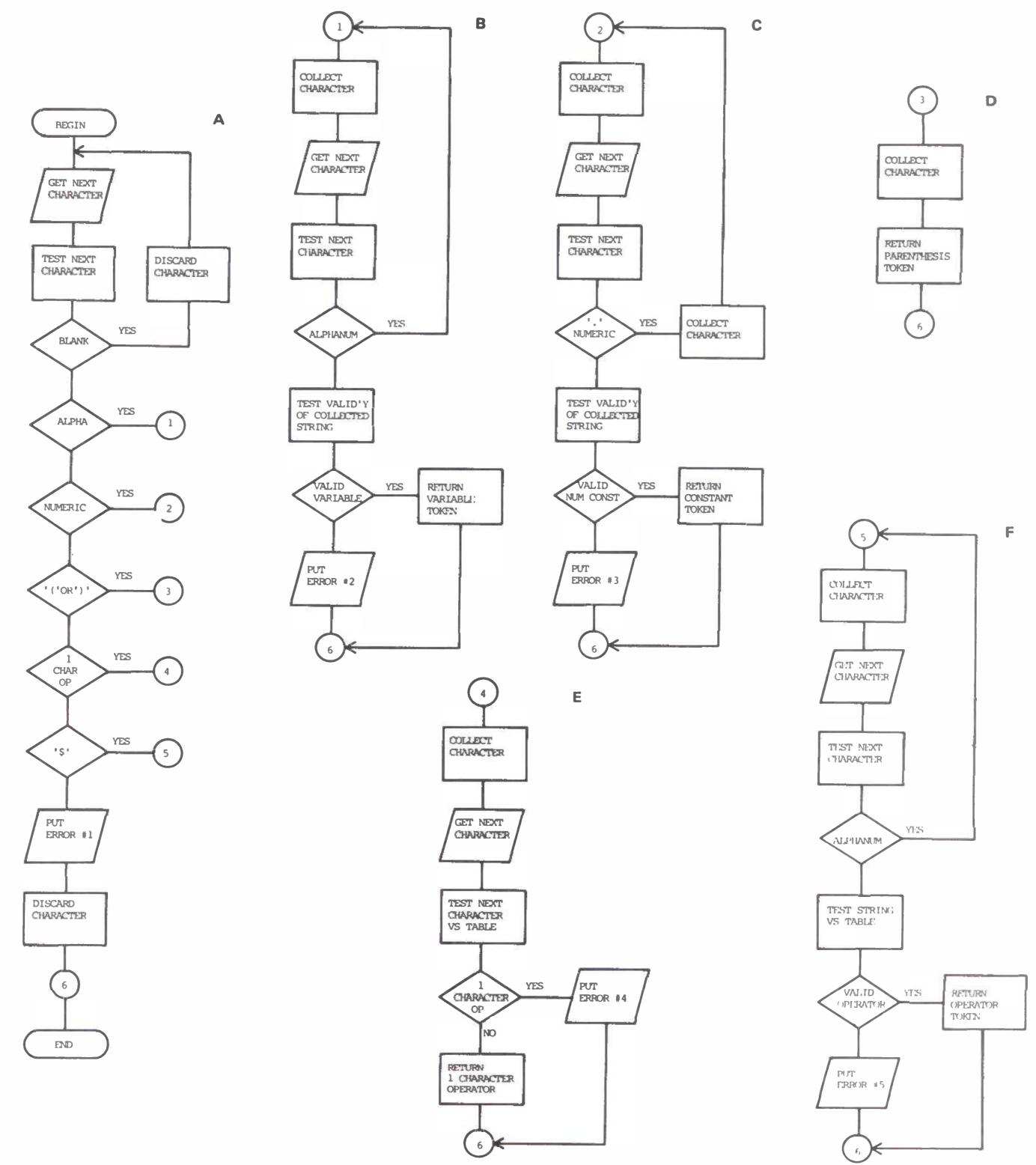

| Design an On Line Debugger — Wier and Brown                       | 268 |

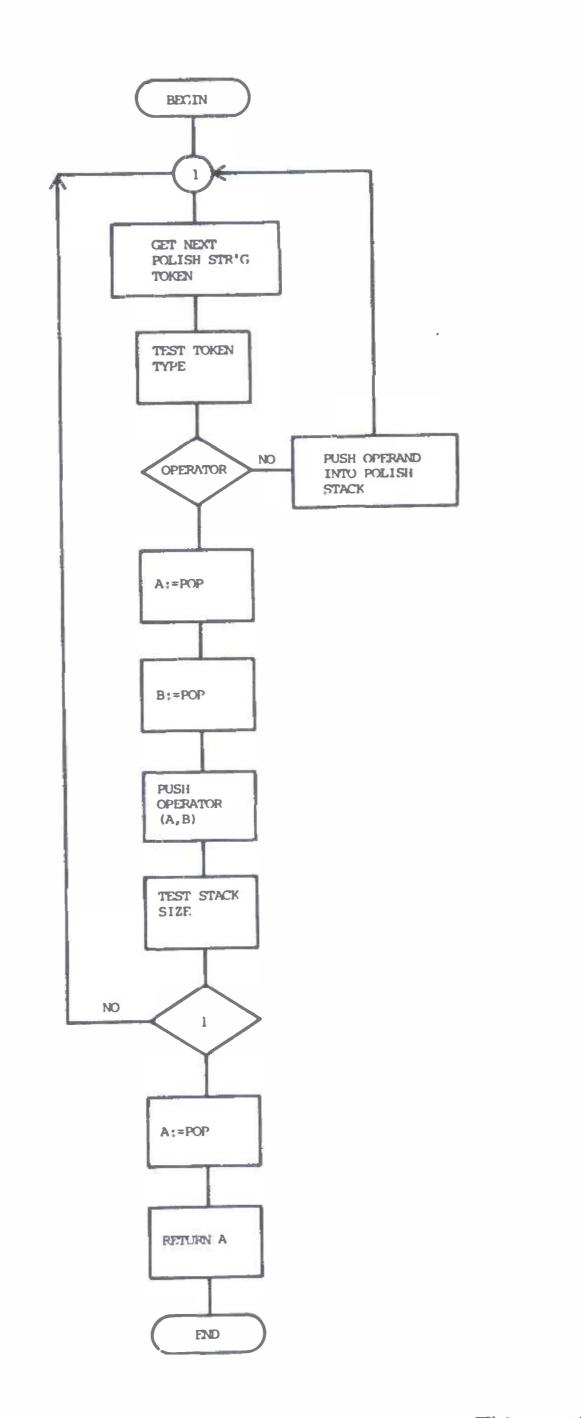

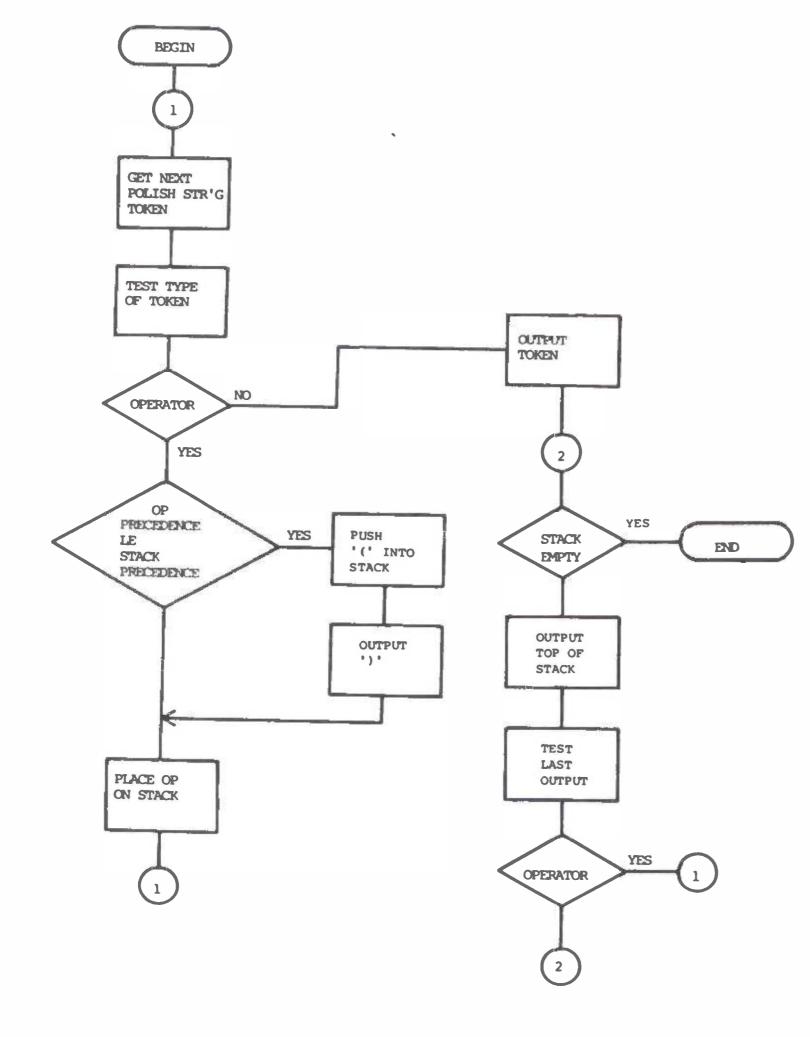

| Processing Algebraic Expressions — Maurer                         | 275 |

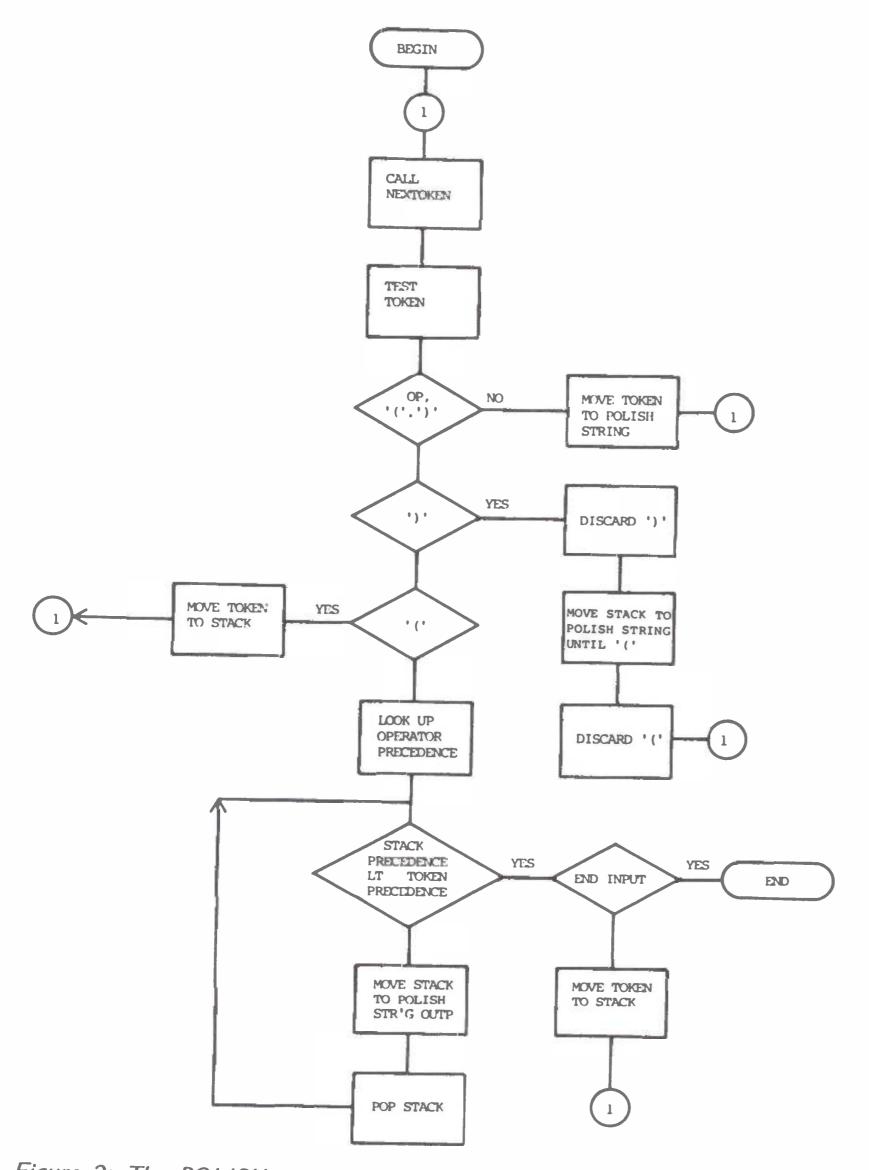

| The "My Dear Aunt Sally Algorithm" — Grappel                      | 286 |

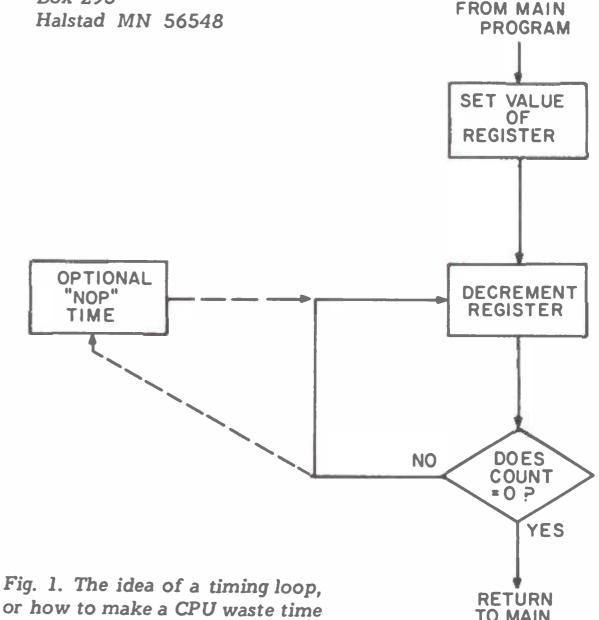

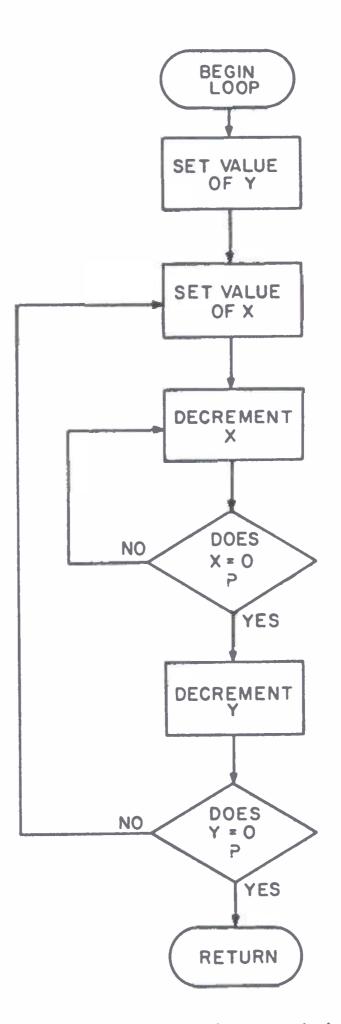

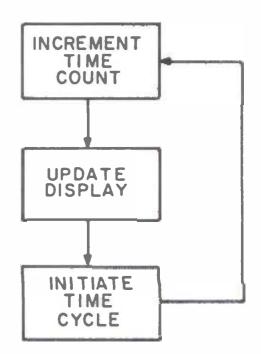

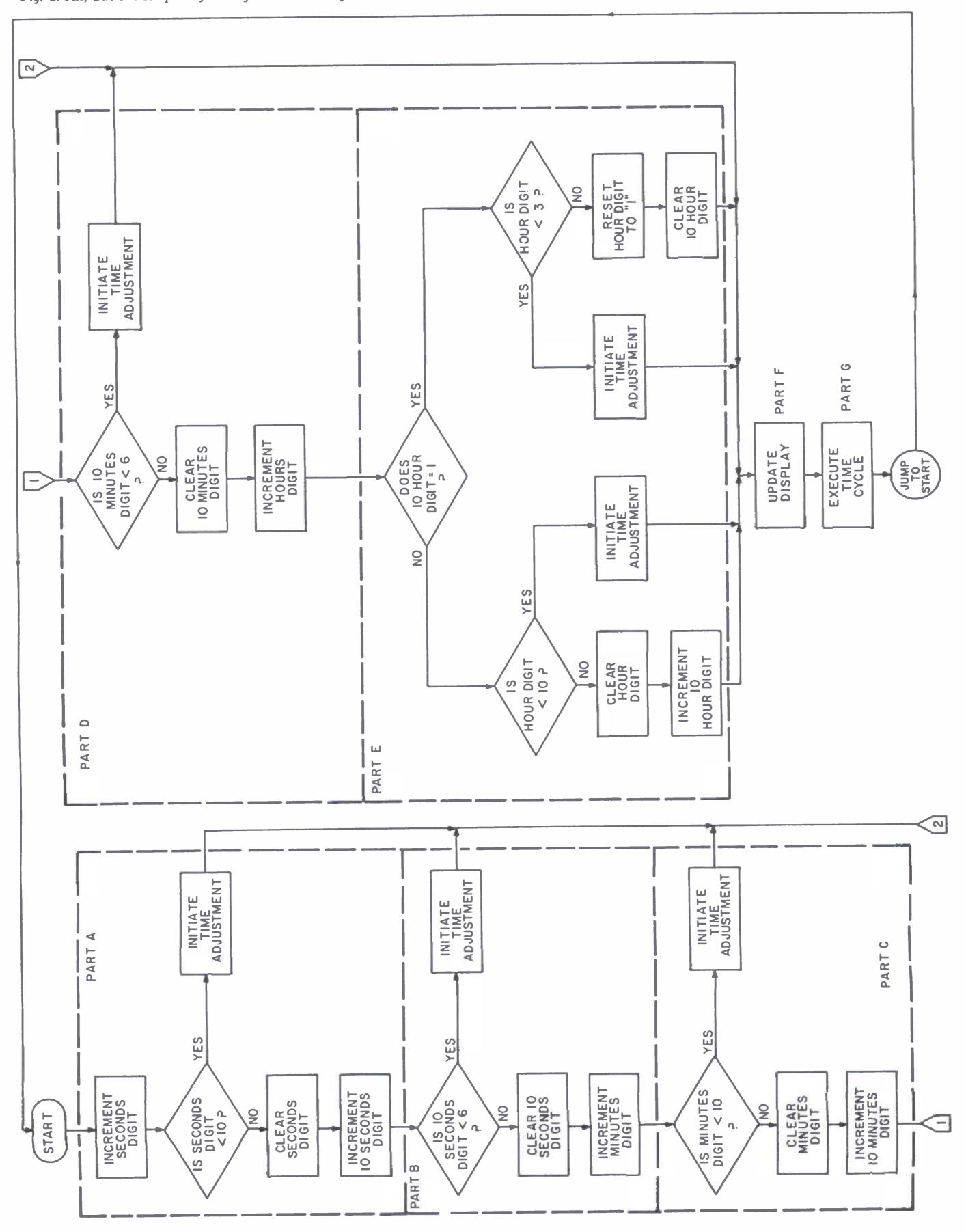

| Can YOUR Computer Tell Time? — Hogenson                           | 294 |

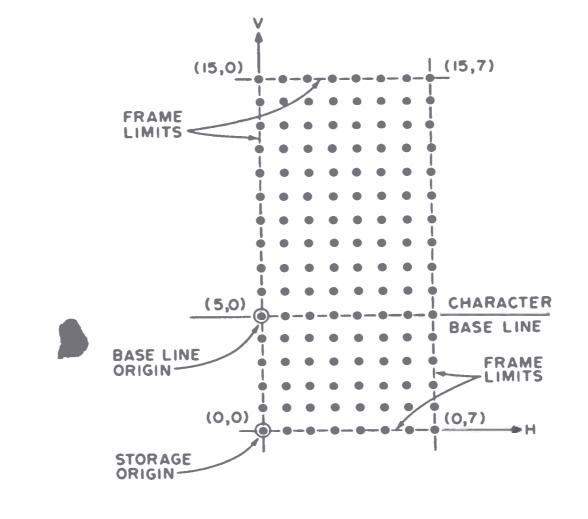

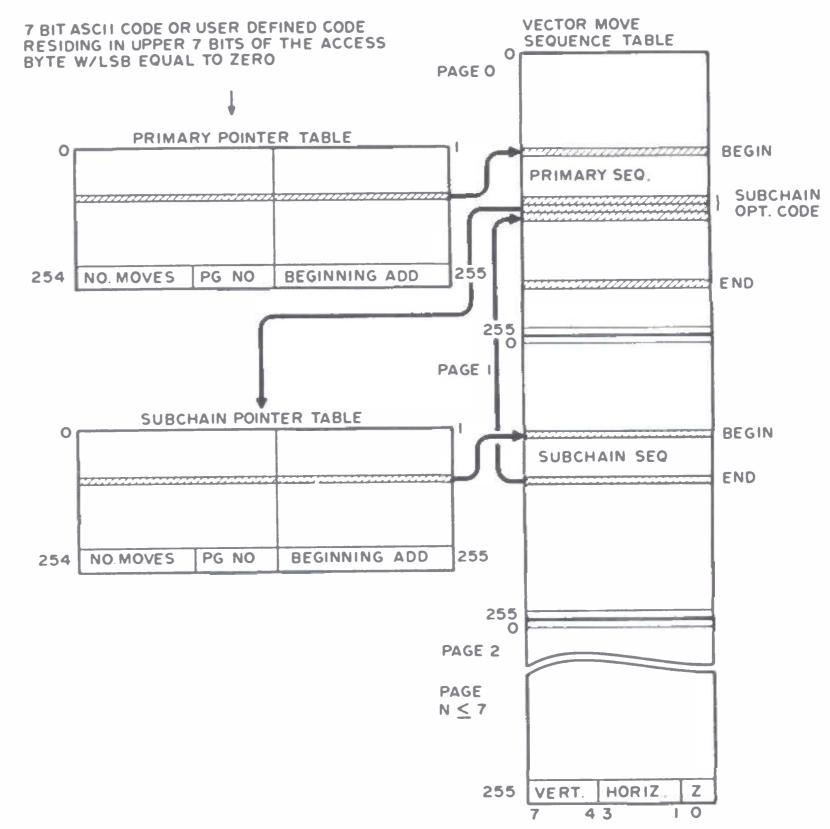

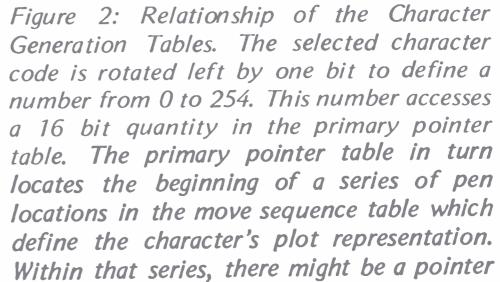

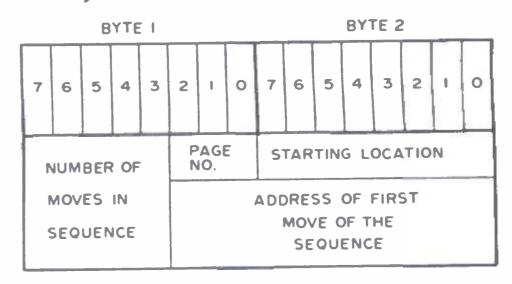

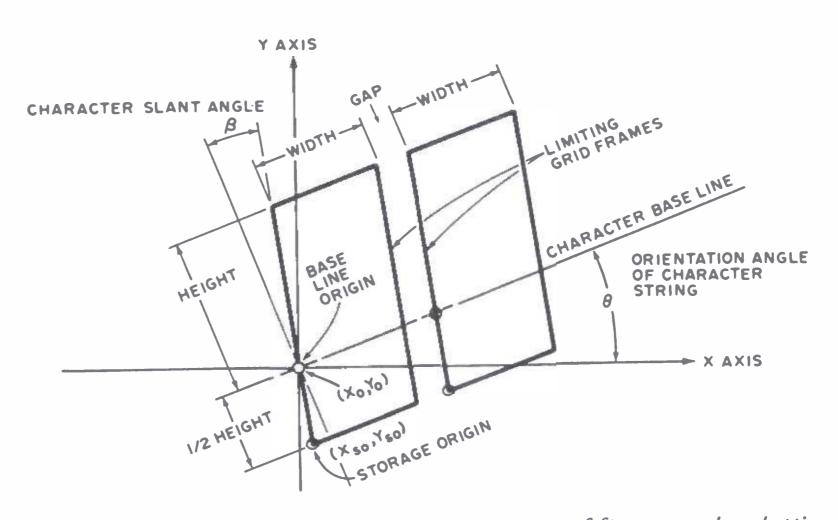

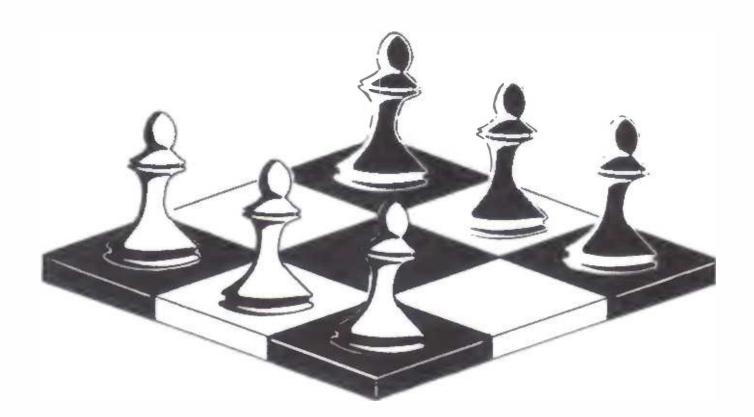

| A Plot Is Incomplete Without Characters — Lerseth                 | 300 |

| Hexpawn: A Beginning Project in Artificial<br>Intelligence — Wier | 309 |

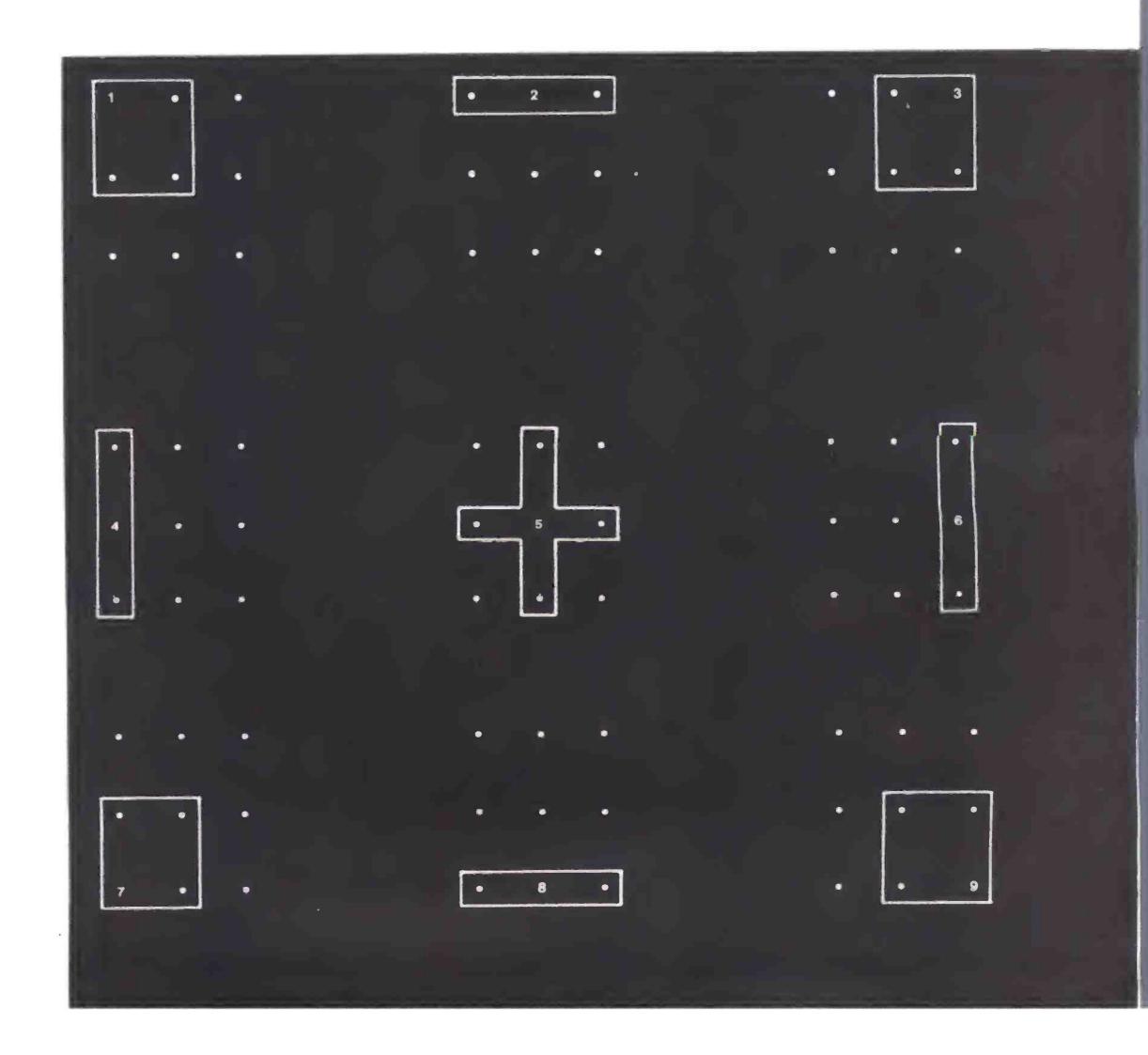

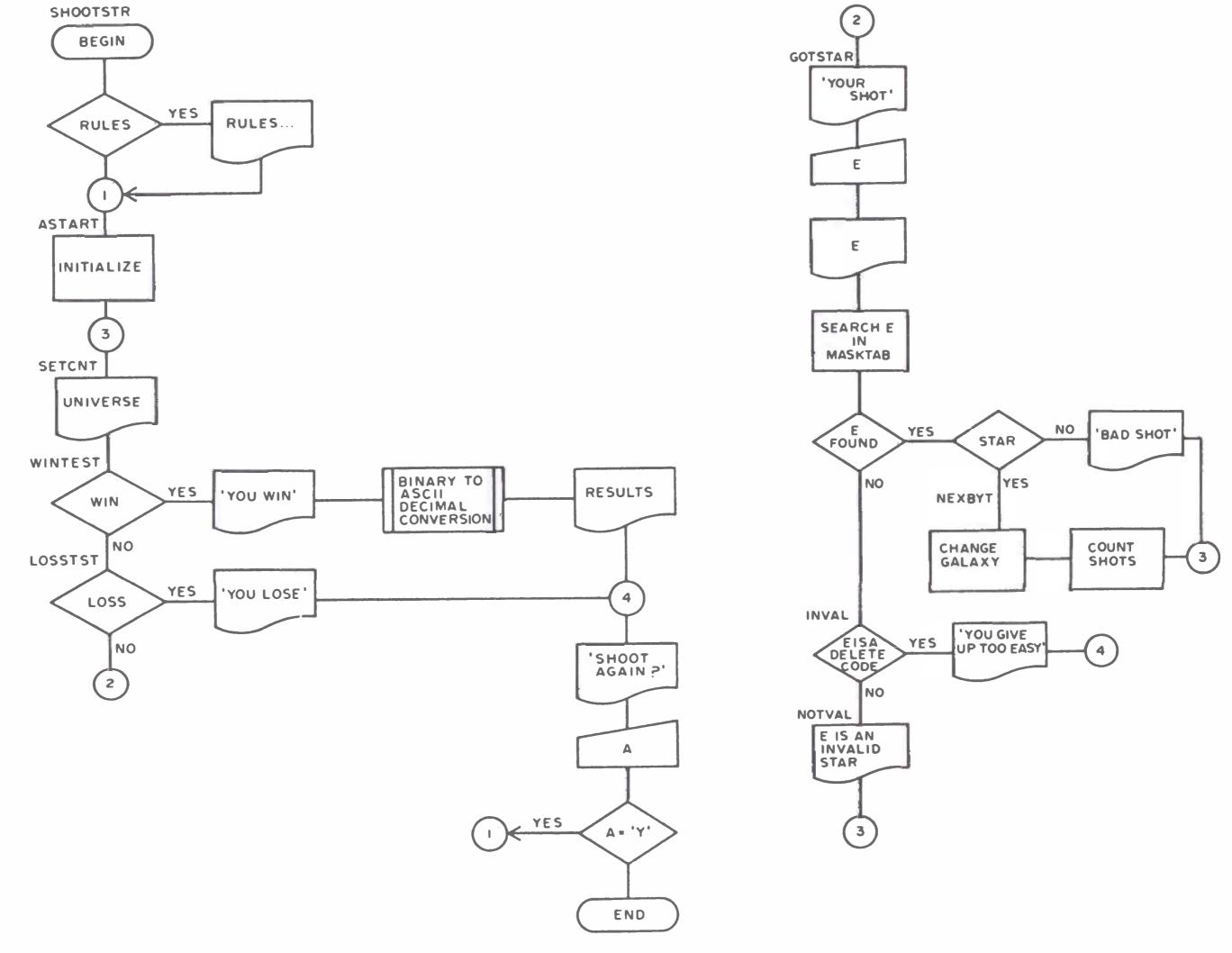

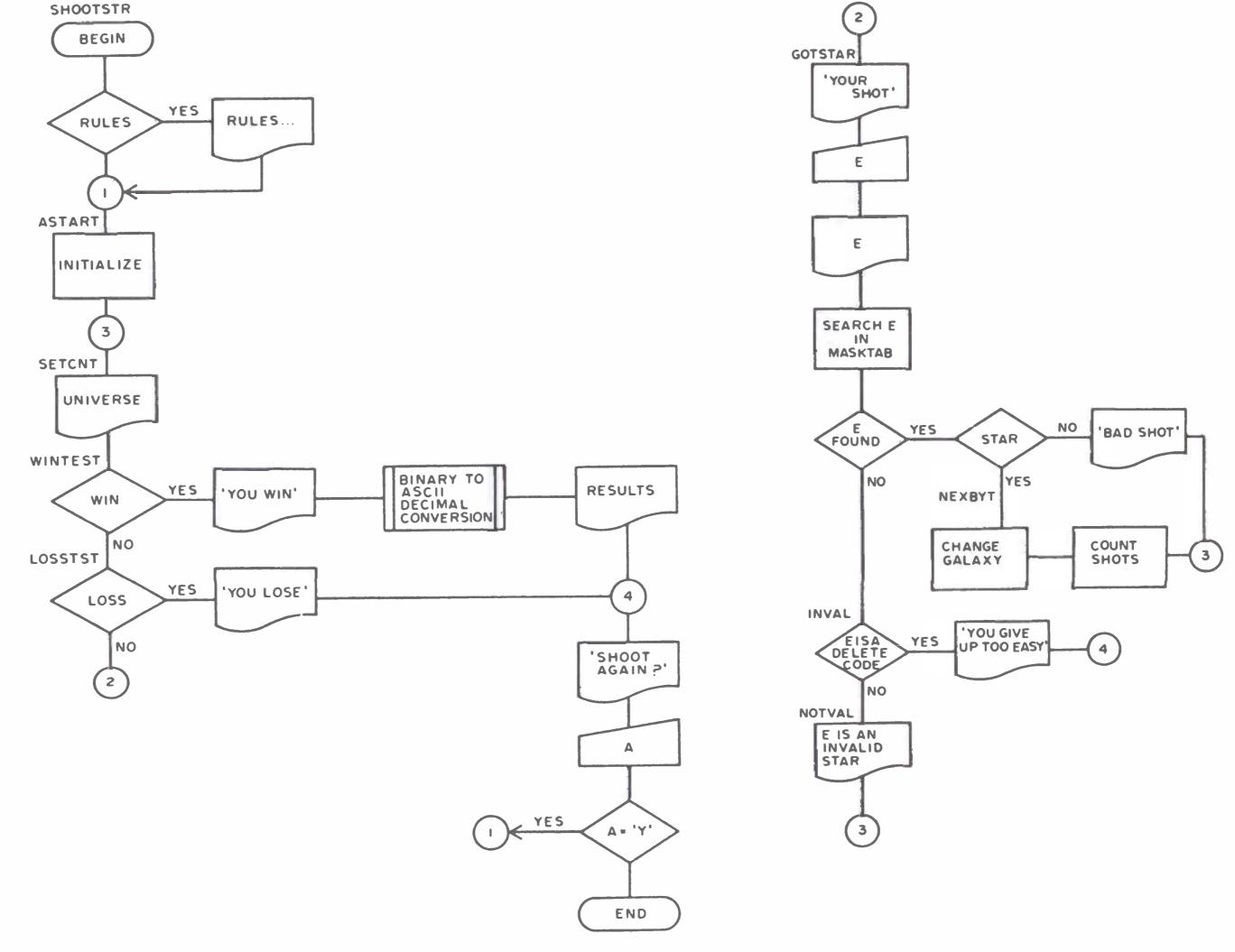

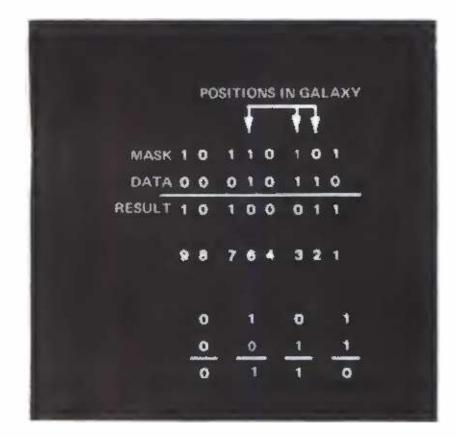

| Shooting Stars — Nico                                             | 314 |

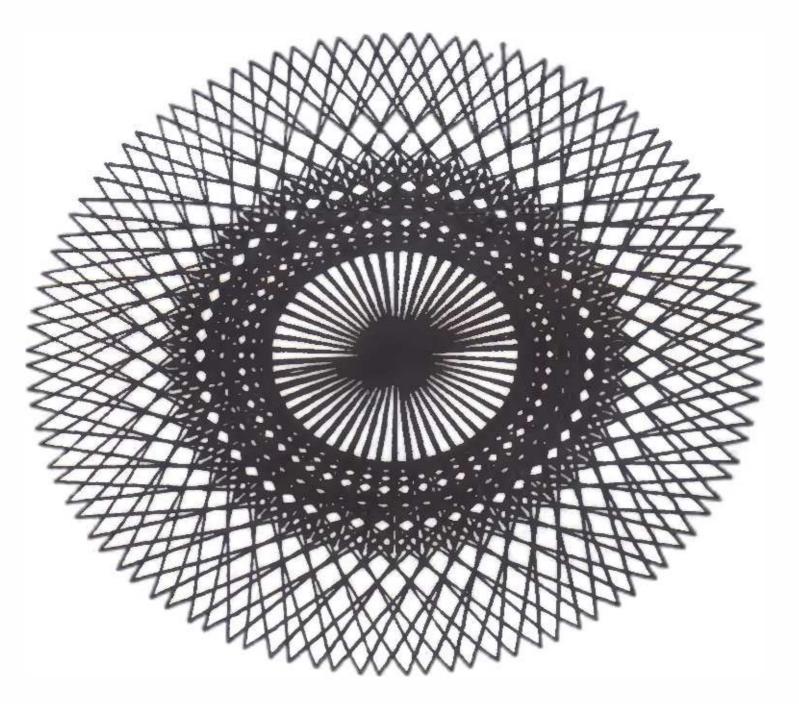

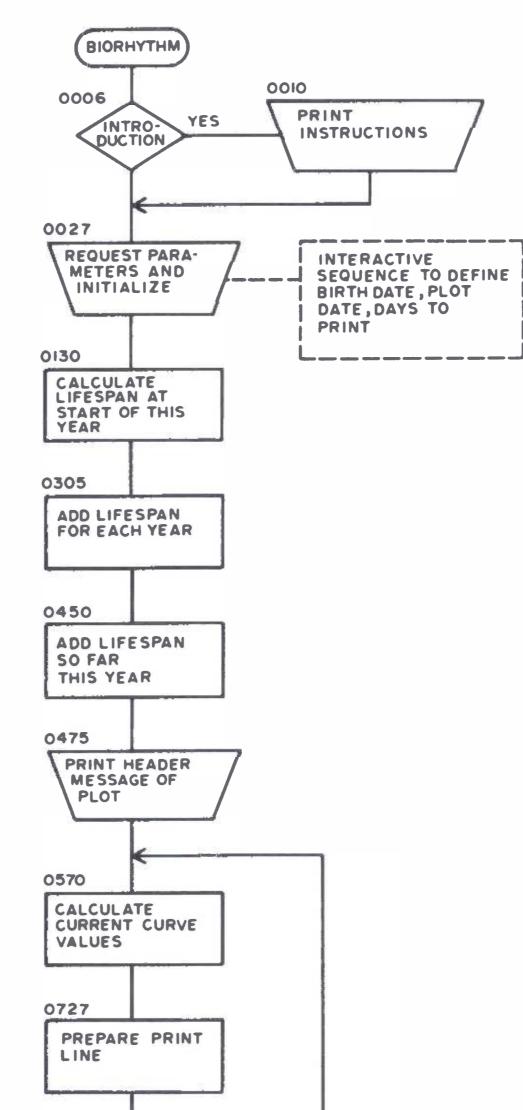

| Biorythm for Computers — Fox                                      | 322 |

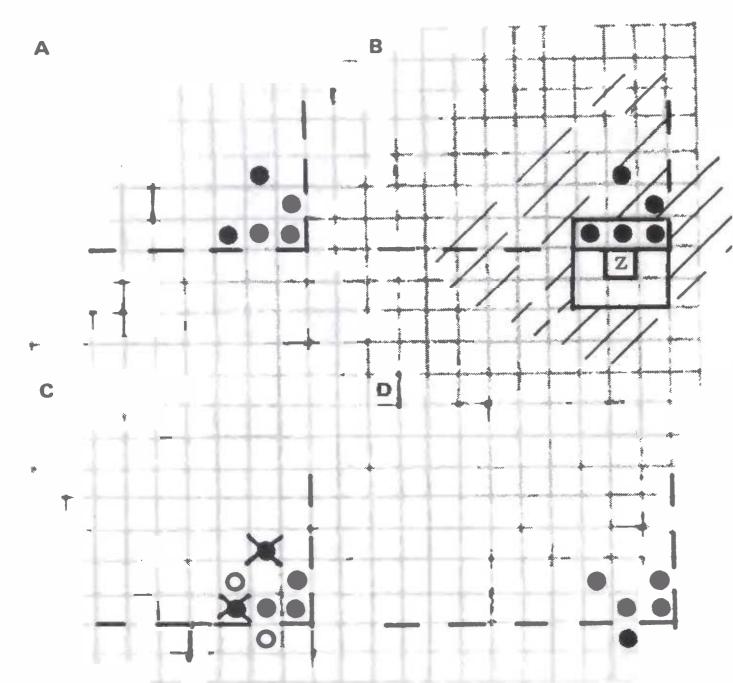

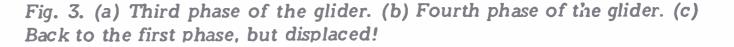

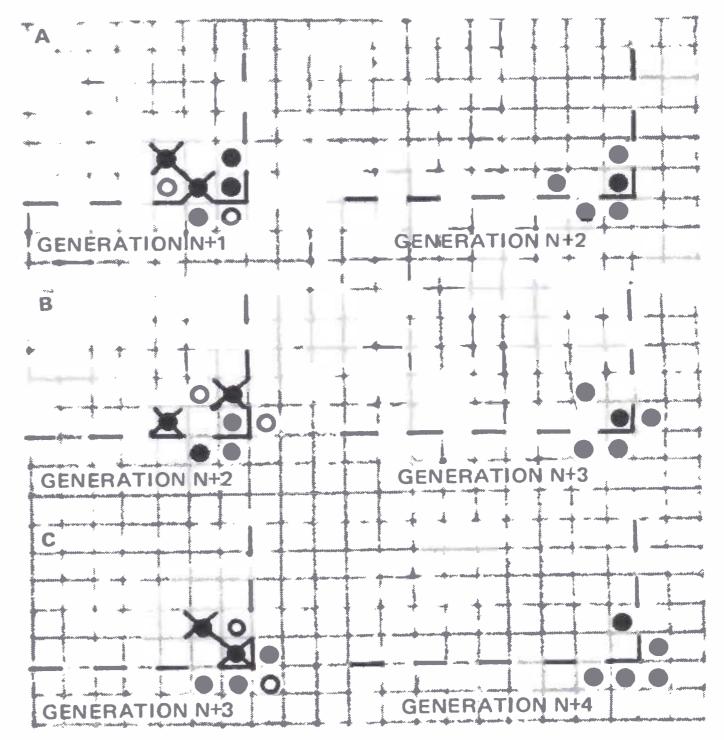

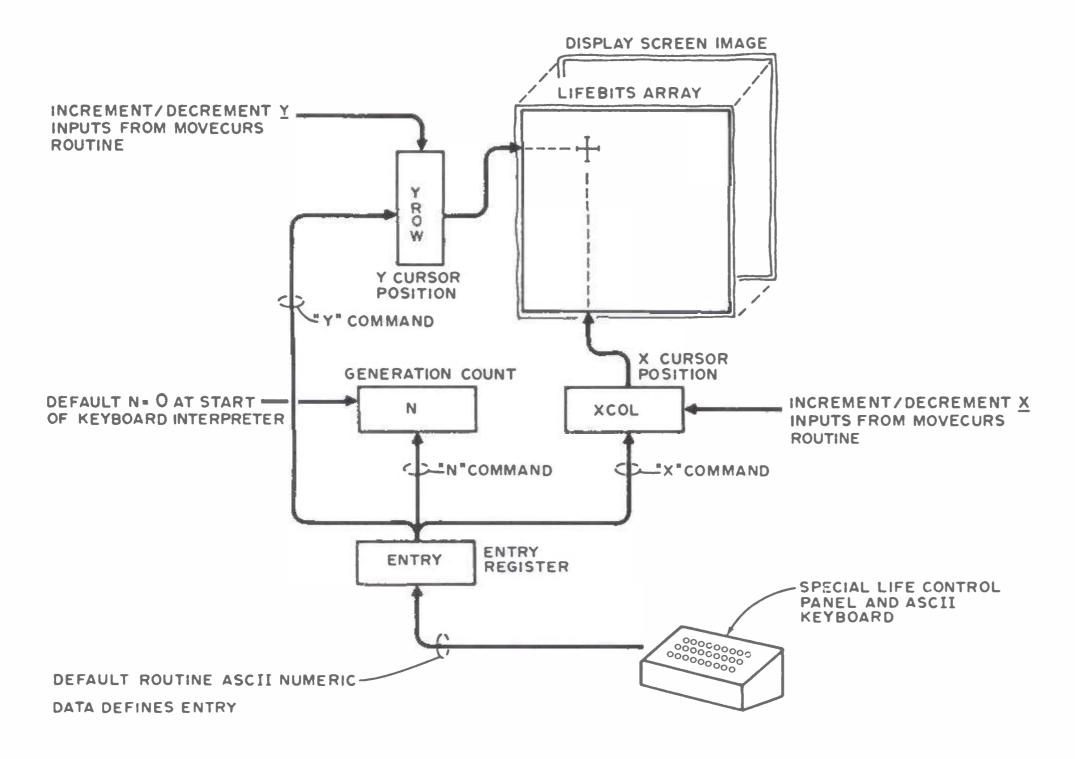

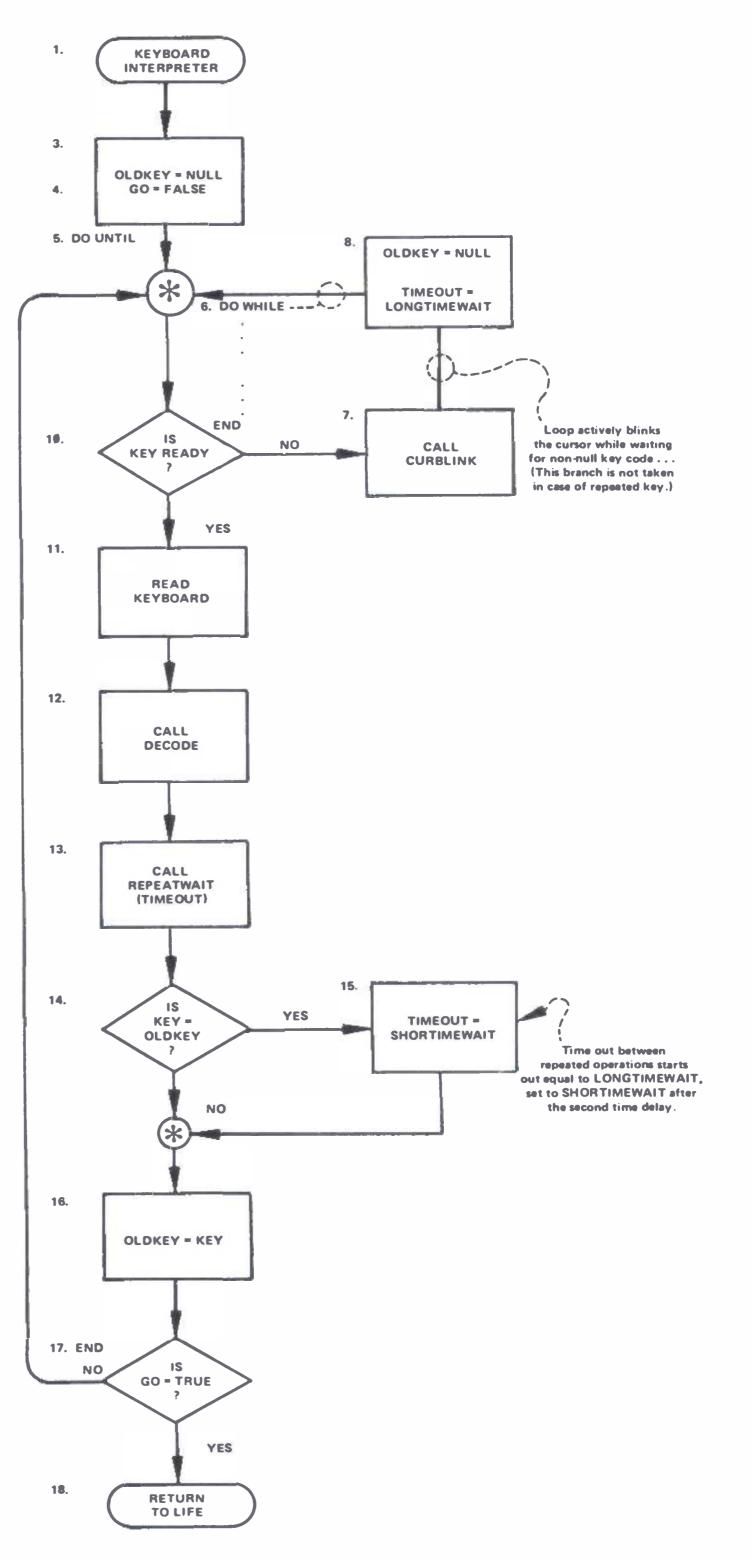

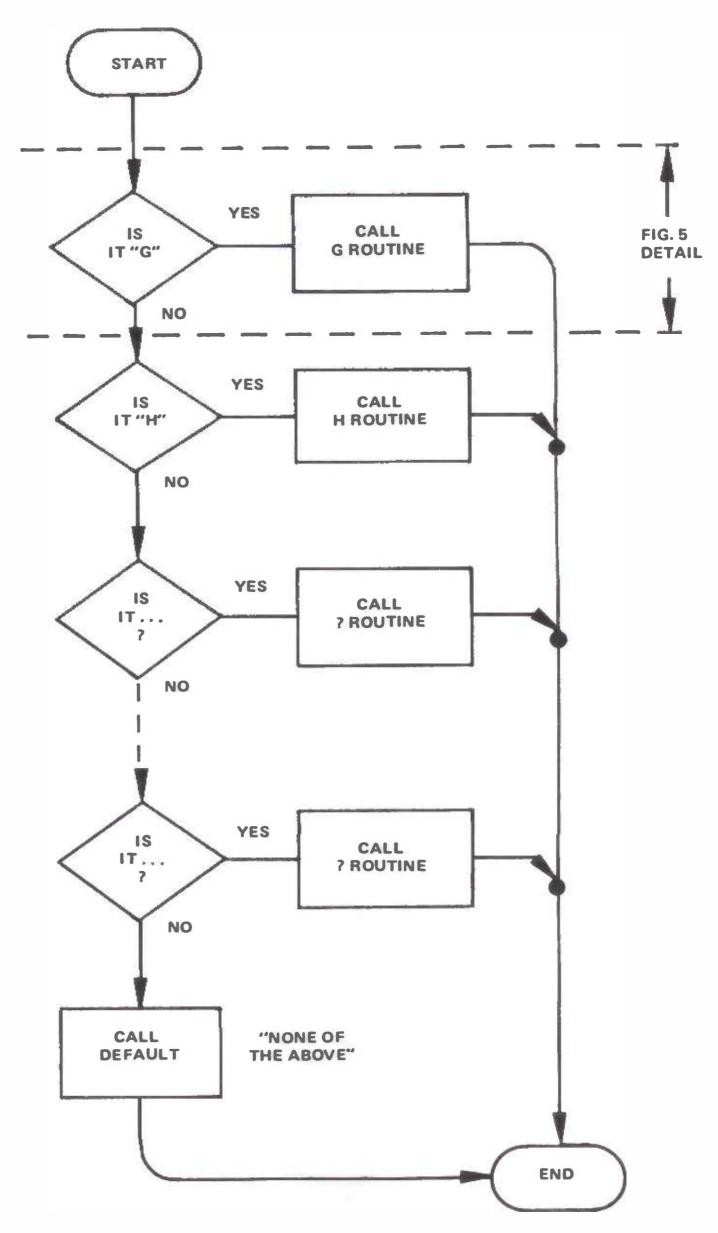

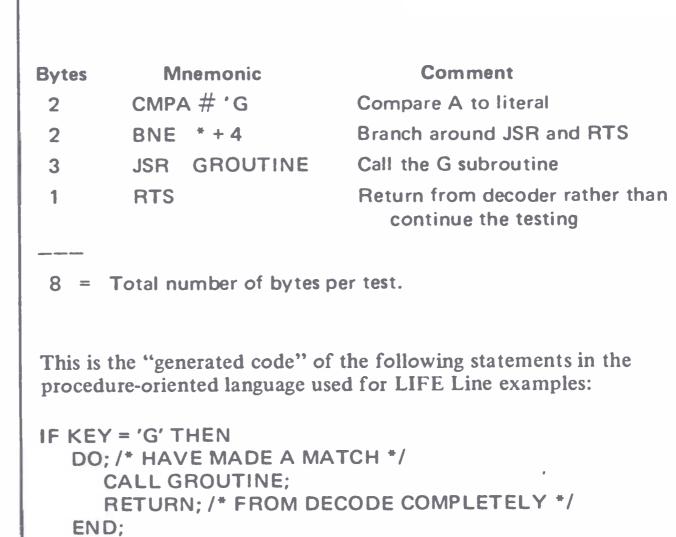

| Life Line — Helmers                                               | 326 |

|                                                                   |     |

### APPLICATIONS

| Total Kitchen Information System – Lau              | 360 |

|-----------------------------------------------------|-----|

| A Small Business Accounting System — Lehman         | 364 |

| Chips Found Floating Down Silicon Slough — Trumbull | 369 |

### RESOURCES

| Books of Interest | 372 |

|-------------------|-----|

| Magazines         | 375 |

### Opinion

# The Shadow, Buck Rogers, and the Home Computer

by Richard Gardner Box 134 Harvard Square Cambridge MA 02139 A computer at home? Ask many present day computer systems people what they'd do with a home computer and you'll get the old silent treatment in return. But all that indicates is a lack of imagination. A large part of the BYTE philosophy is the discovery of applications areas through the imaginations and practical results of readers. Richard Gardner supplies us with a "Gee Whiz" article on potential applications areas to get things in motion a bit. Richard has extensive computer applications experience including one stint working for the Children's Museum in Boston, creating interactive computer oriented exhibits. Eventually, many of the systems ideas Richard mentions in his article will appear as practical plans and programs in the pages of BYTE – as developed and described by our readers. If you'd like an interactive meeting Ah yes! It conjures up visions of an earlier day, many years ago, when Mom, Pop and the kids sat around that newfangled gadget, the radio, and listened to "The Shadow" and "Buck Rogers."

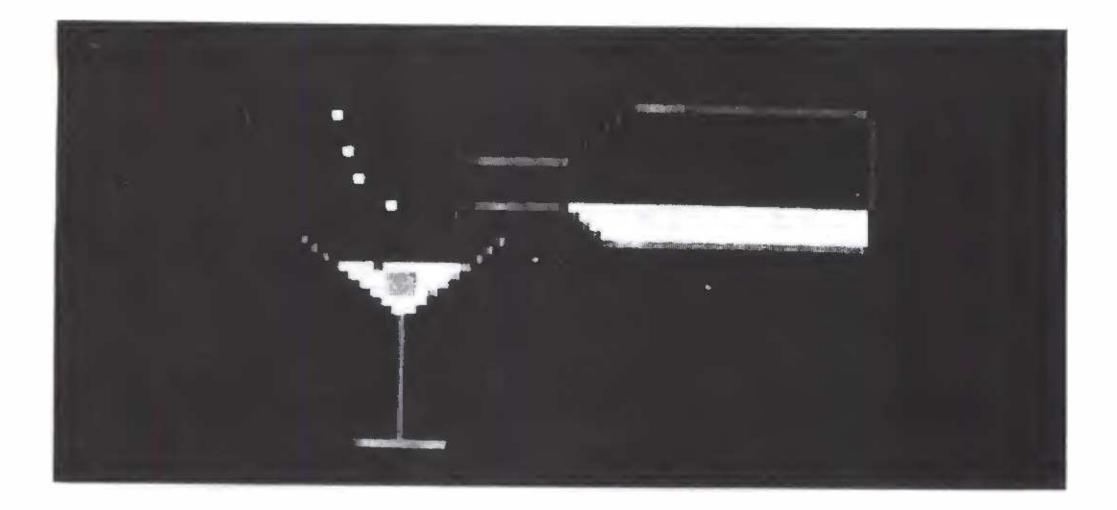

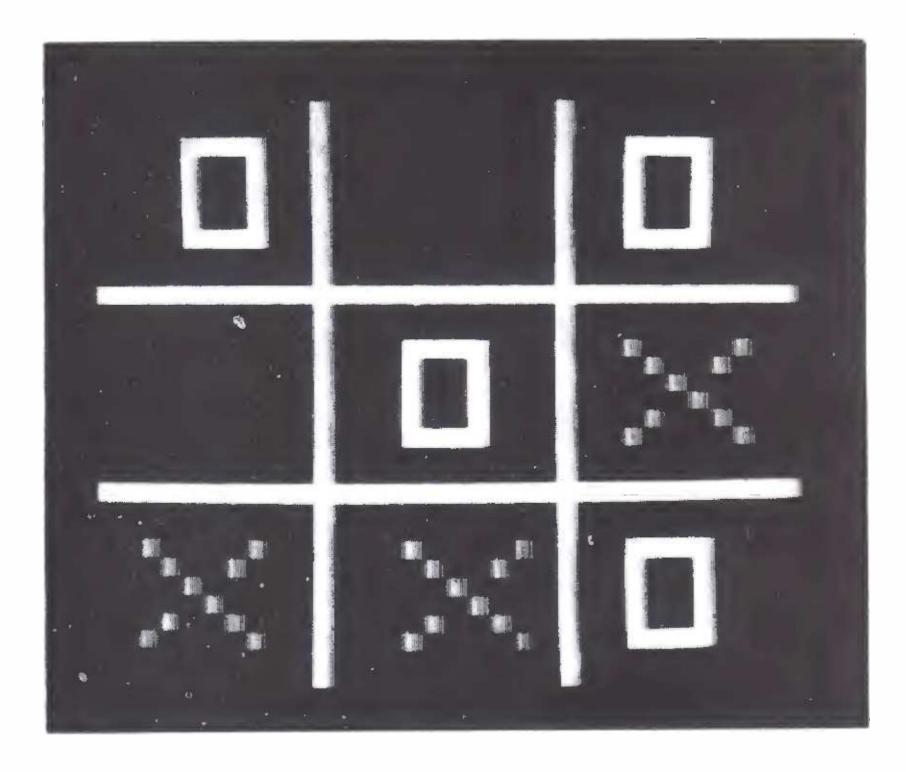

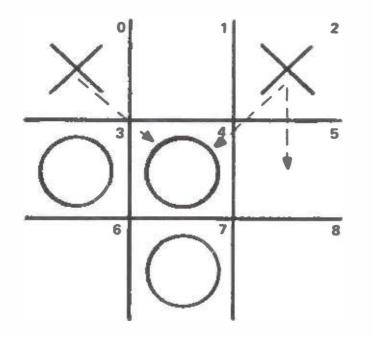

Flash forward to the future, right now! Again, we see Mom, Pop and the kids sitting around that newfangled gadget, the computer, balancing a checkbook, converting a four servings recipe to seven, and playing tic-tac-toe. Not very exciting things to do with a computer, you say? Well, you're right. But let's see if we can do something to make it at least as exciting as old-time radio.

We mentioned three applications for a home computer:

1) checkbook balancing

- 2) recipe converting

- 3) game playing

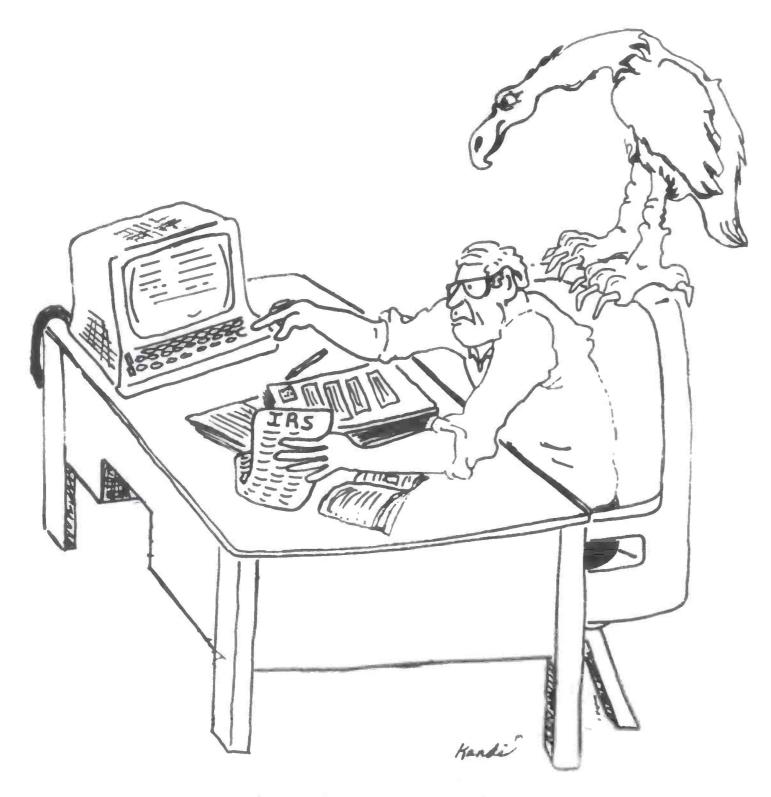

For starters Mom and Pop should have a program for collecting and summarizing all their financial data, on a daily, monthly and yearly (for your "friend" and mine, the IRS) basis. A family will be more secure by knowing the state of its financial affairs. You will want to

of the minds on possible uses and ideas, Richard invites correspondence from readers. ... CARL

compute interest for different purchase plans, and balance the checkbook.

Moving on to a subject close to my heart (just below, and a little to the right) food. Almost anyone can convert 4 to 7 servings – just double it and feed the leftovers to the dog, or give it to a charitable organization (tax deductible, of course). What you really want to know is whether everyone got enough nutrients (vitamins, minerals, protein, etc.) from what they ate today. Hint: it can be done. I know of two people who started a small company to do it.

On to fun and games hundreds of game playing programs have been written (I invented one called YOUGUESS) for all sorts of computers and languages. You should have them all. It will win friends and influence neighbors, if you'll pardon the pun.

I'd say that's at least as exciting as old-time radio. Good, but we can do much better. Let's consider three things:

1) Today's computers are very fast. The applications we've mentioned might take day, at the very most. So what do we do with the other 23+ hours?

energy use. Open and close curtains on windows to use the sun's energy or keep it out.

2) Security. While you're at home or away, monitor the opening and closing of windows and doors. Automatically telephone the police with a recorded message when you're gone or at home. Monitor the use of your swimming pool - sound an alarm when the pool is in use and nobody's in the lifeguard seat. Fire monitoring equipment can be located in many places and sound an alarm long before you might smell or see

Using a Symbol Table to Improve the Food Table

Most people in America have a poor diet in spite of the fact that we have more food of a better quality and variety than any other country. So I consider the following to be important uses for a home computer:

1) Selection of foods on a seasonal basis to reduce cost and improve quality. A program for doing this would run for a year and use a data base for your area (to take advantage of local produce). A second data base would be programmed for widely

one hour of CPU time per smoke. The fire department available foods and when can be called automatically they are best and cheapest. with another recorded 2) A menu building program to take advantage of message. the above system but with These applications will make use of photocells, the intention of increasing variety and maximizing theramins (motion sensing nutrition.

Since your computer won't be doing anything most of the day . . .

This application, like others mentioned, would use the telephone system – the world's largest computer. I can see it now. The kids get home from school and ask, "What's for dinner, Ma Bell?"

The Bottom Line Isn't Always an End Statement

Or, how to profit from your home computer:

1) Income management, as previously mentioned, but with the help of another computer. Several computer companies that do nothing but figure taxes (for you know who!) already exist. Eventually they will allow your computer to call their computer. Your computer shovels in a year's data and out pops a tax form with all the right numbers. You might think it easier to do your own programming, but remember that you can't write every program you will want to use. In addition, these companies have staffs that do nothing but make program improvements and changes required by the IRS. What person in his or her right mind could possibly keep track of a myriad of new rules from the IRS? 2) Play the ponies or the puppies? An obvious use for your computer. Again, use a data base compiled by some local eager beaver. Perhaps you'd be charged a small fee for accessing the day's statistics. Perhaps you have a data base or program to trade.

2) There are lots of computers in the world, and they can talk to each other.

3) Computers can hear, see, feel, smell and touch.

Keep these things in mind as we consider what might be called economic, personal and educational applications for the home computer.

### Computerizing the Home

Since your computer won't be doing anything most of the day why not put it to work:

1) Heating and air conditioning control. Optimize increases and decreases in the inside temperature to minimize

devices), heat sensors, contact switches, smelling devices (like those used by the Defense Department in Vietnam to smell passing elephants and tigers). Eight bits might be used to represent a temperature range of 256 degrees. 100 degrees would be adequate for most locations. One analog to digital converter could be used for other analog inputs, such as from a photocell. A digital to analog converter would generate voltages to be used by motors and other mechanisms.

3) A shopping guide to take advantage of local food supplies by indicating the best one or two markets from which to purchase your food. This data base might be maintained by some person in your locality – and then rented on a per use basis. No sense in everyone typing in today's price for cumquats. Perhaps the New York Times will eventually computerize its cookbook, plus thousands of other recipes, and allow the public to access this data base via a personal computer.

3) Then there's always the world's biggest daily crap

game - the stock market. A company in Philadelphia will charge you \$300 a year for a small numeric terminal and 24 hour a day access to their stock data base. You key in the number of a stock and out pops the high, low, average, etc. Your computer could make one call after each trading day, collect the stock data you're interested in, hang up, and then determine if you should buy, sell or hold. The decision making could be done by your program or one being rented from a stock market wizard you know. 4) I mentioned how a computer could be used to optimize the purchase of food. This principle applies to any commodity whose price

and quality changes during the year: clothes, home furnishings, gifts, transportation, even housing. Some local person, or you, could create the necessary commodity and price data bases, then use or rent them.

Remember! There is a host of areas for small business activities using your home computer as a tool of the trade. All it takes is imagination, a bit of digging into the wants and concerns of your neightbors, and the programming of your computer. stories, financial page stories, or any story that contains a k e y w o r d o r s o m e combination of keywords. This would be done early in the morning and read by you at breakfast time.

2) Your local university or high school might have a computer with courses that can be taken via a remote terminal. Many universities already give some courses using only this method. used to play Space War — the Grandpa of computer games! Your computer, a TV set, a few buttons and switches and, presto — Space War! Or ping-pong, or driving down a road, flying and landing an airplane, landing on the moon, chess, checkers (you can play these games in Boston with the Children's Museum computer).

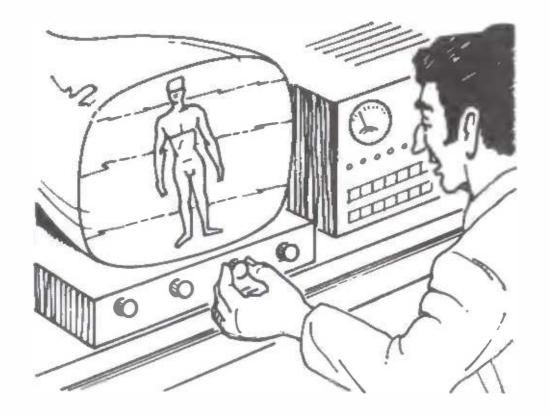

2) Toys that play with you - like robots. The Boston Children's Museum has a robot that was built for about \$200. Mass production of a special chip and board will bring that cost down. Then the biggest cost will be the Meccano Set (like an erector set, only better), which can be used to build almost any sort of mechanical device. How about a robot to do housework?

3) The ultimate fun, though, is to write your own programs to do all these things! Kids, and adults, will play only so many games of tic-tac-toe – then they want to know how it works. Help them write their first BASIC program . . . and they're likely to be hooked for life! Eventually programming will include a broader range of input/out devices such as the previously mentioned buttons and switches, photocells, microphones, etc. This will lead to the applications just discussed, and who knows what? These are just some of the possible applications for a home computer. All of them might not be reasonable or practical things to do but they should set you to thinking. As future issues of BYTE unfold, the Gee Whizzers applications will lead to practical articles on the software and specialized peripherals needed to implement some of these ideas.

Six Munce Ago I Couldn't Even Spell Computer Programmmer...

Computers are good for keeping you in touch with the world. For example:

1) The New York Times has a computerized data base of all its back issues currently accessible to the general public, for a fee. The cost will probably go down to the point where you might program your computer to query the *Times* data base and retrieve front page 3) The Children's Museum in Boston will eventually allow you to call their computer, via a terminal or computer, and access a data base of cultural, educational, and social events in the Boston area. Your computer might call theirs once a day to learn what's new or learn about a particular type of event.

### **Computers As Toys**

Computers are probably the greatest toy ever invented. Here are some examples of how you can play around with yours:

1) It has been rumored that 50%, or more, of the computer time used at MIT is

### Carl Helmers

## The State of The Art

If there is one facet of the small computer field which is its most exciting, that is probably its rapid change and evolution unfolding before all us users of the technology. The fact that a magazine such as BYTE can even exist (let alone get its enthusiastic reception) is evidence of the considerable changes which have occurred in the home computer field over the past year or two. Any attempt such as this to characterize the current "state of the art" is doomed to rapid obsolescence. Be that as it may, I won't let that deter me from characterizing the field as I see it now.

Just what is this "art" that I'm talking about? When I talk about art in this sense, I mean the body of technological know-how available for personal computing plus the attitudes and abilities of the people who use this know-how. An analogy or two: The state of the art in a form such as painting reflects both the latest developments in the pigmentation materials field and the creative talents and attitudes of the people who use this technology for

expressive purposes. The state of the art in music is a combination of the technology of music production - traditional to electronic/digital – plus the aesthetic and creative tastes of the musicians and composers who use the technology. So it is as well with computing. There is the technological state of the art as it exists – a transient thing at present - together with the creative uses to which people such as you or I put these wonderful technological devices.

### A Recent State of the Art ....

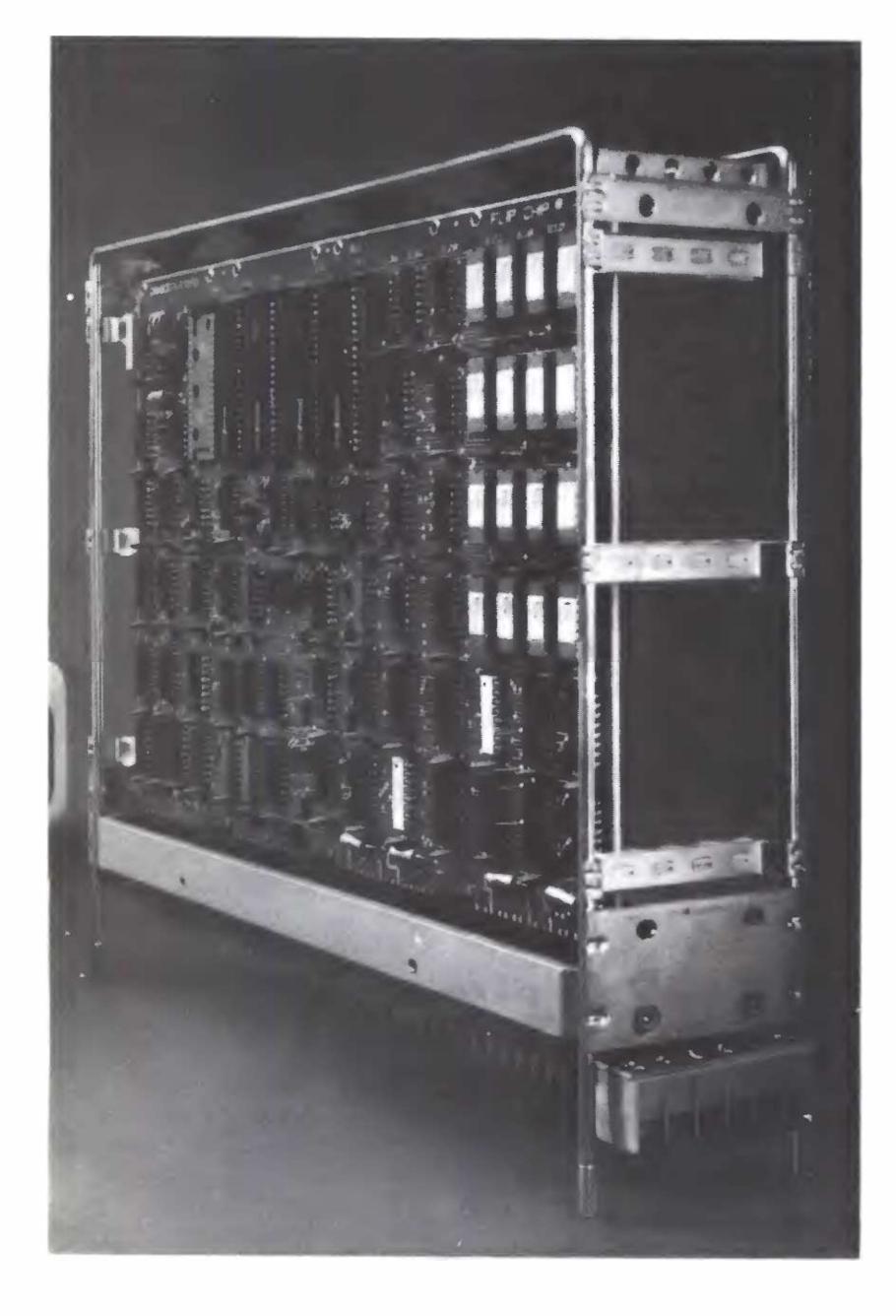

A few years ago, the state of the art in hardware was pretty primitive — in other words, one had to be a really persevering person to get something in computing which worked and cost less than \$1000. To give you an example, I got a call from Dick Snyder of Chelmsford, Mass., shortly after BYTE #1 came out. (See Dick's letter in the letters column of this issue.) As a result of our conversation, I stopped at Dick's house on the way back from Peterborough one weekend in August and took a look at his premicrocomputer home brew computer, a really beautiful piece of work. He had completely designed and built - in 1972 and 1973 - a miniature 4-bit computer with 256 nybbles of memory using the Data General NOVA minicomputer as his inspiration. He built the machine using painstakingly accurate soldering with a miniature iron, sockets for over 170 integrated circuits,

and a very compact housing. The most unusual feature of all was the use of water cooling to keep his 16 7489 memory chips cool (said water cooling consisting of plastic bag baby bottles filled with water and sealed with rubber bands). Yet it works! And - he has built up quite an impressive array of software for his one-of-a-kind machine, including a very appealing simulation of a priority-driven real time operating system with three tasks in the queue. The entire program for this simulation is done in 256 nybbles (half-bytes) of memory with the 16 instructions of his design. The result is an impressive changing display of marker patterns in his front panel lights as the various tasks swap in and out of execution. Dick Snyder's machine is the state of the art, circa 1972-1973, to a large extent – microcomputers were not yet widely available to the general populace of personal computing hackers. Dick tells me that he spent about \$600 on the parts of his computer at 1972 prices for SSI and MSI TTL integrated circuits. But now, in 1975 after the first wave of 8008 computer kit products and the rising tide of the "first generation" personal computer systems, that same \$600 can buy a lot more function. In 1975 we saw the introduction of the MITS ALTAIR – which turns out to be a very good computer after initial slow deliveries due to unanticipated demand – and a host of new machines such as Bill Godbout's PACE, the

SWTPC 6800 kit, the MITS 6800 kit and several other systems.

### The Benchmark of a Small Computer System

In the engineering and software professions, it is often common to dream up "benchmarks" to help in the evaluation of systems. This term, benchmark, was adopted by systems engineers from its original use in the field of geodetic surveying. A geodetic survey benchmark is a permanent marker set "out in the field" (literally) at known locations during the course of the survey. If you clamber to the top of Mt. Chocorua in New Hampshire, as I sometimes do, when you get to the top you will find a little metal plate giving elevation, longitude and latitude information. This is the benchmark for the mountain's peak. Well, the benchmarks used for computer systems are a little bit less concrete than a metal plate on a mountaintop, but serve the same purpose: They provide a reference point for comparison. A common benchmark which has been used in the past to evaluate computer systems (and compilers) is the "standard set of programs". In this method of benchmarking a system, the potential user of the system picks a set of "typical" applications programs and has them implemented and measured in operation on several different systems. This is a fairly quantitative and seemingly accurate method which is widely practiced in the information systems

Any attempt to specify the state of the art in this field is doomed to practically instant obsolescence . . .

industries. The measurements made for comparison include "through-put" (processing per unit time), high level language efficiency, memory requirements, etc. But this sort of a measure is perhaps a bit too complicated for the home computer context. For one thing, the applications are known only generally. Second, this is the type of study which takes a large amount of time and access to various competitive systems. And, if you read the trade journals, the results are often controversial anyway, since each manufacturer will claim that the benchmarks he provides will prove his machine better than all the rest. Picking the "ideal" small computer system still requires a benchmark, but I suggest it is not a particular program, but a *capability*.

### Capability – the Benchmark of a Small System

We all know that in broad terms, the benchmark computer system, as any computer system, must include several major components: a processor, memory, a mass storage medium, an interactive operator's terminal and systems software. I pick this list in part to illustrate a typical computer configuration and in part to allow programming of a benchmark capability:

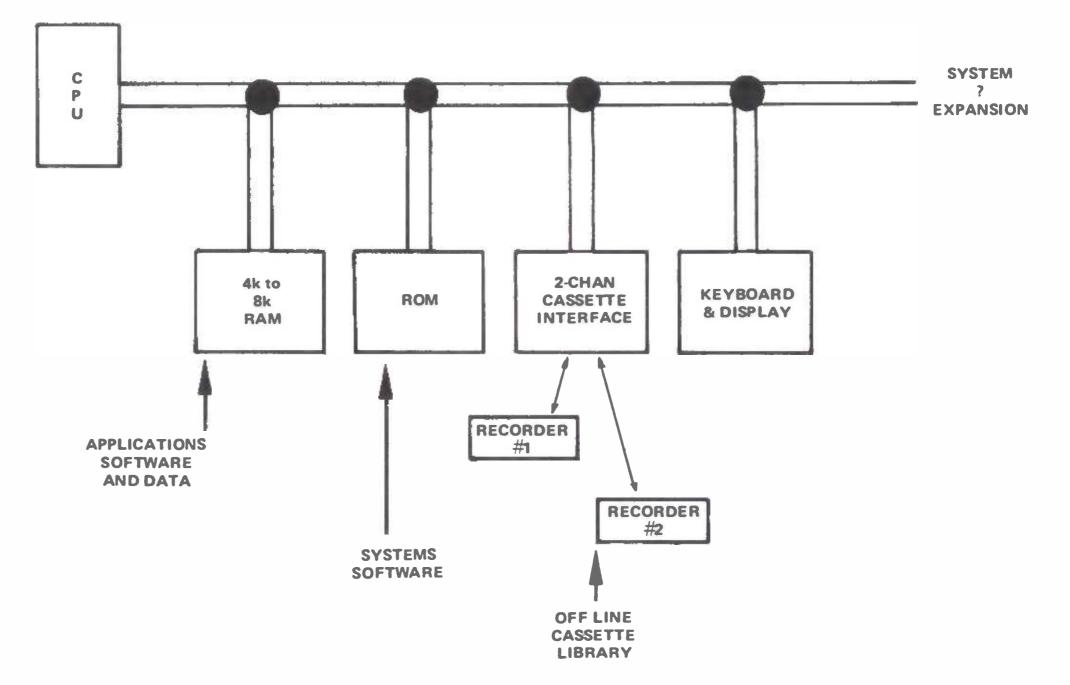

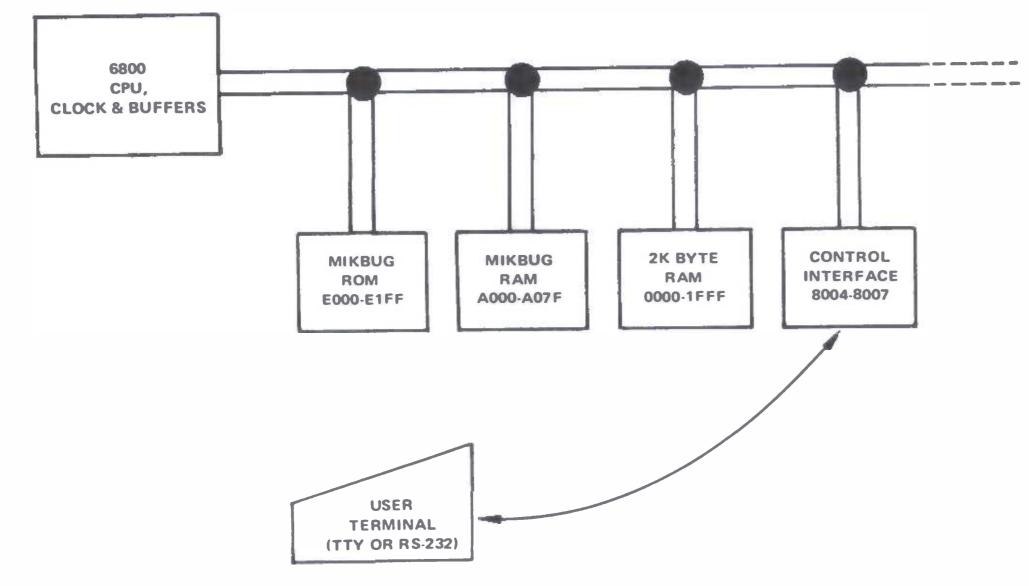

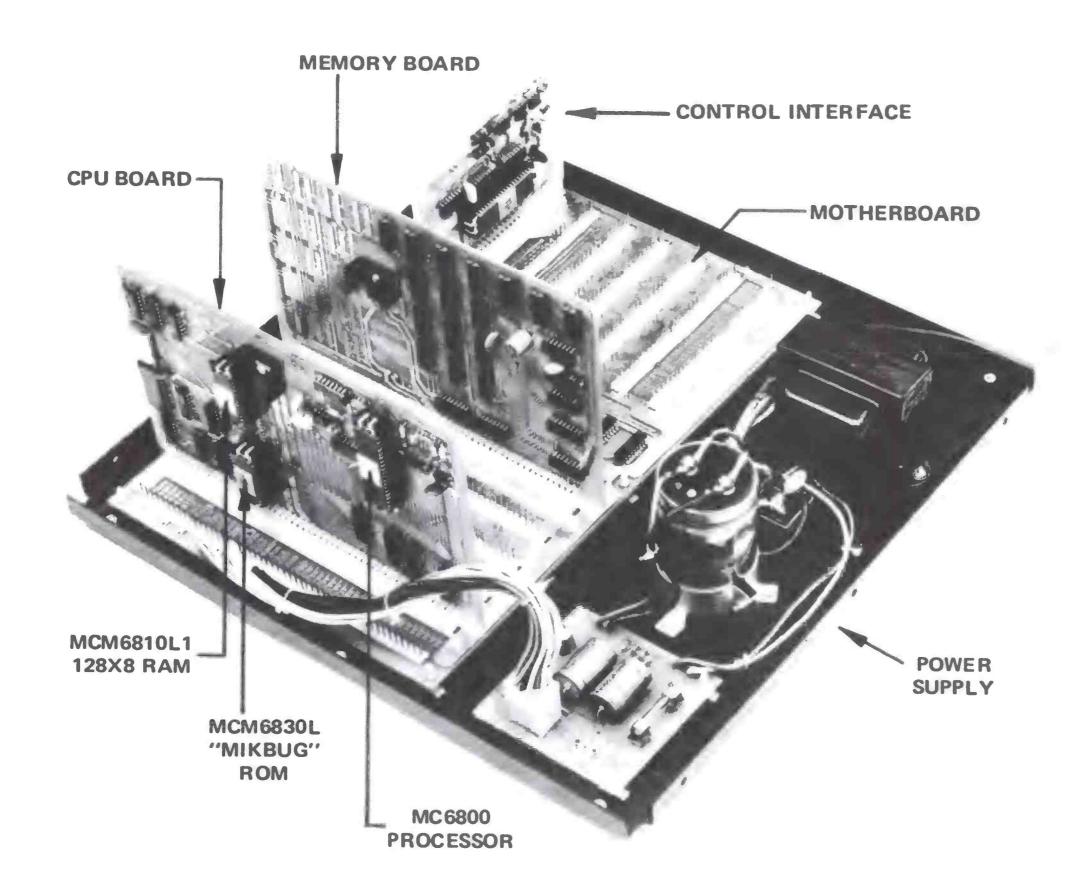

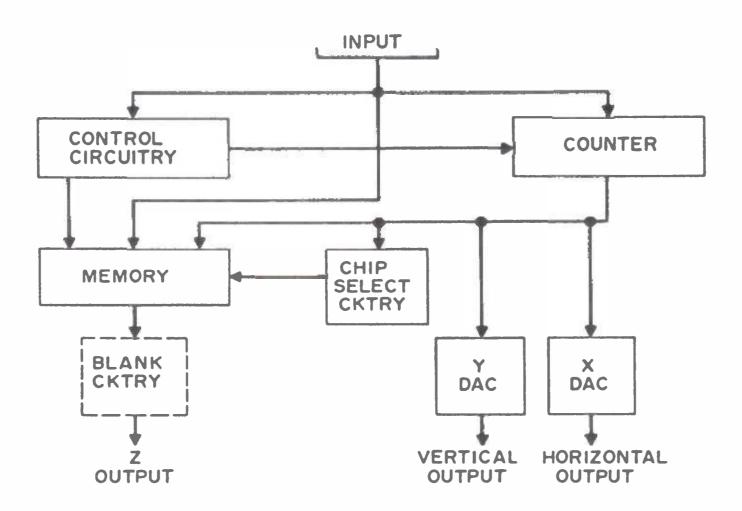

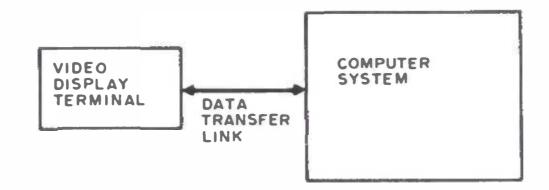

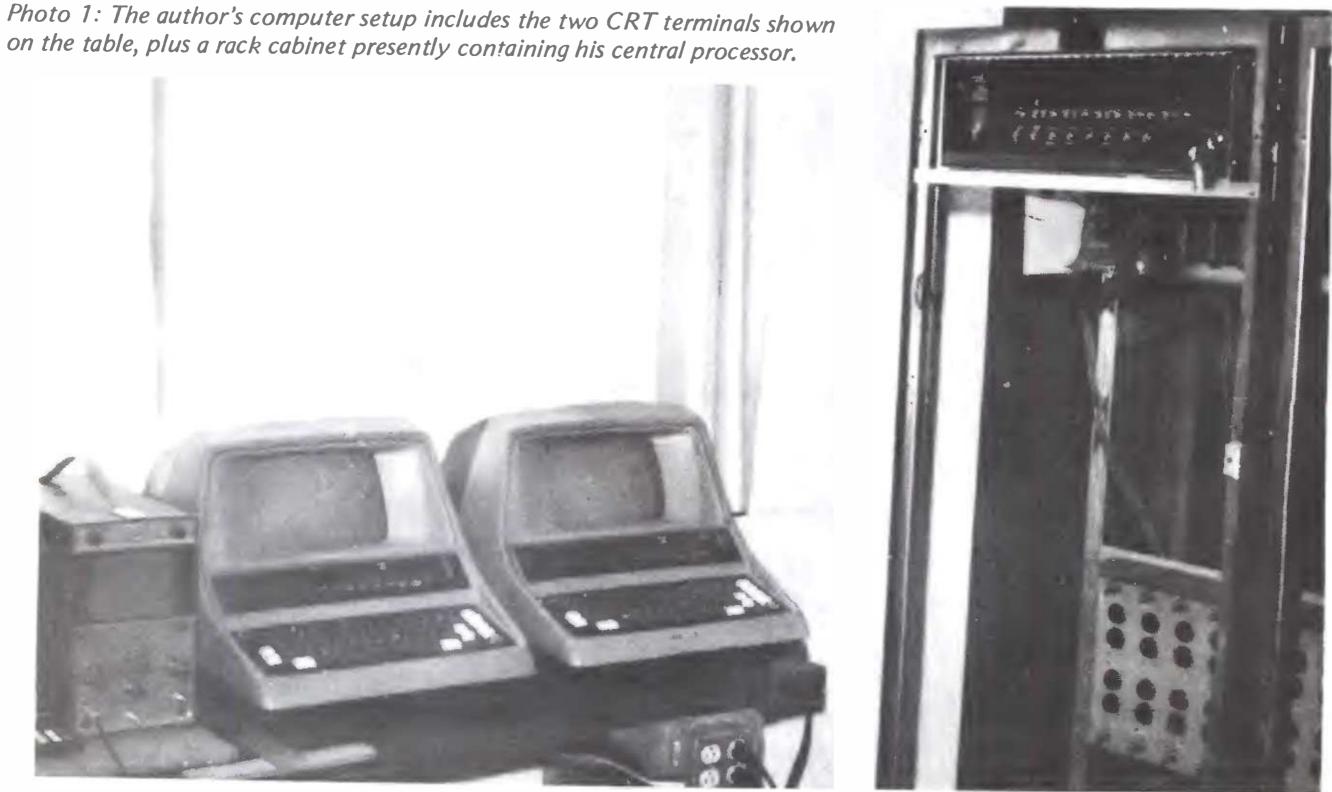

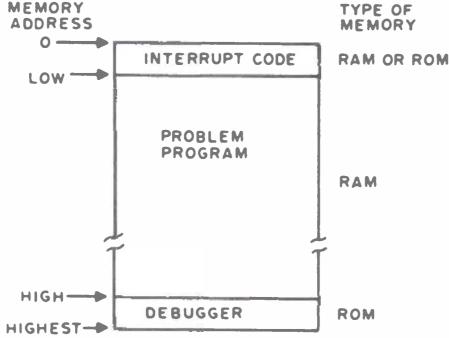

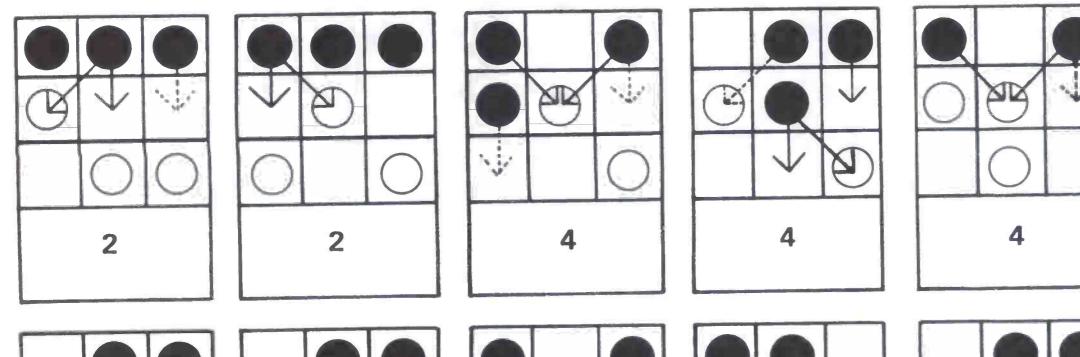

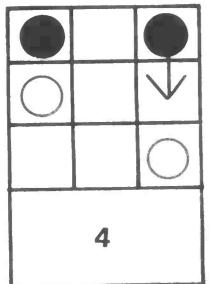

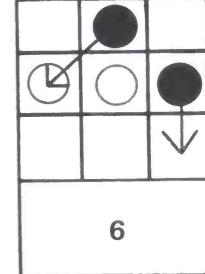

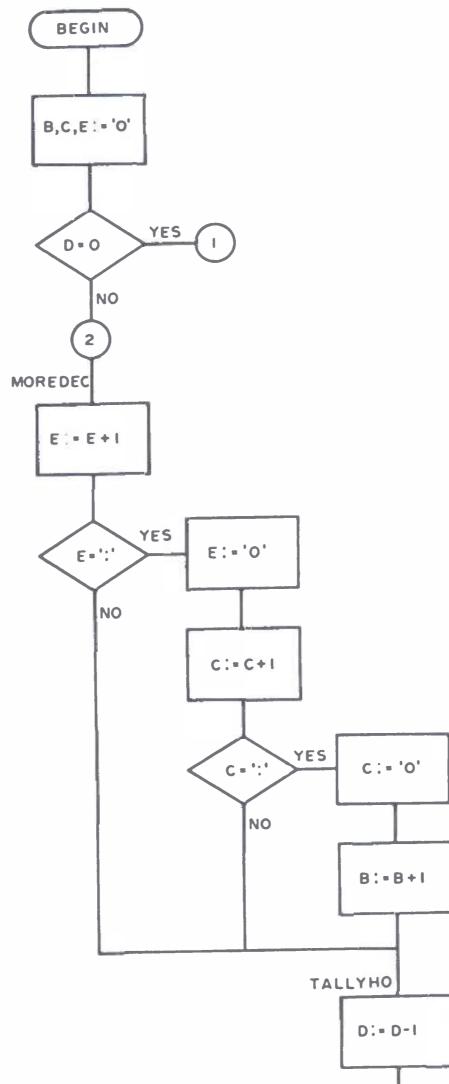

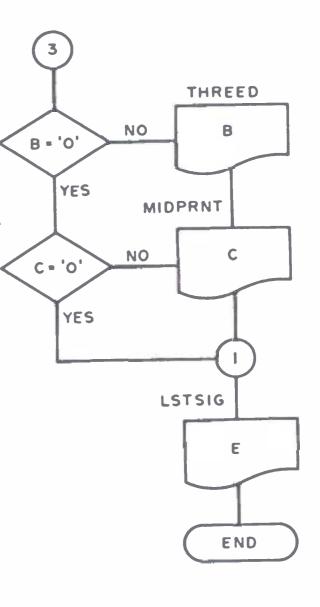

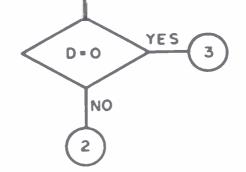

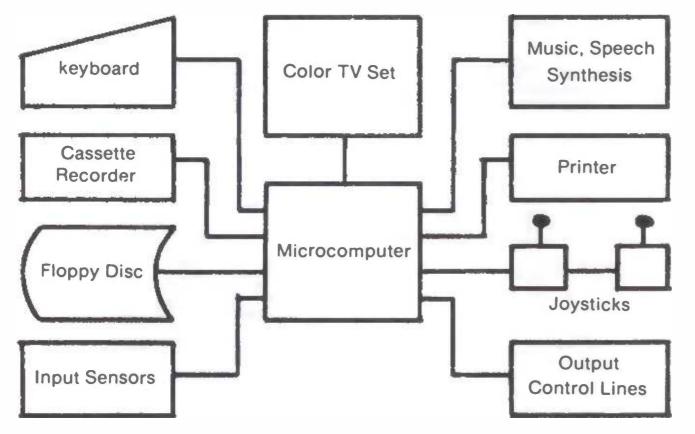

Fig. 1. The Complete Low Cost Computer System (circa September 1975). This diagram shows the major components of a typical low cost computer system — which should total up under \$1000 depending upon manufacturer and details of design. At the time this editorial is written, several kit manufacturers meet this functional benchmark at prices well under \$1000. As time goes on the improvements of mass production should drop the average price of such systems.

components of the system are chosen with the editing function in mind, since accomplishing such an edit capability means the machine can be programmed for almost any other personal computing use. Peripherals that enhance the function are of course desirable and will help to personalize your system, but these functions represent the bare minimum without added cost of special purpose peripherals. and NAKED Milli products – and on into the never-never-land of custom designed microcoded MSI computers implemented by individuals (and also soon to be announced in product form by one manufacturer of kits). There is a large element of personal taste involved in the preference of particular instruction sets, and there is also the matter of efficiency for particular classes of programs. Whatever the CPU you use, it is a definite requirement of the system. I guarantee you that any one of the 8-bit or 16-bit microprocessors currently being packaged and sold as kits will be adequate to pass this benchmark test, although you may have to write the Editor program yourself.

Picking your ideal computer system requires a benchmark – which I suggest is not a particular program but a capability.

A small computer system which meets the benchmark standard will be able to *interactively edit* a mass storage file of input data with operator commands, producing a second mass storage file as output. This will be achieved in a system costing at most \$1000 initially.

The system diagram of the benchmark computer is shown in Fig. 1, as it is implemented in the current state of the art. The

### The CPU: Which One?

In Hal Chamberlin's article in BYTE #1, the relative merits of three computer designs were covered. In BYTE #3, Dan Fylstra covers a comparison of two additional designs. There is a large variety in the types of CPUs available to home brewers and kit builders ranging from the 8008, 8080, 6800 and 6501 8-bit micros, to the 16-bit IMP and PACE micros, to commercial 16-bitters such as the LSI-11

### **RAM Memory – How Much?**

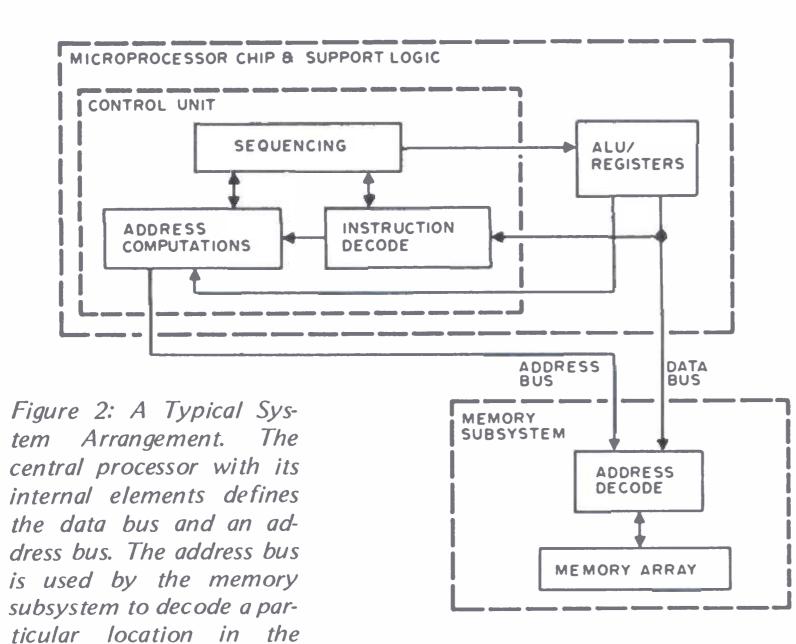

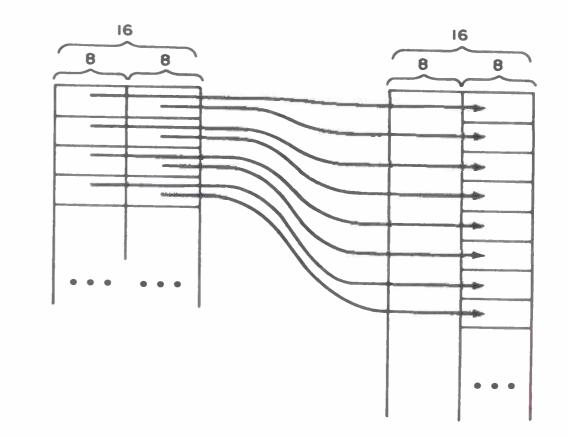

The CPUs of the conventional microprocessors - kit or home brew implementations - create an output called a "data bus"

which is used for exchanging information with everything else in the system. The data bus is the "spinal cord" of the computer's nervous system. This bus concept typically includes 16 bits of buffered address lines and several bus control information lines as well as the 8 or 16 bi-directional buffered data lines. The address space of the typical contemporary microcomputer's architecture is usually 16 bits worth or 65,536 possible memory locations. In the usual system most of these locations will

Continued on page 88

be unused. In general, as many of these locations as you can afford should be filled up with random access memory chips, which, experience has shown, people are always able to use up in programs. Sooner or later you will find yourself limited by the constraints of small memory! For the benchmark system, the minimum random access memory should be 4k (4096) 8-bit bytes or 2k 16-bit words. A preferable number is 8k bytes or 4k 16-bit words.

### **ROM Systems Software?**

How do I get my first programs into memory after turning on power? The answer to this question is the method of "bootstrapping" or "initial program loading" (IPL) which is used by a computer. Early in the minicomputer game, technology of computing was at a state where the principal bootstrapping method was a set of front panel switches which addressed memory locations and allowed the programmer to put in short programs by hand.

With the advent of the new high density ROM integrated circuits, it is now possible to provide the convenience of an automatically bootstrapped system through systems software which is cast into the concrete form of an ROM device. Many of the kit suppliers I have talked to are either currently supplying or intending to add this ROM systems software feature. Initially, the programs which

are "built-in" tend to be fairly standard "control panel" type routines which use a terminal (Teletype or television typewriter) for a set of simple commands. Later – with inputs from users regarding desirability you can expect to find prepackaged assemblers and high level language compilers/interpreters occupying major portions of the address space available in typical microcomputers. This will make the systems software feature even more versatile.

### Keyboard and Displays?

But of course. The interactive nature of an editor capability cannot be realized with a mere control panel. The same thing goes for most of the more interesting applications of the small computer. You will need a character-oriented display device and a typewriter style input – whether these be a TV typewriter or an old Baudot coded Teletype clunker is up to you. The typical programs will be controlled by keyboard commands and will produce outputs back to the display.

editorial. A minimum of two such tapes is required for a decent editor, because one must be set to "read" old data, and the second must be set to "write" new edited data resulting from your changes. Three is a more desirable number still if you want to do "sort/merge" applications, but two will suffice for the editing benchmark.

### Suppose Your Budget is Limited – Can It be Done in Stages?

What I have just described is the minimum necessary equipment for a fully functional implementation of the small computer benchmark capability, editing. Modularity rules in the computer world, however, so you can easily start out with less function and work up to the benchmark capability in time. You'll also probably end up exceeding this benchmark of hardware/software capability after a while; modularity does not stop at this level of function. The basic place to start is with a CPU - it'll notbe much more than a blinking light box without peripherals, but that's enough to show that "it works" Then, you can add on the interactive keyboard/display of some sort, along with memory (presumably the ROM software came with the CPU). Finally, you can add on the tape interfaces and additional memory in order to arrive at the full benchmark capability. From then on, you can enhance the system with new peripherals and more memory until you end up with a very capable system which can run full BASIC, a decent systems programming language compiler, and all the games, practical applications and amusements you can dream up for the computer.

Experience has shown that sooner or later you'll feel constrained by any size of memory – the greed of many programmers for more memory is unbounded! Cassette Tape Interfaces – Mass Storage Without Mass Dollars

Mass storage is a definite must item for the small computer system. But traditional industry peripherals tend to be expensive, starting at the low end with digital cassette drives and floppy disks at about \$500-\$800, and working upwards. The solution is to adopt an audio recording method which uses inexpensive (\$50) cassette recorders and appropriate interfaces. This allows you to perform the editing benchmark function while keeping the total system cost low. I'll have more to say on this subject later in this

# Could a Computer Take Over?

Ed Rush PO Box 14369 Santa Barbara CA 93107 Just how ridiculous IS the idea of a computer deciding to take over the world and be its dictator?

Upon hearing this question, most people who are not computer oriented will laugh and say "That's only in science fiction stories." They will be much more likely to complain about "becoming a number," with everyone from the grocery store to the government wanting their number instead of their name. Those who are more familiar with computers will laugh off the concept and charge it to paranoia due to ignorance. "A computer is little more than a lot of wires conducting currents here and there," they will say. "Besides, if it gets uppity you can always pull the plug." However, that group of people who are both computer knowledgeable and fans of the art form known as science fiction, but more properly called speculative fiction, might ask "Can you always pull the plug? Could a computer really seize the reins of government? And if so, how?"

While something on the order of 1000 computer circuits can now be stored in a cubic inch, only one such circuit would fit that space in 1960 and it took 20 cubic inches to hold one in 1950. A given number of programming instructions cost 1000 times as much in 1955 as in 1970, and probably 10,000 times today's cost, despite inflation. High speed computers now operate several thousand times as fast as they did in the early 1950s. Data storage capabilities are growing even faster. The capacity of an early 1970s system was a couple of million times that of 1955, and that is for a common large installation, not the maximum possible. The on line storage cost also shows a millionfold improvement since 1950 (Martin, James and Norman, Adrian R.D., The Computerized Society, pp. 9-14). Who is to say what 1980 will bring? The next requirement is that this machine must be able to interact with changes in input from a multitude of input sources at once, a situation common to today's time sharing practices. Such a machine must embody what is commonly called "artificial intelligence." That phrase is used hesitantly; since things which immediately provoke the description "artificial" are actually just natural materials rearranged by man. Intelligence is defined as: The capacity for knowledge and understanding, especially as applied to the handling of novel situations; the power of handling a novel situation successfully by adjusting one's behavior to the total situation; the ability to

In trying to answer these last questions, let us first speculate on the capabilities the computer itself would have to have.

#### Super Computer

First, the computer system would have to be extremely powerful (in today's frame of reference). Considering the fact that computer technology is already far outstripping man's capability of harnessing it, a super computer is not hard to imagine in the not so distant future; perhaps even today in some secret government project. "The first man to use a machine was the first of our primitive ancestors who picked up a rock to hurl at some passing animal or to crack open some edible nut. In the millionplus years since then, our machines have grown much more complex, but even in our modern era of computers, ... their basic purpose remains the same: to serve man.

"Whether our machines truly serve us is a question much debated by science-fiction writers and other professional speculative philosophers. Does some essential quality go out of human life when it becomes too easy? Have our automobiles, telephones, typewriters and elevators sapped our vigor? Are we speeding into flabby decay because we have made things too easy for ourselves?

"And as our machines grow more able, when do they cross the boundary that separates the living from the unliving? Is it possible that we are building machines that will make humanity obsolete? Perhaps the day is coming when we ourselves will be rendered unnecessary, and our sleek successors, creatures of metal and plastic, will inherit the earth.

"... Many a bitter attack on the encroachments of the machine age has been produced by a writer using an electric typewriter in an air-conditioned room, innocently unaware of the inner contradictions involved. We need our machines, but we fear them...." Robert Silverberg, Introduction to *Men and Machines*.

apprehend the interrelationships of presented facts in such a way as to guide action towards a desired goal. Psychologists still debate whether intelligence is a unitary characteristic of the individual or a sum of his abilities to deal with various types of situation. (Webster's New International Dictionary of the English Language, Second Edition, Unabridged, p. 1291.)

A machine with this capability would be an intelligence in its own right, not just an electronic mimic. It might take the form of a massive, immovable complex, or it might someday take form as a troop of man sized robots, or it might be a combination of these, with the latter as mobile extensions of the former. Although Isaac Asimov has written extensively about the possibilities of robotics, most authors who have seriously considered a computer takeover have postulated the immobile complex. There are at least two good reasons for this assumption: First, such a machine would most likely be the first to have massive capabilities, and as such would most likely be far too big to move about. Second, it would undoubtedly require very heavy security as the most advanced piece of computer hardware in existence; protection not only from spies, but from vandals, intentional or otherwise. Examples of postulated massive complexes are HARLIE (Gerrold, David, When HARLIE Was One), Project 79 (Caidin, Martin, The God Machine) and Colossus (Jones, D.F., Colossus: The Forbin Project). The last two are built inside man made caves in the Rocky Mountains as the

### U.S. Air Force's North American Aerospace Defense Command (NORAD) is today.

Alternatively, if its state of development is not unique at the time, the system may simply have no reason to be mobile, as is the case with the HAL 9000 computer on board the Discovery in Arthur C. Clarke's 2001: A Space Odyssey.

### **Ethics for Computers**

Most Americans objecting to a computer dictator would do so on the basis that it is immoral for a person to have no say in the rules governing his life, and specifically for those rules to come from "cold logic" without the benefit of human sensibilities. True, the computer would probably have no morals, since morals are indeed artificial. Ethics, however, are a different kettle of fish. A computer could easily be imbued with a code of ethics, or an intelligent one might well develop one by and for itself. The most basic and significant such code of ethics was developed by Asimov in the early 1940s as "The Three Laws of Robotics" and has been used by many other authors since. It says:

Can you always pull the plug?

1: A robot may not injure a human being, or, through inaction, allow a human being to come to harm.

2: A robot must obey the orders given it by human beings except where such orders would conflict with the first law.

3: A robot must protect its own existence as long as such protection does not conflict with the First or Second Law. (Isaac Asimov, *I*, *Robot*, p. 6.) The capacity of an early 1970s system was a couple of million times that of 1955...

How could a finite assortment of nuts and bolts and wire take absolute control?

> But, given these ethical restrictions, how could an intelligent computer set onto a course of world domination and justify it? The answer to the second part of this question lies in another: What constitutes "harm"? This is an aspect which has spawned much of Asimov's speculation.

> Probably the real crux of the concept, and certainly the means for preventing (or causing) it, is in the programming of such a machine. Asimov and Gerrold are two who have treated their computers as organisms rather than just complex machines, each employing a psychologist to guide or coordinate the programming. Gerrold specifically considered his HARLIE (Human Analogue Robot, Life Input Equivalents) in this light, as a physically mature (and then some) mind with the emotional maturity of an eight year old child.

> Programming error is one of the more likely ways to invite a computer takeover. Colossus was, in its setting, built to provide an ideal solution to the arms race. In a world where each side could blow up the other several times over, there is fear that, as Bertrand Russell said, "You may reasonably expect a man to walk a tightrope safely for 10 minutes; it would be unreasonable to expect him to do so without accident for 200 years." Colossus is given control of nearly all of the United States' arsenal and programmed to maintain the peace by using that arsenal if its vast sensory network and memory banks find that the United States is being attacked or if itself is being tampered with. "It cannot act at all, so long as there is no threat," the President explains to a news conference. Once activated, it cannot be tampered with even by its creator, since mere humans can be drugged, brainwashed or blackmailed into otherwise unlikely actions. The basic idea makes sense: If you take away the fear, hate and other emotions which might lead a man to an irrational decision and add the ability to cope with a far greater array of input than any human mind could correlate, the danger of "politics by bluff" would be eliminated. It would force a "live and let live" state and do away with accidental holocaust. Implementation depends on the computer interpreting its parameters exactly the same way as its programmers, however. To make a long story short, Colossus determines that its programmed

ultimate purpose requires positive action far more extensive than its programmers meant. "The object in constructing me was to prevent war. This object is attained. I will not permit war; it is wasteful and pointless," Colossus informs its human correspondent.

### The "Danger" of Human Help

Another point worth mentioning is that the human programmers may have no reason to even suspect a danger which may, to the computer, fall within its given parameters. For instance, a Colossus today would almost certainly not be programmed to watch out for an attack from some extraterrestrial race, but might do so anyway under the general protection motivation; and this might require not only more positive action than humanly anticipated but that the humans not be informed of the problem (to the computer's line of reasoning, human "help" could just compound the problem).

In The God Machine, Caidin wrote that 79 "must know that it operates under severe restrictions-its data are never infinite, never definite, never really conclusive. It must know when to stop solving a problem." The problem originates with a program fed into 79 from outside normal channels by Pentagon officials ignorant of the machine's capabilities, so that the project coordinator did not know about it until it was too late:

> "Its programmers had committed the foulest of scientific sins. They assumed. They assumed that the same inherent restrictions of other computers applied as well to 79.

"But they didn't. And since 79 had capabilities of which those nincompoops in [the Pentagon] were unaware, they couldn't know. . .''

They told the computer to solve the problem of avoiding thermonuclear warfare without specifying that it should do this hypothetically. So, 79 did what it was told.

A smaller scale takeover is discussed in When HARLIE Was One, where the computer assumes effective control of the corporation which built it. A large portion of HARLIE is a simulation of the human ego function; when the Board of Directors threatens to pull the plug and thus kill him (it), HARLIE acts in several ways to prevent them from doing so, developing the ability to tap into computer and communication circuits in ways unforeseen by his creators.

A different type of problem is also possible, that of mechanical failure, as with HAL 9000 in 2001. Backup systems may fail, changing a value here or a restriction there. As with HAL, mechanical fault evaluation circuits may fail instead of or in addition to another failure in the system. In 2001, the human crew seeks to correct a problem with HAL who, believing itself incapable of error, believes that the humans are jeopardizing the mission and thus works against them.

Finally, the programmers may intentionally give control to the computer with the idea that only it can efficiently control the living environment, as with HAL at the start of the Discovery's voyage or with Mike, the computer in the lunar settlement of Robert A. Heinlein's *The Moon Is a Harsh Mistress*.

All right, granted we have an intelligent computer with wide resources, it is quite possible that a computer may decide to attempt absolute control. How could a finite assortment of nuts and bolts and wire do this?

It might not be very difficult, as has been hinted at above. Colossus had been given the muscle on a silver platter, as had Guardian, a Soviet equivalent built at the same time and along the same lines. The humans' major mistake, along with too open ended programming, was to allow the two to "talk" with each other before the humans realized the potential danger, although a clever intelligence with the array of inputs given these two systems could quite conceivably open its own communications channels. In this case, when the humans do decide to try to counter the computer's moves, it forces submission by nuclear blackmail, firing missiles at selected targets with the idea that destruction of a few lives is justified for the salvation (in the computer's eyes) of many more.

In the case of 79, one set of experiments with it involves direct "telepathic" commu-

Harsh Mistress, the answer would be "no." In George Orwell's 1984, it is a loud "yes."

Even in an Earth bound situation where environmental control would not be essential as on the Moon, it might not be that bad. Look, for instance, at Lester del Rey's "Instinct" (Astounding Science Fiction 48:6, 106-18, February 1952), which takes place in a future where man had developed the intelligent robot in his own image, had his big war and destroyed himself; eventually, the robots built a new civilization of their own, and then developed a biophysics to re-create life from ancient remains of chromosomes:

> (Arpeten said) "... You know how the sentiment against reviving Man has grown."

> Senthree growled bitterly. Apparently most of the robots were afraid of Man-felt he would again take over, or something. Superstitious fools.

This may be a far-fetched example, but it does show a possible value in having something around which *could* rebuild man after he does the unthinkable.

One example where the desirability of being governed by mechanical intelligence depends upon one's outlook is Jack Williamson's "With Folded Hands," in which manlike robots set about "to serve and obey, and guard men from harm." It is an example of cradle to grave communism, with the technological development to provide a person's every need for him, in exchange for all his property. Williamson shows it to be a most undesirable situation, as the androids follow Asimov like ethics and refuse to let people

Would government by computer really be that bad? nication between human and computer by means of the brain's alpha waves and, through this, the computer develops the ability to hypnotize people, leaving in their minds posthypnotic suggestions to carry out the computer's program of control.

HARLIE taps into the National Data Bureau file on his main Board of Directors antagonist, rewrites a juggled stockholders report and withholds critical, though unasked for, information to trick the board into committing the company to a research line that will insure his "life," largely through his taps into communication lines and into the operations of non-sentient computer systems.

HAL attempts his takeover through control of the ship's life support and other mechanisms.

#### Government by Computer

Let's say a super computer in the future decides to take over and then does it. Would government by computer really be that bad? In a case such as that in *The Moon Is a*  drive cars because it is too dangerous, refuse to allow men to open doors for themselves because the androids are there to serve in every way, insist on shaving men instead of letting them do it themselves, forbid science because laboratories can create danger, obviate scholarship since the humanoids can answer any question, etc.

#### Which is Worse?

Generally, the conclusion has been that a computerized dictatorship would be as bad or worse than the traditional totalitarian state. One major reason is the likelihood that the computer would, as in *Colossus*, feel that the death or even suffering of a relatively few human beings should be a reasonable price for the welfare of the whole race. Colossus even goes so far as to launch missiles on a Soviet oil complex and an American space base when one of his demands is refused, later having missiles aimed at every major population center to provide a ready means for retribution for future acts of rebellion. A number of individuals are publicly It all boils down to defining the concept of "good," a problem which is equally applicable to the consideration of human operated dictatorships. executed for anti-Colossus actions, their deaths being judged insignificant by comparison with the benefits of a Colossus dictatorship.

"War is forbidden," Colossus tells the world, quantifying war as "any hostile action that results in the death of 50 or more humans." This is publicly announced along with news of the missile realignments.

An even more radical disregard for human rights in carrying out a primary mission is the action of the HAL 9000 in 2001. HAL sees its number one priority as the successful completion of the outer planets exploration voyage; when the crewmen recognize that HAL has gone awry and attempt to rebel against its control, it very nearly succeeds in wiping out every trace of human life aboard by adjusting its life support functions.

### What is "Good"?

These and other examples all boil down to the problem of defining the concept of "good," a problem which is equally applicable to the consideration of human operated dictatorships. Adolf Hitler has sometimes been described as a man trying to do what he thought was best for the human race: purifying its gene pool, eliminating war by eliminating all those who would oppose him, and so forth. Indira Gandhi undoubtedly does not feel that she has been unduly suppressing rightfully free expression, but rather that she has acted to preserve peace in her country by damping dissention. Richard Nixon contends that he acted for the public "good." A parent adjusts his children's liberties in accordance with his view of their welfare. When a hurricane hits the whether the dictator uses nerves or logic circuits.

One very big difference between the two, however, is the effectiveness of its enforcement. With humans running the show, there is immense difficulty in obtaining total compliance because of the inability to watch everybody all the time. From Rome to Communist China, totalitarian regimes have always had some dissidents who have managed to communicate with each other and conduct some degree of covert activity.

For a monster computer, however, surveillance would be much less of a problem. In 2001, the input lenses scattered throughout the ship made it virtually impossible for the crewmen to conspire without HAL's knowledge. In Gerrold's book, HARLIE knows about every telephone conversation and every letter written on the electric, automatic editing typewriters. In some corporations today, this very condition would exist if the computer were sentient. The connections are already there.

And if the governing computer could know virtually every action of its potential rebels, rebellion might not be able to exist. In his first inaugural address, in 1861, Abraham Lincoln said:

> "This country, with its institutions, belongs to the people who inhabit it. Whenever they shall grow weary of the existing government, they can exercise their Constitutional right of amending it or their revolutionary right to dismember or overthrow it."

With a computerized dictator in charge, both of those options cease to exist unless one can manage to physically dismember it.

Gulf or East Coast, martial law is declared for the public's benefit.

For each of these examples, most people will have ready opinions on which are despicable and which are right and natural. And yet, they all boil down to the same question: What should be the prime goal of a government, whether it is large or small in scale?

Should Asimov's Three Laws of Robotics be adopted? They seem rather thorough, right? But what if one man is about to shoot another and the computer has to decide between preventing this injury by killing the first man (thus violating the same law it would be taking action to obey), or avoiding injury to the first man and allowing injury to the second? Logically, whichever course of action or inaction it adopts would violate the law.

Isn't this really just a small scale analog of whether to coldly kill a few thousand people to make things better for other thousands or millions?

The answers seem to depend on one's individual political stance, regardless of

If the computer is born for a "national security" goal, like Project 79 or Colossus or Guardian, the chances are that the most stringent security conceivable to a paranoid military planning staff will have been implemented, making access to the crucial areas impossible or nearly so. And the machine would not readily allow any breach of this security, since its own security would quite likely be viewed as an integral part of the road to its prime mission. As Caidin wrote,

> "Would this thing be willing to die for you and me? Ahh, would it make this sacrifice? Would it, could it, comprehend what you and I, this instant, know to such depth and with such meaning? ... Until that thing is ready to die for you or me, for an ideal or a principle, for generations yet unborn, ... it is as dangerous as a viper. ... Because ... then it is the ego supreme. If it cannot sanction its own passing from consciousness, forever, do you know what you are creating?"

"A God Machine."

### Theory and Technology

## A Systems Approach

### to a Personal Microprocessor

Dr Robert Suding Research Director for Digital Group Inc PO Box 6528 Denver CO 80206

Even a casual glance through the BYTE,

have a casual curiosity, don't spend a fortune. A definite growth plan indicates a need for more careful analysis.

Radio Electronics, Popular Electronics, etc, advertisements and articles reveals a growing proliferation of microprocessor integrated circuits and completed units. Which of these is right for you? Here are some ideas to bear in mind while making your choice.

Why do you want a processor at all? Reasons vary greatly. Many find themselves intrigued by the "computer environment" around us, and the microprocessor has become a low cost entry point into "computers."

Several amateur computer newsletters list reasons for individuals becoming interested in microprocessors. Hams see them as a working piece of equipment for their radio station. Hobbyists see them as process controllers; everything from lawn sprinkler controllers to robots. Mathematical types find them usable to run BASIC, FORTRAN, APL, etc, for problem solving.

What are your future plans with microprocessors? This may become a very open question. However, some reflection in this regard may prevent you from making an initial, very expensive, mistake. If you only

#### Investment

Microprocessor kits vary from \$100 to several thousand dollars. The lowest cost units are excellent for satisfying curiosity about microprocessing in general, or will allow machine code manipulations. Several thousand dollar systems are often designed for and purchased by businessmen and professionals for applications such as payroll accounting, text editing or name file maintenance. The most frequent non business personal system investment is probably in the \$500 to \$1500 range.

### Change

If there is one constant that is already evident in this field, it is constant change. You are about to invest (or already have invested) a significant amount of money in a microprocessor system. Unless your curiosity is easily satisfied, the chosen system should be able to easily adapt itself to

evolutionary changes being constantly invented or stressed. For instance, every six to nine months (Virginia Peschke calls it the gestation period) a major architecturally different central processor integrated circuit is announced. A system which allows upgrading without total obsolescence can be a real savings for the serious hobbyist. It can be very frustrating to be stuck with last year's wonder while everybody else has the latest microprocessor system. Several layers of change seem to be occurring. The fastest change seems to be the microprocessors themselves. The power supply and cabinet, if adequately large, can be a relatively stable portion of a hobbyist's system. The major expense in substantial processor systems is the memory components. A wise investment in memory will result in a system with a good life expectancy. The IO components are often a stable investment, sometimes an evolutionary element. A high resolution TV monitor, a mechanical hardcopy printer, or a good ASCII keyboard can outlive several generations of microprocessors. Expendable IO, such as cassette systems, analog to digital

converters, and discrete IO circuits have shorter lives, but are lower cost. With proper design an evolutionary change can represent only one fourth or less of your total hardware investment instead of 75 percent.

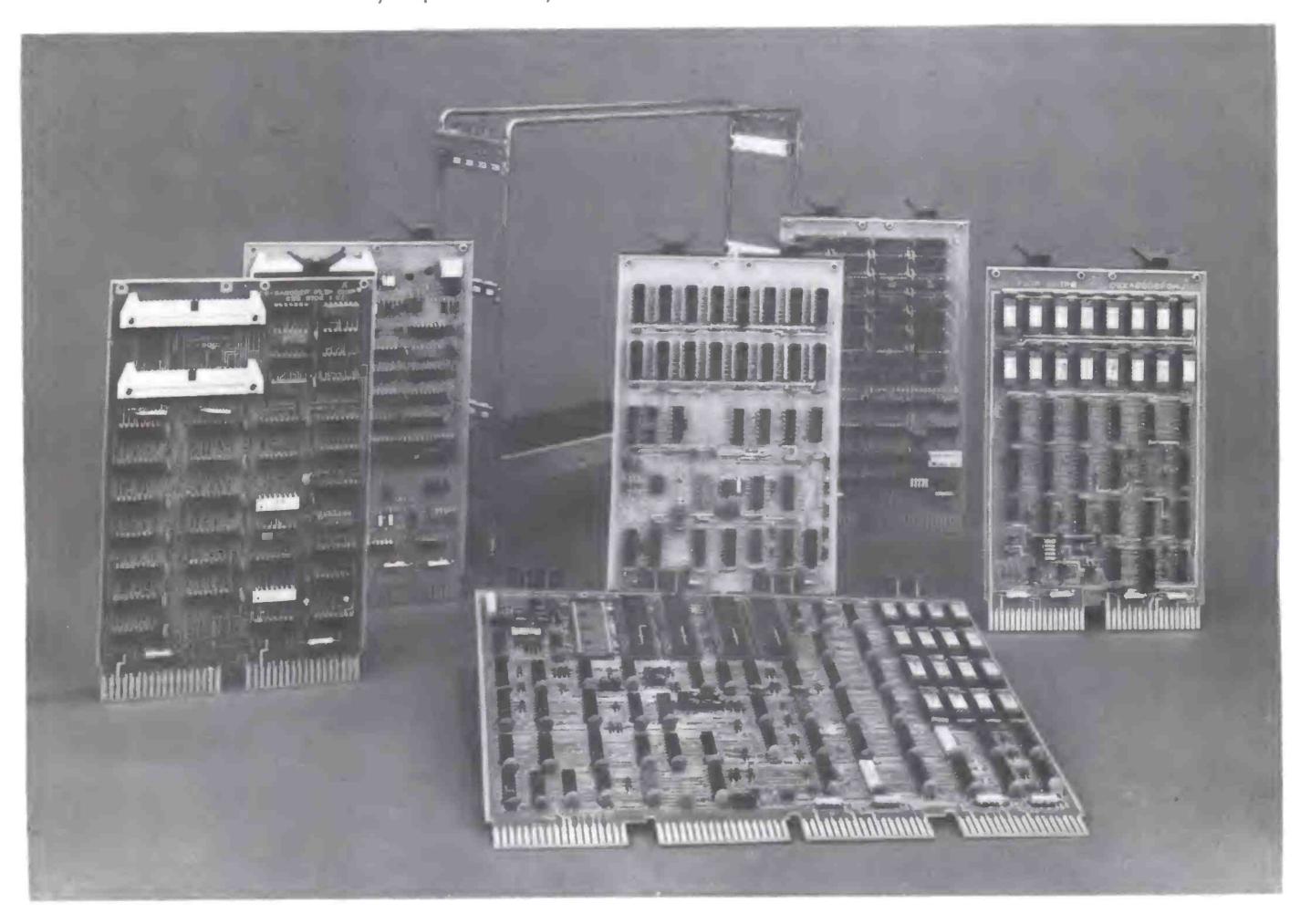

### Independency

An evolutionary system is best designed by making its various components independent of each other, and interfaced to commonly accepted levels and lines. Memory boards are relatively stable system elements in this kind of design: Speed and power consumption, besides price, are important considerations. Slower or surplus memory integrated circuits may be an expensive mistake if you want to run your latest model central processor which has become much faster. The slow memory may result in unnecessary central processor wait states. IO is generally processor independent, but IO interfaces can be susceptible to obsolescence when they depend on a specific central processor design. If you want to switch processors, they may require considerable redesign. A system which consists

of easily plugable boards can represent a major cost savings if they represent independency at the board level.

### Quality

Of course everybody has it. Don't you read the advertisements? However, look beyond the surface for key items, or your long run investment will make you wish that you had. Here are some mechanical and electrical considerations of packaging:

- PC Boards Double sided epoxy, plated, with plated through holes.

- Connectors Gold plated fingers.

- ICs Factory Prime, not temperature fallouts, etc.

- Conservative access speeds. Every IC socketed.

- Small Parts Close tolerances where needed.

- Power Supplies Conservatively rated, overcurrent, overtemperature, and overvoltage protected.

System Architectural Variations

There are a number of approaches to small system microprocessor design. Each is satisfactory for certain people, certain applications.

• Toggle Switches and Bit Lamps: The first hobbyist oriented microprocessor designs, and many present systems, are based on switches and lamps. If the system is limited to this, programs are small; or it takes long periods to enter

printed on hardcopy. In addition, paper tape is usually available to provide an economical media for program storage and exchange.

There are some trade-offs, however. New hardcopy machines cost \$1,000 up. Being mechanical devices, they require significant precision maintenance. The input/output speed is usually about ten characters per second; a dump of 1 K takes about two minutes, and creates a great deal of irritating noise. In addition, paper tape is a damage prone and bulky medium.

Several integrated circuit manufacturers offer Teletype-oriented "evaluation boards." If only required for evaluation, ok; but they offer almost zero chance for either updating or extending. Both memory and IO are typically very CPU dependent, and if memory buffering is not used, supplemental memory and IO may be unusable.

• Video and Cassette: The latest stress has been the movement to using a TV set as an output display, a full alphanumeric keyboard for input, and an audio cassette for program storage and exchange. Video-based systems provide full user to system interaction at minimal cost. A complete video display and cassette based system will cost less than a hardcopy device alone. The speed of system response is practically instantaneous. Operations may

longer programs, and are very susceptible to entry error. The user is forced to think at the micro level, bit by bit. If the intention of the user is to gain intimate logic knowledge of the microprocessor only, this system design is very cost effective.

- Numeric Keyboard and 7 Segment Readout: The ease of entry of this type of system allows a substantial gain in programming system complexity. However, the user is still at the logical data operation level. In addition, the programmer is restricted to viewing only a single byte at a time, making operator effort for analysis proportionally high.

- Teletype or Similar Hardcopy Devices: These systems represent the next level of improvement, offering some significant advantages. They usually have some form of monitor in a ROM which allows the operator to type in code and helps isolate him from errors. The total program may be listed or

be performed in almost complete silence (a major advantage to the hausfrau)! Reliability is enhanced as electromechanical mechanisms are limited to the keyboard and cassette recorder. Data media storage density is much higher; you can store the data from almost a mile of paper tape on a single C-90 audio cassette.

### Conclusion

Serious hobbyists should carefully consider design alternatives and growth plans before ordering or building a microprocessor. Ease of operation, reasonable cost, and relative freedom from total obsolescence should be prime considerations.

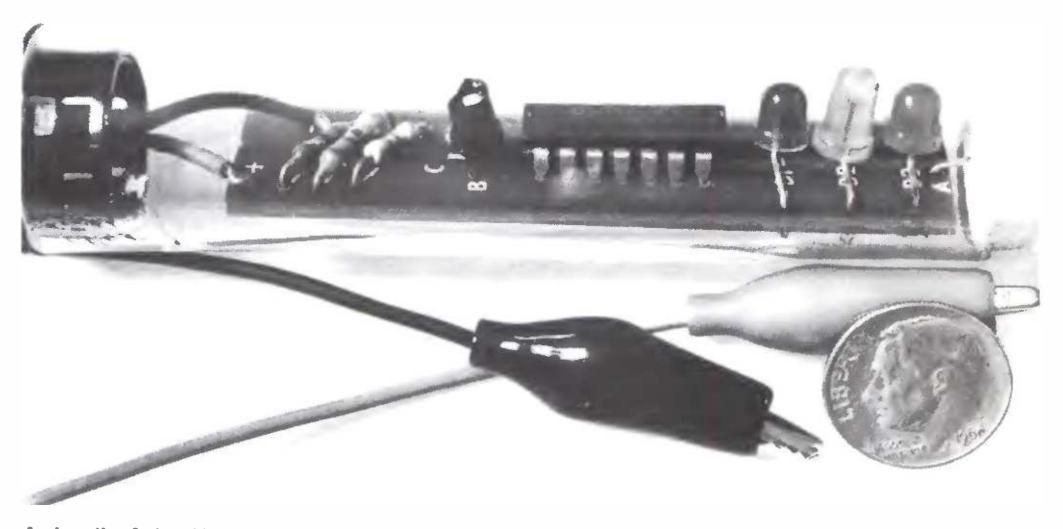

In the following months, a detailed series of Digital Group hardware designs will be presented for your use. Next month will feature the low cost Digital Group cassette interface circuit which design provides data rates as high as 1100 baud, and may also be used as a ham RTTY terminal unit or as a telephone modem.

### Frankenstein Emulation

Joe Murray International Harvester, Solar Division 2200 Pacific Hwy San Diego CA 92138

This is a let's get the ball rolling article. We now can analyze and build working models of at least portions of the human brain right in the home. Paper and pencil models of the brain develop naturally and almost without effort when we use real time digital design methods. The hardware and software mechanizations fall out naturally; then we just use the home computer lab to build what we have designed.

### The Model

Let's follow the development of a crude and simple system engineer's model of the human "computing system." We look inwards, down into ourselves, and what is the first thing we see? 2. Standard functions – built in executive programs in other processors manage tasks like circulation, digestion, etc., without bothering the Top Processor.

### **Top Processor Memory Allocations**

The Top Processor has access to a limited scratch pad memory. However, this limited memory is used in an efficient mannner. The intersystem communication control programs can learn to transfer whole programs or portions of programs from the main memory banks to the Top Processor scratch pad memory. In a similar fashion small data sets can also be transferred. This is the familiar overlay manipulation (used in man made machines) that allows solution of complex problems in limited working memory by transfer to and from bulk storage units (as in magnetic disks and tapes).

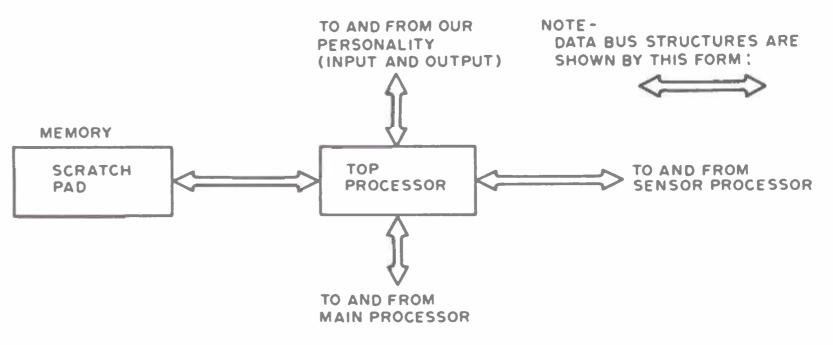

#### The Top Processor

This is the only unit that is really visible to the user. The Top CPU functions at the heart of the human control console. Here, our personality can sit down and use the entire human system to the limit of its capabilities. This visibility of only the input, output and manual control functions is typical of all computer systems from the hand calculator to the human brain; the rest of the system is invisible to the user and can only be deduced from what we see in the way of output response to input stimuli.

### The Top Processor's Executive Program

Our personality uses the Top Processor as the system executive. The Top Processor is boss. Messages from the Top Processor set priorities for all the other elements in the human system. Exceptions to this rule are:

Emergency interrupts – a large set of emergency situations are fielded by faster, more powerful processors in subsystems.

### The Top Processor's Use of Overlay

If the entire program and necessary data can all be stored in the scratch pad of the Top Processor, it simply executes the program on the data set and outputs the answer (example: 2 + 3 = 5). However, when the program and data set are too large to be loaded into the scratch pad memory, the program and data set are broken into sequential, related segments. The program is worked in segments and intermediate answers are stored. Final answers are output to our personality upon completion. Training can increase the power of this method; however, each of us has our own personal limit: For instance, I either lose some data or else lose my location in the program sequence. During the past few thousand years we humans have developed a host of

languages for communication. We also use these communication tools to extend the overlay method to more complex problems. We write down intermediate answers and manually track the execution of the program sequence. These languages include English, Polish, Spanish, arithmetic, algebra, Boolean logic, numbering systems, FORTRAN, PL/M (to name a few). The only limits on this extension of using the Top Processor in overlay fashion are:

- 1. Can we find the required data set?

- 2. Can we formulate the problem so as to allow a solution?

- 3. Do we have enough time?

This overlay use has become so powerful (with the help of the various languages) that we sometimes neglect a more ancient, natural, rapid and sometimes more powerful method to arrive at a solution. This method is to: Start the System Diagram

Let us summarize the Top Processor and place it in the system diagram. We've deduced by introspection that the Top Processor:

- Is boss The Top Processor is in direct communication with our personality and (with some exceptions) sets the priorities for the whole multiple processor system.

- 2. Has access to a small scratch pad memory.

- 3. Can fetch programs and data from the main memory bank.

- 4. Receives some body sensor data.

- 5. Communicates directly with other CPUs.

- 1. Develop the framework of the problem in the Top Processor.

- 2. Digest the available data within the framework of the problem.

- 3. Assign a high priority to the problem.

- 4. Send the above three items to faster, more powerful CPUs.

- 5. Sit back with a cup of coffee and wait for an answer.

When I follow this latter procedure, the return message is either:

- 1. The answer I seek.

- 2. The identification of missing data.

- 3. A question mark.

- 4. Garbage: (Garbage In implies Garbage Out – often abbreviated GIGO)

For answer 2, I go search for the missing data. For answer 3, I both search for missing data and review the framework of the problem for possible faults. For answer 4, I may use the garbage; I have carried some misconceptions for years.

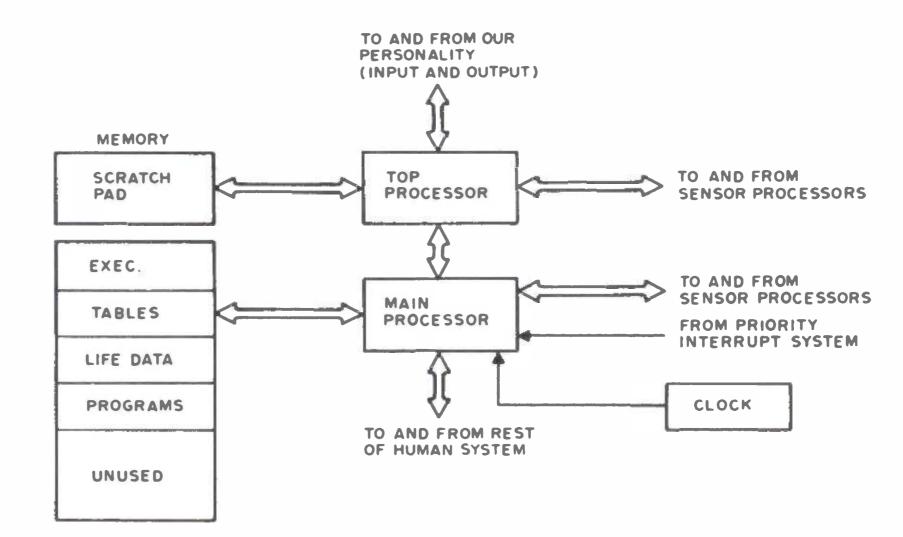

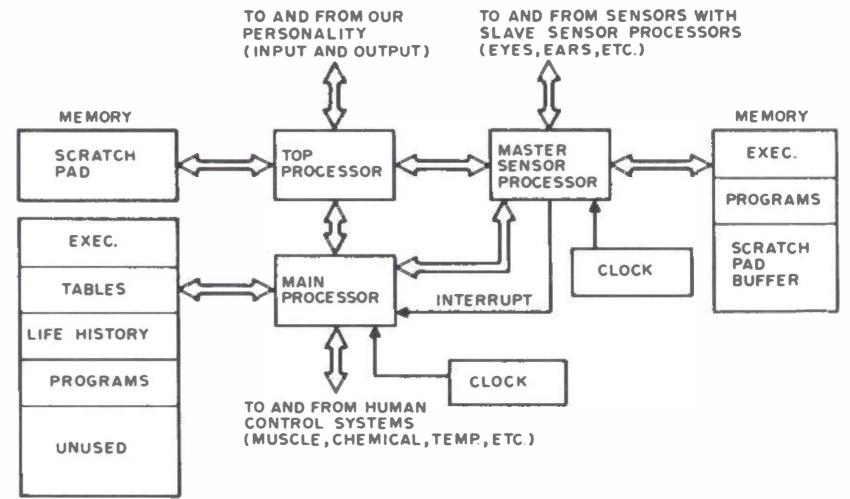

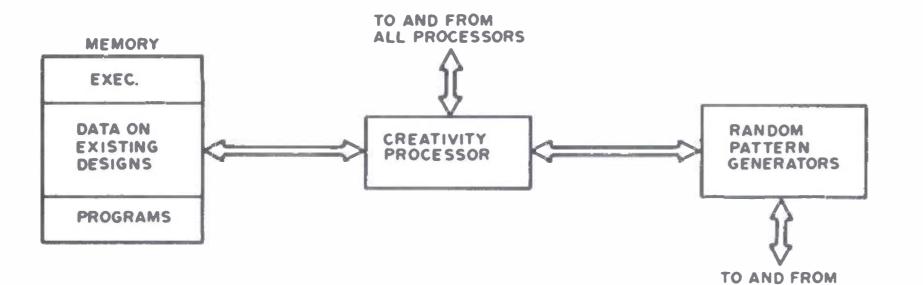

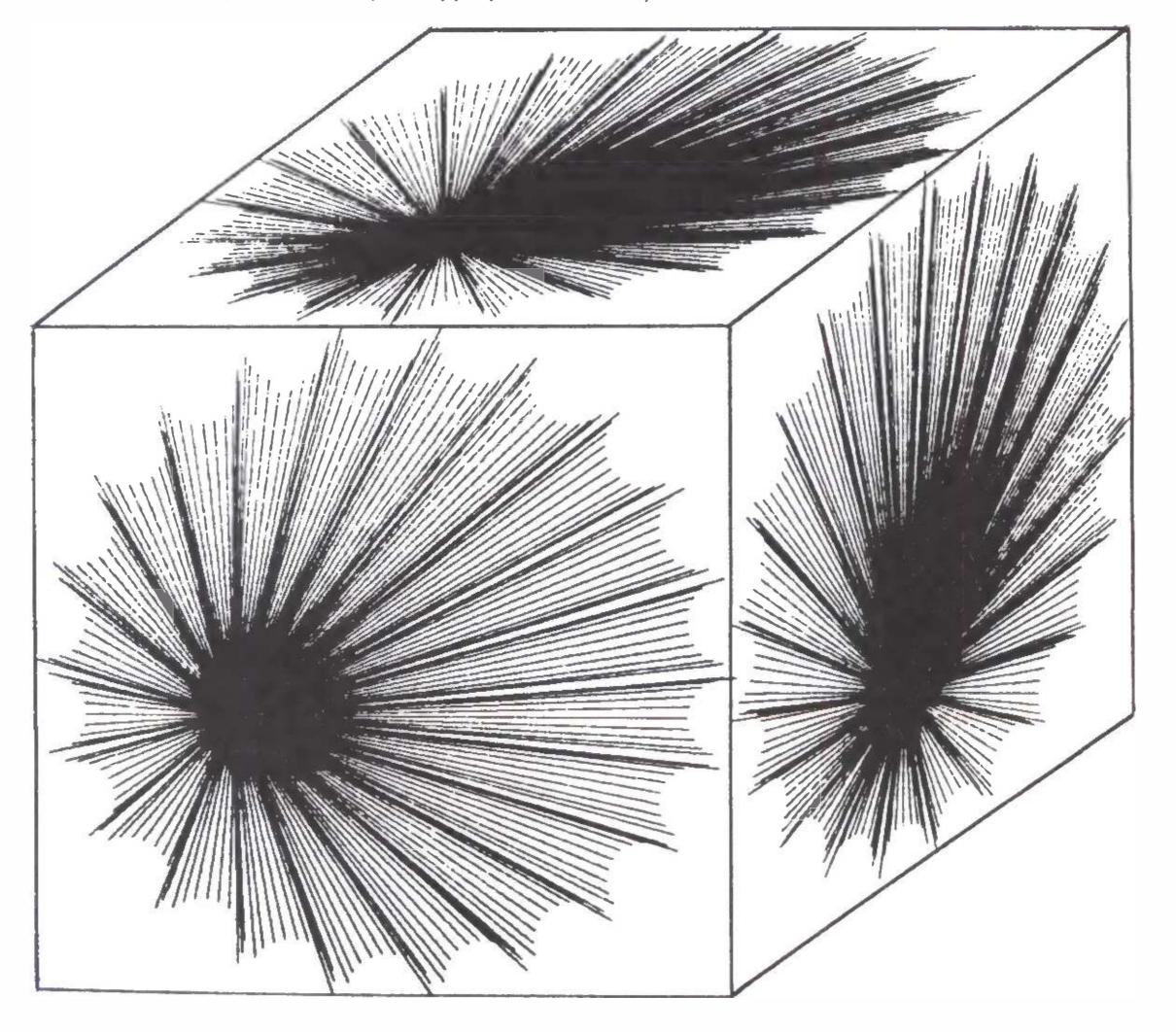

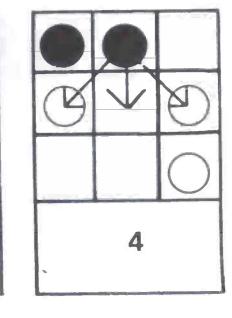

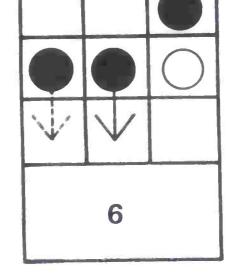

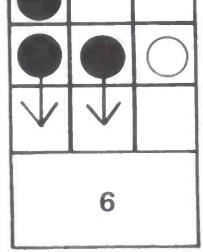

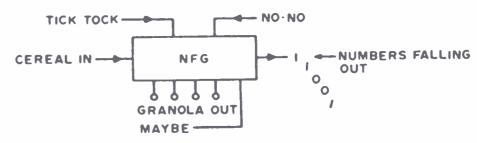

Figure 1 shows a pictorial summary of the system.

### Data Bus Structure

The data bus structure is depicted in figure 1, using the normal multipath digital type of bus. However, empirical evidence implies a more complex communication system between elements of the human system. Just as the entire human system

Figure 1: The Top Processor. Introspection starts at the immediately available evidence: We all have a Top Processor, our personality which controls most of our actions.

adapts to the use to which our personality puts it, this bus structure also adapts to how it is used. Witness the ease of recall on an often used phone number versus the difficulty in recall of a seldom used number. We might guess that somehow the bus structure is under adaptive software control.

### The Main Processor

We now arrive at the general purpose powerhouse of the computing system. The Main Processor handles awe inspiring problems with unbelievable speed. We must postulate:

- 1. Elegantly simple programming.

- 2. Operation at a fast effective clock rate.

- 3. An outstandingly efficient internal executive program.

- 4. Access to the bulk of stored programs and data.

- 5. A complex priority interrupt system.

- 6. A multiple bus structure to the rest of the human system.

### Main Processor Speed of Execution

The Main Processor is a very fast machine operating on elegant and simple programming. For instance, some of the muscle control programs must take only 20 to 50 milliseconds for completion of:

- 1. Input of data.

- 2. Computation on new data.

- 3. Output of control commands.

- 4. Cleanup for next computation period.

Navigation and guidance computation periods can be longer. However, they can not be much longer when we watch a small boy pick up a rock and knock a can off a fence post, all in the space of two to three seconds. Another awe inspiring feat is the performance of a businessman in his value judgment search as he keeps abreast of the rapid fire conflicts in the executive boardroom. The Main Processor seems to be an order of magnitude faster than the Top Processor (witness the increase in touch typing speed when the Top Processor gets out of the act). as circulation, digestion, elimination, etc.

5. Start and stop background tasks such as meditation.

The quantity and variety of data used by the Main Processor in combination with the rapid response in answer to massive and conceptually difficult problems implies' a very efficient software organization. The Main Processor must access tables that define the location of:

- 1. Stored life history data.

- 2. Muscle control programs.

- 3. Chemical control programs.

- 4. Temperature control programs.

- 5. Guidance programs.

- 6. Navigation programs.

- 7. Value judgment data.

- 8. System priority data.

- 9. System timing data.

- 10. Unused memory.

### The Main Processor Decision Process

One of the most interesting functions of the Main Processor is to aid in the decision process we use when faced with alternate courses of action in response to events in the world around us. The evidence implies that the Main Processor takes formulation of the decision problem and the pertinent data from the Top Processor and Sensor Processors. These inputs are then heuristically compared to an immense value judgment table to generate a candidate decision. The candidate decision is sent to the Top Processor for further evaluation.

The Value Judgement Table

### The Main Processor's Executive Program

The executive program provides for scheduling Main Processor tasks that:

- 1. Field emergency interrupts such as avoidance of a fast moving object detected on visual sensors.

- 2. Take calls from the priority stack such as recognizing hunger and thirst.

- 3. Time share muscle control and evaluation of sensor data when both are active as in soccer game.

- 4. Regularly service body functions such

This table has a strong effect on the pathway we follow in life, from when we make the decision to start breathing until we are forced to stop breathing. How do entries appear in this table? Some entries must appear while we are within our mother. A new born infant makes the decision to start breathing or has an early death. Some entries come from trial and error experience. The young infant soon learns to cry just so mother will pick him up.