UNDERSTANDING DIGITAL ELECTROMES RH. Worring

# Michael J. Sanfilippo SECONDEDITION

# Understanding Digital Electronics

2<sup>nd</sup> Edition R. H. Warring and Michael J. Sanfilippo

This second edition is dedicated to my mother. Her courage and inspiration have given me an example of dedication and commitment that I shall always remember, and I shall ever be grateful to her.

-M. J. Sanfilippo

#### SECOND EDITION FIRST PRINTING

Understanding Digital Electronics was originally published in 1984. Printed by permission of Lutterworth Press.

#### Copyright © 1990, 1984 by R.H. Warring Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. The publisher takes no responsibility for the use of any of the materials or methods described in this book, or for the products thereof.

#### Library of Congress Cataloging-in-Publication Data

Warring, R. H. (Ronald Horace), 1920-1984

Understanding digital electronics / by R.H. Warring and Michael J. Sanfilippo. - 2nd ed.

p. cm. ISBN 0-8306-9226-6 TK7868.D5W37 1989 621.381-dc20

ISBN 0-8306-3226-3 (pbk.) 1. Digital electronics. I. Sanfilippo, M. J. II. Title 89-36603

CIP

TAB BOOKS Inc. offers software for sale. For information and a catalog, please contact TAB Software Department, Blue Ridge Summit, PA 17294-0850.

Questions regarding the content of this book should be addressed to:

**Reader Inquiry Branch** TAB BOOKS Inc. Blue Ridge Summit, PA 17294-0214

Acquisitions Editor: Kimberly Tabor Technical Editor: Alyson Grupp Production: Katherine Brown

# **Contents**

# Introduction

iv

14

30

47

**Basic Digital Concepts** Analog Systems-Digital Systems-Digital Terminology-Binary Numbers-Truth Tables

#### **Symbols and Switches** 2

Digital Logic Gates—Memory—Simple Switching Functions-Series and Parallel Working-Simple Electronic Switches-Improving Transistor Switch-Off Times—Diode Switching—Schottky Diodes-Unijunction Transistors-Thyristors-**Bounce-Free Switches**

Mathematical Logic (Boolean Algebra) 3

Basic Logic-Solving Problems-Boolean Algebraic Theorems

# **Logic Circuit Devices**

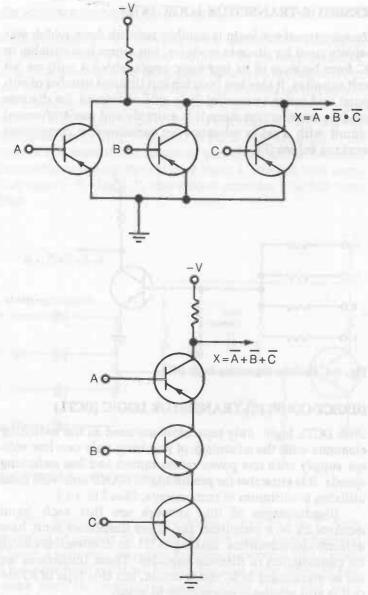

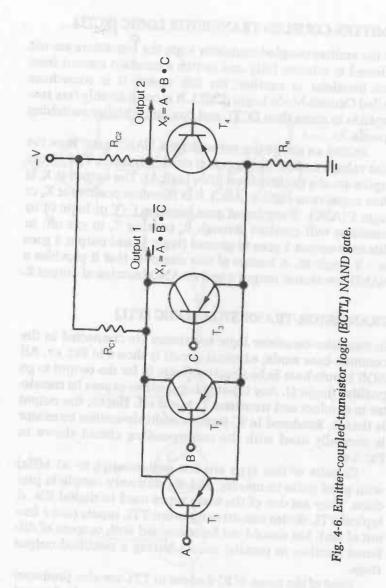

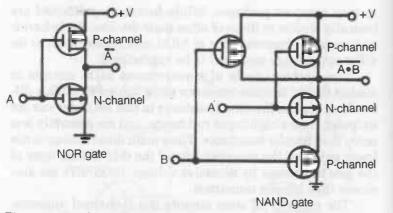

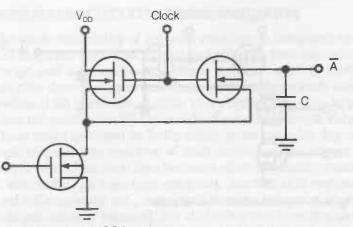

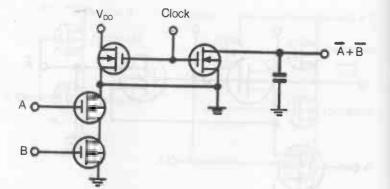

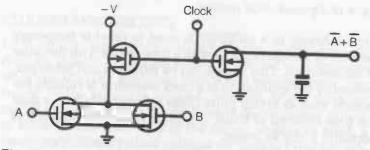

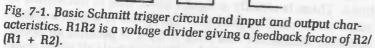

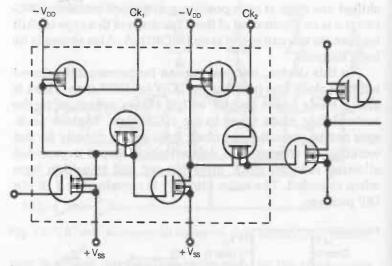

Diode-Transistor Logic (DTL)-Resistor-Transistor Logic (RTL)-Direct-Coupled-Transistor Logic (DCTL)-Emitter-Coupled-Transistor Logic (ECTL)-Transistor-Transistor Logic (TTL)-MOSFETs-Complementary MOS (CMOS)-MOS Logic-Clocked MOS Circuits-Dynamic MOS Inverters-Dynamic MOS NAND Gates-Handling MOS Devices-Integrated Circuits and Minimization-Standard IC Gates-Multiple Gate ICs-IC Buffers-Schmitt Trigger—Complex ICs—Digital Families Compared

#### **Flip-Flops and Memories** 5

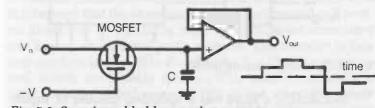

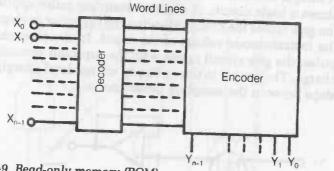

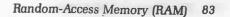

RS Flip-Flops-D Flip-Flops-JK Flip-Flops-The IK Master-Slave Flip-Flop-Sample-and-Hold-Read-Only-Memory (ROM)-Random-Access Memory (RAM)-Registers

# 6 Number Systems

85

Binary Coded Decimals—Types of Codes—Parity Bits—Other Number Systems—Handling Fractions

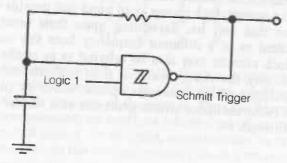

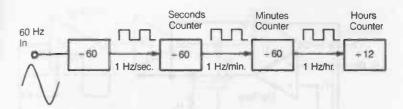

# 7 Digital Clocks

97

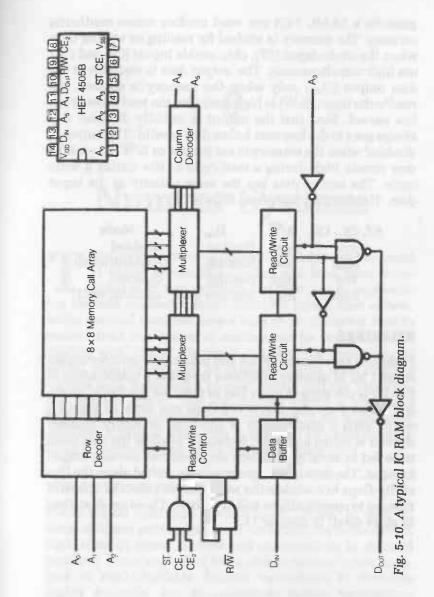

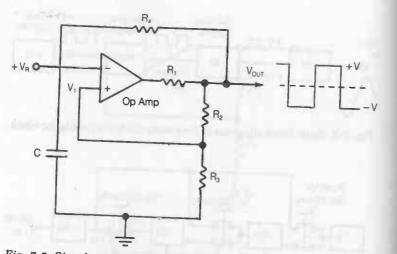

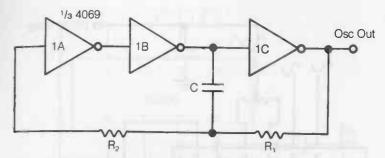

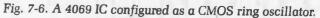

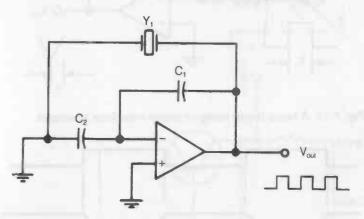

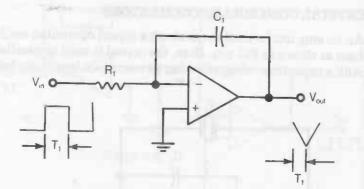

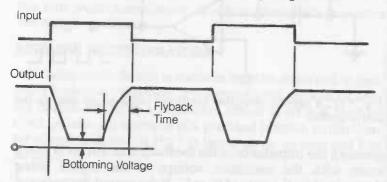

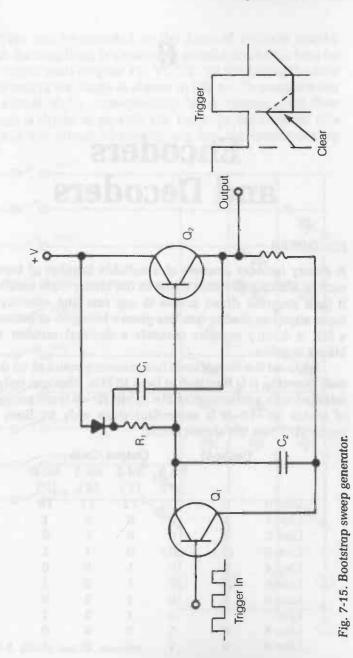

Operational Amplifier Clocks—IC Oscillators— Monostable Multivibrators—Bistable Multivibrators— Crystal Controlled Oscillators—Sweep Generators— Schmitt Trigger—IC Digital Clock

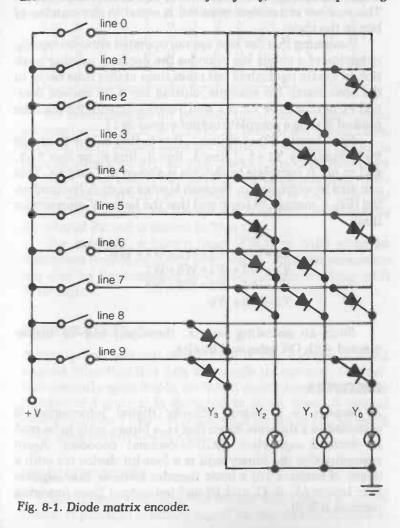

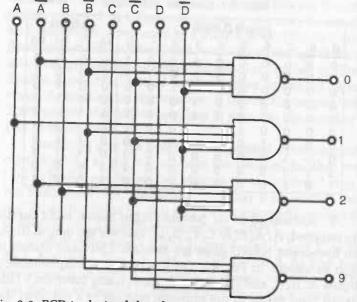

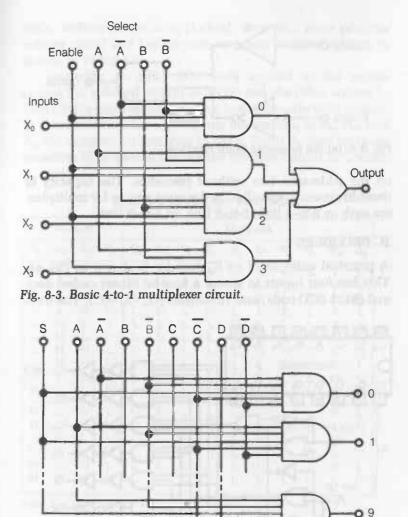

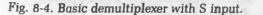

# 8 Encoders and Decoders

108

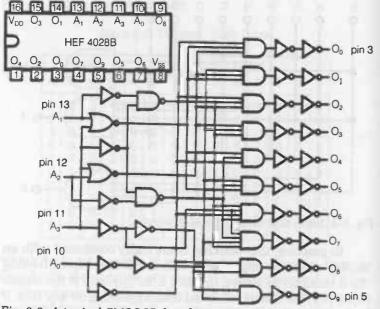

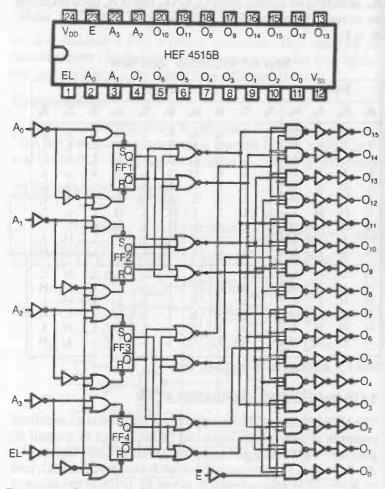

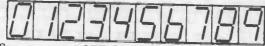

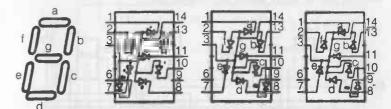

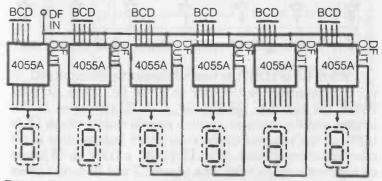

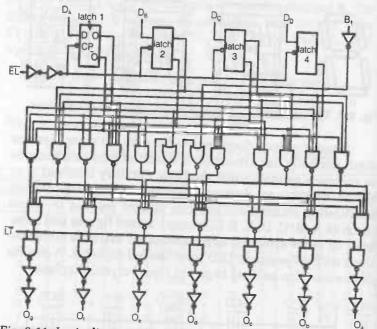

Encoders—Decoders—Multiplexers—Demultiplexers—IC Decoders—1-of-16 Decoder/Demultiplexer—LED Readout—Display Drivers

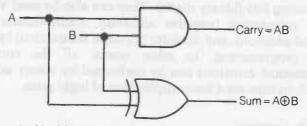

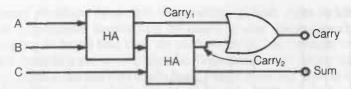

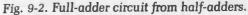

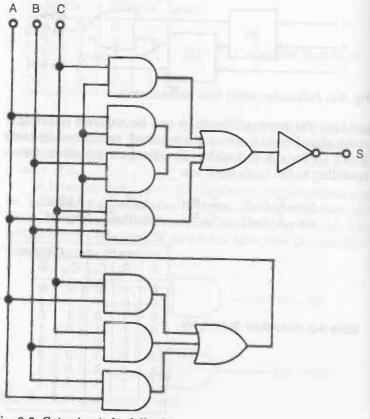

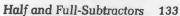

# 9 Digital Adders

123

Binary Adders—Half-Adders—Full-Adders—Binary Subtractors—Serial Adder/Subtractor—Half and Full-Subtractors

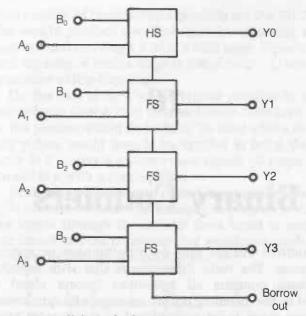

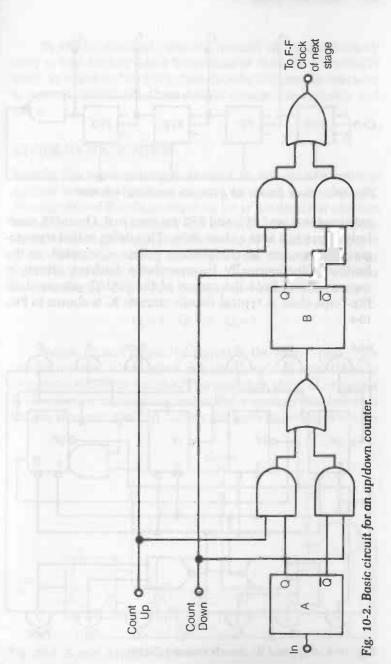

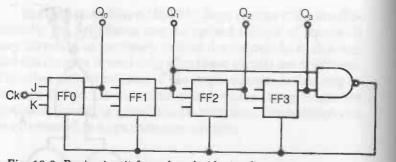

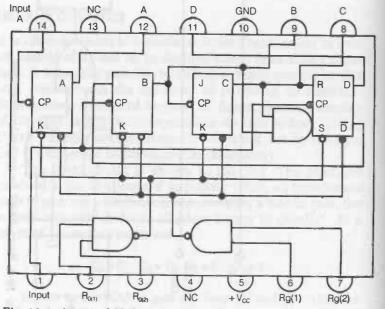

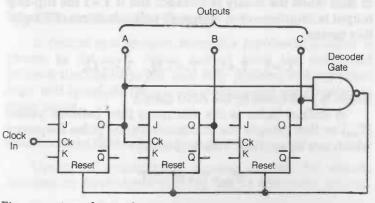

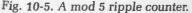

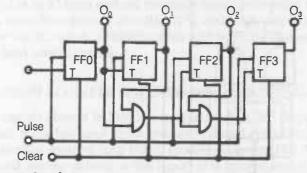

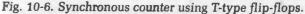

**10 Binary Counters**

134

The Basic Ripple Counter—Reversible Counter—Decade Counter—Divide-by-N Counter— Synchronous Counters—Johnson Counter (Twisted Ring Counter)—IC Binary Counters—IC Synchronous Counters

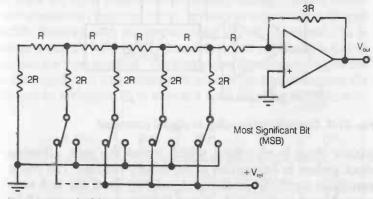

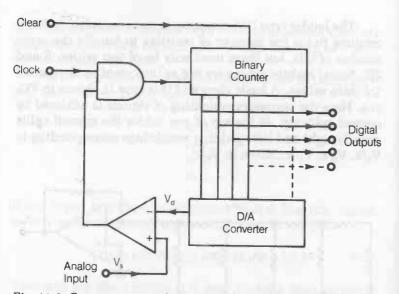

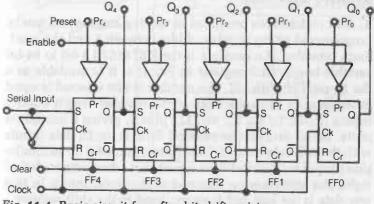

11 Converters and Registers146

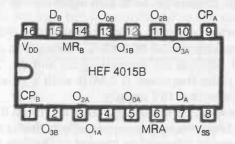

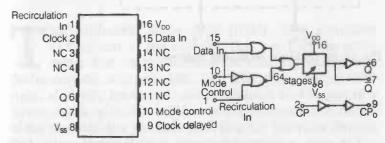

Digital-to-Analog Converters (D/A)—Analog-to-Digital Converters (A/D)—Shift Registers—IC Shift Register— Dynamic MOS Shift Register

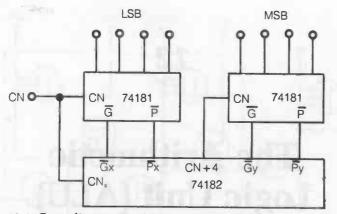

12 The Arithmetic Logic Unit (ALU) 157

Cascading ALUs—ALU Functions—Microprocessors

# **Appendices**

| A | <b>Binary/Decimal Equivalents</b>   | 168 |

|---|-------------------------------------|-----|

| B | Simplifying Digital Logic Circuitry | 173 |

| С | Computer Programming                | 182 |

|   | Index                               | 184 |

# Introduction

The book you are about to read, the second edition of Understanding Digital Electronics, has been completely revised and is very much up to date. Digital electronics, however, is constantly changing. It requires continuous review, vigilant reading, and constant experimenting from all of us who are a part of this exciting, everwidening area of study and want to remain knowledgeable about it.

When I first undertook this project, I looked at this as an opportunity to review another writer's work and to perhaps, in some small way, add newer bits (no pun intended) of information to it. As a published author myself (Solid-State Electronics Theory with Experiments, TAB Books, 1987) I knew the amount of effort required to research, write, and illustrate a technical book. In that sense, this book was very much a challenge.

The majority of the chapters in this second edition contain all new circuit diagrams and most contain information not found in the first edition. Existing diagrams were corrected to reflect electronic symbols used in this country. Most concepts were expanded upon and explained in simpler, layman's terms.

The most pronounced change is in the last chapter, "The Arithmetic Logic Unit (ALU)." The original book

#### vi Introduction

based the theory of the ALU on a device foreign to us here in the United States. I found it more appropriate to base ALU theory on the 74181, a device common to many electronic circuit labs in technical schools throughout the country.

Also, binary arithmetic, along with a great many other topics, was added to this second edition. This book is, therefore, considerably more complete and up-to-date than its predecessor. That is not to say that it is all-inclusive; no book ever is. It does reflect a somewhat simpler approach with more information.

My intentions, then, were to strive for a second edition which would be more enjoyable and easier to understand without sacrificing the good intent of the first edition author. I hope I have achieved those objectives and have instilled in you, the reader, a desire for further study of digital electronics and eventually, microprocessors.

# **Basic Digital Concepts**

O understand digital electronics, you first need to understand the terms digital electronics and analog electronics, as well as the basic differences between the two. This will help those of you with a knowledge of basic and/or solid-state electronics identify with digital concepts. If you don't have an electronics background, you will find that digital concepts are relatively easy to understand. This chapter deals with some of those concepts and shows the simplicity, and hence the beauty, of digital electronics.

We will explain some advantages and disadvantages of each type of system or concept, then introduce binary arithmetic, and finally provide some information about truth tables. Truth tables are an invaluable tool in designing and troubleshooting all kinds of digital electronic circuits, from the simplest to the most complex.

## ANALOG SYSTEMS

Analog systems offer a faster response to changes in the analog input signal, and less distortion in systems designed to amplify and reproduce the input analog signal.

However, analog systems also involve higher power dissipation, more weight, larger size (usually translated to higher

**Binary Numbers 3**

costs), and greater sensitivity to environmental, or temperature, changes.

# **DIGITAL SYSTEMS**

Digital systems have many advantages, including smaller size, less power dissipation, lower costs, lighter weight, and less sensitivity to environmental changes.

Disadvantages of digital systems are few, and are becoming less and less as our manufacturing processes and engineering capabilities improve. The most significant are induced distortion, which is an inherent effect of converting an analog input signal into a digital output signal (A to D or A/D conversion); and a comparatively long response time in performing the opposite operation (D to A or D/A conversion). Today's technology has reduced that response time, but it is still a considered factor in electronic circuit design.

# **DIGITAL TERMINOLOGY**

Digital electronics uses a relatively new vocabulary. It is a vocabulary filled with terms that are very logical. They also provide you with a useful base of electronic terms, which is helpful if you plan to study further those areas of electronics that include microprocessors and circuits that are controlled by microprocessors.

Some of these terms are AND gates, OR gates, NAND gates, NOR gates, and NOT gates. The most important of these are the AND, OR, and NOT gates. Almost all of today's digital computers operate on the concepts of these three simple digital electronic devices.

#### **BINARY NUMBERS**

Digital systems employ binary devices which function in only two states. (Binary simply means two.) These two states are described in various ways:

- on/off or close/open for switching devices

- 1/0 for counting or computing devices

- true/false or yes/no for logic devices

- pulse/no pulse for trigger circuits

- high/low for practical circuits where voltage levels are relative (i.e., a low signal is not necessarily zero)

All these pairs of terms mean the same thing, one state or the other, with no intermediate state. This is the whole basis of digital (binary) working.

Binary numbers are based on just two digits, 1 and 0. Individual digits in a binary number then represent equivalent powers of 2, instead of 10 as in the decimal system. A particular advantage of the binary system is that there are no multiplication tables as such, and any problem involving addition, subtraction, multiplication, or division can be broken down into a series of individual binary operations, with each switching element in the system being continuously used (that is, either in the on or off state).

Compared with the decimal system, binary numbers are tedious as a written language. For example, TABLE 1-1 shows the binary equivalents of decimal numbers from 1 to 32.

Remembering that the binary system is based on powers of 2, the simplest way to derive the binary equivalent of a large decimal number is to subtract the highest power of 2 contained by the number, then subtract the highest power of 2 from the remainder, and so on until only a 1 or 0 is left as the remainder. For example, to find the binary equivalent of the decimal number 269, perform the following operation:

The highest power of 2 within 269 is  $2^8 = 256$ . This leaves 269-256 = 13. The highest power of 2 within this remainder is  $2^3 = 8$ . This leaves 13-8 = 5.

| Decimal             | Binary<br>Number | Decimal                           | Binary<br>Number |

|---------------------|------------------|-----------------------------------|------------------|

| 1 (2º)              | 1                | 17                                | 10001            |

| 2 (21)              | 10               | 18                                | 10010            |

| 3                   | 11               | 19                                | 10011            |

| 4 (2 <sup>2</sup> ) | 100              | 20                                | 10100            |

| 5                   | 101              | 21                                | 10101            |

| 6<br>7              | 110              | 22                                | 10110            |

|                     | 111              | 23                                | 10111            |

| 8 (23)              | 1000             | 24                                | 11000            |

| 9                   | 1001             | 25                                | 11001            |

| 10                  | 1010             | 26                                | 11010            |

| 11                  | 1011             | 27                                | 11011            |

| 12                  | 1100             | 28                                | 11100            |

| 13                  | 1101             | 29                                | 11101            |

| 14                  | 1110             | 30                                | 11110            |

| 15                  | 1111             | 31                                | 11111            |

| 16 (2⁴)             | 10000            | 32 (2 <sup>5</sup> )<br>and so on | 100000           |

Table 1-1. Decimal-To-Binary Conversion

The highest power of 2 within this remainder is  $2^2 = 4$ . This leaves 5-4 = 1.

The corresponding number is thus  $2^8+2^3+2^2$  with a remainder of 1. Another way to show it is:

| Power       | Binary    |   | Decimal     |

|-------------|-----------|---|-------------|

| $2^{8} =$   | 100000000 | = | 256 decimal |

| $2^{3} =$   | 1000      | = | 8 decimal   |

| $2^2 =$     | 100       | = | 4 decimal   |

| remainder = | 1         | = | 1 decimal   |

|             | 100001101 | = | 269 decimal |

This binary number is long, consisting of 9 digits (bits). It counts in a system involving only 1 or 0 so it can readily be handled by digital devices. The number of bits (binary digits) to be handled in a calculation does not represent any practical limitation. The speed at which these devices can work is extremely high. Here, for example, is the number of bits different types of digital circuit devices can handle per second:

MOS(metal-oxide-semiconductor): 3-4 million CMOS(complementary-metal-oxide-semiconductor): 10-15 million HTL(high-threshold-logic): 20 million DTL(diode-transistor-logic): 35 million RTL(resistor-transistor-logic): 80 million TTL(transistor-transistor-logic): 170 million ECL(emitter-coupled-logic): 250-1000 million

# **Binary Arithmetic**

Adding and subtracting can be performed in binary just as in decimal, but certain rules must be followed when using binary digits or bits:

| Addition   | Subtraction |

|------------|-------------|

| 0 + 0 = 0  | 0 - 0 = 0   |

| 0 + 1 = 1  | 1 - 1 = 0   |

| 1 + 0 = 1  | 1 - 0 = 1   |

| 1 + 1 = 10 |             |

| 1+1+1 = 11 |             |

As you can see, remembering these rules makes adding and subtracting binary numbers quite simple. An example of adding two binary numbers is shown below:

| Binary | <b>Decimal Equivalent</b> |

|--------|---------------------------|

| 1011   | 11                        |

| +100   | +4                        |

| 1111   | 15                        |

Here is an example of binary subtraction:

Truth Tables 7

## 6 Basic Digital Concepts

| Binary | <b>Decimal Equivalent</b> |

|--------|---------------------------|

| 11011  | 27                        |

| -1001  | -9                        |

| 10010  | 18                        |

In digital electronic circuits, devices called half adders and full adders perform binary addition and subtraction. Additional information on these types of circuits may be found in chapter 10.

#### **Binary Coded Decimal**

To simplify working with large numbers a hybrid system known as a binary coded decimal (BCD) is normally used. Here, separate groups of binary digits are used to express units, tens, hundreds, etc. Since each binary group needs to be able to accommodate a count of up to 9, it must consist of four digits; that is, to accommodate 9 it must run 1001. (Refer to TABLE 1-1.)

The number 269 (100001101 in the binary system) is, as a binary coded decimal:

#### 0010 0110 1001

equivalent to

# 2 6 9

in decimal numbers.

For the next number up, 270, the right-hand binary group changes to 1010, representing 10, which is immediately carried forward into the next group. The binary coded decimal would then read:

#### 0010 0111 0000

equivalent to

2 7

0

in decimal numbers.

Binary coded decimal systems are described further in chapter 7.

#### **TRUTH TABLES**

Table 1

Truth tables are an easily-understood way to represent the way digital devices and circuits work. They are widely used with Boolean Algebra (discussed in chapter 4) to solve circuit design problems. A truth table lays out the complete range of signal states for a device in terms of 1 (signal on) or 0 (signal absent).

Starting with the simplest device, an inverter or NOT gate, there is one signal input, A (which may have a state of 0 or 1) and one signal output, X. An inverter makes the state of output X the inversion or opposite of input A. The truth table then reads as shown in TABLE 1-2. This fully expresses all of the possible working states (two in this case) of the inverter, sometimes referred to as a NOT logic element or gate.

|                     | A | X |   |

|---------------------|---|---|---|

| -2. NOT Truth Table | 0 | 1 | 1 |

|                     | 1 | 0 |   |

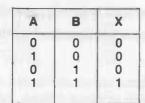

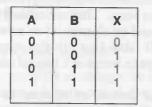

All other devices have more than one input. A basic rule to follow here in compiling a truth table is that with series logic, all the inputs must be 1 before the output can be 1, and with parallel logic the output is always 1 if any of the inputs is 1. This is equally well explained by mechanical thinking, since parallel logic is the equivalent to a number of on-off switches connected in parallel (any one switch which is on will pass a signal) and series logic is equivalent to a number of on-off switches connected in series where all of the switches must be on before a signal can be passed. The basic truth tables for such devices, written for two inputs, are shown in TABLES 1-3 and 1-4.

# 8 Basic Digital Concepts

Table 1-3. Series Logic

Table 1-4. Parallel Logic

An example of a truth table for an OR gate, sometimes called an OR logic element, with two inputs is shown in TABLE 1-5. It is, in fact, an example of a parallel logic device. Expanded to cover more than two inputs, the same basic rule applies. X equals 1 when any input equals 1. TABLE 1-6 illustrates the truth table for a four-input OR gate. There are, as you can see, sixteen different states possible with any fourinput gate. In the case of the OR device, fifteen of these give the output signal.

|   | A | в | X |      |

|---|---|---|---|------|

| 1 | 0 | 0 | 0 |      |

|   | 1 | 0 | 1 | Tabl |

|   | 0 | 1 | 1 |      |

| 1 | 1 | 1 | 1 |      |

| L |   |   |   |      |

Table 1-5. OR Truth Table

An example of series logic is the AND gate. Its basic truth table for a two-input device is shown in TABLE 1-7.

TABLE 1-8 is an illustration of the AND gate written out for four inputs. Again, there are sixteen possible different states, but only one provides an output of X=1. With sixteen switches connected in series (in mechanical terms) the path through them from input to output remains broken until all the switches are on.

|    | A               | в             | С                                                                       | D                 | X                                       |

|----|-----------------|---------------|-------------------------------------------------------------------------|-------------------|-----------------------------------------|

|    | 010001111100001 | 0010011011101 | 0<br>0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 0                 | 011111111111111111111111111111111111111 |

|    | 1               | 0             | 0                                                                       | 0                 | 1                                       |

|    | 0               | 1             | 0                                                                       | 0                 | 1                                       |

|    | 0               | 0             | 1                                                                       | 0                 | 1                                       |

|    | 0               | 0             | 0                                                                       | 1                 | 1                                       |

|    | 1               | 1             | 0                                                                       | 0                 | 1                                       |

|    | 1               | 0             | 1                                                                       | 0                 | 1                                       |

|    | 1               | 0             | 0                                                                       | 1                 | 1                                       |

|    | 1               | 1             | 1                                                                       | 0                 | 1                                       |

|    | 1               | 1             | 0                                                                       | 1                 | 1                                       |

|    | 1               | 0             | 1                                                                       | 1                 | 1                                       |

|    | 0               | 1             | 1                                                                       | 1                 | 1                                       |

| 14 | 0               | 1             | 0                                                                       | 1                 | 1                                       |

|    | 0               | 1             | 1                                                                       | 1                 | 1                                       |

|    | 0               | 0             | 1                                                                       | 1                 | 1                                       |

|    | 1               | 1             | 1                                                                       | 00001001011111111 | 1                                       |

|    |                 |               |                                                                         |                   |                                         |

Table 1-7. AND Truth Table

Table 1-6. Four-Input OR Gate

| A | в | X |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

Table 1-8. Four-Input AND Gate

|   | A                                                             | в                                                                       | С                                                                       | D               | x                                                                                      |

|---|---------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------|

|   | 0                                                             | 0                                                                       | 0                                                                       | 0               | 0                                                                                      |

|   | 1                                                             | 0                                                                       | 0                                                                       | 0               | 0                                                                                      |

|   | 0                                                             | 1                                                                       | 0                                                                       | 0               | 0                                                                                      |

|   | 0                                                             | 0                                                                       | 1                                                                       | 0               | 0                                                                                      |

|   | 0                                                             | 0                                                                       | 0                                                                       | 1               | 0                                                                                      |

|   | 1                                                             | 1                                                                       | 0                                                                       | 0               | 0                                                                                      |

|   | 1                                                             | 0                                                                       | 1                                                                       | 0               | 0                                                                                      |

|   | 1                                                             | 0                                                                       | 0                                                                       | 1               | 0                                                                                      |

|   | 1                                                             | 1                                                                       | 1                                                                       | 0               | 0                                                                                      |

|   | 1                                                             | 1                                                                       | 0                                                                       | 1               | 0                                                                                      |

|   | 1                                                             | 0                                                                       | 1                                                                       | 1               | 0                                                                                      |

|   | 0                                                             | 1                                                                       | 0                                                                       | 1               | 0                                                                                      |

|   | 0                                                             | 1                                                                       | 1                                                                       | 1               | 0                                                                                      |

|   | 0<br>1<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>1 | 0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>1 | 0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>1<br>1 | 000010010111111 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1 |

|   | 1                                                             | 1                                                                       | 1                                                                       | 1               | 1                                                                                      |

| 1 |                                                               |                                                                         |                                                                         |                 |                                                                                        |

The immediate reaction to these two examples is probably a feeling that it is much simpler to work in terms of switching equivalents than truth tables—and for very simple problems in digital logic it is. However, most problems require a combination of logic devices to provide the solution, which may involve both series and parallel logic. Drawing out the switching circuits can then become a more elaborate process than plotting truth tables and be more susceptible to mistakes.

Truth tables for other logic gates are given below. These are written for two-input devices. They can be expanded to present truth tables for more than two inputs by following the same established pattern.

The truth table for a NOR logic gate with two inputs is shown in TABLE 1-9. This can be identified as inverted series logic. Note also that inversion has changed the parallel logic of the OR gate to series logic in the case of the NOR (Not OR) gate. The significance of this occurs frequently when working with Boolean Algebra.

| в | X      |     |

|---|--------|-----|

| 0 | 1      | Tal |

| 1 | 0<br>0 |     |

|   | 0      | 0 1 |

Table 1-9. NOR Truth Table

The truth table for a NAND gate with two inputs is shown in TABLE 1-10. This can be identified as inverted parallel logic. Inversion has changed the series logic of AND to parallel logic in the case of NAND (Not AND).

| A | В | <b>X</b> <sub>1</sub> |                          |

|---|---|-----------------------|--------------------------|

| 0 | 0 | 0                     | Table 1-10. OR Truth Tab |

| 1 | 0 | 1                     |                          |

| 0 | 1 | 1                     |                          |

| 1 | 1 | 1                     |                          |

# **Combinations of Logic Gates**

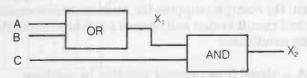

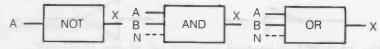

The state of combinations of logic gates can be expressed in the same way as a truth table. Suppose, for example, the design requirement is to provide for input signals A or B to produce an output signal only in combination with a third input signal C. (For example, A and B are trainee operators who can only give a command signal to a machine when the instructor (C) also adds his or her own signal.) FIGURE 1-1 shows how this can be implemented using OR and AND logic.

TABLES 1-10 through 1-12 show how the truth tables are arranged beginning with the OR device or gate, proceeding to the AND device, and finally culminating in the truth table for the combination of both the OR and AND devices. Writing the truth table for the OR device first and calling the output X, is shown in TABLE 1-10. X, is now one of the inputs to the AND device. The truth table for this device is then shown in TABLE 1-11. The combined truth table can then be written as shown in TABLE 1-12. Note that the number of states is equal to the number of devices multiplied by the number of inputs to each device. In this example,  $3 \times 2 = 6$  possible states.

Table 1-11. AND Truth Table

| С | X <sub>2</sub> |

|---|----------------|

| 0 | 0              |

| 0 | 0              |

| 1 | 0              |

| 1 | 1              |

|   |                |

#### 12 Basic Digital Concepts

Table 1-12. OR and AND Truth Table

# **Plotting Truth Tables**

A truth table can be drawn up as a starting point in design. For example, suppose the problem is concerned with a control circuit to start and operate a machine under the following conditions:

A = signal from operator standing by machine

OR D = signal from a remote start

AND B = signal confirming guard is in place

AND C = signal from detector showing workpiece is in place

The machine must not start under any other conditions.

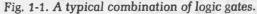

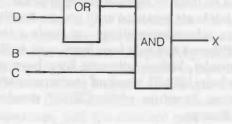

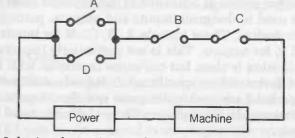

There are four inputs to consider, which results in sixteen possible combinations or states. This establishes the basis for writing out a five-column, sixteen-line truth table. On the output column, 1 must appear only when A = 1 OR D=1 AND B=1 AND C=1. All the other combinations of A, B, C, and D must give X=0. This is shown in TABLE 1-13.

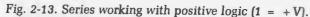

FIGURE 1-2 shows this truth table implemented with logic devices and also with mechanical switches.

| A                                                                                 | В                | С            | D                               | X                                                                                           |

|-----------------------------------------------------------------------------------|------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------------|

|                                                                                   | 0                | 0            | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

| 0                                                                                 | 0                | 0            | 1                               | 0                                                                                           |

| 0                                                                                 | 0                | 1            | 0                               | 0                                                                                           |

| 0                                                                                 | 0                | 1            | 1                               | 0                                                                                           |

| 0                                                                                 | 1                | 0            | 0                               | 0                                                                                           |

| 0                                                                                 | 1                | 0            | 1                               | 0                                                                                           |

| 0                                                                                 | 1                | 1            | 1                               | 1                                                                                           |

| 1                                                                                 | 0                | 0            | 0                               | 0                                                                                           |

| 1                                                                                 | 0                | 0            | 1                               | 0                                                                                           |

| 1                                                                                 | 0                | 1            | 0                               | 0                                                                                           |

| 1                                                                                 | 0                | 1            | 1                               | 0                                                                                           |

| 1                                                                                 | 1                | 0            | 0                               | 0                                                                                           |

| 1                                                                                 | 1                | 0            | 1                               | 0                                                                                           |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0000111000011111 | 001100110011 | 0                               | 1                                                                                           |

| 1                                                                                 | 1                | 1            | 1                               | 1                                                                                           |

Table 1-13. Truth Table Used for Design

Fig. 1-2. Logic solution (top) and implementation with mechanical switches (bottom).

#### I TABLE INTO A COMPANY

# 2

# **Symbols and Switches**

NE of the most confusing things about the use of symbols representing the various logic elements or gates is that the original (and literally logical) way of designating them in the form of annotated blocks has largely been abandoned in favor of representative symbols, the significance of which is not apparent until you are familiar with them. Even then, misunderstandings can easily arise, since over the years different symbols have been used to illustrate the same function(s). Various attempts have been made to standardize symbols; US MIL standard recommendations are used in American literature while CETOP standards are widely used in Europe.

Another source of confusion is that different letter symbols are used to designate inputs and outputs, particularly for basic devices. These include A, B, C...N for inputs and W, X, Y, Z for outputs. This is not particularly important if the application is clear, but can cause confusion with more complex devices where specific symbols (and sometimes different symbols) are used to designate specific integrated circuit (IC) terminals. Examples are Ck for clock input and D for data input.

# **DIGITAL LOGIC GATES**

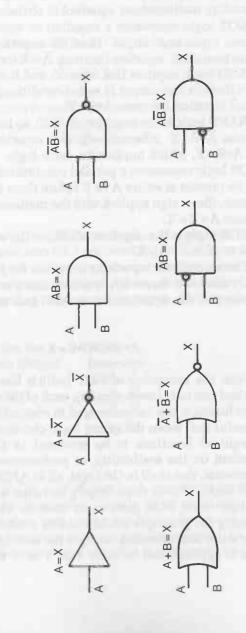

The simple block method of symbolizing logic elements is obvious, readily readable, and needs no extensive description. All symbols are in the form of a rectangular block with the function written inside. Input lines are added to the left side of the block and an output line to the right. FIGURE 2-1 shows a number of representative logic elements with two or more inputs and one output each. (The NOT gate has only one input.) For the sake of consistency, separate inputs are designated A, B, C, etc. The output line is designated X. The value 1 is used to designate a signal present, and a 0 represents no signal at that line.

Fig. 2-1. Examples of block logic symbols and annotation.

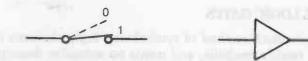

Such block symbols are rarely used now, except in elementary textbooks, so you need to know the alternate forms of other basic symbols. Each function is dealt with separately and is illustrated with its corresponding mechanical switching function. (Devices are restricted to two inputs for simplicity.) The switching function is shown as 1 in the operated position and 0 in the off position. As you can see in the following drawings, both the standard gate symbol and, where appropriate, its mechanical switch equivalent are represented.

# The YES Gate

The YES gate is a 1-input, 1-output device with input and output always the same; that is, A=0, X=0; or A=1, X=1, where A is the input signal and X is the output signal. The YES gate is also referred to as a *buffer*. The symbol for a YES gate is shown in FIG. 2-2.

Fig. 2-2. YES logic symbols.

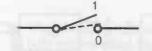

# The NOT Gate (Inverter)

The NOT gate, a 1-input, 1-output device, works the other way round to the YES gate. If there is an input to A, there is no output at X and vice versa (that is, A=1, X=0; or A=0, X=1). The symbols in FIG. 2-3 show this inverted mode of working by means of a circle on the output side.

Fig. 2-3. NOT logic symbols.

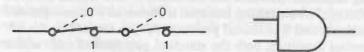

#### The AND Gate

The AND gate produces a logic level 1 at its output only when both inputs, A and B, are at logic level 1. (See FIG. 2-4.) In mechanical form, it is two switches in series.

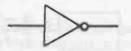

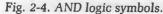

#### The NAND Gate

The NAND gate is an inverted form of the AND gate where there is a logic level 1 output for all input states except when both A = 1 and B = 1; in that case, X = 0. (See FIG. 2-5.)

Fig. 2-5. NAND logic symbols.

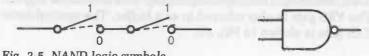

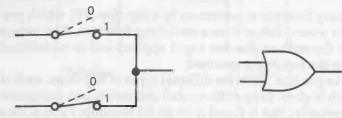

#### The OR Gate

The OR gate is the equivalent of a parallel switching circuit. When either switch is closed, or both switches are closed, there is an output. (See FIG. 2-6.)

Fig. 2-6. OR logic symbols.

#### The NOR Gate

The NOR gate is the inverted form of the OR gate, so once again the symbols have the inversion mark (a circle on the output side) added, as shown in FIG. 2-7. Note that the switches are normally closed and there is an output (X=1) only when both A=0 and B=0.

Fig. 2-7. NOR logic symbols.

# The Exclusive OR (XOR) Gate

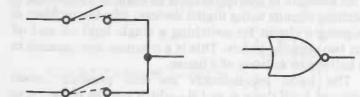

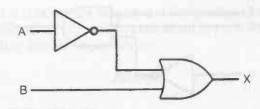

The exclusive OR gate is a special form of AND logic providing an output only when one particular input is equal to 1. If a 1 appears at the other input, it is inhibited or inverted to 0. Basically, in fact, this is an AND gate with one input inverted. FIGURE 2-8 shows the symbol for the exclusive OR (XOR) gate.

Fig. 2-8. Exclusive OR (Ex-OR) gate logic symbol.

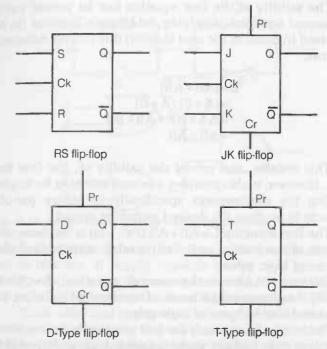

## MEMORY

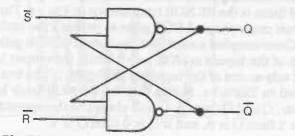

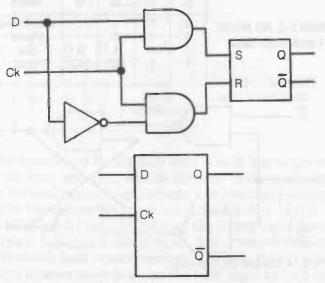

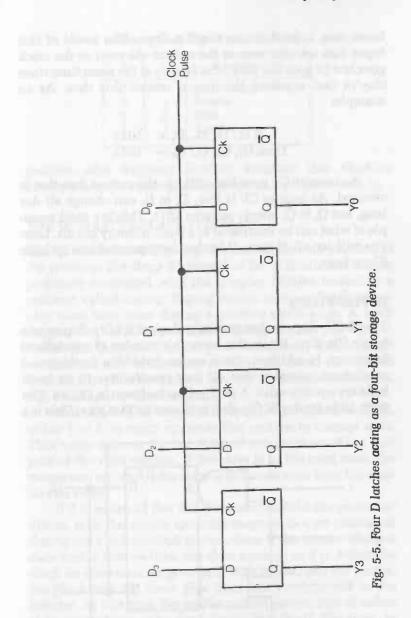

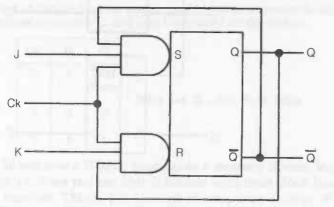

Memory function is performed by a flip-flop (FF) which performs a store rather than a switching function. The output state depends on the last input applied and is maintained when the inputs are resumed.

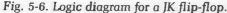

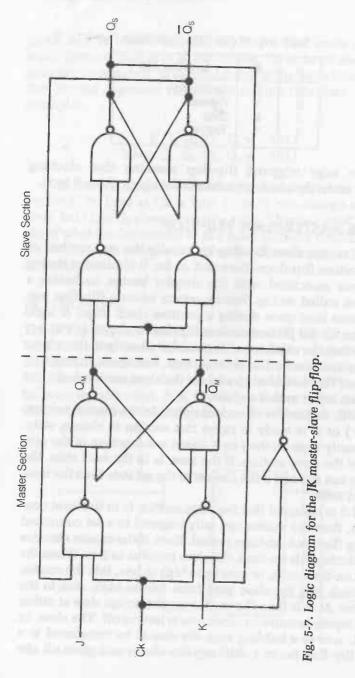

In practice, there are different types of flip-flops, each of which is given its specific symbol and inputs and designated accordingly; that is R and S for an RS flip-flop, J and K for a JK flip-flop, D for a D type flip-flop, and T for a T type flipflop. Outputs are then designated Q and  $\overline{Q}$ . In addition, the flip-flop may have a clock signal input (designated C, or Ck); a clear signal input (C); and a preset input (P) depending on type. These symbols are illustrated in FIG. 2-9. For more detailed information on flip-flops, see chapter 6.

# SIMPLE SWITCHING FUNCTIONS

As an example of the application of logic to the design of switching circuits using digital devices, take the problem of designing a circuit for switching a single light on and off from two separate points. This is a common arrangement in the hallway or stairway of a house.

The basic requirements are two possible inputs (switches)—call them A and B—which may be either on or off. When either A or B is on, there is an output (that is, a circuit completed to light the bulb). A and B cannot be on at the same time. If one is on, operating the other switch switches the light off.

This can be written in the form of a truth table (TABLE 2-1). A 1 under columns A or B represents a switch on and a 1 under column L represents the light on. This can also be expressed in the form of this equation:

|                                     | 1 ~ |   | 1.1 |

|-------------------------------------|-----|---|-----|

| Table 0.4.4                         | 0   | 0 | 1   |

| Table 2-1. 1 = sw. on, 1 = light on | 0   | 1 | •   |

|                                     | 1   | 0 |     |

|                                     | 1   | 1 | (   |

|                                     |     |   | 1   |

This states L = A on AND B off OR A off AND B on. More about equations in the next chapter, but for now a further equation can be written expressing the combinations that do not produce an output; that is, do not switch the light on. This output can be represented by the letter D for dark and follows:

The validity of the first equation can be proved using this second equation. Applying deMorgan's theorem (to be discussed in detail in the next chapter) this second statement becomes:

$$L = (AB + \overline{A}\overline{B})$$

= (A + B) (A + B)

= AA + AB + AB + BE

= AB + AB

This restates, and proves the validity of, the first formula. However, it also provides a second equation for implementing the requirements specifically in binary (on-off) elements to produce the desired switching circuit.

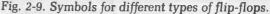

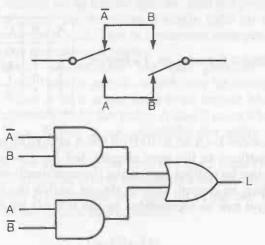

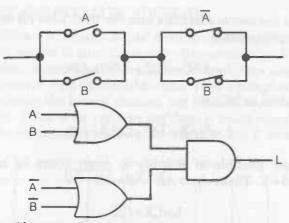

The first equation  $L = \overline{AB} + A\overline{B}$  (FIG. 2-10) is implemented in terms of mechanical switches (or relay contacts) and also in terms of logic gates.

FIGURE 2-11 shows the second equation,  $L = (A+B) \cdot (\overline{A}+\overline{B})$ , implemented in terms of mechanical switches (or relays) and also in terms of logic gates.

FIGURE 2-10 is obviously the best practical solution, since it involves only half the contacts (series logic as opposed to

Fig. 2-10. First solution to switching problem.

Fig. 2-11. Alternate solution to switching problem.

parallel logic). In the case of the gate solutions, the choice is not so obvious. It largely depends on the type gates most readily available. FIGURE 2-10 requires two AND gates and one OR gate. FIGURE 2-11 requires two OR gates and one AND gate.

These solutions may seem overcomplicated for the problem involved. Basically, they are presented to show the principle of digital switching circuit design with a simple, easily-understood example. Suppose we take it one step further to derive suitable circuitry for switching a light on from any of three different switch points.

The starting point is to draw up the truth table as shown in TABLE 2-2. This establishes all the possible input conditions, but does not give any immediate clue as to possible circuit design without drawing out each combination in detail.

Table 2-2. All Possible Combinations

| A | в                     | С                                             | L                                |

|---|-----------------------|-----------------------------------------------|----------------------------------|

| 0 | 0                     | 0                                             | 0                                |

| 0 | 0                     | 1                                             | 1                                |

| 0 | 1                     | 0                                             | 1                                |

| 0 |                       | 1                                             | 0<br>1<br>1<br>0<br>1<br>0<br>0  |

| 1 |                       | 0                                             | 1                                |

| 1 | 0                     | 1                                             | 0                                |

| 1 | 1                     | 0                                             | 0                                |

| 1 | 1                     | 1                                             | 1                                |

|   | 0<br>0<br>0<br>1<br>1 | 0 0<br>0 0<br>0 1<br>0 1<br>1 0<br>1 0<br>1 1 | 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1 |

You can derive a formula from the truth table (or original logic requirements):

$$L = ABC + \overline{ABC} + \overline{ABC} + \overline{ABC} + ABC$$

This factors as follows:

$$L = \overline{C}(A\overline{B} + \overline{A}B) + C(\overline{A}\overline{B} + AB)$$

It is now possible to simplify to some extent by calling  $\overline{AB} + \overline{AB} = X$ . Then, since  $\overline{AB} + \overline{AB} = \overline{AB} + \overline{\overline{AB}}$ :

# $L = \overline{C}X + C\overline{X}$

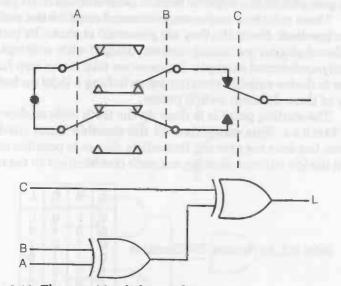

Solutions to this equation implemented in the form of both mechanical switches and exclusive OR logic gates are shown in FIG. 2-12.

Fig. 2-12. Three-position light switching solution.

## SERIES AND PARALLEL WORKING

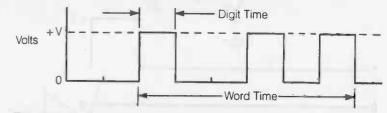

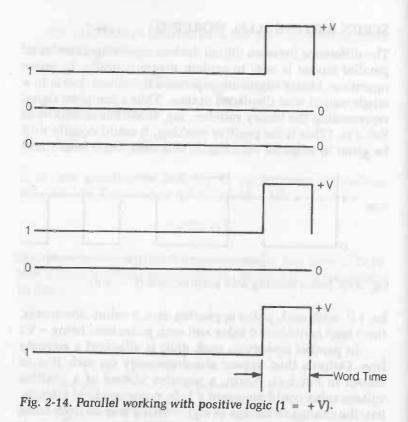

The difference between digital devices operating in series or parallel modes is easy to explain diagramatically. In series operation, binary digits are expressed by voltage levels in a single output wire displaced in time. Thus a complete signal representing the binary number, say, 100101 is as shown in FIG. 2-13. (This is for positive working; it could equally well be given by negative working. In this case, the 0 level could

be + V, with each pulse appearing as a 0 value; alternately, the 0 level could be a 0 value and each pulse level being -V.)

In parallel operation, each digit is allocated a separate line. Outputs then appear simultaneously on each line as shown in FIG. 2-14. Again, a negative instead of a positive voltage value could represent a 1. In many practical circuits, too, the change in voltage or signal swing may be from some nominal voltage representing condition 0 to some more positive (or more negative) voltage representing a 1. In such cases the description HIGH or H is commonly used to designate a 1 signal, and LOW or L represents a 0 signal. In other words, HIGH (or H) is used instead of 1; and LOW (or L) instead of 0.

Series working may appear the logical choice since it needs only one digital device or output wire to handle any number of digits. Parallel working has the disadvantage of requiring n devices or output wires to handle n digits, or n times as much circuit hardware to handle the same information. However, it has the advantage of being n times as fast as series working. In practical circuits, however, both the number of components used and operating time may be modified by other factors.

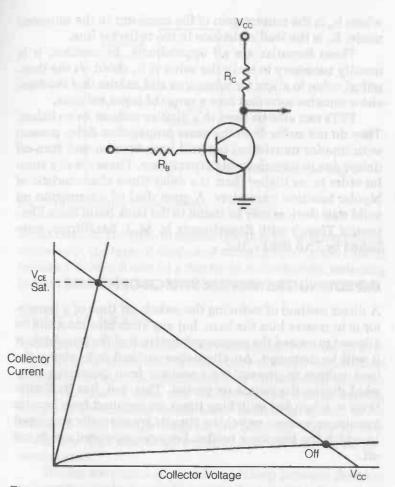

# SIMPLE ELECTRONIC SWITCHES

A bipolar junction transistor can readily work as a switch although its characteristics are not ideal for this purpose. The most usual way of working is in the saturation mode, when the transistor has two stable states, one passing no current (except for leakage current) corresponding to off, and the other in the saturated state passing maximum current and corresponding to on. (See FIG. 2-15.)

In the off condition, the collector voltage approaches  $V_{cc}$ . In the on condition, the collector voltage is  $V_{cc}$ , which is typically on the order of 0.15 to 0.6 volts. However, the transistor is now capable of passing a (relatively) large voltage.

Simplified design parameters for such a switching circuit are:

| Base current             | $I_{B} = V_{CC}/R_{B}$                    |

|--------------------------|-------------------------------------------|

| <b>Collector current</b> | $I_c = V_{cc}/R_c$                        |

|                          | $I_{\rm C} = h_{\rm FR} \times I_{\rm B}$ |

| Bias resistor            | $R_{\rm B} = h_{\rm fe} \times R_{\rm C}$ |

where  $h_{f_e}$  is the current gain of the transistor in the saturated mode.  $R_c$  is the load resistance in the collector line.

These formulas are all approximate. In practice, it is usually necessary to make the value of  $R_B$  about 1/4 the theoretical value to allow for tolerances and ensure that the transistor remains saturated over a range of input voltages.

FETs can also be used in a similar manner as switches. They do not suffer from the same propagation delay present with bipolar transistors, but still have turn-on and turn-off delays due to interelectrode capacitance. These are of a similar order to, or higher than, the delay times characteristic of bipolar junction transistors. A great deal of information on solid state devices may be found in the book Solid State Electronics Theory with Experiments by M. J. Sanfilippo, published by TAB Books, Inc.

# **IMPROVING TRANSISTOR SWITCH-OFF TIMES**

A direct method of reducing the switch-off time of a transistor is to reverse bias the base, but any such bias must not be allowed to exceed the reverse voltage limit of the transistor, or it will be damaged. An alternative method is to clamp the base voltage to prevent the transistor from becoming saturated during the switch-on period. This, too, has its limitations so when fast switching times are required from bipolar transistors, current switching circuits are normally employed in which the transistor neither becomes saturated nor is cut off.

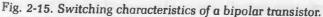

## **DIODE SWITCHING**

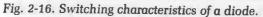

Diode switching characteristics are illustrated in simplified form in FIG. 2-16. When reverse biased there is only a very small leakage current. Application of forward voltage results in an immediate step to +V (forward conduction). The next application of reversed (-V) voltage, however, produces a transient due to stored charge effect, which then decays to the leakage current value. The peak transient reverse current can approach -V/R as a maximum, where R is the resistance

in the circuit. The time to reverse this charge, or storage time, varies with the type of diode and construction. In the case of ordinary diodes it can be a matter of milliseconds, reducing to nanoseconds in the case of high-speed switching diodes.

# SCHOTTKY DIODES

The Schottky diode differs from conventional diodes in having a metal-to-semiconductor function at which rectification occurs. It has specific advantages over conventional junction diodes in that it does not exhibit carrier charge storage effects, thus enabling much faster switching speeds to be achieved. The voltage drop of the Schottky diode is also much less than that of an ordinary diode for the same forward current.

Diodes are commonly used as a clamp between the base and emitter of a transistor to prevent the transistor from entering saturation and to minimize propagation-delay time. It is readily possible to combine a Schottky clamping diode with a transistor as an integral device. Such a combination is called a Schottky transistor.

# UNIJUNCTION TRANSISTORS

Unijunction transistors have two base contacts and an emitter. They become conductive (switch on) at a particular firing

voltage, which typically ranges from 0.5 to 0.85 of the supply voltage. A particular application of the unijunction transistor as a switching device is to generate short pulses when supplied with a varied supply voltage, with pulse rates of up to 1 MHz readily obtainable.

### THYRISTORS

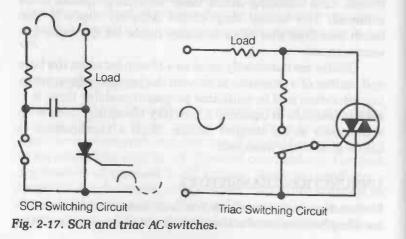

An SCR is basically a silicon diode with an additional cathode electrode known as a gate. If the gate is biased to the same potential as the cathode, it does not conduct in either direction (except for a small leakage current). However, if the gate is biased to be more positive than the cathode, the SCR behaves as a normal diode; that is, it works as a switching element triggered by the application of a positive pulse to the gate.

The triac is similar in construction, except that it has both a cathode and anode gate; hence, it can be triggered by both positive and negative pulses.

SCRs and triacs are also known as thyristors. They are essentially alternating current switches, an SCR being triggered by the positive half of an ac voltage and a triac by both positive and negative halves of an ac voltage. Typical basic switching circuits are shown in FIG. 2-17.

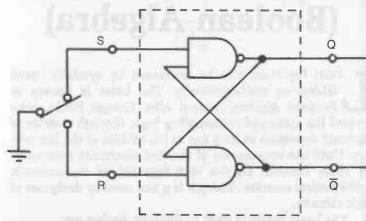

# **BOUNCE-FREE SWITCHES**

Mechanical switches commonly suffer from contact bounce when closed, which can give a spurious signal (especially when switching at rapid rates). This can be avoided by employing a bounce-free (or no bounce) switch. An example is shown in FIG. 2-18, employing an RS flip-flop as a follower for a mechanical switch. The effect of any contact bounce is now to raise both inputs to the flip-flop to logic 1, leaving the outputs unaffected.

1 200 A 100 A

Bine bait we being an about the St. in tent we have

3

# Mathematical Logic (Boolean Algebra)

OGIC functions can be expressed by symbols, truth tables, or mathematically. The latter is known as Boolean algebra, named after George Boole, who devised the system of representing logic through a series of algebraic equations as long ago as the middle of the last century. Until the appearance of the first electronic computers (in 1938) Boolean algebra was regarded as an academic mathematical exercise. Today it is a tool used by designers of logic circuits.

The basic symbols used in Boolean algebra are:

- meaning a series condition or AND logic

- + meaning a parallel condition or OR logic

- meaning negation or opposite condition or NOT logic

At this stage it is best to forget conventional arithmetic where • means multiply and + means add; otherwise, Boolean algebra may be confusing at first. Multiplication and addition do enter into working with Boolean equations, as explained later.

# **BASIC LOGIC**

Basic logic symbols are shown again in FIG. 3-1 with equivalent equations in Boolean algebra.

annotated logic symbols with equivalent Boolean equations.

of

Examples

3-1.

Fig.

YES logic represents a simple continuous condition; that is, the output (X) is the same as the input (A). The corresponding mathematical equation is obviously A = X.

NOT logic represents a negation or opposite condition between input and output. Here the negation sign used in the mathematical equation becomes  $\overline{A} = X$  (or  $A = \overline{X}$ ).

AND logic requires that input A and B are both present before there is any output (a series condition), so the mathematical equation becomes  $A \cdot B = X$ .

NAND logic is the negation of AND, so here the equation becomes  $\overline{A \cdot B} = X$ . Alternatively, this equation can take the form  $A \cdot B = \overline{X}$ , which implies the same logic.

OR logic represents a parallel condition in that an input must be present at either A or B before there is an output. In this case, the + sign applies, and the mathematical equation becomes A + B = X.

NOR logic is the negation of OR, so the negation sign is added to give  $\overline{A} + \overline{B} = X$ .

The above basic equations are given for just two inputs. Exactly the same forms apply where there are more inputs. For example, the equation for an AND gate with five inputs is:

#### $A \bullet B \bullet C \bullet D \bullet E = X$

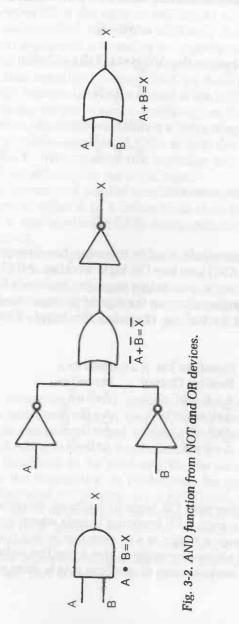

With the exception of NOT (which has only a single input and can only invert signals), each of the expressions for a logic function can be rearranged to obtain the others. This is a useful tool when designing logic circuits, for it enables the required functions to be rendered in the same logic dependent on the availability, or preferences for particular components, that is all in OR logic, all in AND logic, or all in NAND logic. This is done largely by using a NOT function (or single input NOR gate) as an inverter where necessary, and using the principle established by deMorgan's theorem which states that inversion changes the state of the logic each time it is applied; that is, from  $\bullet$  to + or + to  $\bullet$ . For example, starting with the AND function:

$A \bullet B = X$

Inversion changes the AND (•) to OR (+) logic:

$\overline{A} + \overline{B} = \overline{X}$

Inverting again gives a positive output:

$\overline{\overline{A}} + \overline{\overline{B}} = \overline{\overline{X}}$

which is the same as:

A+B=X

In other words, double inversion has changed the function of an AND gate into OR logic working. All of these steps are shown in FIG. 3-2. At this stage, the basic rule to remember is that inversion changes the sign of the equation (except in a NOT gate) as well as changing the input. This is shown below:

|       | Equation For                                                 | With                                                                    |

|-------|--------------------------------------------------------------|-------------------------------------------------------------------------|

| Logic | <b>Positive Output</b>                                       | Inversion                                                               |

| OR    | A + B = X                                                    | $\overline{A} \bullet \overline{B} = \overline{X}$                      |

| NOR   | $\overline{\mathbf{A}} \bullet \mathbf{B} = \mathbf{X}$      | $A + B = \overline{X}$                                                  |

| AND   | $A \bullet B = X$                                            | $\overline{\mathbf{A}} + \overline{\mathbf{B}} = \overline{\mathbf{X}}$ |

| NAND  | $\overline{\mathbf{A}} + \overline{\mathbf{B}} = \mathbf{X}$ | $A \bullet B = \overline{X}$                                            |

#### **OR** Logic

Working with OR logic throughout, equations must use only the + sign, with inversion signals where necessary; that is, to change a  $\bullet$  sign to a + sign producing the same function, and where necessary to give a positive output. The first example worked above shows how this is done with an AND

gate. NAND and NOR functions can be obtained in a similar way.

The NAND function is already in OR logic:

$\overline{A} + \overline{B} = X$

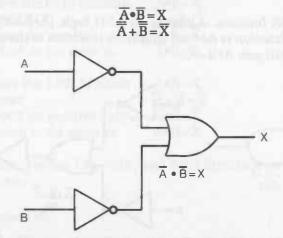

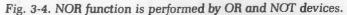

Employing an OR gate to yield a NAND function theory requires inversion of both inputs as shown in FIG. 3-3. The NOR function is in AND logic:

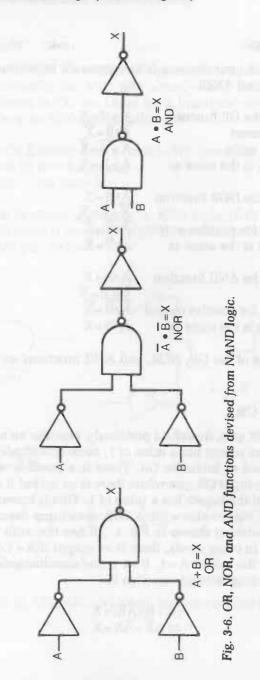

Fig. 3-3. NAND function performed by two NOT and one OR device.

Inversion on inversion puts the equation back to its original state, so this expression simplifies to:

$A + B = \overline{X}$

Thus the NOR function is performed in OR logic by an OR gate followed by a NOT gate for inversion. (See FIG. 3-4.)

## **AND Logic**

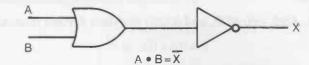

Here the aim is to express all equations with the • (AND) sign. Obviously, an AND gate already does this;  $A \bullet B = X$ and is shown in FIG. 3-5. Other logic functions can be determined from an AND gate as follows:

| The OR function can be provided by inversion | $\overline{A} + \overline{B} = \overline{X}$ |

|----------------------------------------------|----------------------------------------------|

| Check by inverting again                     | $\overline{A} + \overline{B} = \overline{X}$ |

| Which is the same as                         | A + B = X                                    |

The NOR function is already in AND logic ( $\overline{A} \cdot \overline{B} = X$ ). The NAND function is devised simply by inversion of the output of an AND gate  $A \bullet B = \overline{X}$ .

Fig. 3-5. AND, OR, NOR, and NAND functions devised from AND logic.

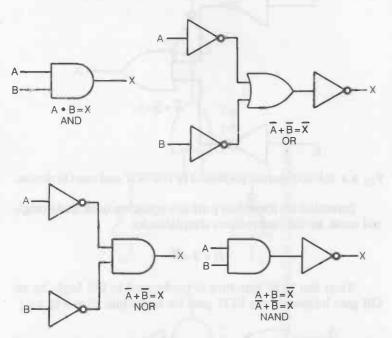

# NAND Logic

Here, the requirement is to express all equations in the form (inverted AND).

| To derive the OR function<br>then invert<br>invert again<br>which is the same as           | $A + B = X$ $\overline{A \bullet B} = \overline{X}$ $\overline{A + B} = \overline{X}$ $A + B = X$                                                                                                                                      |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| To derive the NOR function<br>invert<br>invert for positive output<br>which is the same as | $\overline{\overline{A} \bullet \overline{B}} = X$ $\overline{\overline{A} + \overline{B}} = \overline{X}$ $\overline{\overline{A} \bullet \overline{B}} = \overline{\overline{X}}$ $\overline{\overline{A} \bullet \overline{B}} = X$ |

| To derive the AND function<br>invert<br>invert for positive output<br>which is the same as | $A \bullet B = X$ $\overline{A + B} = \overline{X}$ $\overline{A \bullet B} = \overline{X}$ $A \bullet B = X$                                                                                                                          |

Derivations of the OR, NOR, and AND functions are shown in FIG. 3-6.

#### **Exclusive OR**

The OR gate, described previously, provides an output if one or more inputs has a value of 1. More specifically, it can be described as inclusive OR. There is a possible variation with a two-input OR gate where there is an output if one and only one of the inputs has a value of 1. This is known as the exclusive OR (it is also written XOR, sometimes described as non-equivalence) shown in FIG. 3-7. It has the truth table of TABLE 3-1. In other words, there is an output if A = 1 or B = 1, but not if the values A=1, B=1 occur simultaneously. The corresponding Boolean equation is:

> $(A+B)(\overline{A}\overline{B}) = X$ or  $A\overline{B} + \overline{A}B = X$

Fig. 3-7. Exclusive-OR shown in three different forms.

Table 3-1. Exclusive-OR Truth Table

| In | put | Outpu |  |

|----|-----|-------|--|

| A  | В   | X     |  |

| 0  | 0   | 0     |  |

| 0  | 1   | 1     |  |

| 1  | 0   | 1     |  |

| 1  | 1   | 0     |  |

Incidentally, notice in this equation that the period, or small point, between A and B has been eliminated. In fact, the point is almost never used and is understood as being there when two or more letters follow one another; that is, when they sit side by side.

A particular application of an exclusive OR is as a comparator or equality detector. For example, if the two input signals applied to the gate differ, there is an output. In this case the gate, in a sense, compares the two signals and detects the difference. Conversely, if the two input signals are identical, the exclusive feature means that there is no output. This absence of output indicates an equality of inputs.

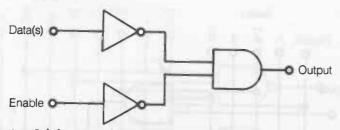

#### Enable

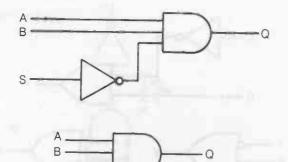

Enable is an inhibit, such as provided by a NOT applied to one input of an AND gate as shown in FIG. 3-8 for a twoinput AND gate with inhibit. The third input is called the strobe (S) or enable input, giving the truth table of TABLE 3-2

Fig. 3-8. ENABLE has an inhibit function on the S input.

|   | Input | Output |   |

|---|-------|--------|---|

| A | В     | S      | Q |

| 0 | 0     | 0      | 0 |

| 0 | 1     | 0      | 0 |

| 1 | 0     | 0      | 0 |

| 1 | 1     | 0      | 1 |

| 0 | 0     | 1      | 0 |

| 0 | 1     | 1      | 0 |

| 1 | 0     | 1      | 0 |

| 1 | 1     | 1      | 0 |

Table 3-2. ENABLE Truth Table

where the output is designated as Q. When a high is placed on the strobe input, a low is applied to the AND gate. This causes the AND gate to produce a low at its output. No matter what the other input sees, the output of the AND gate is always low.

As you can see from TABLE 3-2, there is an output, 1, only when A=1 and B=1, and S=0. The presence of an inhibit

signal (S=1) holds the output at 0 irrespective of any possible combinations of A and B, even when A = 1, B = 1. The corresponding Boolean equation is:

$AB\overline{S} = Q$

## SOLVING PROBLEMS

The basic process of designing logic circuits to meet particular requirements is to break down the problem into elementary yes-or-no or stop-go steps involving formal logic, and co-relating these steps as necessary. This means dealing with original truths (the facts of the question) called propositions and putting these together to arrive at an answer, or syllogism, based on the presence of these truths. Specifically, for example, if a single truth can be dealt with by NOT logic, the output responding to an input is either NOT (not true) or NOT NOT (true). Normally, however, more than one input is involved and there is some interrelationship between inputs, calling for the use of connections expressing the relationships. The most important of these are the AND and OR functions.

The following is a problem involving several propositions and connections, representing the prerequisites necessary to qualify for an executive position:

#### A. College Degree

OR B. Technical college with relevant certificates

C. At least 5 years of experience in a certain profession

D. Over twenty-five years of age

E. Not married

In plain language the basic relationship is:

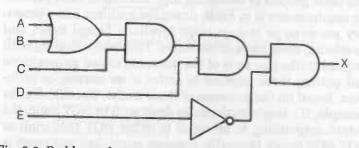

A OR B AND C AND D AND NOT E

The corresponding Boolean equation is:

$(A+B)CD\overline{E} = X$

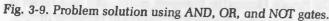

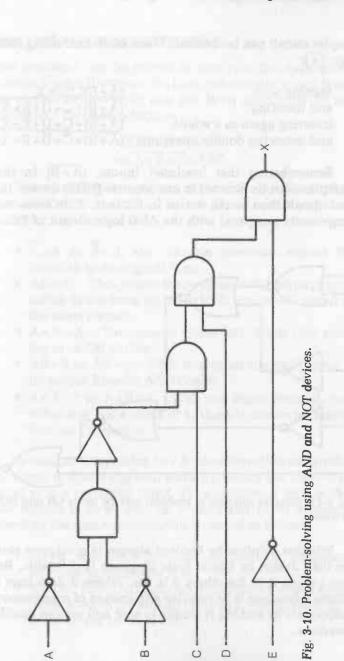

An immediate solution employing AND, OR, and NOT logic gates is shown in FIG. 3-9. This also follows directly from the Boolean equation. Suppose, however, that only AND and NOT devices are available. This means that the problem must be solved in AND logic only. This can be started by inverting the original equation thus:

# $(\overline{A}\overline{B}) + \overline{C} + \overline{D} + \overline{\overline{E}} = \overline{X}$

Now invert again:

# $(\overline{\overline{A}}\overline{\overline{B}})\overline{\overline{C}}\overline{\overline{D}}\overline{E}=\overline{\overline{X}}$

Note here that by containing (AB) as one term in a bracket it does not change its state on inversion. Now remove double inversions as they merely mean using pairs of NOT devices to get back to the original output:

# $(\overline{\overline{A}}\overline{\overline{B}})CD\overline{\overline{E}}=X$

The bracketed term  $(\overline{AB})$  remains something of a problem as it still contains double inversion. However, since we are restricted to NOT and AND devices this is really no problem at all, as it can be accommodated by a NOT device in each input to an AND, and a further NOT in the output. The final circuit in AND logic is shown in FIG. 3-10.

Given no restrictions on availability of components, further solutions can be worked in Boolean algebra to see if any

simpler circuit can be derived. There is, in fact, using NOR logic (+):

| Starting with                  | $(\underline{A + B})\underline{C}\underline{D}\overline{E} = X$                |

|--------------------------------|--------------------------------------------------------------------------------|

| and inverting                  | $(\overline{A+B}) + \overline{C} + \overline{D} + \overline{E} = \overline{X}$ |

| inverting again as a whole     | $(\overline{A+B})+C+D+\overline{E}=\overline{X}$                               |

| and removing double inversions | $(\overline{A+B})+\overline{C}+\overline{D}+E=X$                               |

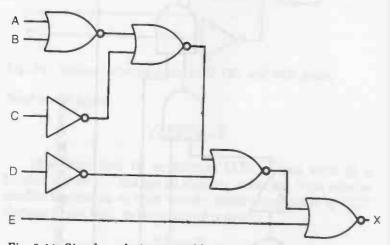

Remembering that bracketed inputs,  $(\overline{A+B})$  in this example, must be directed to one separate (NOR) device, the final circuit then works out as in FIG. 3-11. This saves two components compared with the AND logic circuit of FIG. 3-10.

Fig. 3-11. Simpler solution to problem solving using OR and NOT devices.

Whether solution by Boolean algebra is quicker or simpler than design by digital logic diagrams is debatable. For some people it is, for others it is not. Where it does have a definite advantage is in positive elimination of unnecessary components by making it simple to spot and remove double inversions.

## **BOOLEAN ALGEBRAIC THEOREMS**

Most problems can be solved by applying the appropriate Boolean algebra theorems, the basic rules under which Boolean algebra works. Only one has been mentioned so far, deMorgan's theorem, which is:

# $\overline{ABC} = \overline{A} + \overline{B} + \overline{C}$ or $\overline{A + B + C} = \overline{ABC}$

There are numerous others, some obvious, others rather more difficult to understand at first. Those which may be of particular significance are:

- $\overline{\overline{A}} = A$  or  $\overline{\overline{B}} = B$ , etc. Double inversion returns the function to its original form.

- AA = A. This means that with an AND device, application of the same signal to both inputs will result in the same output.

- A+A=A. The same as above, but in this case relating to an OR device.

- $A\overline{A}=0$  or  $A\overline{B}=0$ . With one input inverted, there is no output from an AND device.

- $A + \overline{A} = 1$  or  $A + \overline{B} = 1$ . With one input inverted, provided one has a value of 1, there is always an output from an OR device.

A number 1 appearing in a Boolean equation means that one signal is always applied, while a 0 means that there is no signal at that particular input. (The numbers 1 or 0 in this case replace A or B, etc., on a particular input diagram.) Therefore the next equations can be stated as follows:

- A0=0 (the AND function can never be completed with one input always at 0).

- A1=A (the AND function is completed with a single input A when the second input is 1; the output is governed by the value of A).

- A+0=0 (the OR function is complete with one input signal if the other input signal is 0).

- A+1=1 (the OR function is complete with a single input when the second input is 1. Compare this with the AND equivalent).

Functions enclosed by a bracket are subject to normal algebraic treatment when expanded, as shown next:

- A(B+C) or A AND (B OR C) becomes AB+AC(A AND B OR A AND C)

- (A+B) (C+D) OR (A OR B) AND (C OR D) becomes AC+AD+BC+BD (A AND C OR A AND D OR B AND C OR B AND D)

Checking by writing out in words and comparing with the original expression verifies if the original expansion is correct or not; i.e., A + (AB) = A. This is self explanatory on spelling it out; A OR A AND B. It is an OR function satisfied if only A is present.

In the example  $A + (\overline{AB}) = A + B$ , this is an OR function, so it is satisfied if A OR B is present. This can be shown with the following equation:

# A OR NOT A AND B = A OR B

1

# **Logic Circuit Devices**

B ASICALLY all the functions of a logic switching system can be provided by NAND/NOR gates, or by either an AND or OR gate(s) and inverters. The former is the preferred method since AND/OR circuitry has a number of practical limitations. If AND/OR elements are cascaded, for example, each produces some attenuation of the signal which may require additional amplification at certain stages, thereby complicating circuit design. With NAND/NOR circuit design, this is not necessary since the main requirement here is in observing the maximum number of inputs (fan-in) and outputs (fan-out) provided by each element.

Initially, all electronic logic circuits were constructed from discrete components such as transistors and diodes for active elements and resistors and capacitors for passive elements. Typically, these yielded printed circuit modules about 1 inch to 2 inch by 1 inch for assembly into complete circuits. These have now been almost entirely replaced by integrated circuits (ICs) offering the performance capabilities of numerous interconnected modules in a single miniaturized package. Besides offering very great reductions in weight and size, as mentioned in chapter 1, integrated logic circuits also have the advantages of greater reliability and greater speed of operation. They are now generally cheaper

#### 48 Logic Circuit Devices

than all the components needed to construct discrete modules covering the same functions.

Some integrated circuits have the disadvantage of lower signal levels in the order of 0.8 to 2 volts as compared with 6 to 12 volts (or even 24 volts) normally employed with discrete modules. This renders the IC more susceptible to noise and can place a premium on component location, lead length, and grounding requirements. However, the widely used CMOS ICs can be used over a wider voltage range and have very high noise immunity.

As with discrete component modules, IC logic circuits are based on the same components of transistors, diodes, etc., although in very much miniaturized form. Schematically, therefore, the two forms of circuits are identical, although for the purpose of use only the external connection points of the IC normally need to be identified.

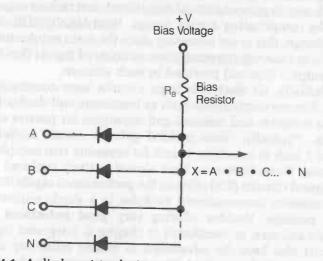

The diode-resistor network shown in FIG. 4-1 provides positive AND logic. With all inputs A, B, C...N positive (logic 1), all the diodes are reverse biased and do not conduct, giving an output of + V (logic 1). In the absence of any

Fig. 4-1. A diode-resistor logic network using positive AND logic and negative OR logic.

one input, that diode conducts, causing the output to fall to 0.

The same circuit with negative logic (-V corresponding to logic 1) works as an OR gate giving a 1 output in the presence of any input. Equally, if the bias voltage is made more positive than logic 1, all diodes conduct when all the inputs are present together, clamping the output to logic level 1.

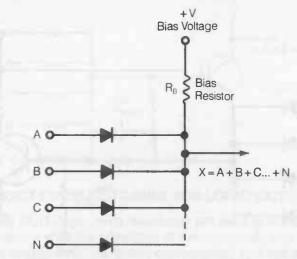

The network shown in FIG. 4-2 has the diodes connected in the opposite manner to those of FIG. 4-1. This time, with positive logic (+V as input) it works as an OR gate and with negative logic (-V as input) it works as an AND gate. Again there is the possibility of clamping the output if required.

Fig. 4-2. A diode-resistor logic network using positive OR logic and negative AND logic.

The disadvantage of these networks is that if the circuits are cascaded, the input current to any one circuit must be provided by the circuit preceding it. This means that relatively low values of bias resistors must be used in order to maintain the required drive currents. In practice this may not be possible and buffer amplifiers have to be inserted between stages.

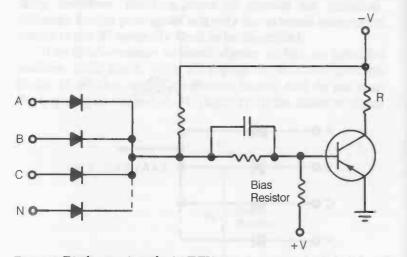

## **DIODE-TRANSISTOR LOGIC (DTL)**

Diode-transistor logic overcomes the limitation of cascading by incorporating a transistor amplifier in the output circuit. A typical positive logic NOR gate of this type is shown in FIG. 4-3. Here any input going positive (logic 1) causes the base of the transistor to go positive with respect to the emitter and cut off. The output is then logic 0 (no current flow through the collector circuit). When all of the inputs are logic 0, the base of the transistor is negative, yielding a collector output approaching the emitter value or logic 1. Worked with negative logic (-V = logic 1), this circuit provides a NAND function.

Fig. 4-3. Diode-transistor logic (DTL).

DTL logic was originally widely produced in IC form operating at speeds of 2-20 MHz with logic levels between 0.5 and 5 volts and for power supplies between 3 and 6 volts. It has now been replaced by simpler and more efficient networks such as transistor-transistor logic (TTL) and more exotic devices.

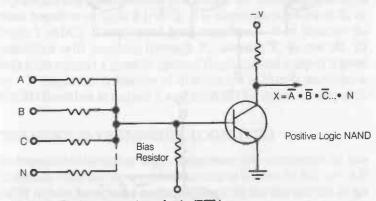

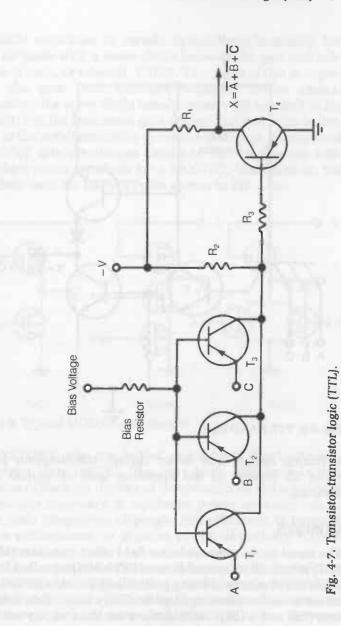

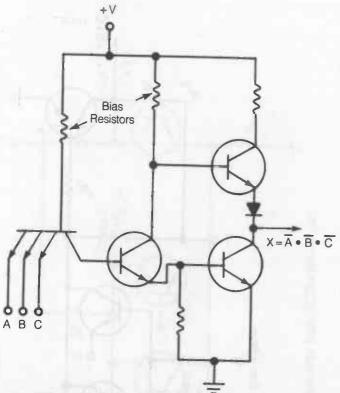

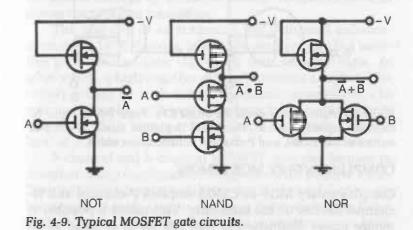

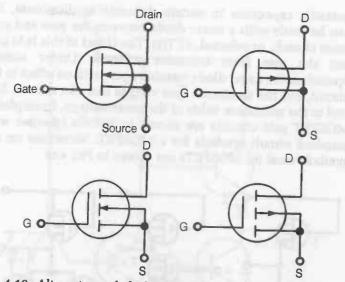

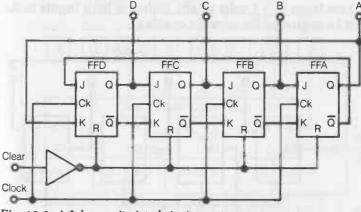

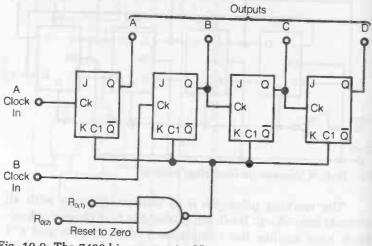

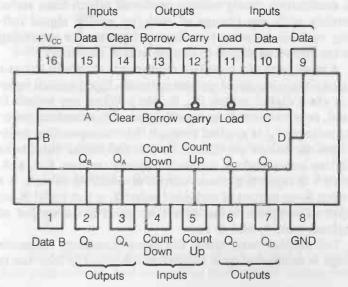

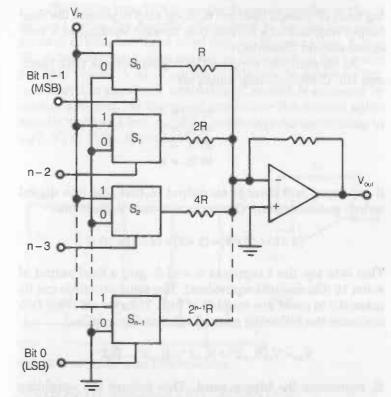

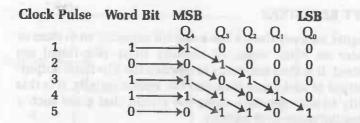

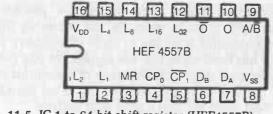

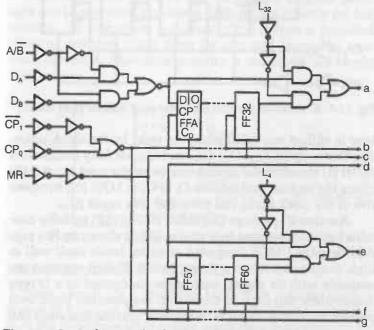

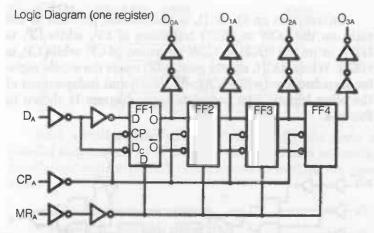

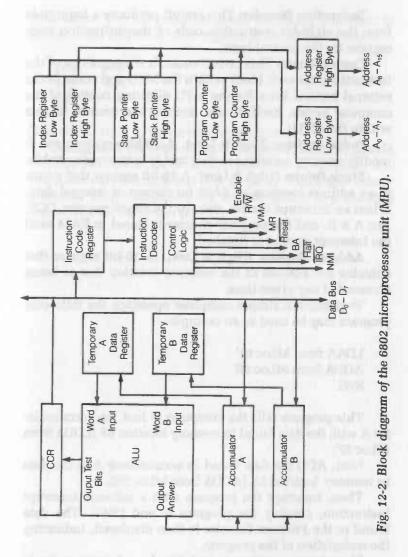

# **RESISTOR-TRANSISTOR LOGIC (RTL)**