# THE BELL SYSTEM

# TECHNICAL JOURNAL

DEVOTED TO THE SCIENTIFIC AND ENGINEERING ASPECTS OF ELECTRICAL COMMUNICATION

| Volume 49 | December 1970 | Number 10 |

|-----------|---------------|-----------|

|           | Section 1997  |           |

Copyright © 1970, American Telephone and Telegraph Company

# TSPS No. 1:

# System Organization and Objectives

By R. J. JAEGER, JR., and A. E. JOEL, JR.

(Manuscript received September 14, 1970)

This article is an introduction to a series of detailed technical articles that describe the Traffic Service Position System No. 1. The organization and objectives of the system are given and the overall operation of the system is explained.

#### I. INTRODUCTION

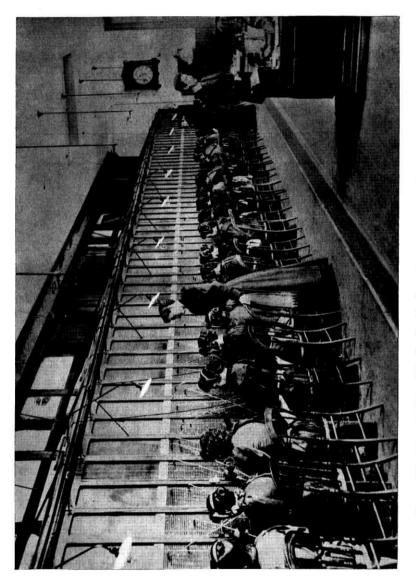

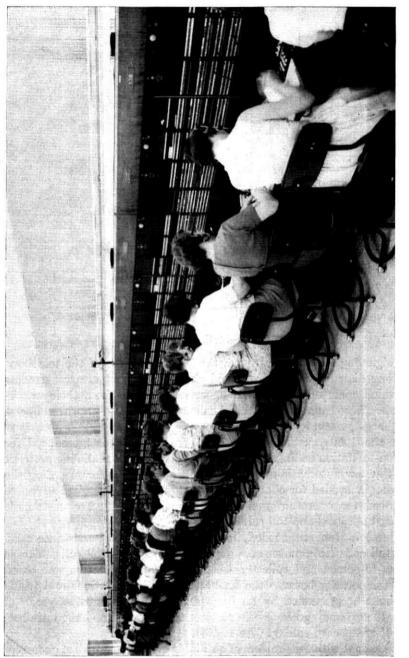

At the outset of telephony, connections between telephones were established by operators through cords, plugs, and jacks at switchboards. Within the first decade, switchboard design and operating techniques soon settled into a pattern that is still followed today. The switchboards of 80 years ago are remarkably similar to those commonly used today. (See Figs. 1 and 2.) With rapidly increasing traffic, it became apparent that to use operators to establish local calls was not the best way to continue. Dial switching was invented.

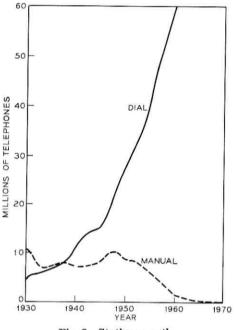

Although the shift to local dial office operation started early in this century, it was in the years following World War II that the transition was rapidly completed. (See Fig. 3.) As the efficiency of transmission

Fig. 1-Multiple switchboard in the Cortlandt exchange, New York City, installed in 1888.

ORGANIZATION AND OBJECTIVES

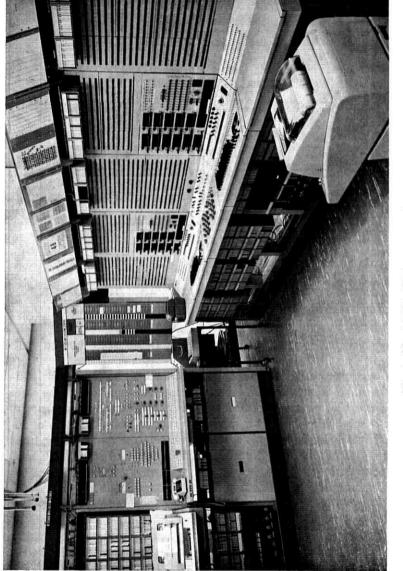

Fig. 2-Switchboards today in New Jersey.

Fig. 3-Station growth.

and signaling facilities improved, the burgeoning use of the telephone for long distance calling permitted the development of arrangements by which operators dialed and supervised toll calls from their switchboards. These capabilities speeded call completion and improved operator charging accuracy.

In the 1950s customer direct distance dialing was introduced for station-to-station calling. This used the established toll dialing network and the new automatic message accounting facilities for recording the call details needed for charging. Thus, through technological advances the need for operators was greatly ameliorated by the customer's dialing both local and toll calls.

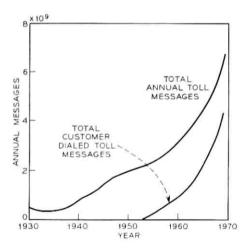

Operators were still needed, however, to handle local assistance calls, coin toll calls (to monitor coin deposits) and special toll calls, such as person-to-person and collect calls. The need for operators was eased only temporarily because the unabated growth of stations and traffic has been accompanied by an increase in the number of special toll calls, the expanding use of coin stations for toll calls, and the introduction of credit card calling. (See Fig. 4).

Coincident with the problem of obtaining greater numbers of operators was a changing labor market. It was becoming more difficult to hire

2420

women to work in the urban switchboard locations, particularly for weekend and night duty. Competition from broadening job opportunities in business offices, sales work, and suburban factories was being felt. These factors combined to start a search to do the operator's job more efficiently and to make it more attractive.

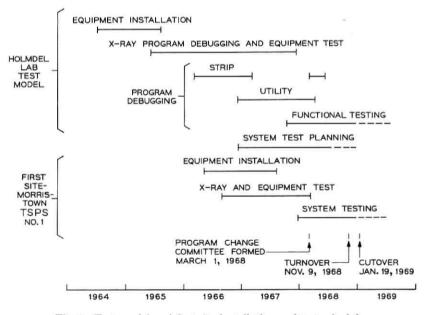

Toward this end, the New York Telephone Company developed an operator assistance switchboard for customer dialed special toll calls to work with No. 5 crossbar system called PPCS (person-to-person, collect, and special) in 1958.<sup>1</sup> Based on this start, Bell Telephone Laboratories undertook the development of a standard cordless console with semiautomated call handling of customer dialed special toll calls through the crossbar tandem system in the early 1960's to provide a more comprehensive design to meet the broader needs of the Bell System. The new console was named the traffic service position (TSP) and the first standard installation went into service in 1964 in Cleveland, Ohio.<sup>2</sup> There are now some 21 installations in major cities. To provide TSP features with the other toll switching systems in the same manner would have required similar development for the No. 4 toll crossbar and No. 5 crossbar systems.

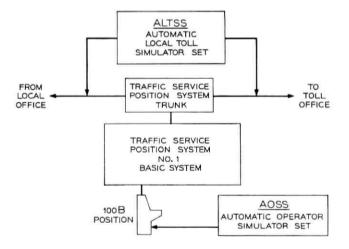

In order to provide a single system that could work with any toll switching system, present or future, the idea of an autonomous system to provide the automatic operator functions was conceived. That system, named the traffic service position system No. 1 (TSPS No. 1), has been developed. It is the purpose of this article and the six that follow to describe the new system.

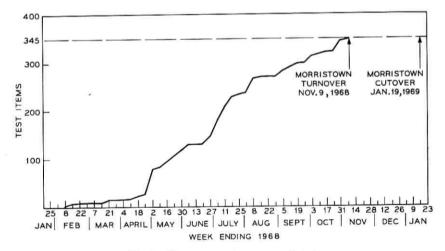

Fig. 4-How toll calls have increased.

#### II. OBJECTIVES

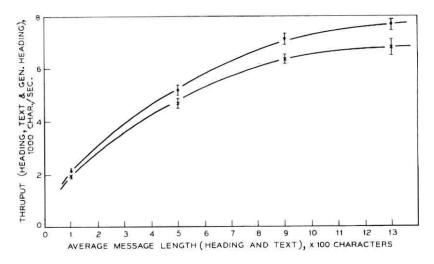

The basic objective of the system design is to relieve the operator of handling the routine switchboard operating functions so that she can concentrate on providing those functions which require judgment to be exercised and data to be put into the system. The initial design of the system provides for the types of calls and the operator functions described in Table I.

There are a significant number of call types now handled on toll switchboards that were not included in the initial design of TSPS in order to limit the size of the development and to meet the most urgent needs of the field. Typical call types not included in the initial design are conference calls, mobile and marine calls, inward to operator calls, and special handling of hotel and motel calls.

In order to handle the calls outlined in Table I and to obtain the desired service, administrative and operational improvements discussed in the introduction, these general design objectives were established:

(i) Autonomous system with standard trunk interfaces to other systems.

(ii) Modern attractive consoles.

- (iii) Economical position remoting capability.

- (iv) Stored program system design.

- (v) Economical over a reasonable range of office sizes.

- (vi) Improved administrative features.

- (vii) Improved maintainability.

- (viii) Flexibility in adding new features.

(ix) A generic processor-memory complex useable in other system applications.

(x) Use of "on-the-shelf" hardware.

In order to expedite development and field introduction, it was decided to adapt both the basic hardware components and the system structure of No. 1 ESS.<sup>3</sup> A number of fundamental modifications were made, however, and these are described later in this series of articles.

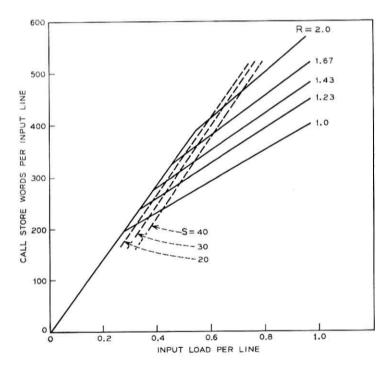

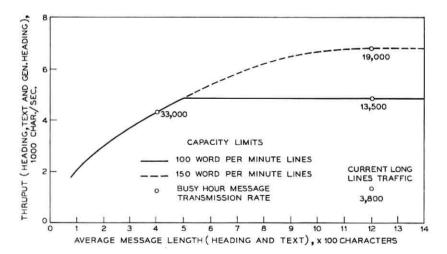

To establish bounds for the size of the design, a review of the potential market was made. Considered were trunking needs and the number and size of chief operator groups.\* With the recognition that the system would receive wide application, equipment quantities were selected so that no one system component would be limiting in obtaining maximum

<sup>\*</sup> A chief operator group is the location of a group of positions under a single administrator or chief operator.

| Noncoin $0+$ $0+$ $0+$ $0+$ $1+, 0+$ $1+, 0+$ Coin $1+, 0+$ $0+$ $0+$ $1+, 0+$ $1+, 0+$ | From<br>Stations | Input Credit<br>Card or<br>Third Number | Called Customer<br>Identification<br>on Person-to-Person | Obtain Acceptance<br>of Charges<br>on Collect | Operator<br>Identification<br>of Calling Number* | Monitor<br>Coin Deposits | Operator<br>Assistance |

|-----------------------------------------------------------------------------------------|------------------|-----------------------------------------|----------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|--------------------------|------------------------|

|                                                                                         | Noncoin          | $1^{+}, 0^{+}$                          | +0                                                       | $^{+0}_{+0}$                                  | $_{1+, 0+}^{1+, 0+}$                             | $^{-}_{1+, 0+}$          | <br>0                  |

TABLE I-OPERATOR FUNCTIONS

Customer dialed station-to-station calls Customer dialed special calls Operator assistance calls

<u>++</u>!

\* Needed only when calling number is not automatically identified and forwarded from the local office.

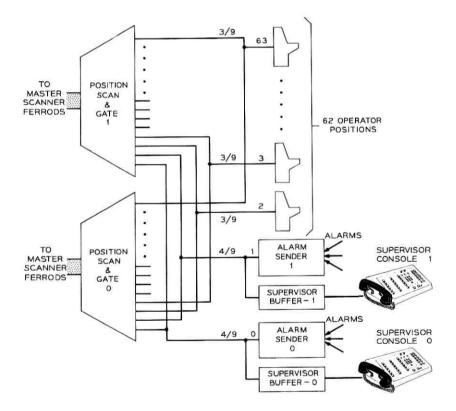

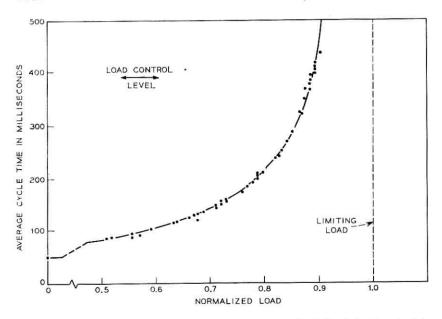

system utilization. As it now stands, the design is limited by data processing capacity. The maximum quantities of the major system elements shown below have covered the needs of all installations to date.

- (i) 3000 trunks,

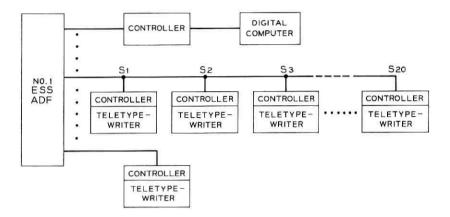

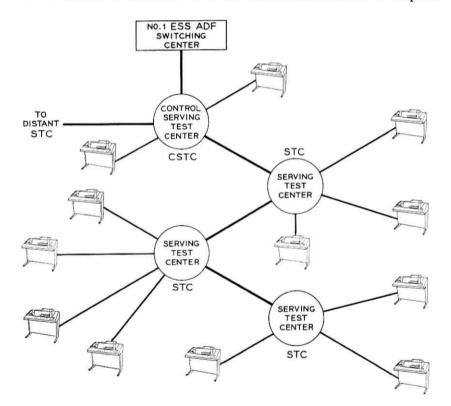

- (ii) 310 positions, accessible as a single team,

- (iii) 62 positions per chief operator group, and

- (iv) 9 chief operator groups, remote, local or both.

The number of cities expected to require multiple installations of the system is small, indicating that a larger system with its higher start-up cost was not justified for the current potential market of several hundred systems.

#### III. SYSTEM DESCRIPTION

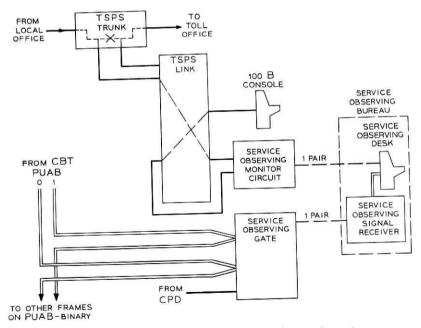

#### 3.1 100B Console

Since the basic function of TSPS is to automate the routine aspects of the operator's work, the system description begins from the operator's viewpoint: the way calls appear on her console, her responses, and the features of the console. Against this background, descriptions of the software and hardware should be more meaningful.

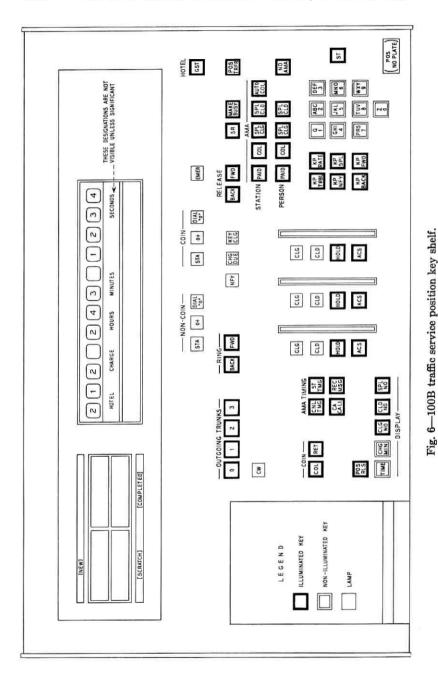

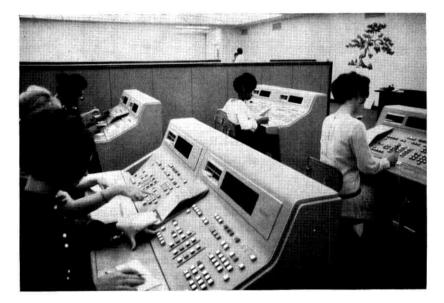

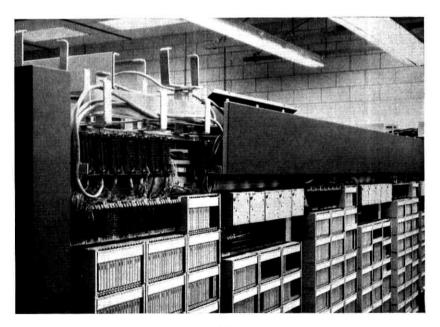

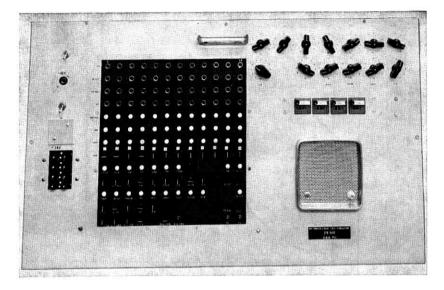

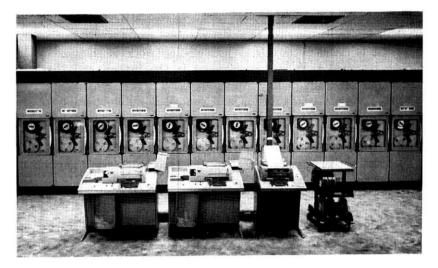

Figure 5 shows a typical operating room. Each console section contains two positions in a desk-like arrangement. Figure 6 is a closer view of the console keyshelf with its lamps and keys. Except for the digital display in the uppermost portion of the section of the console, the remaining lamps are on the main panel. Some keys are equipped with lamps and are indicated in the legend.

A position becomes available to the system for service when an operator inserts her headset plug into its jack. Calls are automatically distributed to all attended positions in such a way that all operators receive an equal share of the traffic load. When a position is given a call, the operator hears a zip tone and is given a lamp display. A lamp indicates the type of the originating station, coin or noncoin, and whether the customer dialed 0 followed by 7 or 10 digits (0+), dialed 0 only (0-)or dialed a station-to-station call (1+). The use of a "1" prefix for station calls is not universal, but for purposes of description, stationto-station calls are often referred to as 1+.

With these indications the operator is able to respond appropriately. On calls received from coin stations, the deposit for the initial period and duration for the call dialed by the customer are also indicated in the numerical display when the operator takes the call. On 0+ calls she

# ORGANIZATION AND OBJECTIVES

Fig. 5-A typical operating room.

2425

THE BELL SYSTEM TECHNICAL JOURNAL, DECEMBER 1970

2426

asks what type of operator assistance the caller wants. When she determines the type of call being placed, the operator depresses a class of charge key. If it is necessary for the operator to enter a credit card number, the number of a third station for billing purposes, or to provide the called number or calling number, there is a keyset in the lower right corner which is conditioned by the operation of an appropriate key pulse key to indicate the type of number being entered into the system by the operator.

In the lower center part of the key shelf are three columns of keys which are referred to as "loops". When a call is connected to the position, it is associated with one of these loops. When the operator is in voice contact with the customer, the bottom key lamp designated acs (access) is lighted. If the operator desires to keep this call associated with her position while handling other calls, she can push the HOLD key lamp. The upper two lamps of each loop indicate the switchook condition of the originating and terminating stations when a call is in either ACCESS OF HOLD. The call is released from the position when both the ST TMG (start timing) key to the immediate left of the three loops and the POS RLS (position release) key in the lower left corner are operated.

Whenever a call is connected to a TSPS position, all call details are available from the system memory. These call details are directly equivalent to those that she would have written on a ticket if the call had been processed at a cord switchboard. She can display, under key control, the calling number, the number that is being called, a credit card number if keyed into the system, the number of a third telephone if one is being billed, and the charging rate on coin calls. Also, the operator can get the exact time of day being used by the system by depressing the TIME key. The displays associated with the two leftmost keys do not lock in and are only displayed as long as the key is operated. The time display is fixed at the instant the key is depressed.

Other operator controls include the ability to release connections forward or backward, ring the stations forward or backward, collect or return coin deposits and connect to special service operators over outgoing trunks.

Although the operator has some freedom in the way she handles calls, many of her key actions are automatically checked and flashing lamps used to indicate detectable errors. If, for instance, the operator depresses the START TIMING key before a class of charge has been recorded, the START TIMING lamp will flash. The operator must then determine what information is missing. Similarly, keying 11 digits on a 0- call will cause the KP FWD (KP forward) lamp to flash.

# 2428 THE BELL SYSTEM TECHNICAL JOURNAL, DECEMBER 1970

For all calls that are to be automatically timed by the system two key operations normally end the initial position seizure. These keys are ST TMG (start timing) and POS REL (position release). The START TIMING key is used to indicate to the system that the operator has all of the billing details on the call, and that when her position is released from the call, and the called station answers, the time of the connection is to be recorded. On 1+ coin calls the START TIMING key may be operated before the called party answers, but on person-to-person calls the START TIMING key is operated after the conversation starts. In either case, the time of connection is established when the operator is disconnected from the call. Timing for charges stops when a call is reconnected to a position for any reason.

# 3.2 General

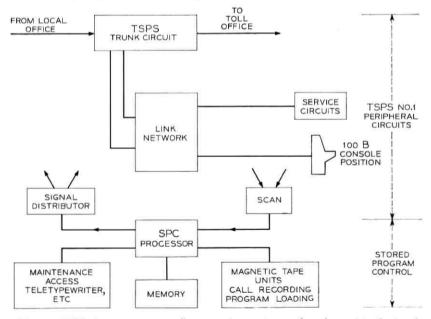

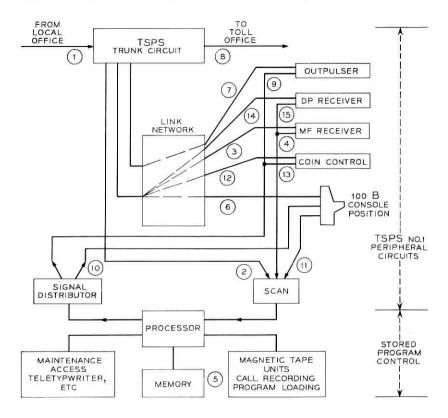

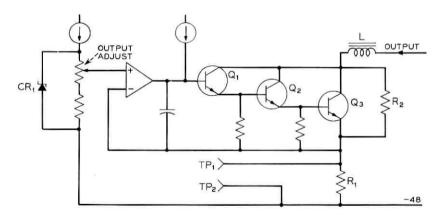

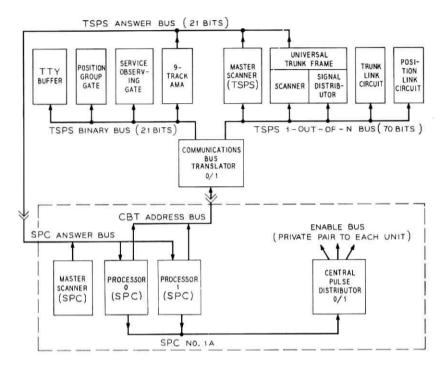

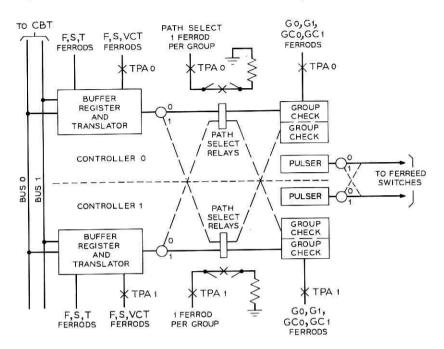

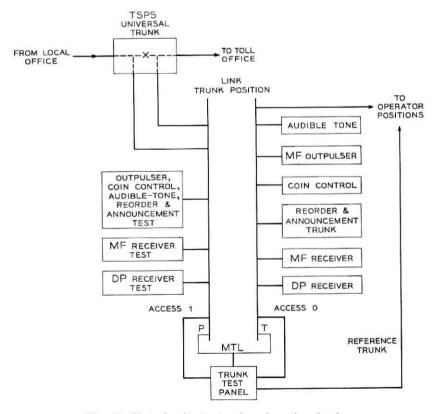

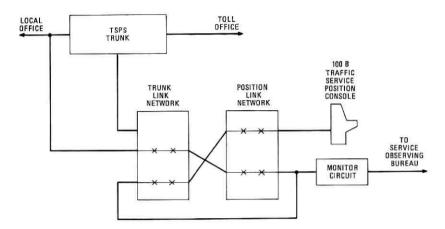

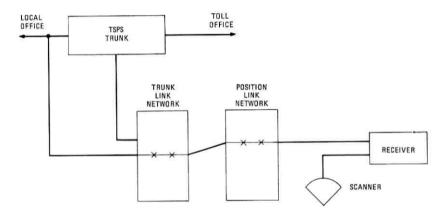

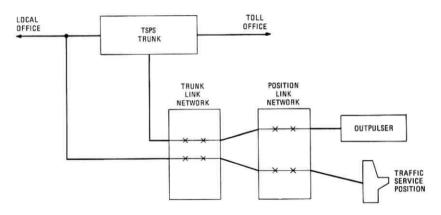

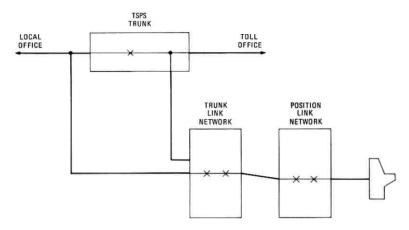

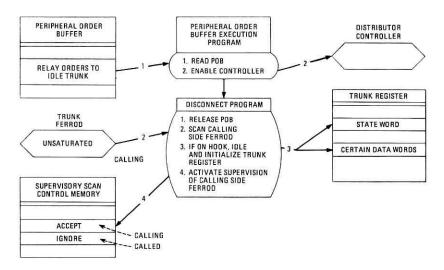

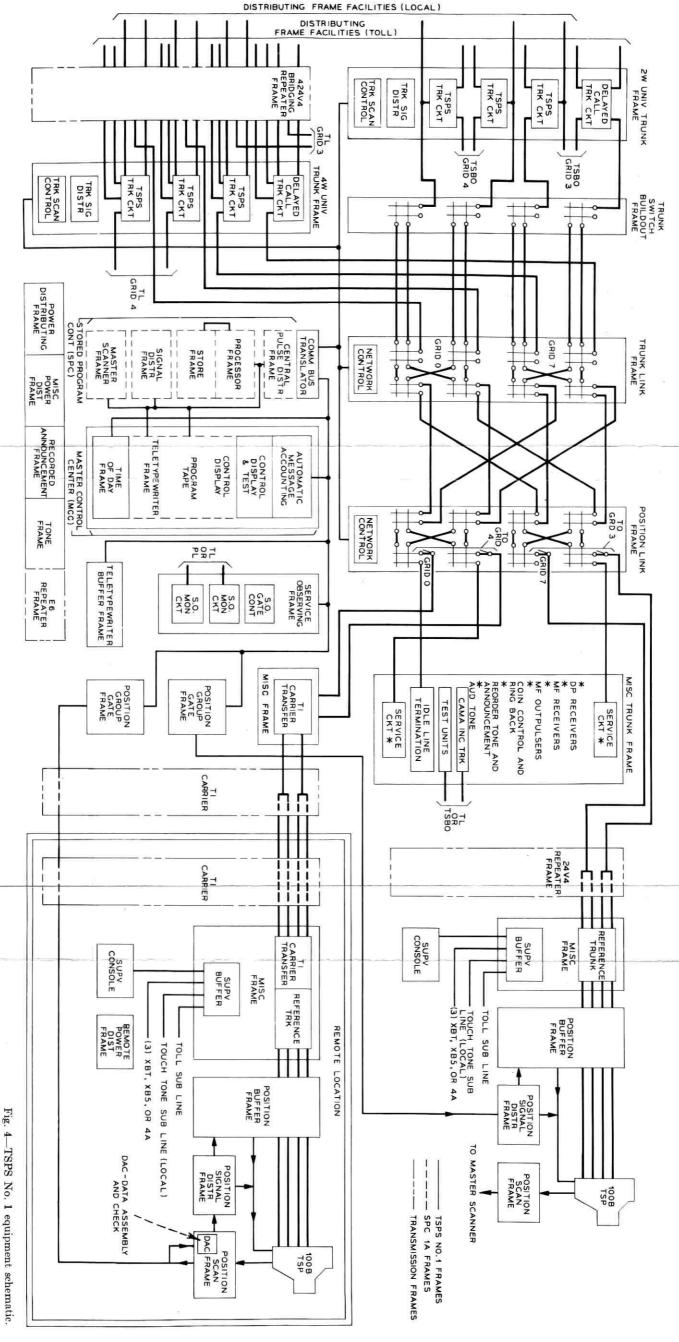

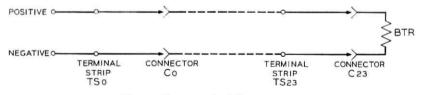

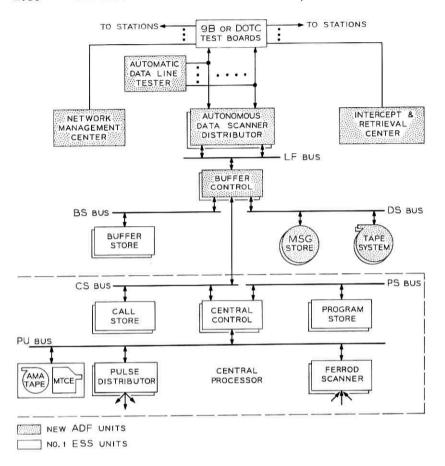

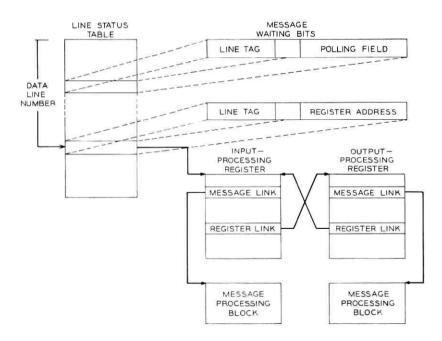

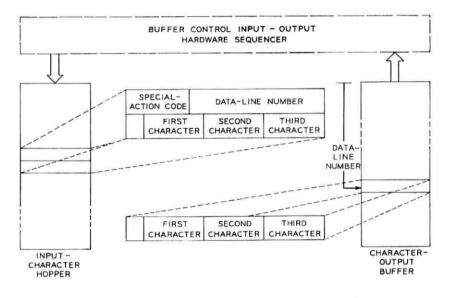

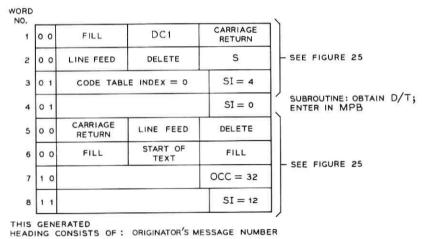

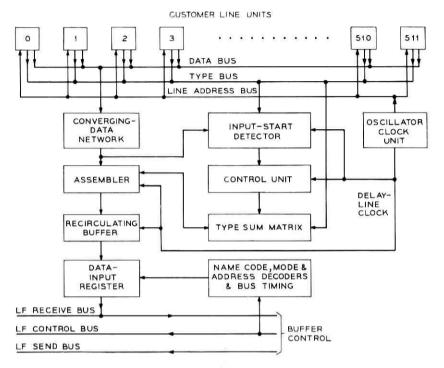

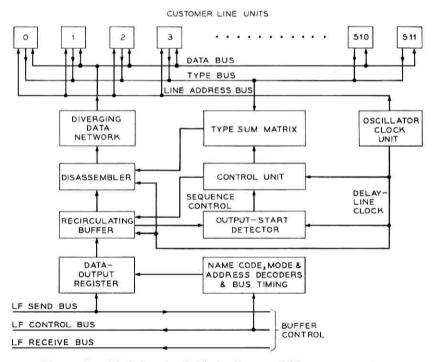

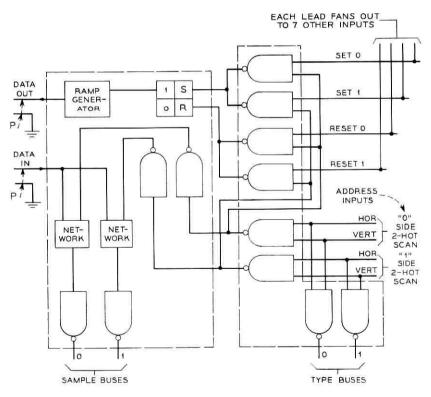

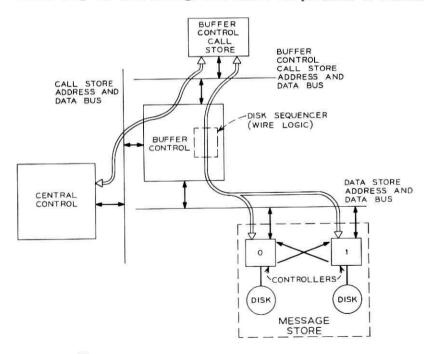

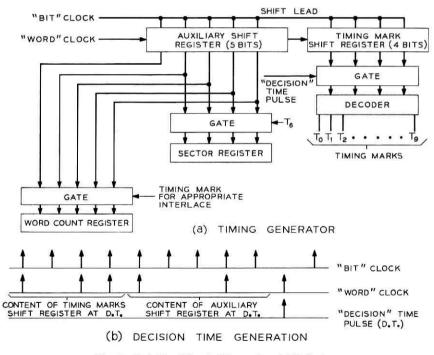

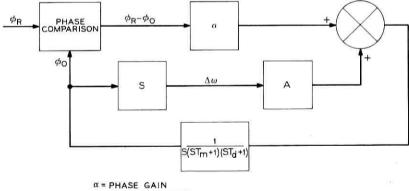

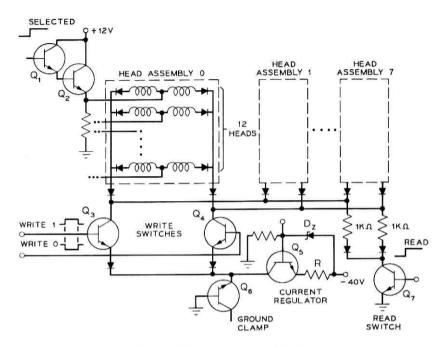

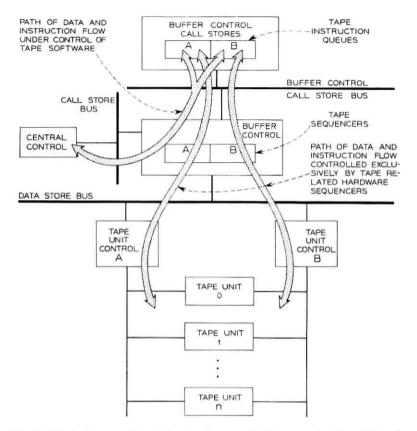

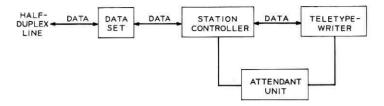

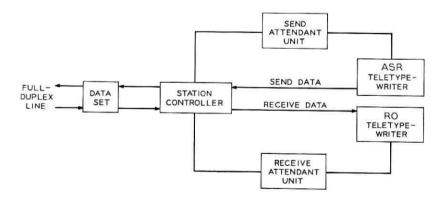

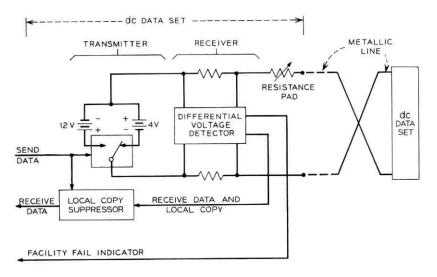

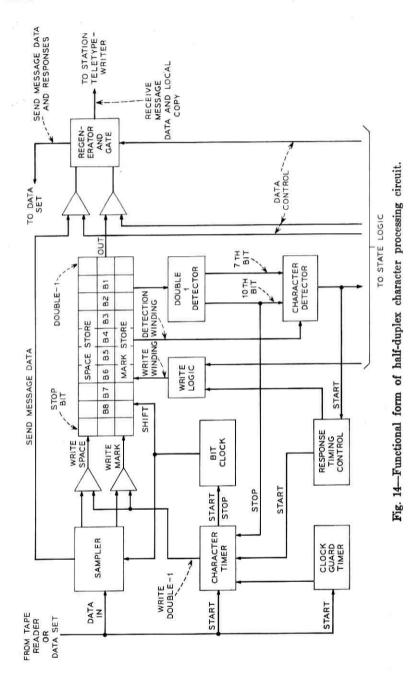

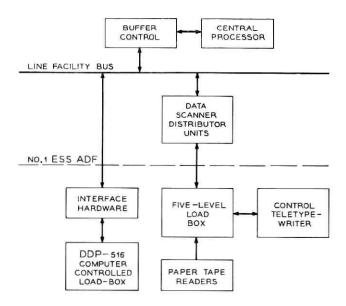

Figure 7 is a basic block diagram for this system. All trunks have two two-wire appearances on the link network. The network connects the trunk to various service circuits—digit receivers, outpulsers, coin control circuits, tone circuits, and operator positions. Being a stored program system, the basic call logic instructions are in the memory and are executed by a processor. Changes of the supervisory state of trunk,

Fig. 7-TSPS elements temporarily connect operators and equipment to the trunk circuit.

service, and other peripheral circuits including the positions themselves, are detected by scanners. Output instructions via signal distributors and central pulse distributors control these circuits and the position lamps.

During the conversation period of a call, the customers are connected only to each other; there are no connections to operators or service circuits. It can be seen in Fig. 7 that the TSPS trunk circuit is a dedicated facility connecting the local office to the toll office. No switching capability nor concentration exists for this trunk circuit at TSPS. Thus, TSPS is a unique type of switching system because all the elements of a switching system are present only for the purpose of temporarily connecting equipment units and operators to the trunk circuit.

#### 3.3 Equipment

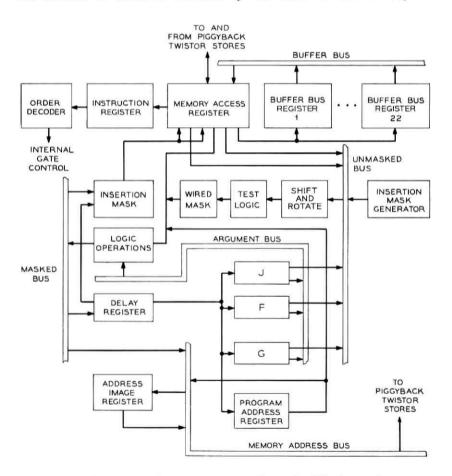

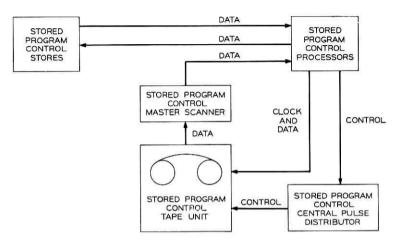

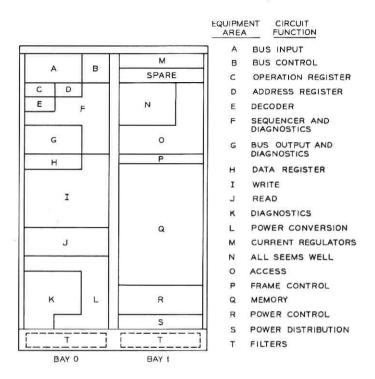

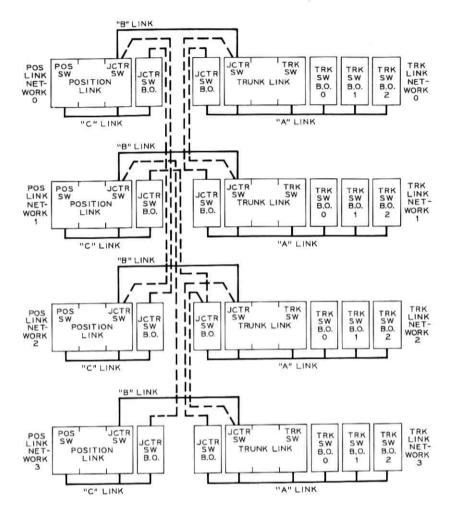

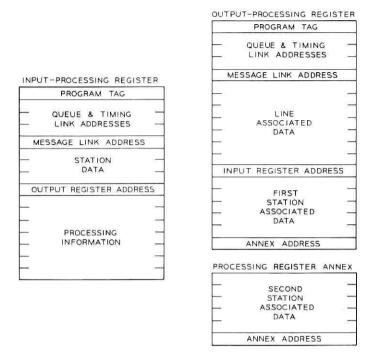

The system equipment is divided into two principal parts, the processor-memory complex, and the TSPS No. 1 periphery which includes the position subsystem.

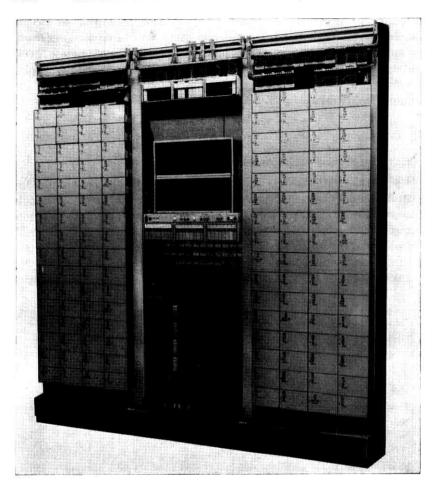

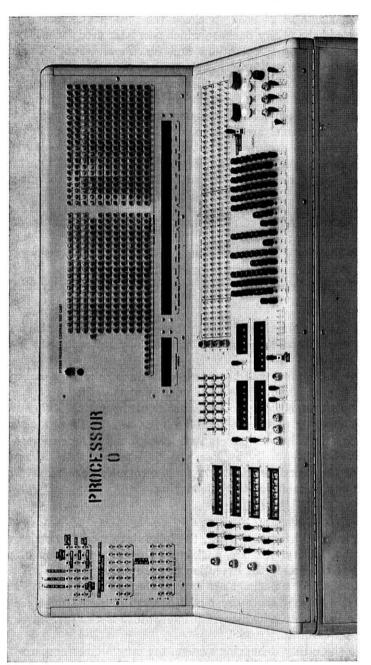

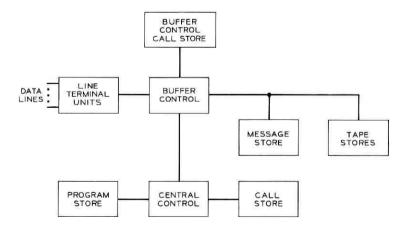

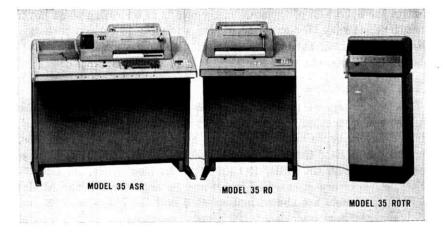

# 3.3.1 Processor-Memory Complex

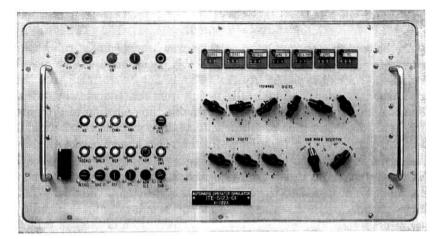

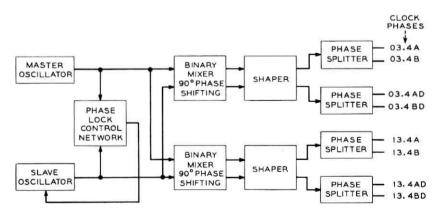

One of the major points of divergence from the No. 1 ESS design is in the processor-memory complex. The processor-memory complex, including such supporting units as the control and display panel, a signal distributor, a central pulse distributor, a master scanner, the maintenance teletypewriter and the program tape unit for loading and unloading memory, constitute a subsystem called the stored program control No. 1A (SPC). The SPC equipment is covered by a separate set of engineering documents and has well defined interfaces so that it can be easily used in other applications. It is used with the electronic translator system for No. 4 toll crossbar as well as for the TSPS No. 1.<sup>5</sup>

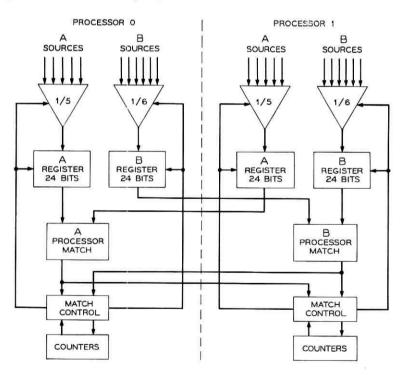

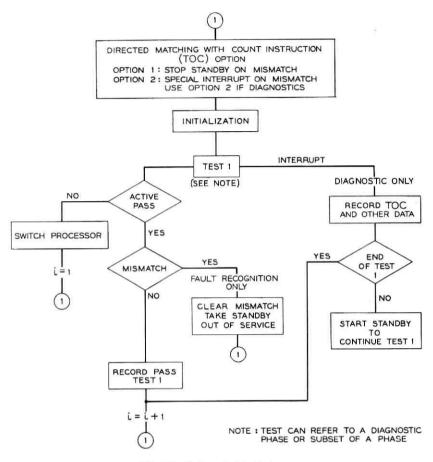

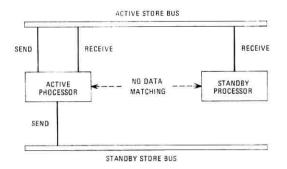

The SPC No. 1A design incorporates several novel improvements. For example, the duplicated processors have fast dc matching circuits that compare the states of certain internal circuits and are able to abort orders within the failing cycle when a mismatch occurs. This provides for improved discrimination of errors and faults as well as better recovery from mismatches. Another difference is in the use of a simplified store bus arrangement to minimize the complexity and inherent hazards of having cross bus switching at every store frame.

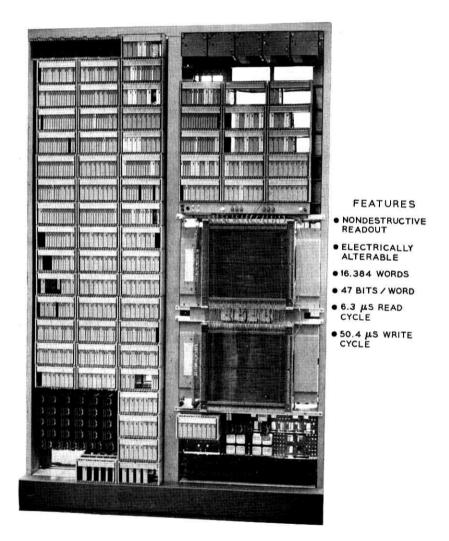

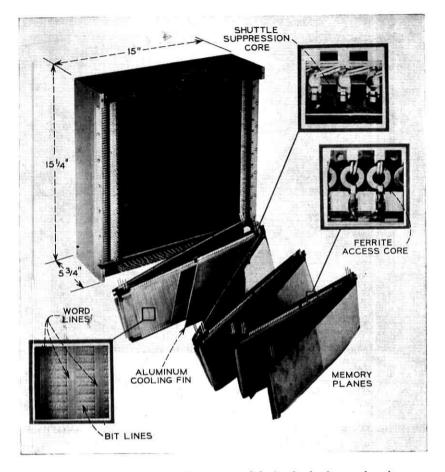

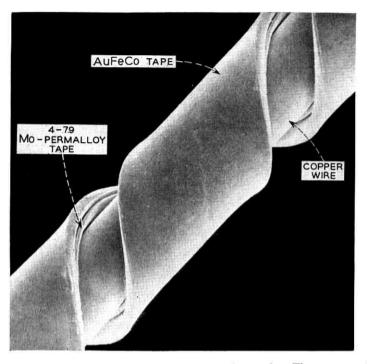

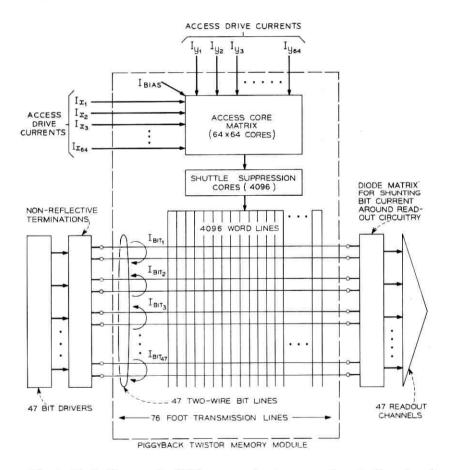

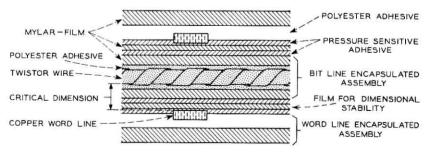

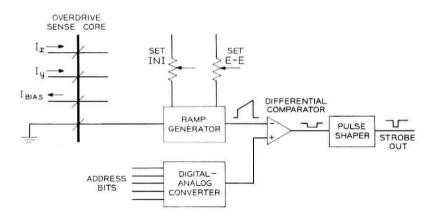

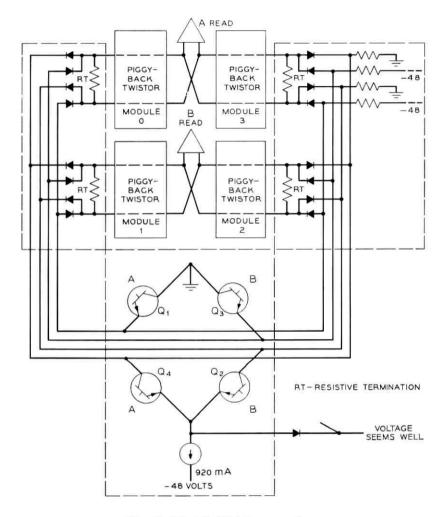

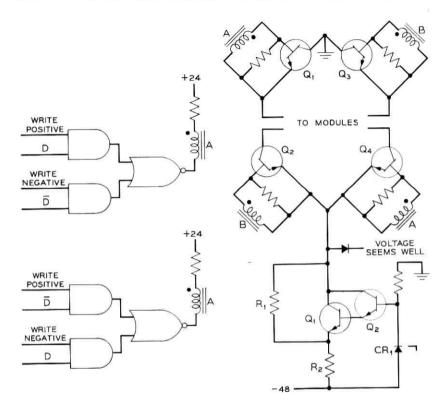

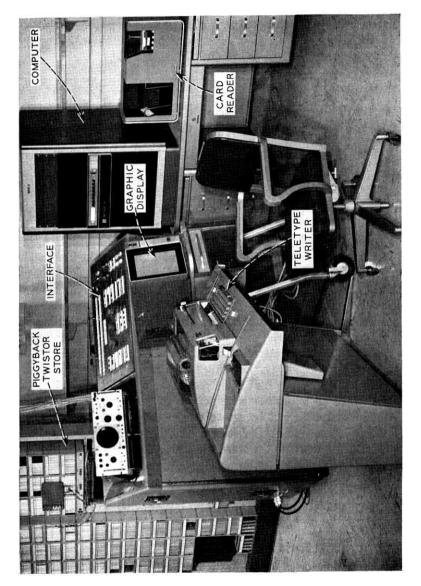

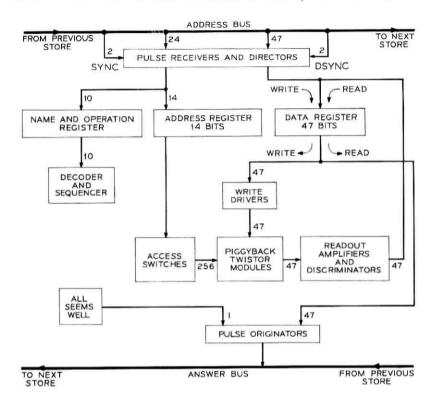

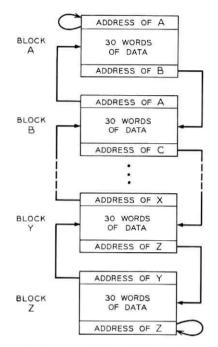

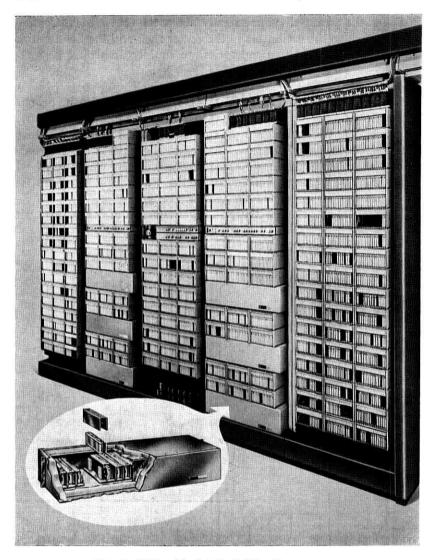

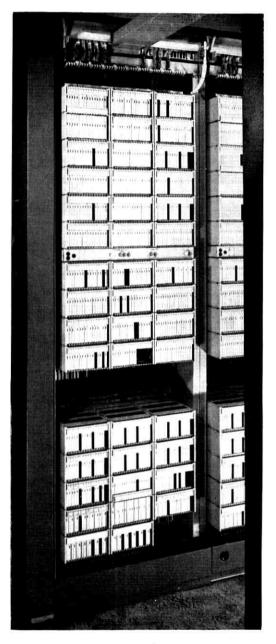

For system simplification, a single type of store using the electrically alterable, nondestructive readout piggyback twistor was chosen to provide all of the memory required by the system applications.<sup>4</sup> The advantage of using this memory is discussed elsewhere in this issue.

# 3.3.2 TSPS Periphery

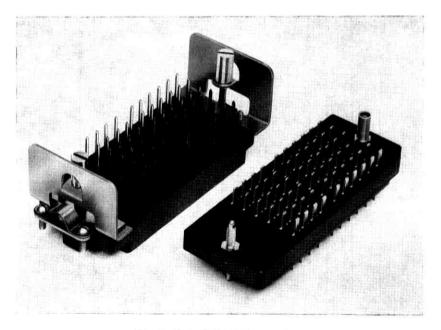

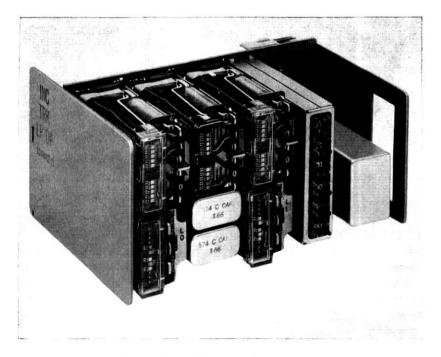

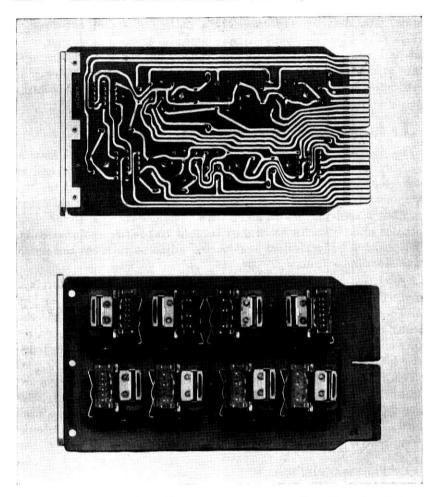

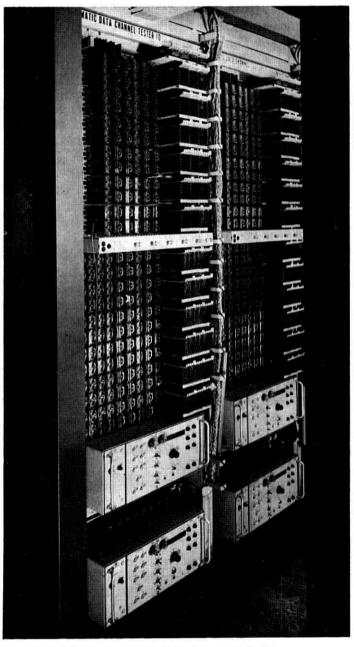

Many of the peripheral units of TSPS No. 1 are similar in function and appearance to those of No. 1 ESS. The plug-in circuit packs, the framework, and terminal strips are virtually identical. Details of the differences are described in Ref. 6.

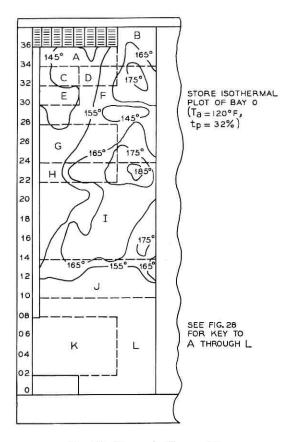

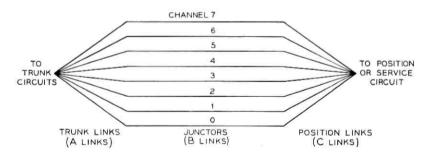

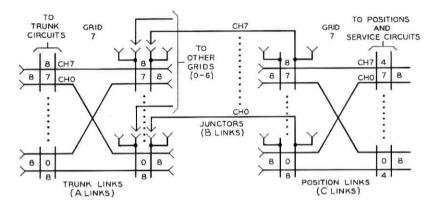

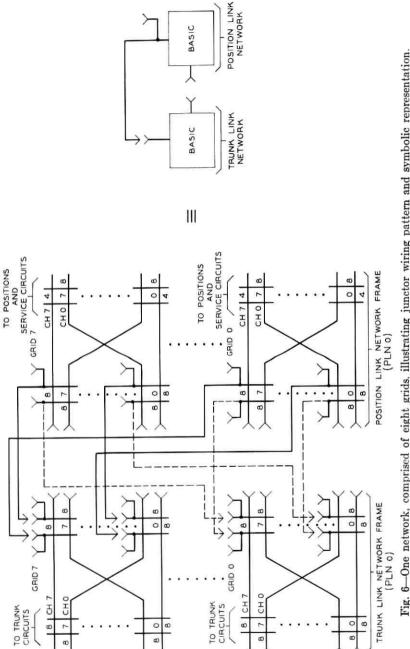

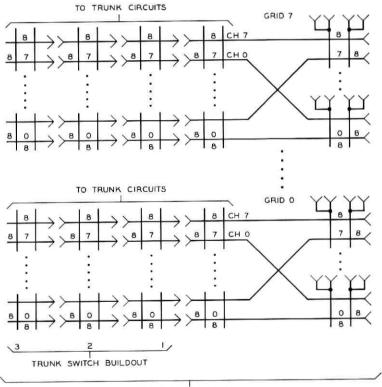

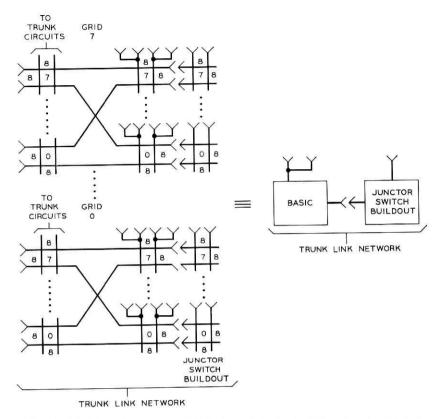

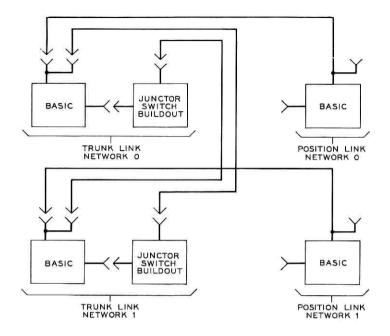

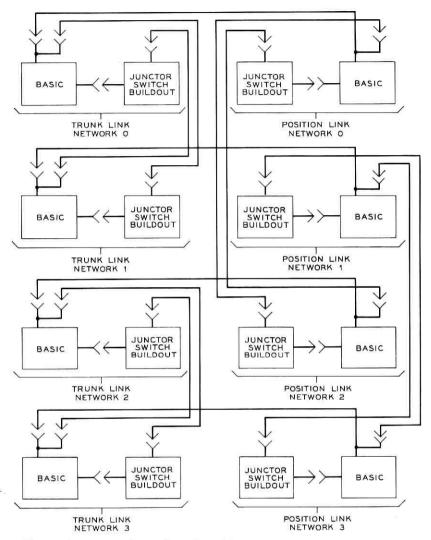

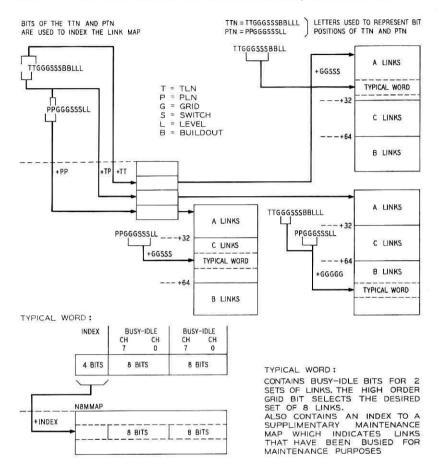

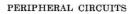

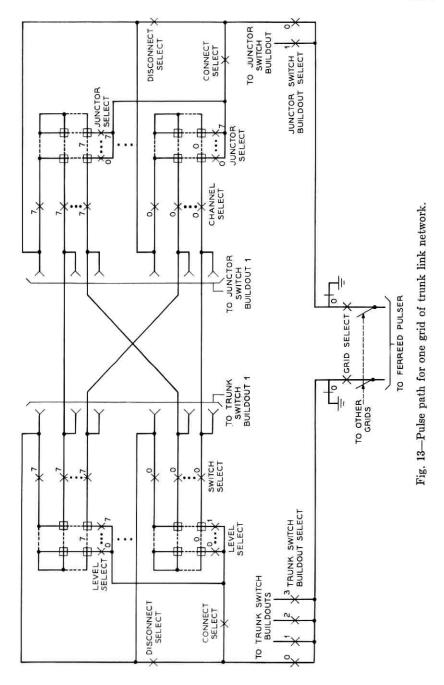

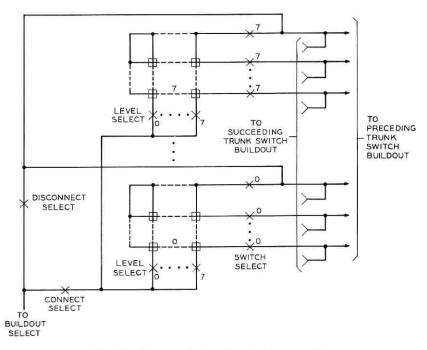

The switching network used to connect the trunks to the service circuits and positions is a four-stage, two-wire space division network using ferreeds. In order to provide uniform traffic loading of the linkages for the widely differing traffic occupancies of TSPS trunks, a unique network configuration that involves build-out frames has been provided. The build-out frames are physically attached to the basic frames by cable connectors to ease the problem of network growth.

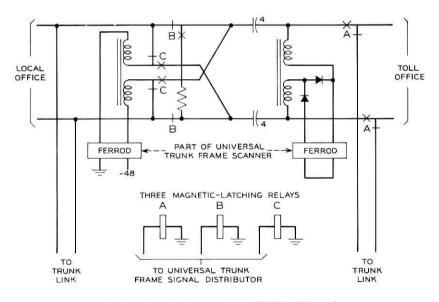

The plug-in trunk units and the universal trunk frames look like No. 1 ESS units. They are quite different in function and this is reflected in the internal design. Because TSPS works with any local office type, it must be able to receive multifrequency pulsing or dial pulsing over both loop and carrier facilities. Since the serving toll office may have a four-wire switching system, both two-wire and four-wire trunk circuits are provided. The four-wire trunk circuits are used when the toll office has four-wire switching and the incoming trunk facilities are four-wire.

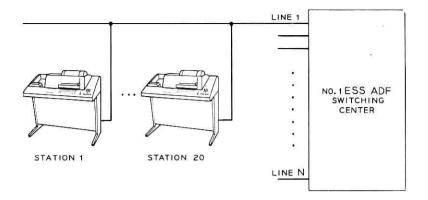

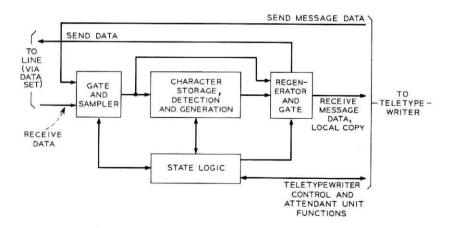

# 3.3.3 Position Subsystem

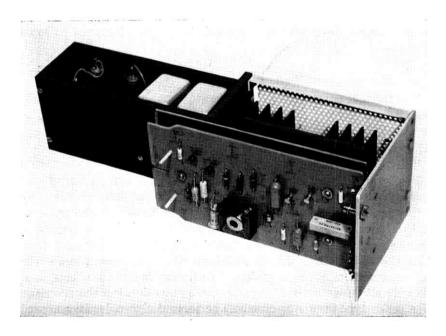

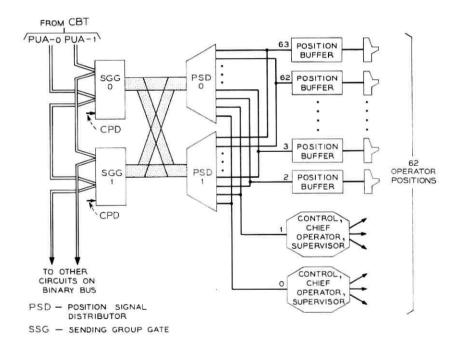

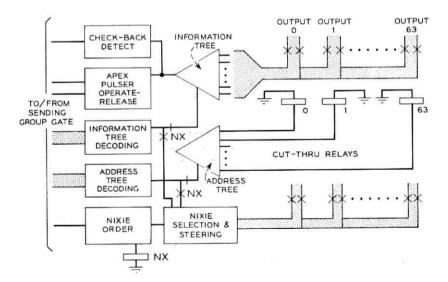

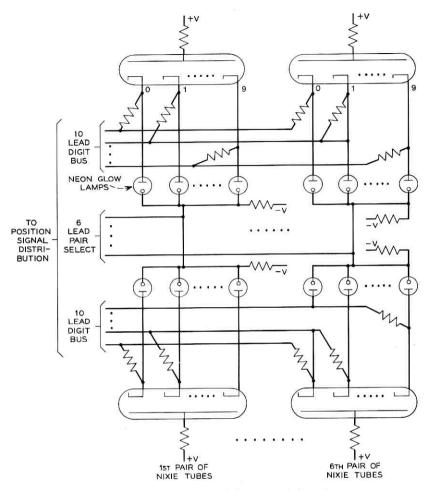

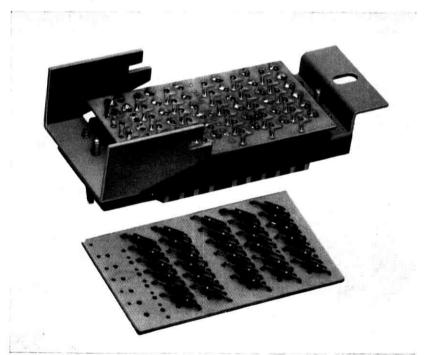

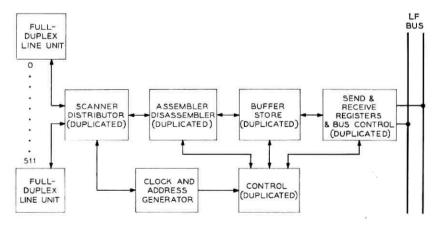

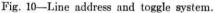

While the position subsystem is really part of the TSPS periphery, it is sufficiently large and novel to warrant separate mention. Orders from the SPC to control the lamps at the consoles are decoded in a position signal distributor which operates or releases magnetically latched miniature wire spring relays. These relays are circuit pack mounted in the position buffer and, with a modest amount of wired logic, control the lamps and key lamps on the console. The console's numerical display is controlled directly from the position signal distributor.

Operators' key actions are detected by an autonomous scanner which codes and gates the keyed information along with the position number back to the peripheral master scanner.

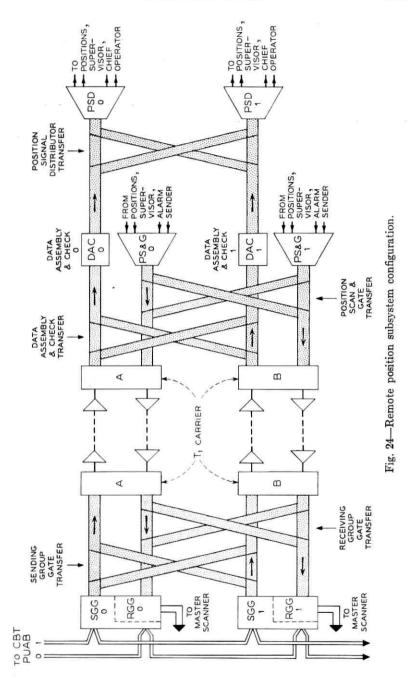

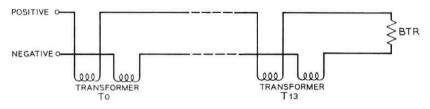

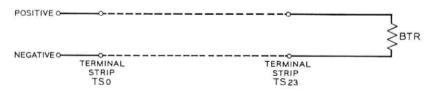

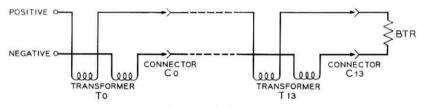

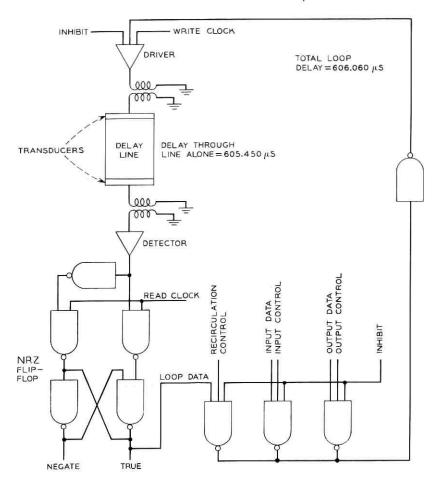

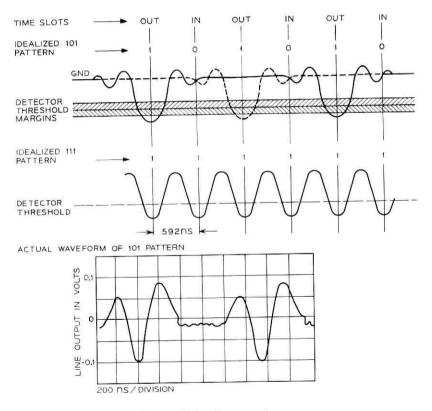

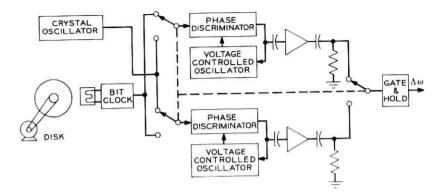

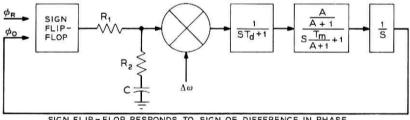

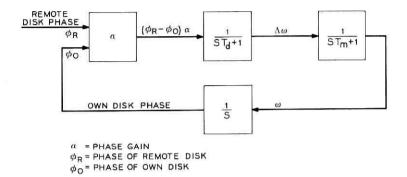

When the positions are remotely located, the orders to control the position lamps and the data words for key operations are sent via the digital T1 carrier system which acts as an extender of the peripheral bus. The T1 carrier also provides the voice circuits for the operators. The manner in which the T1 system provides voice and data capability simultaneously is described in detail in the article on the TSPS periphery.<sup>7</sup>

#### 3.4 Software

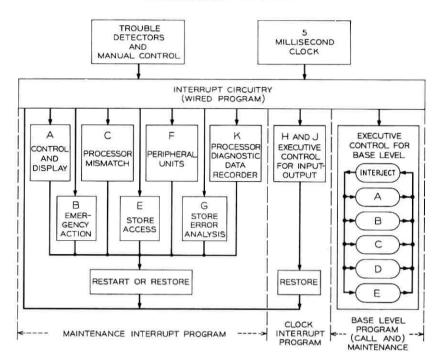

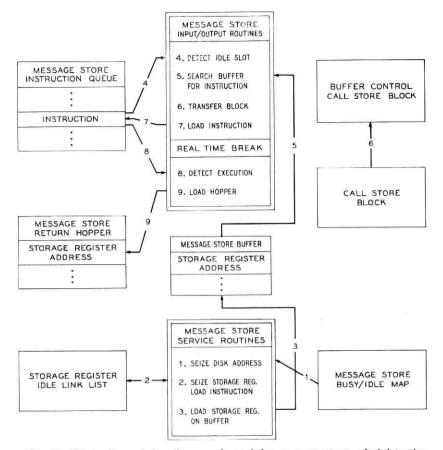

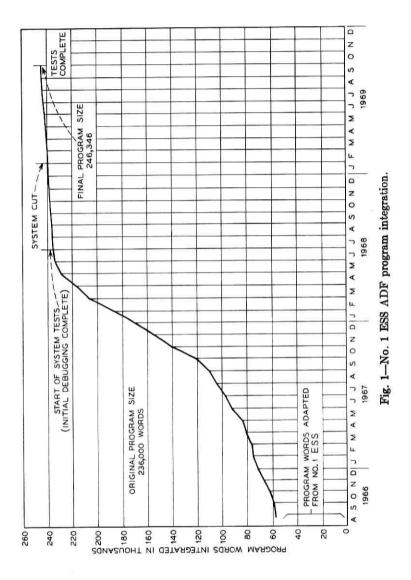

The program structure for TSPS closely follows that for No. 1 ESS.<sup>3</sup> An executive control program, interrupt levels, priority work lists, fault recognition programs and diagnostic programs are employed to provide the real-time, time-shared characteristics of the system. The individual programs are arranged to be part of either the SPC or TSPS similar to the equipment dichotomy described in section 3.3.1.

# 3.4.1 SPC

The SPC program package provides the system framework within which the TSPS programs function. It is composed of the executive control, maintenance control, interrupt and input-output programs. It also has those programs needed to maintain SPC equipment. The interfaces between the SPC and application programs have been carefully arranged to avoid significant penalties in overall program size and system real-time usage.

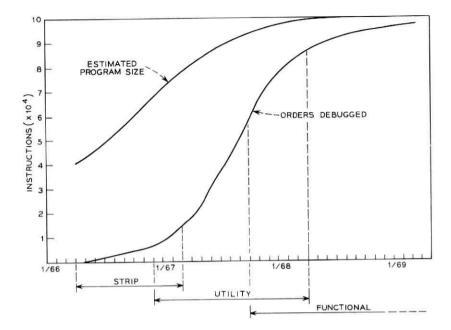

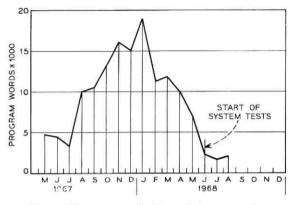

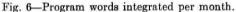

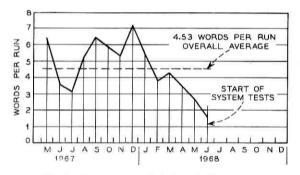

The SPC program package is covered by separate documentation that is coordinated with the SPC equipment. There are 35,000 words of SPC program of which 24,000 are for maintenance functions.

#### 3.4.2 Traffic Service Position System

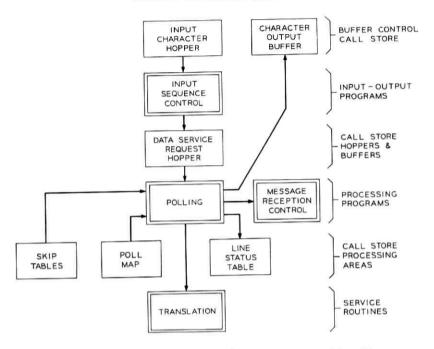

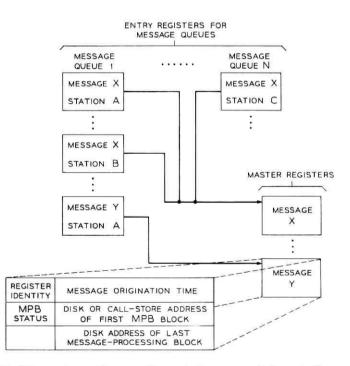

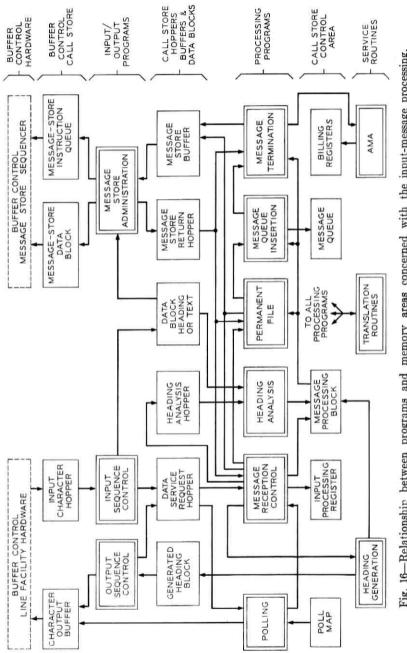

The TSPS programs operate within the SPC framework to achieve the desired total system functions. They are composed of both call processing and maintenance programs.

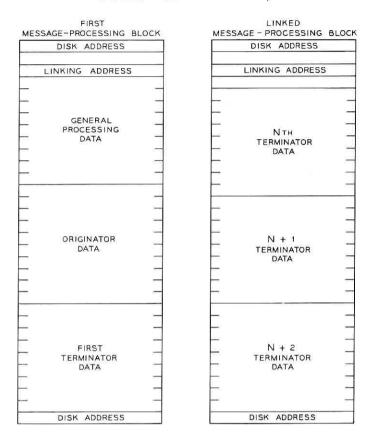

The call processing programs provide call handling logic and are concerned with the input-output functions of scanning and signal distribution, and the control of peripheral hardware to process calls. These programs detect changes of state, provide the data processing to interpret the changes of state, and issue orders to the periphery to change the status of the hardware to further the progress of the call. For example, call processing programs provide for the reception of digital information, establishing connections through the ferreed link network, the sending of information to control the lamp displays at operator positions, the reception of key signals from the operators, the computation of coin charges, and the placing of billing information on the magnetic tape. These programs operate under the stored program control executive control program structure which insures that all necessary work will be given an opportunity for execution within selected time periods.

For the programs that cover the operator functions, care has been

taken to insure that standard operating practices are reflected in the program design. The primary intent here is to give the operator maximum latitude in sequencing her actions while insuring that she properly completes all the necessary functions before releasing the call from her position.

There are 80,000 words of TSPS program of which approximately 37,000 are for maintenance of the peripheral equipment including the local and remote positions.

# 3.5 Maintenance Features

#### 3.5.1 General

In this system as in other Bell System central office electronic switching system designs, the maintenance strategy is based on having vital hardware units in duplicate, using signals to indicate the successful execution of orders and using programs to test, detect faults, and diagnose trouble. The deductive and test strategies designed into the programs are relied on heavily to obtain fast and effective results. The use of teletypewriters and lamp displays to simplify the man-machine interface aids in an overall improvement in maintenance. The intent is to achieve greatest reliability through automation wherever possible.

#### 3.5.2 Equipment

The most fundamental aspect of equipment maintenance is the extensive use of plug-in circuit packs to simplify replacement of defective units and to minimize the need to repair or adjust apparatus in the office. Duplication of important, commonly used equipment assures continuity of service while failing units are being repaired or additions are made. One method of duplication is achieved by having two separate and identical units, one active and the other a working standby operating in parallel. Only the active unit participates in system call processing. The stored program control processor and stores are examples. Another technique is to provide two halves of a unit and divide the work. When one half fails, the other half takes over the total work load; the link frame controllers are an example. There is also duplication in power and bussing of data signals.

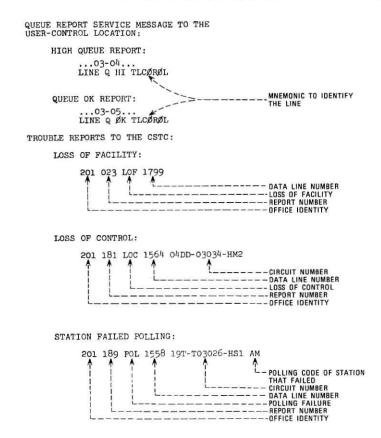

As already mentioned, the teletypewriter is the primary means for a man to communicate with the system. Messages printed on the teletypewriter identify trouble and failing units. The messages provide the needed detailed information for the maintenance craftsmen to take action. There are periodic teletypewriter reports given on system functioning so that a picture of the relative state of the machine can be obtained periodically. It is also possible via the teletypewriter to modify system operations. For example, the maintenance craftsman can request the system to test particular units.

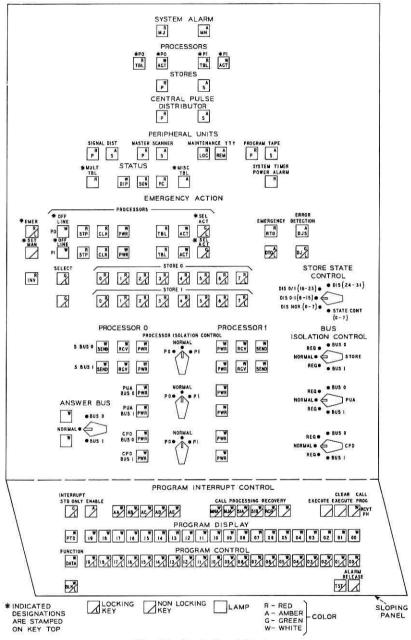

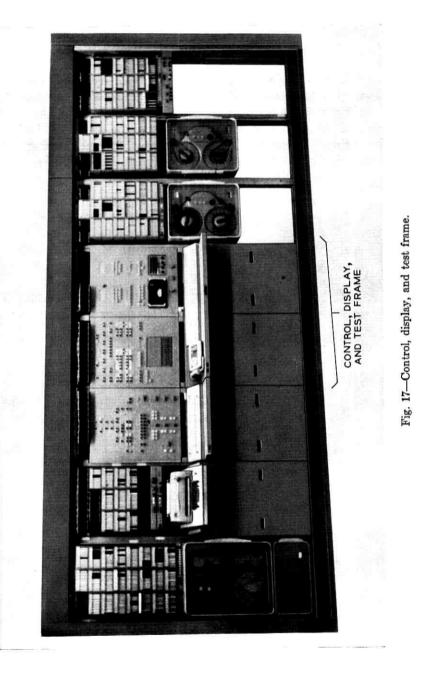

In addition to the teletypewriter, there are adjacent display panels at the master control center for the SPC and TSPS equipment that give the status of the major equipment elements indicating whether they are in trouble or removed from service. These panels also have control keys which permit the maintenance craftsman to directly reconfigure the system. This permits him to manually associate certain equipment units to form a working system when automatic software defenses are inadequate or other troubles warrant.

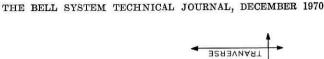

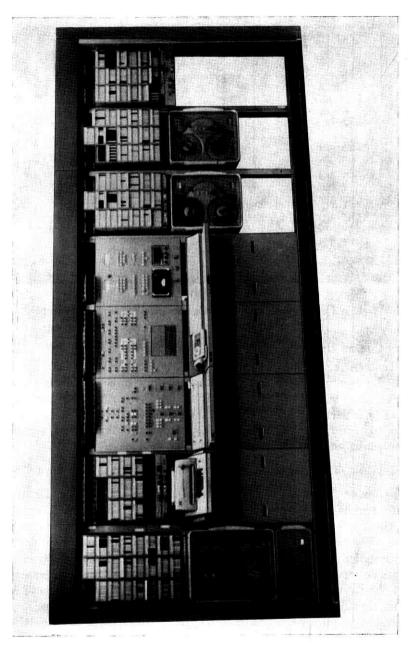

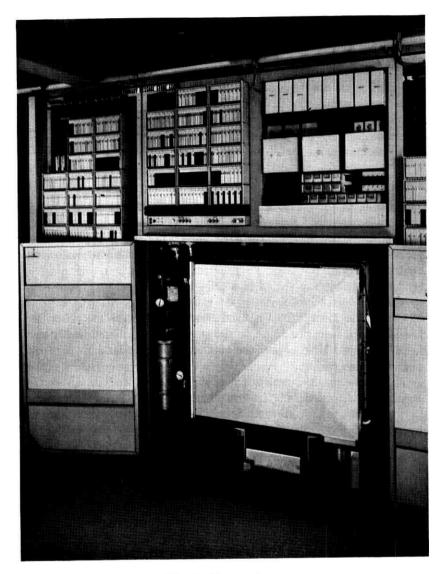

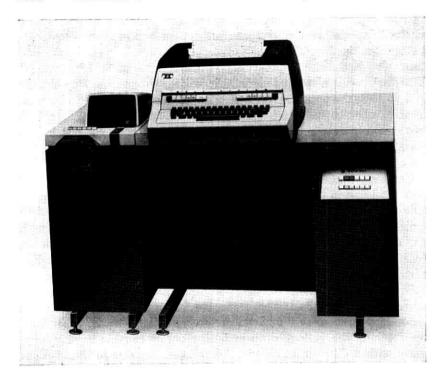

The program tape unit for loading the electrically changeable memory via a magnetic tape is located in the master control center (see Fig. 8). This unit can also be used for recording on magnetic tape the contents of system memory to aid in the analysis of program problems. It is also used by the Western Electric Company to obtain a magnetic tape record of office data when engineering for growth.

Craftsmen gain access for testing service and trunk circuits, and to make transmission measurements over trunks through the control display and test panel. A voltmeter is available for making the normal ground and battery cross-checks on cable pairs that connect to the system.

The duplicated automatic message accounting magnetic tape units are in the master control center so that the maintenance craftsman can remove and replace the magnetic tapes on which call billing data are placed. The time of day circuit has key controls, also located at the master control center, for setting the time if commercial power interruptions cause slight time errors to occur.

Almost all frames in the office have the standard POWER OFF keys which are used to remove power from circuits when replacing faulty circuit packs. Because the position subsystem can sometimes have some of its equipment located at a remote site, special controls are provided at the remote location to aid the maintenance man in clearing troubles. Using these controls to enter requests, the system sends selected test orders to the position subsystem signal distributor and position buffer frames. These and other maintenance features unique to the position subsystem are described in Ref. 7.

Fig. 8-TSPS master control center.

# 3.5.3 Software

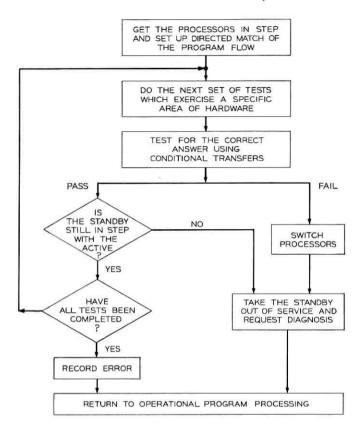

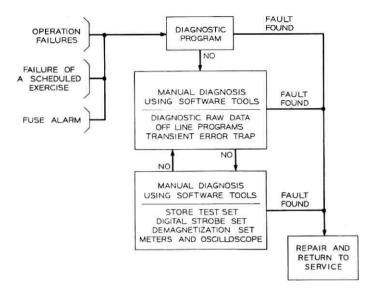

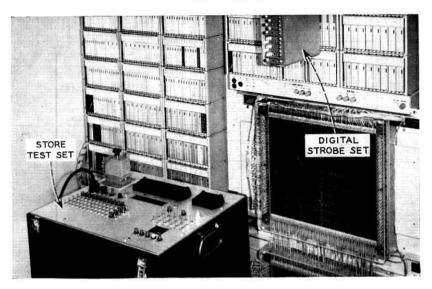

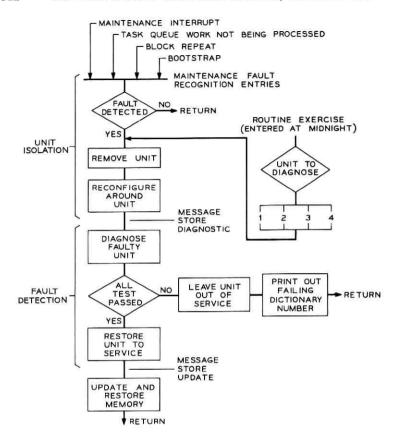

Both the TSPS and the SPC provide fault recognition and diagnostic programs for all major circuit elements. The purpose of fault recognition programs is to quickly detect faulty equipment units and cause them to be removed from service. When the execution of an order fails in the processing of a call, an appropriate fault recognition program is called in to determine if the trouble is repeatable and if so, to locate the faulty unit and remove it from service. Later, on a lower level of priority, diagnostic programs are called in to test the removed unit to isolate the trouble to a small circuit area. A trouble test number is printed on the maintenance teletypewriter for each specific test that fails. The maintenance man looks this number up in a trouble locating manual which indicates the circuit pack or packs that are likely to be faulty.

#### IV. DESCRIPTIONS OF TYPICAL CALLS

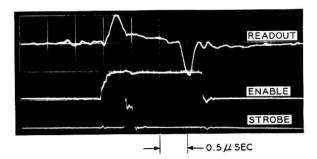

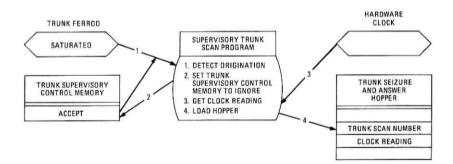

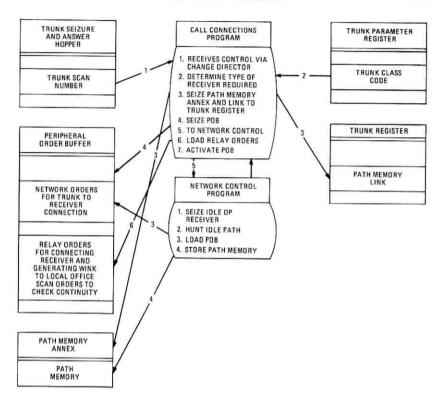

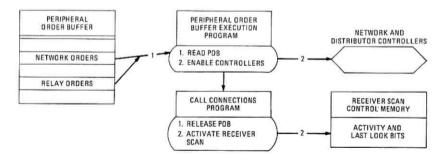

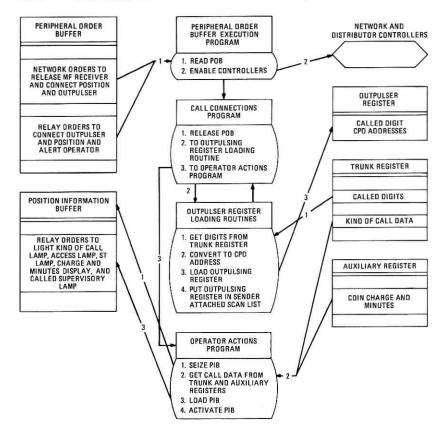

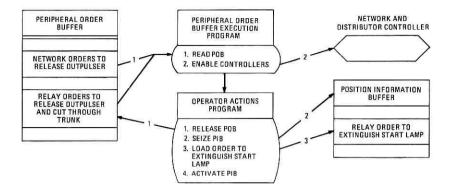

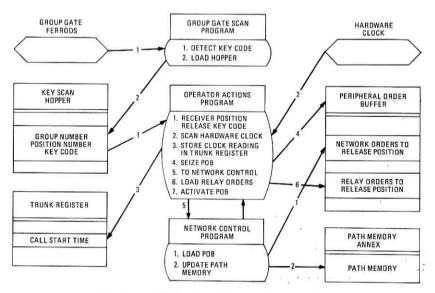

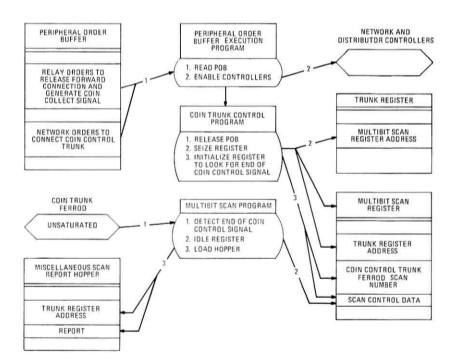

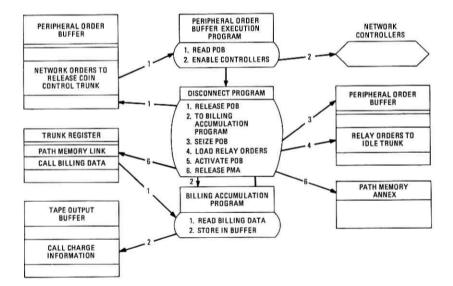

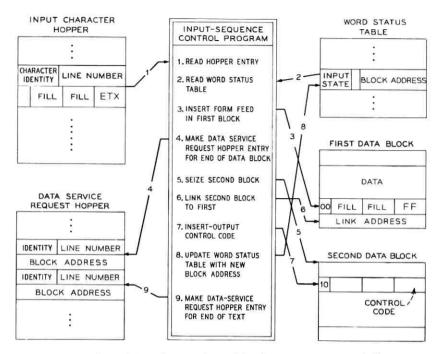

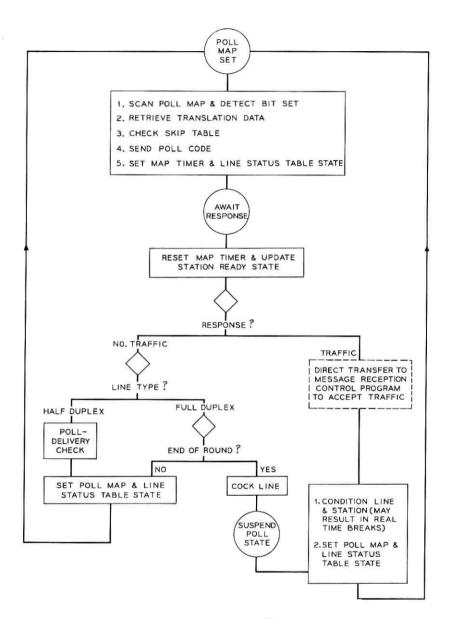

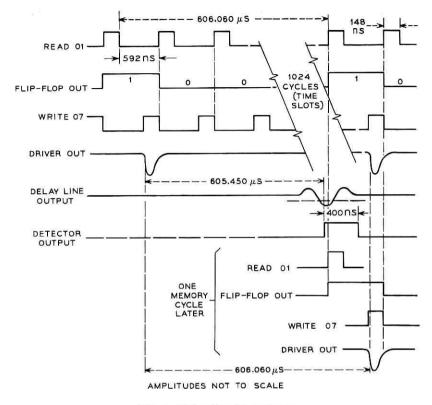

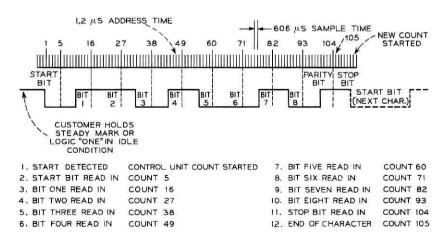

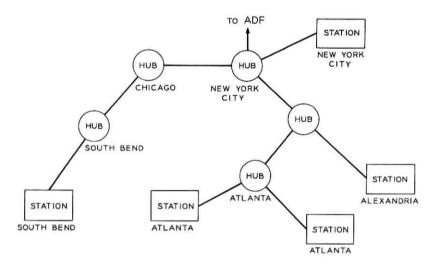

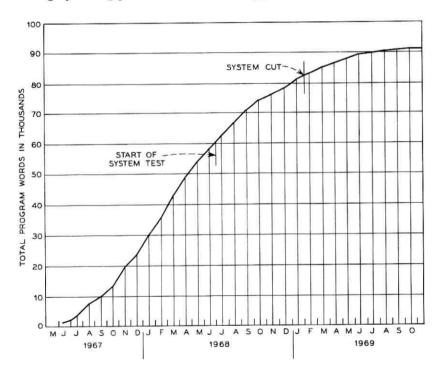

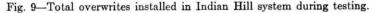

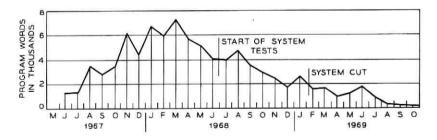

The operation and purpose of the system is best understood by describing how it processes two of the many varieties of calls. The numbers in Fig. 9 might be helpful as a guide.

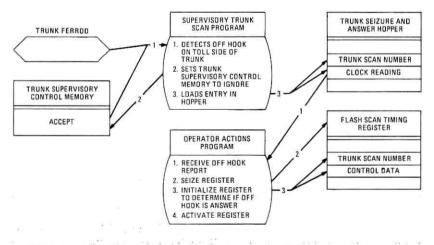

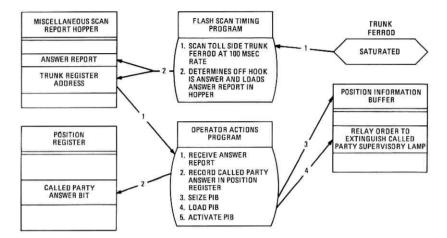

### 4.1 Coin Call

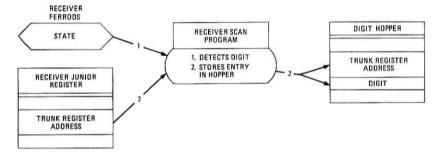

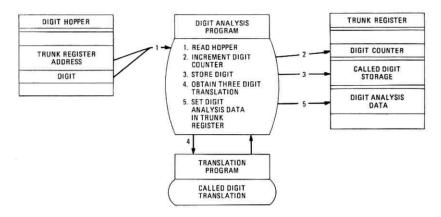

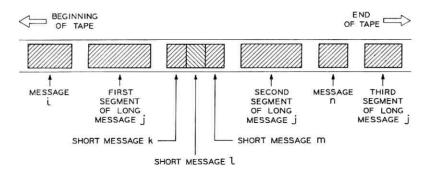

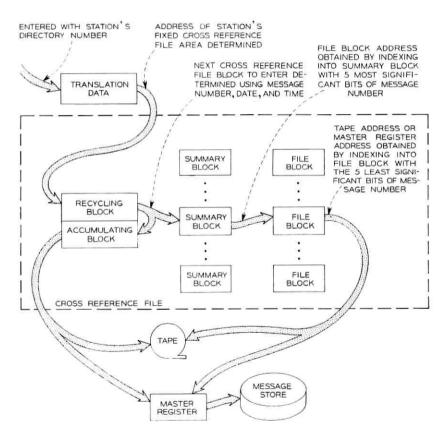

When a customer places a toll call from a coin station associated with a local office that is served by a TSPS, the instructions on the coin telephone direct that the complete called number, that is, the area code (if required) and the seven digit number for the desired party be dialed as soon as dial tone is obtained. If the customer wishes to place a stationto-station call, either a one prefix or no prefix is dialed prior to the called number depending upon local numbering plan arrangements.<sup>8</sup> As soon as the local office receives the digits, it determines that this call requires the services of a TSPS operator and the call is forwarded over a trunk to the TSPS. (See 1 in Fig. 8.) At the TSPS, as soon as the trunk circuit seizure is detected by scanning (2), a connection is established through the link network (3) to an appropriate service circuit.

Assuming the call is from a local office that has multifrequency outpulsing, a multifrequency receiver is attached and a supervisory signal is returned to the local office to indicate that outpulsing can begin. As each digit is received in the multifrequency receiver, it is detected by a directed scan (4) and placed in memory (5). When the complete called number has been received, a supervisory signal is returned to the local office requesting that the calling number be identi-

Fig. 9—To understand typical TSPS calls, study this drawing and its numbered parts in conjunction with the text.

fied and outpulsed to the TSPS office. In this case the multifrequency receiver remains attached to the trunk and receives the complete calling number and places each digit in memory.

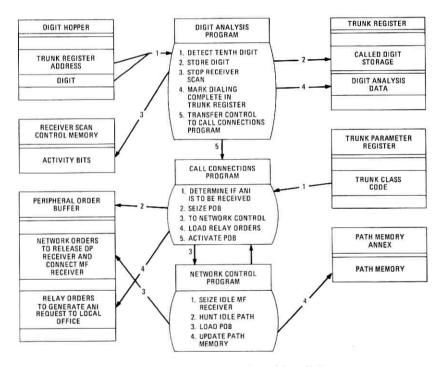

When both the called and calling numbers are stored, the system simultaneously seeks an idle operator position (6) and an idle outpulser (7). When both are available, it establishes connections from the two appearances of the trunk circuit to these two circuits (6), (7). While the operator is responding to the call and talking to the originating party, the outpulser is connected to the toll office (8) and after an exchange of supervisory signals, outpulses the called number supplied to it a digit at a time by the central pulse distributor (9).

The operator's display, controlled by a signal distributor (10), indicates that this is a coin call and gives the initial charge and time period

2436

for the call on a numerical display. She depresses the class of charge key to indicate to the system that a station-to-station type of call is being handled.

The customer, in responding to the request for money, deposits the coins. The operator monitors to see that the proper deposit has been made. In the meantime, the outpulser completes its function, is released, and the call is forwarded through the direct distance dialing network. An audible ring can be heard by both the operator and the originating party because the trunk has now connected the calling and called parties. Since this is a station-to-station call, the operator depresses the start timing key and releases her position as soon as the coins are deposited and she hears audible ringing. She is not required to participate in the call any further.

If the call is of the person-to-person type, she depresses a different call type key and remains with the call until the called station answers. After determining that the desired person is speaking, she depresses the start timing key and releases her position (6). All key actions are detected by a scanner and recorded in memory (11).

With the operator released, the call is timed by the system for the initial period. Eighteen seconds prior to the completion of the initial period, the TSPS sends a coin collect signal (12), (13) to the local office to cause the initial deposit to be collected automatically. This alerts the customer that the initial period is drawing to a close.

At the end of the initial period the system connects (6) an idle operator position to the trunk circuit. The position is not likely to be the same operator as for the initial seizure. This operator notifies the customer that the initial period is completed and that his call is going into the overtime period. If the call continues more than six seconds after the operator releases, the overtime period begins.

When the call is concluded, as indicated by on-hook supervision, the system seizes an available position (6) and indicates to its operator that this is the end of an overtime coin call. The overtime duration and charges are displayed. If the calling customer's phone is on the hook, the operator rings it by operating the appropriate key. After monitoring the deposit of the overtime charges, the operator depresses a key which signals that coins are to be collected and releases her position. Whenever charges are given to the operator for coin collection, appropriate taxes are computed and automatically added to the charge.

Studies have shown that normally it is not economical to provide memory space for coin rating tables for all calls. Most telephone companies attempt to provide automatic coin rating for about 95 percent of their coin traffic. When calls are not automatically rated, the operator receives a display indicating that she must do the rating of the call either by using the bulletin on her position or by calling a special operator over one of the outgoing trunks. Having determined the rating information, she then keys it into the system and the system automatically computes the charge, adding appropriate taxes. Except for the manually rated cases, it is the responsibility of the system and not of the operator to use the proper rate period based on the time of day and to keep track of holidays and weekends.

# 4.2 Person-to-Person Credit Card Call

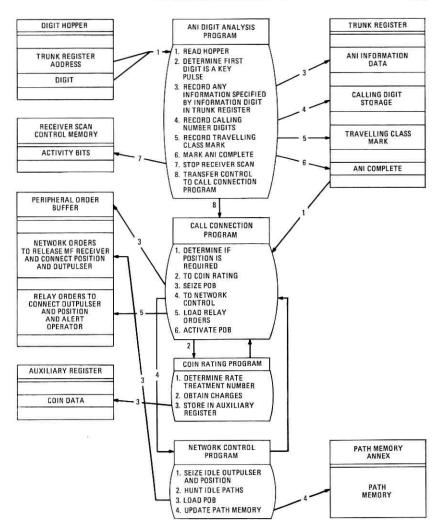

Calls made from noncoin stations are handled basically the same as they are from coin stations without the use of the coin features. To illustrate the difference in operation when dial pulsing is involved, let us follow a call from a step-by-step office.

Assuming a noncoin customer in a step-by-step office wishes to place a person-to-person call, a "0" will be prefixed before the 10-digit direct distance dialing number. The "0" indicates to the local office that the services of an operator are desired and a trunk to the TSPS is seized immediately after the initial "0" is received. Because there is no second dial tone with this type of service, the TSPS must be prepared immediately to receive dial pulse digits as soon as it detects the trunk seizure.

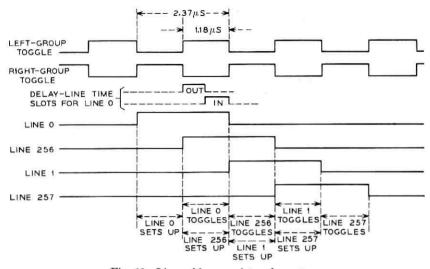

Because it may take 190 milliseconds to establish a connection (see 14 in Fig. 8) to an idle dial pulse receiver, the dial pulse incoming trunk circuits in the TSPS are arranged to receive and store up to two dial pulses to provide the needed time to establish the connection. When the receiver is connected to the trunk circuit through the network, a dc signal is sent from the trunk to the receiver indicating whether 0, 1, or more than 1 pulses have been received. If more than 1 pulses are indicated, the receiver signals (15) the processor to connect the call to reorder because it cannot assure the accuracy of the pulse counting. However, this occurs in less than five in 1,000 cases, which meets the designated service criteria. The remaining dial pulses are counted in the dial pulse receiver and at the end of each digit the processor (15) is given the digit for storing in memory as in the case of the multi-frequency pulsing.

At the end of the called number dialing, the system releases (14) the dial pulse receiver and connects (3) a multifrequency receiver to the trunk circuit through the network. A supervisory signal is sent to the local step-by-step office to request identification of the originating

number which is sent to the TSPS and recorded in memory as in the previously described coin call. In this instance, when the position is seized, the indication to the operator is that it is from a noncoin station and that the customer dialed "0" followed by 7 or 10 digits. She asks the customer what service is required and the customer indicates that he is making a person-to-person call using a credit card. The credit card number is then given to the operator and she keys it into the system. When the called station answers, she seeks the desired party. If the party is not at the station that was called and she determines that the person is at another station, she can release the forward connection (8) and key a new called number into the system (11). An outpulser is again connected (9) to the trunk to send forward the new called number. When she determines that the right parties are connected to each other, she depresses the start timing key, releases her position and the call is now "floating" (not associated with a particular operator) with the system monitoring the switchhook supervision of both the called and calling parties.

If for any reason the calling customer desires the assistance of an operator, a switchhook flash is detected by the scanner (2) and an idle position is connected (6) to the call. The operator determines the problem or the reason for being brought in on the call and takes the appropriate action. If there is a noisy condition, poor transmission, or wrong number, she can disconnect the called number and try again.

All positions in a TSPS are treated as members of one large team of operators to gain efficiency in service. There are several benefits. When the team size exceeds 120 operators, it is possible to achieve the 92 percent occupancy which has been established as an objective for operator services. Also, the full access of all trunk units to all occupied operator positions is valuable during light loads because all traffic can be sent to a small group of operators. This permits all but one group to be completely shut down during the lightest loads.

# V. ADMINISTRATIVE FEATURES

#### 5.1 Recent Changes

As in most complex telephone systems where many of the features are dependent upon the local conditions, call routing and charging must be appropriate to that area. Therefore, it is necessary to provide information known as "office data" for a particular installation to function properly. It is often necessary to modify or change this information from time to time.

## 2440 THE BELL SYSTEM TECHNICAL JOURNAL, DECEMBER 1970

In TSPS, because it uses electrically alterable memory, it is possible to make all changes through teletypewriter messages and for these changes to become a relatively permanent part of the system memory as soon as they have been verified. In order to minimize human errors, the TSPS recent change messages use an easily understood alphanumeric format. The TSPS programs insure that the information being provided for recent changes is rational within the context of the machine. It is also necessary for a person making a recent change to specify the existing information that is being changed. This acts as a double check and minimizes the possibility of errors getting into the system. In order to provide a simple method of operation, a separate teletypewriter channel is provided for recent changes giving the telephone company the option of placing the machine in the most convenient location. Frequently it is located in traffic quarters since most recent change information originates from the traffic department. The greatest recent change activity involves the coin rating tables and the size and classes of the trunk groups.

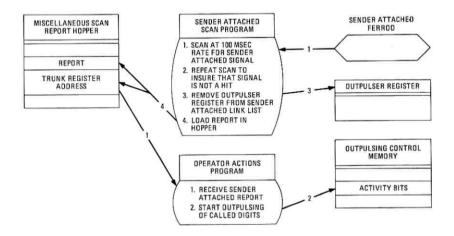

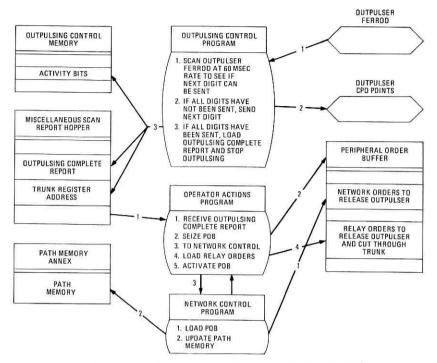

### 5.2 Traffic Facilities and Force Administration

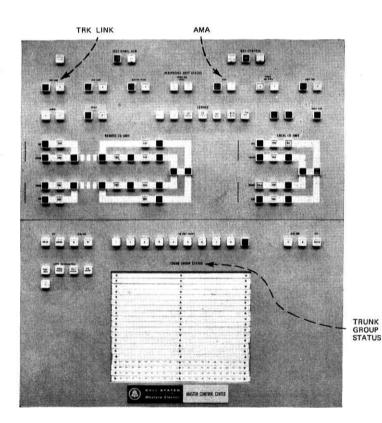

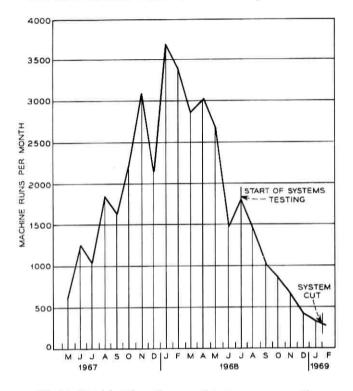

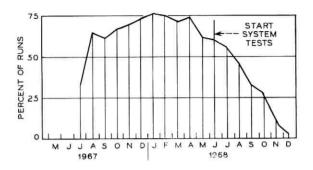

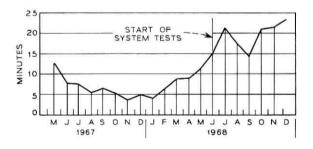

Of fundamental importance in the proper use of any switching system is the administration of the traffic dependent facilities of the system. Adequate quantities of hardware such as receivers, outpulsers, and coin control circuits, as well as software buffers, hoppers, and registers, must be maintained. In addition, a system like TSPS requires a sufficient number of operators to meet certain service criteria such as are set for speed of answer. To assist the traffic people of the operating companies in monitoring the adequacy of these facilities, traffic data is printed out periodically on a teletypewriter at the central administration group.

Part of this data is printed hourly to record peg counts and traffic usage measurements. Peg counts of certain service circuit seizures, usage measurements of in-service and out-of-service circuits, and usage measurements of many software facilities are provided. Additional information is also provided at 15-minute intervals on the load level of the system, the number of trunk seizures, trunk seizures requiring dial pulse receiver use, dial pulse calls encountering reorder, and the number of trunks made busy during an overload. Using this information, the facilities engineer can make adjustments in response to changes in the telephone traffic patterns and loads.

The central administration group also receives data concerning operator usage every half hour. These data include the number of position seizures, work volume, average number of positions occupied, and actual call value or the average holding time/position/call with the figures summarized by chief operator group and for the entire complex. With this data the forcing groups determines the total size of the operator work force and works out the requirements for each chief operator group. Central force administration is particularly important in the TSPS because all operators are a part of one large team but they are divided into as many as nine groups that can be separated by many miles.

Each chief operator also receives operator usage data every half hour for her group as well as for the complex. This information allows her to assess the effectiveness of her own group in comparison with the team and modify the training and supervision of her group.

# 5.3 Operator Keyed Trouble Reports

The TSPS operator, like most operators, is in a unique position of being able to assess the general quality of operation of the telephone network. She can detect operational problems when calls fail to be completed and can judge noise and transmission quality. Moreover, she frequently can detect whether the problems are toward the called or toward the calling party.

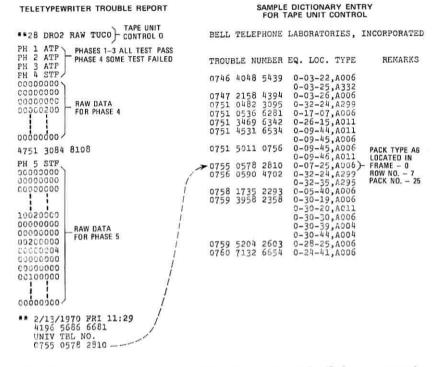

Because TSPS is a stored program system, it has a unique opportunity to record these observations efficiently. Any time she encounters trouble, the operator can, by key operations, indicate to the system the problem with the call then connected to her position. She operates the keypulse trouble key, two digits signifying the nature of the trouble, and the start key. The system upon receipt of the two digits makes a simple translation to determine whether the trouble report should be forwarded to the master control center teletypewriter in addition to the direct distance dialing service bureau teletypewriter.

When the printout is made, the trouble code, the reporting position identity, the identity of the trunk and the calling and called numbers are given. It is possible by analyzing repeated reports to locate such units as faulty trunks or to indicate areas that should get increased maintenance scrutiny. Results to date have indicated that this is a most valuable tool and means are being sought to automatically process the trouble information supplied by the operators so that effective response to these reports can be made in minimum time.

#### VI. PLANNED NEW FEATURES

It is the long range intention of the Bell System to ultimately replace all cordboards with TSP operation. The tedious and repetitious functions that can be best accomplished through mechanization will be automated. In keeping with this intention, it is expected that additional features will be placed on the TSPS No. 1 for handling those calls that still remain on cordboards. For example, mobile and marine calls, conference calls, and inward traffic to a toll center are likely candidates for addition to the TSPS.

There are plans to further automate certain calls now handled on the TSPS with manual ticketing. Included are automating time and charges record keeping on noncoin calls, semiautomated handling of hotel and motel calls, and providing operator assistance for international direct distance dialed calls.<sup>9</sup> It is likely that features that are not foreseen at this time will be added to the TSPS in future years. The stored program concept facilitates the addition of such features to existing offices.

#### VII. CONCLUSION

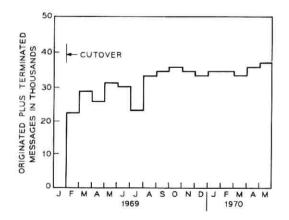

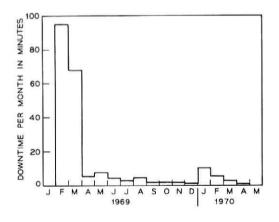

Nine TSPS installations are now in service in the United States. About 30 more offices have had equipment shipped which is now being installed. It is anticipated in the decades ahead that several hundred TSPS installations will be in service.

Experience in the early installations has shown that the TSPS has met its design objective. Those telephone customers who have expressed opinions about TSPS service have been most commendatory because of the speed of service and of the ability of the operator to give her undivided attention to the call. The telephone companies are pleased with this system because it provides simplified engineering, improved maintenance, adequate and timely data for traffic management and significant savings in traffic operating costs. The operators like TSPS because of the attractive decor employed in operating rooms, the modern consoles, and the fact that they can give customers their undivided attention when calls are connected to their positions.

The articles that follow describe many of the features of the system in more detail. Those items that are unique to the design of TSPS are stressed. The material covered in these articles represents the work of many people. This project was supported by many areas of Bell Telephone Laboratories and built upon the techniques of earlier developments such as No. 1 ESS and the crossbar tandem TSP. It also represents a close cooperative effort with the AT&T Company, Western Electric, and those telephone companies that received the early installations, all of whom played a most vital part in establishing requirements and implementing the design.

#### REFERENCES

- Freericks, L., "Special Positions for Person-to-Person, Collect and Credit Card Calls," Elec. Eng., 79, No. 10 (October, 1960), pp. 814-817.

Morris, R. M., "Crossbar Tandem TSP," Bell Laboratories Record, 42, No. 5 (May 1964), pp. 146-151.

"No. 1 ESS," BSTJ, 43, No. 5 (September 1964), pp. 1831-2609.

Clemons, D. G., and Little, R. S. "The Piggyback Twistor Store," Bell Labora-tories Record, 47, No. 11 (December 1969), pp. 359-364.

Fought, B. T., and Funk, C. J. "Electronic Translator System for Toll Switching," IEEE Trans. Commun. Technology, 3, 1970, pp. 168-174.

Baldinger, W. R., and Clark, G. T. "TSPS No. 1: Physical Design," BSTJ, this issue, pp. 2685-2709.

Comella, W. K., Day, C. M., Jr., and Hackett, J. A., "TSPS No. 1: Peripheral Circuits," BSTJ, this issue, pp. 2561-2623.

Keever, R. J., "Telephone Numbering Plans-Keeping Pace With Domestic and World Service Needs," IEEE Trans. Commun. Technology, 14, No. 10 (December 1966), pp. 863-864.

Scott, L. J. "Overseas Dialing: Yesterday, Today and Tomorrow," Bell Labora-tories Record, 48, No. 5 (May 1970), pp. 142-149.

TSPS No. 1:

# Stored Program Control No. 1A

# By G. R. DURNEY, H. W. KETTLER, E. M. PRELL, G. RIDDELL and W. B. ROHN

(Manuscript received August 17, 1970)

The Stored Program Control No. 1A processor complex was conceived as a program sequenced control for the Traffic Service Position System No. 1 and for the Electronic Translator Systems. It was designed to be a highly reliable complex using a conservative discrete component hardware design with excellent fault detecting capability and with exceptionally good automatic recovery of call processing when faced with hardware faults.

The design aims, order structure, hardware features, fault detection, diagnostic, and recovery aspects of the system are described. Stress is placed on those features which are felt to be improvements over previous program controlled systems.

#### I. INTRODUCTION

New telephone services are regularly being conceived which place large demands upon existing switching facilities—demands which are increasingly difficult to satisfy with electromechanical techniques. The use of large high-speed memory and stored-program logic permits the modernization of existing switching functions<sup>1</sup> and implementation of new services more effectively and at lower cost than by electromechanical means. The stored program control (SPC) No. 1A has been developed as a general purpose stored program electronic processing system to provide a flexible control for implementing new or modernized telephone services. It is a system which is independent of application but with generalized interfaces to which hardware and software may be readily applied in the development of specific application systems.

Bell System electronic switching machines must work reliably in an environment in which substantial noise and temperature variations may be encountered. System processing capacity must economically meet traffic handling needs over the projected life of the system. However, this requirement is generally met more readily with state-of-theart technology than the reliability objectives. Thus, the SPC No. 1A represents a conservative design in device technology and processing speed, but an advanced and sophisticated organization for automatic trouble recovery. The emphasis in this article is on the hardware and software organization for maintaining system operation with particular attention given to the maintenance features which depart from those used in other Bell System stored-program processors.

The SPC was developed concurrently with the traffic service position system (TSPS) No. 1, which is designed to improve operator assistance facilities.<sup>2</sup> The SPC is also used in the electronic translator system to replace the present electromechanical call routing translators in the 4A toll crossbar system.

#### II. A COMMON SYSTEM

#### 2.1 Hardware Organization

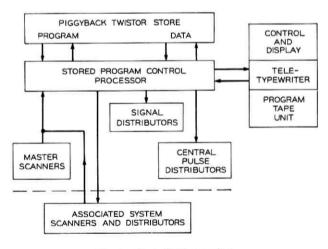

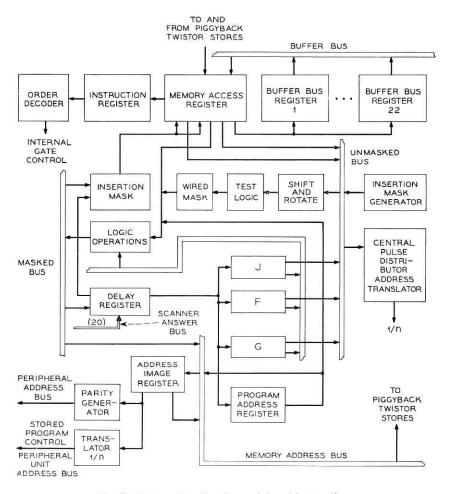

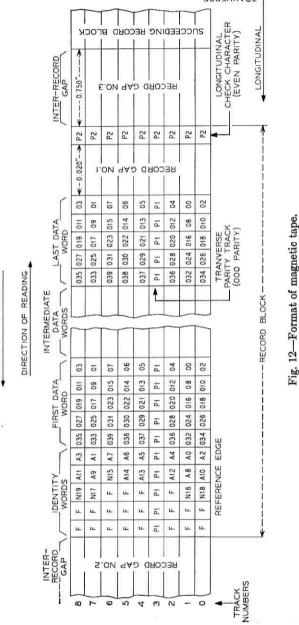

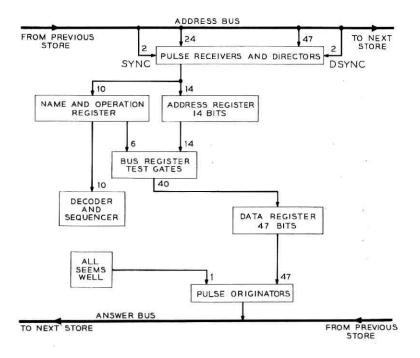

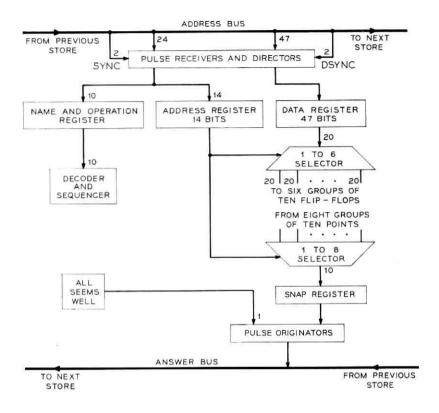

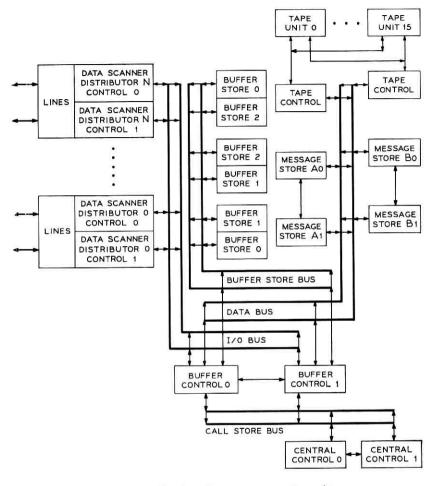

The basic concept of the SPC is that of an electronic data processor operating with a stored program to control all functions of its associated application system on a time-shared basis. The general organization of the SPC complex is illustrated in Fig. 1. The complex consists of the arithmetic-logic unit known as the processor, the memory system using "piggyback twistor" stores,<sup>3</sup> several peripheral units required for maintenance of the processor-memory system, and a master control center complex for man-machine interaction.

Fig. 1-Basic SPC complex.

To permit the widest application for the SPC, careful consideration was given to the structure and definition of the instruction set. The final choice consisted of 19 basic processing operations and 14 maintenance operations. These represent a compact but powerful order set that is well-balanced for either logical data processing or for control of peripheral hardware. This was particularly important for the SPC which in its inception was not aimed specifically at either one of these fields of application.

The first two application systems using the SPC, the electronic translator system and TSPS, are examples of these two quite distinct processing orientations: logical data processing and peripheral hardware control.

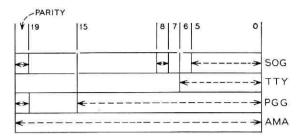

For basic data manipulation, memory access is organized for both word and character. In addition to access to full or half words, individual memory access instructions can, through an option field, specify the reading or writing of any byte. (A byte is an item of i bits positioned j bits from the least significant bit of any half word.) Seven processor index registers are fully flexible, that is, any may be specified for the functions of accumulator, return address, and so on. Transfer tests may be made on the total data or any specified bit of any register. The basic hardware oriented orders are scan and distribute orders. Special purpose orders provide combined operations to permit realtime efficiency for highly repetitive input-output functions.

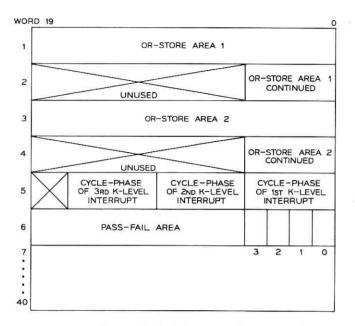

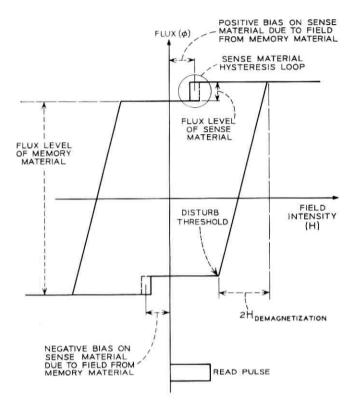

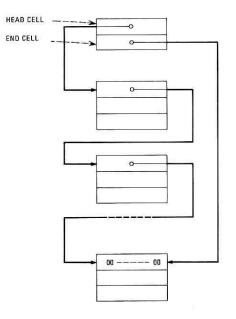

Data transfer to and from memory always consists of a full 40-bit word plus seven bits of error detection and correction code. The stores are nondestructive readout memories which are used to store both semipermanent and temporary data. Semipermanent data locations are protected from inadvertent writing by lockout circuitry. Protection is defined in increments of 1/16th of a store through wiring straps which may be easily changed in the field. The lockout function may be overridden by program control to permit updating or loading the semipermanent data.

Since the stores are electrically alterable, they provide a singlememory-device system for the generic programs, parameter data, office translation data, and the temporary data scratch pad.

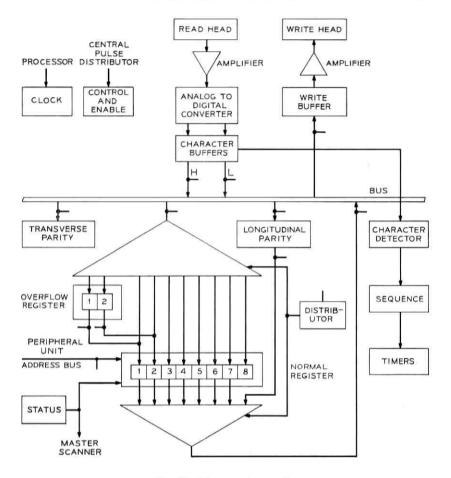

Maintenance of the central processor requires the ability to distribute control signals (that is, to set flip-flops or operate relays). This dictates the need for a central pulse distributor and a signal distributor.<sup>4</sup> To maintain units of the SPC, the system must also perform scan operations to read the states of internal points which requires the use of a master scanner.<sup>4</sup> Points in the matrices of these units which are not required for the SPC are available for use in the application system. Communication to these units is via private SPC peripheral and central pulse distributor address bus systems.

As a common system, the SPC design does not attempt to anticipate the peripheral addressing requirements of the application systems. Thus, provision is made for a standard binary output to an application system peripheral unit address bus. It is assumed that each application system requiring peripheral unit communication will provide an external translator for any desired translation function.<sup>5</sup> Application system scanner type units share the scanner answer bus system with the SPC master scanner.

The master control center consists of a control and display panel, a teletypewriter and a program tape unit. The control and display provides visual and audible indications of major and minor alarm conditions, as well as lamp displays of the status of the various equipment and buses that make up the SPC complex. It also provides keys for data input to the system and for control of the system configuration of on-line equipment units when manually aided recovery is required. These lamps and keys represent additional functions of the SPC that are implemented through the central pulse distributor, signal distributor, and master scanner.

The teletypewriter is the device by which the maintenance craftsman receives detailed information concerning trouble detection and isolation and through which he instructs the system to perform specific tests.

The program tape unit serves as a secondary memory system that is used initially to load the piggyback twistor memory and subsequently to make large changes in the generic program or office translation data. The capacity of the tape memory is such that many application system functions requiring bulk storage with slow access can be accommodated. For example, it can be used to collect dumps of office data for off-line verification and to retain the original office data during changes. It thereby serves as a backup should restoration be required. It can also be used to contain a library of infrequently used application routines, such as growth testing routines.

Flexibility for growth is quite important. In the SPC complex, the impact of growth centers primarily on the stores and central pulse distributors. As previously mentioned, the signal distributor and master scanner are on a private SPC address bus system and contain adequate matrix capacity for all SPC functions up to a maximum size. Assignments in the signal distributor and master scanner have been made to allow for maximum growth in the SPC area before allowing assignment points to be used by the application system. Growth for stores is considerably simplified by providing full bus connectorization.<sup>6</sup>

#### 2.2 Software Organization

The SPC generic program provides the necessary maintenance functions for recovery from troubles and for fault isolation in the various equipment that comprises the SPC hardware complex. (Generic program refers to the set of instructions common to all SPC systems.)

Since maintenance of the SPC hardware involves a man-machine interface, the programs which relate to the control and display, teletypewriter, and program tape unit are also part of the generic program. The maintenance test programs and input-output programs for the SPC equipment function as an integral part of the surrounding softwareenvironment and make very specific assumptions regarding this environment. This environment consists of job administration and certain common service programs. These provide not only a cohesive SPC maintenance system but also the framework for executing a broad range of application programs.

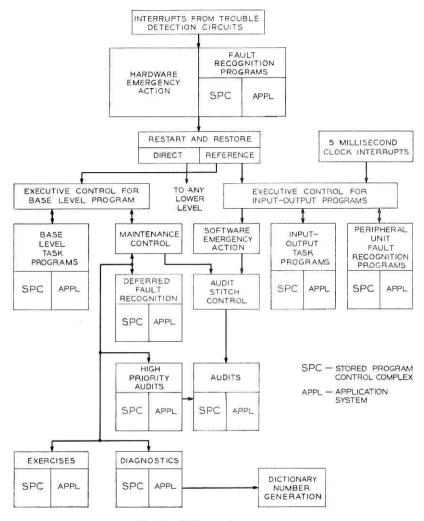

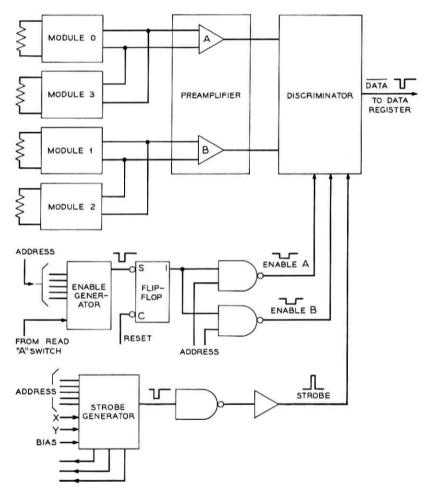

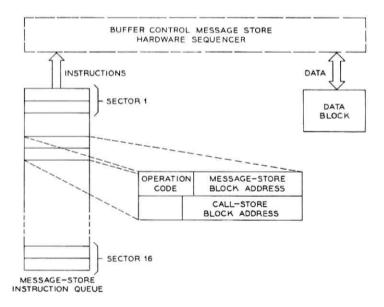

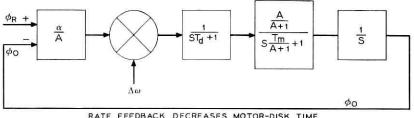

Figure 2 is a general block diagram of the SPC generic program and its interfaces with the application system program. The blocks are arranged from top to bottom to show descending priority levels of program execution. Certain blocks are labeled SPC APPLICATION. This indicates that for this class of program functions generalized interfaces have been established that readily allow integration of application system programs with SPC programs.

Of highest priority in the automatic handling of troubles are the fault recognition programs which are entered by interrupts generated when trouble detection circuits recognize a system malfunction. These programs are required to distinguish non-repeating from repeating circuit malfunctions and, in the latter instances, to remove the faulty unit from service, establishing a working system configuration so that the system's normal tasks may be resumed. In priority ranking, they are concerned with processor, store, and peripheral unit malfunctions. The peripheral unit fault recognition programs at this priority level are concerned with symptoms of hardware trouble which appear immediately after signals are sent to the peripheral system. Failure to receive an enable-verify signal or an all-seems-well signal from the peripheral unit indicates such trouble.

Hardware emergency action is another high priority program that is required to facilitate recovery from circuit malfunctions. It functions 2450

Fig. 2-SPC generic program.

in conjunction with a wired logic hardware sequencer to establish and test new combinations of active processor and active base store until a combination is found which is trouble free. (The base store is the store unit containing the emergency action recovery programs.) It is essential to cope with troubles that destroy sanity of the active control processor system first.

All maintenance interrupt programs return to normal call processing

via the restart and restore program. In most cases, the return is made to pick up processing at the point at which the interruption occurred. However, under some conditions this is not safe or feasible; the return is then made to an appropriate restart or reference point in the job administration stream where carryover of index register data is not required. Several of these reference points are defined in the two executive control programs.

An executive control program for input-output work is entered periodically from interrupts generated by a 5 ms clock.<sup>7</sup> This represents the next lower major priority class of work. Both SPC and application system input-output tasks are scheduled by the executive control. The SPC tasks include teletypewriter and program tape unit input-output, execution of signal distributor orders to operate lamps and alarms, and scanning for alarm conditions.

Another program activity scheduled at the input-output priority level is an extension of peripheral unit fault recognition. These programs look for peripheral controllers that have failed to reset to an idle state in the normal time interval. The SPC program of this class is required to handle signal distributor controller troubles.

A software emergency action is also scheduled by the executive control for input-output programs. It makes several tests for the sanity of system processing to detect degradation that could have been caused by data mutilation in unprotected memory. The SPC system and any appropriate application programs normally detect and correct such data errors by frequently running a series of memory audit programs. However, in some cases, mutilated data will produce an avalanche effect that requires immediate and drastic action. The emergency action program is designed to detect these cases and immediately execute a series of memory audit and initialization routines to restore normal operation.

The lowest priority class is that consisting of all the programs executed at the base level of processing, that is, the noninterrupt level of processing. These are scheduled by an executive control for base level programs which has flexible arrangements for assigning priority and scheduling task programs. These administrative functions are developed through the use of parameter tables which provide a simple interface for application programs.

In general, base level task programs process data collected by input programs and buffer appropriate data to be subsequently distributed by output programs. Return address linking is maintained in the output buffer tables so that the executive control programs can arrange the stages of processing in sequence for each call while providing timeshared processing of many calls.

At the lowest priority level in the base level of processing, the executive control enters the maintenance control program. This program arranges in sequence all maintenance task programs whose work may be performed on low priority relative to other system tasks. These deferrable maintenance tasks are executed by maintenance control according to priority.

The highest priority group consists of the deferred fault recognition programs. These programs are intended to bring as many units as possible into operation, since the interrupt level fault recognition program (because of constraints on interrupt time) may have to put together a minimum working configuration. The next level consists of high priority memory auditing routines designed to check the integrity and consistency of the data used in the various bookkeeping operationsof the program system. The routines are called in at this priority level by programs encountering processing anomalies or hardware failures which might lead to data mutilation.

The diagnostic programs are next in the priority structure. They perform exhaustive tests on the units removed from service by the fault recognition programs and save the pass-fail data for the tests. These data are processed by the dictionary number generation program to produce a number printed on the maintenance teletypewriter. The number is used to enter an appropriate trouble location manual which will identify a circuit pack or packs suspected of causing the trouble. The lowest priority of maintenance programs are the exercises, which include routines that respond to manual requests, routines that periodically test circuit functions which are not in continuous use, and memory audits which are run when all high priority work has been completed. The tables used by the maintenance control program make generous allowance for adding application routines in each of the various priority categories.

Another important function of the maintenance control program is known as audit stitch control. This mode of system operation is requested by the software emergency action program when it detects symptoms of software insanity. Under the audit stitch control, a series of memory audit and software-hardware initialization routines are executed (that is, "stitched") to restore sanity. All call processing activity is suspended during this operation.

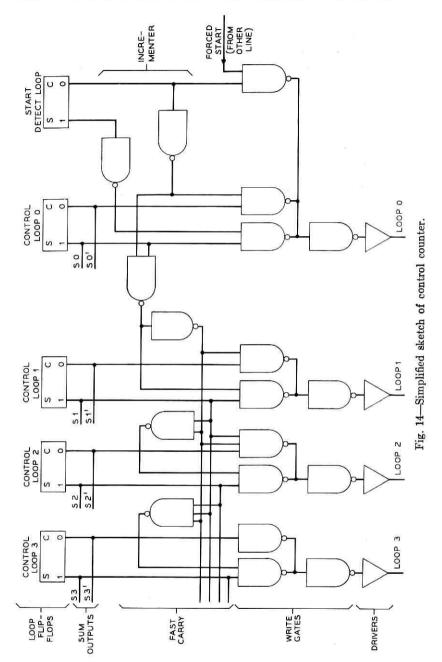

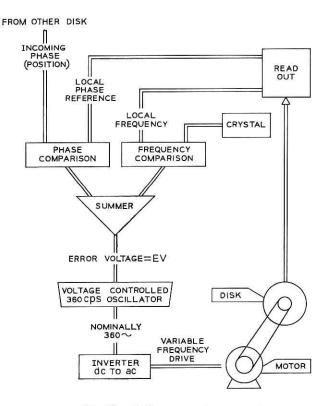

Figure 3 depicts the program control plan specifying the functional assignments for the maintenance interrupts (A through G plus K),

Fig. 3-Program control plan.

the input-output interrupts (H and J) entering the executive control for input-output, and the executive control for base level with its several priority classes of work. Most of the blocks in this figure have been referred to generally in the preceding discussion. However, a few further comments are required to clarify some points.

The maintenance interrupt blocks are designated in terms of the hardware subsystem whose trouble detection circuits generate the particular interrupt level. An appropriate fault recognition program for a given hardware subsystem is entered from the interrupt level associated with the control and display panel where facilities exist for the craftsman to configure the system when automatic reconfiguration is unsuccessful. The G and K levels are associated with specialized functions discussed in detail later.

All base level task programs are assigned to one of the five priority classes (A through E). A priority class of work known as "interject" represents an intermediate priority between interrupt and noninterrupt (base-level) programs. Section IV says more about this class. The

lowest priority base-level class (E) is primarily dedicated to maintenance control and the programs which it schedules.

Several techniques have been used extensively to provide a clean interface between the SPC programs and the application system. One approach in the administrative programs is heavy reliance on table control. The tables of these programs allow very flexible task program scheduling and priority assignment. The SPC and application task programs may be mixed together in the tables with SPC assignments ordinarily remaining fixed.

Transfer vector tables (transfer orders to link interprogram communication) are used as a fixed interface for certain necessary linking of SPC programs and application programs. Since the application programs may be located differently in the various systems, this technique avoids consequent variations in the SPC programs.

These techniques make it possible to provide a standard SPC load tape. This is of considerable value to development organizations that use the SPC in an application system development, since they can freely alter the structure of the application programs without having to reassemble SPC programs.

### III. HARDWARE

#### 3.1 General

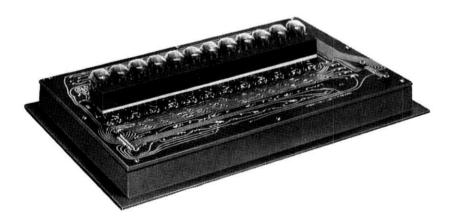

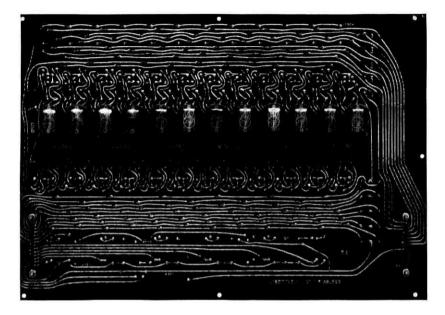

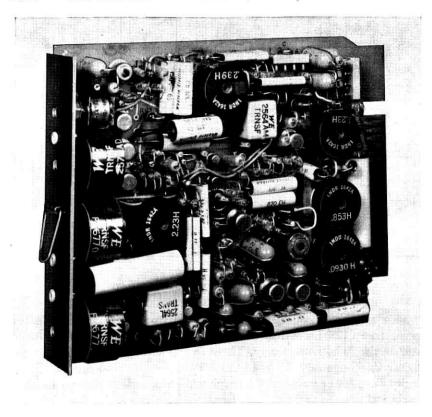

To obtain economic advantages from standardized hardware it was decided early in the development of the SPC complex to use low level logic and the existing ESS No. 1 circuit packs wherever possible.<sup>8</sup> Only when there was no existing circuit pack was one designed. Where possible, entire circuits and circuit functions were used from ESS No. 1 with the result that several units are nearly identical.<sup>9</sup> Because of this decision, the central pulse distributor, signal distributor, master scanner, teletypewriter circuits, and communication bus systems are so similar to ESS No. 1 circuits that only minimal descriptions are given here because detailed descriptions appear in Ref. 10.

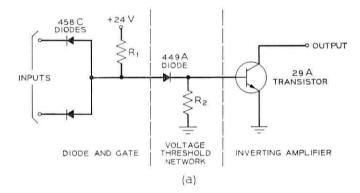

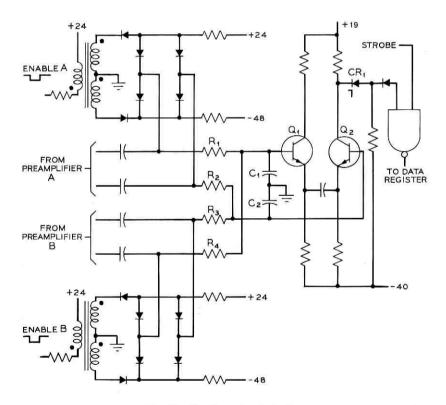

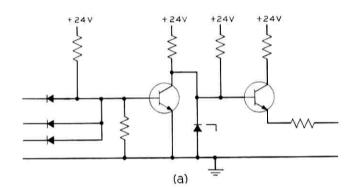

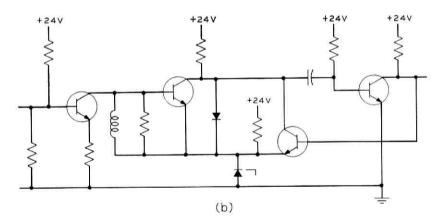

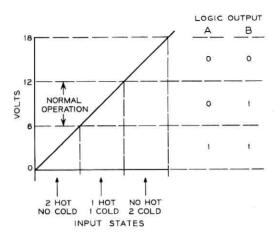

### 3.2 Basic Logic Gate

Throughout the entire system the basic No. 1 ESS "and not" low level logic gate was used (see Fig. 4). The characteristics are as shown. Worst case circuit design techniques were used in order to insure reliability over working voltage and temperature ranges during the life of the office.

For a moderate sized SPC complex with 20 piggyback twistor stores,

| PARAMETER                         | RANGE                      | TYPICAL VALUE   |

|-----------------------------------|----------------------------|-----------------|

| SIGNAL LEVELS                     |                            |                 |

| HIGH (1)<br>LOW (0)               | 4.0 - 5.1 V<br>0 1 - 0.5 V | 4.6 V<br>0.25 V |

| FAN-OUT                           | 1 - 8                      | 4               |

| FAN-IN                            | 1-20                       | 4               |

| TURN-ON DELAY                     | 10-65 N SEC                | 35 DSEC         |

| TURN-OFF DELAY                    | 10-65 NSEC                 | 35 D SEC        |

| NOISE MARGINS<br>HIGH<br>LOW      | 1.6-3.6 V<br>1.0-1.5 V     | 2.5 V<br>1.2 V  |

| CIRCUIT MARGINS                   |                            |                 |

| RESISTOR<br>TOLERANCE             | ± 20 %                     |                 |

| VOLTAGE<br>TOLERANCE              | ±10 %                      |                 |

| POWER<br>CONSUMPTION              | 37-140 MW                  | 76 MW           |

| OPERATING<br>TEMPERATURE<br>RANGE | 0-55°C                     |                 |

(b)

Fig. 4—Basic low level logic gate (a) and characteristics (b).

about 50,000 low level logic gates are required. Forty-two percent are used in the stores, 40 percent in the duplicated processors and the other 18 percent in the rest of the SPC complex. In addition to low level logic gates there are many circuit packs requiring higher powered transistors for power supplies, memory drivers, etc.

## 3.3 Processor Description

#### 3.3.1 General

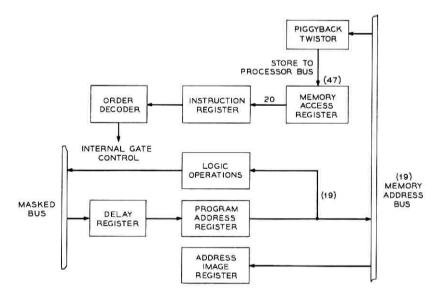

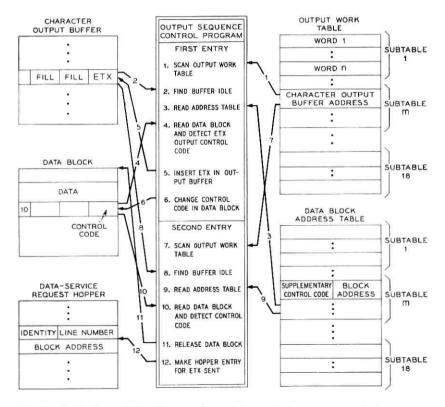

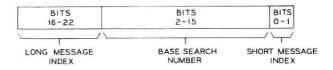

The processor, which provides the control for the system, is a computer-like circuit which executes program instructions received from the piggyback twistor stores. The processor cycle is  $6.3 \mu$  long. Execution of an instruction requires from 1 to 10 processor cycles. During the last cycle of each instruction the processor reads memory to obtain the next instruction to be executed. Figure 5 depicts the essential portions of the processor which are required for this instruction fetching. The memory address of the next instruction is contained in the 19-bit program address register.

The five most significant bits specify the name of the store to be approached, and the remaining 14 bits indicate the internal address within that store. The processor is thus capable of addressing any one of 32 stores and approaching any of 16,384 locations in that store. The total memory capacity for the system exceeds one-half million directly accessible 47-bit words.

The address image register is a 20-bit register which temporarily retains the address of the most recent communication with the store. If an error occurs during the store communication, the address to

Fig. 5—Program fetching.

which readdressing is required is available in the address image register. The least significant bit of the address image register is used internally by the processor to select a half word on some instructions.

The processor performs logic with a 20-bit combinational parallel subtractor which is also capable of addition and the logical operations AND, OR, and EXCLUSIVE-OR.

The result of a logic operation may be gated to the delay register via a 20-bit bus called the masked bus. The delay register provides temporary storage for instructions which require gating of information from the program address register (or an index register) through the logic operation and back to the program address register (or index register).

The memory access register is a 47-bit register which accepts information from the piggyback twistor stores. The 47 bits consist of a 40-bit word generally containing a 20-bit operation code and a 20-bit address or data field as well as a 6-bit Hamming error correction code and an overall parity bit. The instruction register is a 20-bit register which stores the operation code for the instruction to be executed, and the order decoder controls the gating and information signals necessary for its execution.

In memory fetching, the contents of the program address register are gated onto the memory address bus, and a read instruction is sent to a store. While the processor is waiting for the store response, the program address register contents are gated to the logic circuits where they are incremented to the next higher store address to prepare for reading the next program instruction. The resultant address is gated to the masked bus and into the delay register.

When the store has completed its reading cycle, it gates 47 bits of information onto the store-to-processor bus and subsequently into the memory access register. The most significant 20 bits are gated into the instruction register where they provide inputs to the order decoder until the instruction is completed. During the beginning of the execution of the instruction, the updated program address will be gated from the delay register to the program address register in preparation for the next fetch.

There are five main classes of SPC instructions which make up the SPC program repertoire: internal data manipulation, transfer, memory reading, memory writing, and peripheral input-output orders. These instructions are designed to provide a powerful set of orders for use in a broad variety of application programs. To accomplish this objective, virtually every instruction can be executed with any of the internal index registers. Any index register may be used for operations such as address indexing, return address storage, logic operations, and peripheral unit enables. Special circuits were designed to permit some of the frequently performed tasks to be accomplished efficiently. For example, circuitry was added to provide access to a particular bit or set of adjacent bits (that is, a byte) with just one instruction. A corresponding packing option is available through another circuit for memory writing orders.

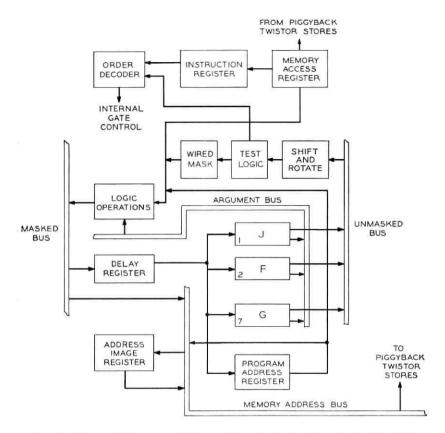

# 3.3.2 Internal Data Manipulation Instruction

An internal data manipulating instruction is used for operations in which data from an internal register are placed into a register after some arithmetic or logic operations are performed on the data. There are seven general purpose registers each consisting of 20 bits which provide storage for information manipulation. For convenience and efficiency all data handling inside the processor is done in the half word size of 20 bits. Two 20 lead digital converted bus systems provide easy access to and from these registers.

Figure 6 indicates the arrangement of the registers and the buses. Access from the registers to the logic operation circuit is provided by the unmasked bus and the argument bus. With this arrangement it is possible to perform a logic operation on any two of the registers by gating one on the unmasked bus and the other on the argument bus and requesting the desired function from the logic circuitry. The results are gated onto the masked bus and into the delay register. From there the result may be transferred to any of the registers.

Although the data words are 20 bits long, operational data themselves normally consist of much smaller bytes. A byte is a quantity defined by a programmer which can vary between 1 and 20 bits. Several of these bytes are then assembled into a 20-bit word for efficiency in storage, and a common task is to unpack a particular byte. The byte of interest is isolated by performing an ANDing operation of the 20-bit word with a register.

Figure 6 also indicates circuits which have been added to permit unpacking of the most commonly used bytes without using a register. The shift and rotate is a combinational circuit which permits shifting or rotating data to the left or the right by any number of bit positions from 0 to 19. The wired mask inhibits transmission of all information except a selected group of right adjusted bits. There are 16 different mask sizes which may be selected. These mask sizes are 1-12, 14-16, and 20 bits. Unpacking is accomplished by gating contents of a register

Fig. 6-Internal data manipulation and transfer instruction information flow.

onto the unmasked bus into the shift and rotate where the data is rotated until the byte to be isolated is adjusted to the right. The byte can then be passed through the wired mask and gated into one of the general purpose registers. Some instructions of this type have sufficient bits in the instruction code to specify a logic operation with a second register after the wired unpacking has taken place.

#### 3.3.3 Transfer Instructions

Transfer instructions require a single machine cycle, and are basically fetching operations. If the transfer is conditional the address at which the fetching occurs depends on whether the transfer conditions are satisfied or not.

The least significant 20 bits of the memory access register contain

the address to which program control is to be transferred if the transfer is consummated. This address may be augmented by adding to it the contents of any one of the seven general purpose registers in an operation called indexing. Indexing is permissable on all orders which involve store or peripheral communication.

An address is indexed by gating the right half of the memory access register to the logic operations and at the same time placing the contents of the selected general purpose register on the argument bus. These two quantities are added in the logic operations, the sum is gated onto the masked bus for subsequent gating to the memory address bus, and to the piggyback twistor stores. When a transfer is executed, the present address may be gated into any one of the general purpose registers and later be used as a link back into the present program.

When a conditional transfer instruction is executed on contents of a register, the register is tested in test logic at the same time as the indexed address is being formed. The result of the test is transmitted to the order decoder where the proper gating is established to transfer program control to the new address or to perform a normal fetch for the next sequential instruction.

### 3.3.4 Memory Reading Instructions

Figure 7 depicts the flow of data associated with a half-word memory read instruction. In a fetching instruction the 20 least significant bits in the memory access register contain the basic store address. During the first part of the first cycle this address can be combined with the contents of any general purpose register to initiate a reading sequence in the store selected.