#### RCA ENGINEER Staff

| W. O. Hadlock         | Editor              |

|-----------------------|---------------------|

| E. R. Jennings        | Assistant Editor    |

| Mrs. C. S. Marchionni | Editorial Secretary |

| J. L. Parvin          | Art Director        |

| J. O. Gaynor          | Photography         |

#### Engineering Editors

C. A. Meyer, Mgr., Commercial Engineering Technical Services, Electron Tube Division

T. T. Patterson, Mgr., Technical Publications,

Electronic Data Processing Engineering

C. W. Sall, Technical Publications

Administrator, RCA Laboratories

L. A. Thomas, Mgr., Publications Services

Astro-Electronics Division

F. D. Whitmore, Technical Publications

Administrator, Defense Electronic Products

#### Editorial Advisory Board

E. I. Anderson, Mgr., Operations, RCA Victor Home Instruments Division

A. D. Beard, Chief Engineer

Electronic Data Processing

J. J. Brant, Director, Personnel

C. C. Foster, Mgr., RCA REVIEW

M. G. Gander, Mgr., Consumer Product

Administration, RCA Service Co.

C. A. Gunther, Division Vice President, Technical Programs, DEP and EDP

E. C. Hughes, Administrator, Technical Committee Liaison, Electron Tube Division

E. O. Johnson, Chief Engineer,

Semiconductor and Materials Division

W. C. Morrison, Assistant to the Chief Defense Engineer, Defense Electronic Products

D. S. Rau, Vice President Engineering,

RCA Communications, Inc.

H. E. Roys, Chief Engineer,

RCA Victor Record Division

D. F. Schmit, Staff Vice President,

Product Engineering

C. M. Sinnett, Director, Product Engineering

Professional Development

V. E. Trauant, Chief Engineer, Broadcast and Communications Products Division

Dr. H. J. Watters, Chief Defense Engineer,

Defense Electronic Products

J. L. Wilson, Director, Engineering

National Broadcasting Co., Inc.

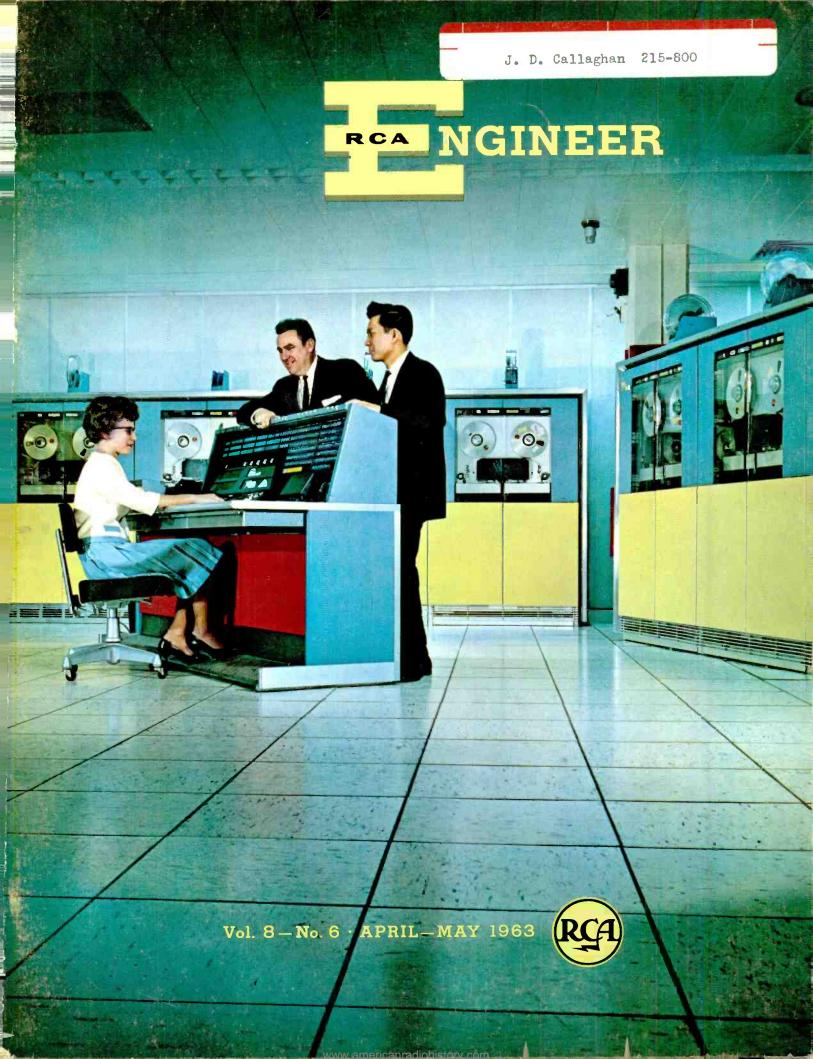

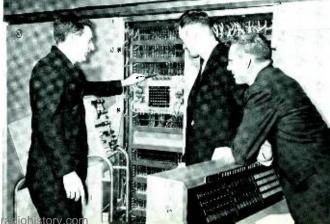

#### OUR COVER

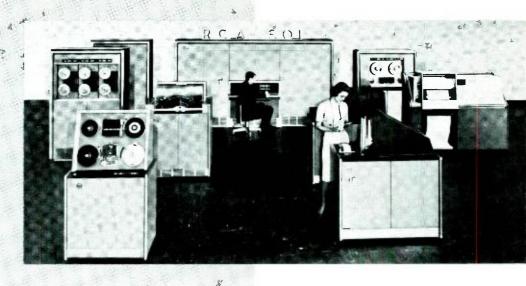

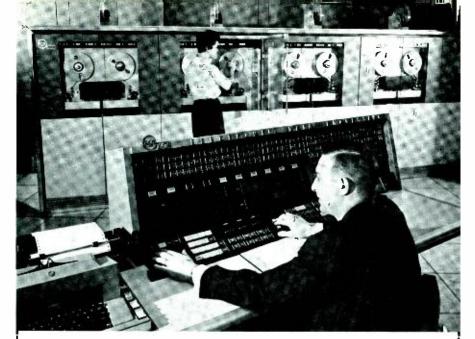

delivered to the New Jersey Bell Telephone Company at Teaneck, N.J., in December 1962. This system was the first of five scheduled far customer delivery by the end of 1963. Shown are Miss Barbara Allen, New Jersey Bell Telephane Company Console Operator, J. J. Worthington, Manager of the RCA 601 Project, and Michael Arya, RCA 601 Logic Design Engineer.

#### The Tidal Wave of Electronic Data Processing

Electronic data processing—from a small ripple in the late 1940's—has surged into a powerful force for business, industry, and the military, and its momentum is increasing at a rapid rate. Technological and application developments have reinforced each other, providing additional impetus and directions for the field to propagate.

ENIAC, the first electronic computer, was delivered to the Aberdeen Proving Grounds in 1947. Mathematicians used its high-speed computation ability, provided by vacuum tubes, to solve artillery ballistic problems. In the early 1950's, magnetic memories gave the computer increased power and flexibility. In the same era, magnetic tape stations and drums began providing large and rapid bulk files for data and instruction storage. Augmented by high-speed input equipment and printers, the computer—which had been the almost-exclusive tool of the mathematician—became part of a data-processing system that could serve the business world in areas such as stock control, payroll application, and insurance billing.

The RCA 501 heralded the advent of the transistorized computers, which increased reliability, performance, and compactness and opened up new doors in the fields of military and industrial control.

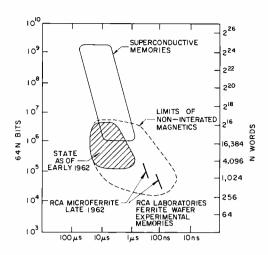

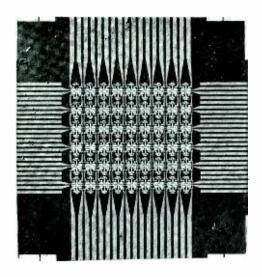

Today, the practical applications of data-processing systems are being expanded by the development of micromagnetic and cryogenic memories, random-access files, optical character reading, data input and collection devices, fast and flexible display systems, and powerful means for integrating communication facilities with computers. The host of technological advances not only are opening up new functions but also are providing increased system performance at lower cost, bringing many new applications into economic practicality.

But in the final analysis, technological advances are only generating better and better tools. Far more people are required to effectively utilize these tools than to develop them. The challenges of successful application are in many ways more difficult. Historically, it has been difficult and slow to overcome the inertia and smugness of present practice. The rewards are great, however, and one only has to view the many application advances to "get the picture."

Engineering is presently utilizing computer systems for mathematical reductions, statistical analysis, circuit design, generation of wire lists, drawing control, schedule and cost control, and simulation studies, to name a few. *Increased productivity* is a primary challenge to all of us, and it is the goal that we *must* achieve to stay competitive—whether from an individual, or company, or national point of view. Electronic data processing provides a tremendous opportunity to achieve this goal. It will require that the individual become knowledgeable and conversant with this tool and that he apply it imaginatively to his area of responsibility.

The wave is here. Are you prepared to swim?

A. D. Beard Chief Engineer Electronic Data Processing Radio Corporation of America

CONTENTS

VOL. 8, NO. 6 APRIL-MAY 1963

NOTES

**DEPARTMENTS**

| and Engineering Memoranda-Questions and Answers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RCA Computer Research-Some History, and a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _        |

| Review of Current Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6        |

| Five Years of Progress—A Review of RCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.4      |

| Electronic Data Processing Product EngineeringJ. N. Marshall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14       |

| Product Trends in the DEP Data Systems Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18       |

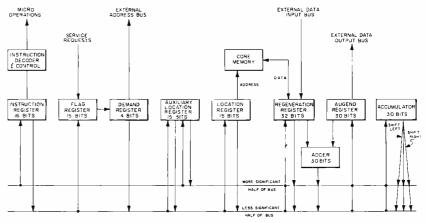

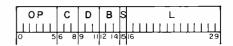

| The RCA 301 Scientific Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21       |

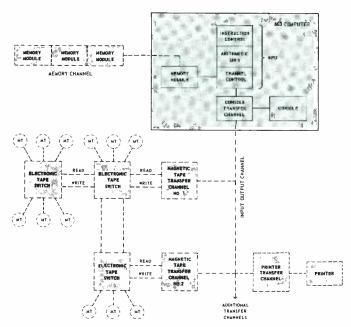

| The RCA 601 Computer System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28       |

| Automatic Data Recording System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| The RCA 4100 Series Military Digital Computers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31       |

| Aerospace Micromod ComputerA. Olsson, F. Hassett, and R. Gorman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36       |

| The 1963 David Sarnoff Outstanding Achievement Awards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40       |

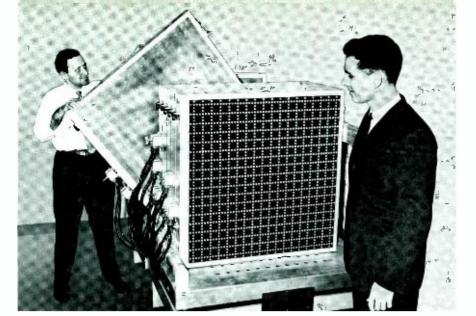

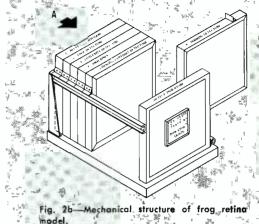

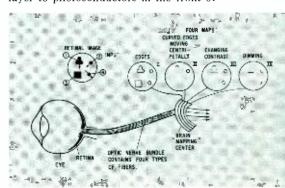

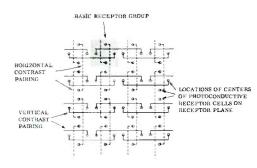

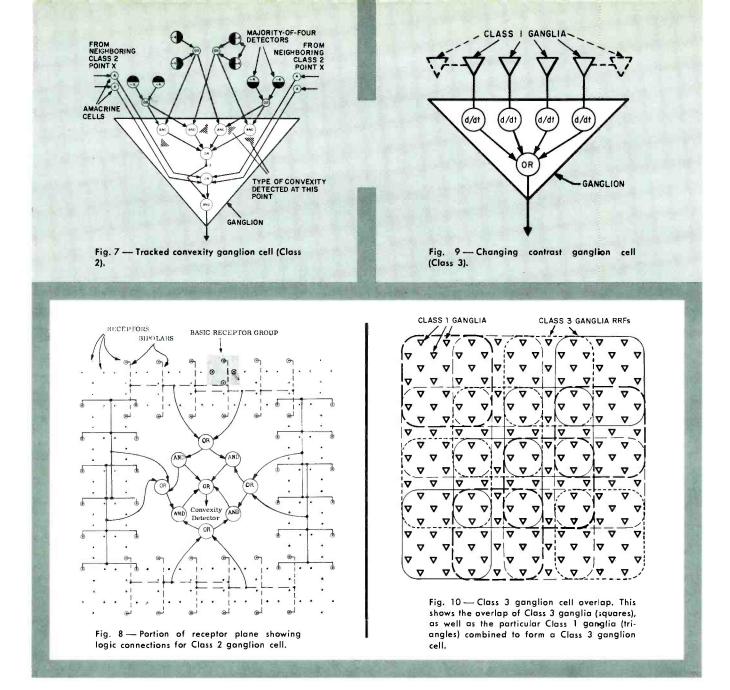

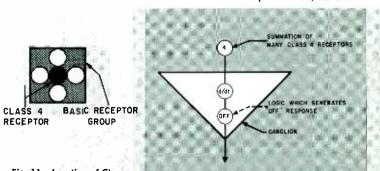

| Functional Electronic Model of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40       |

| Frog Retina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42       |

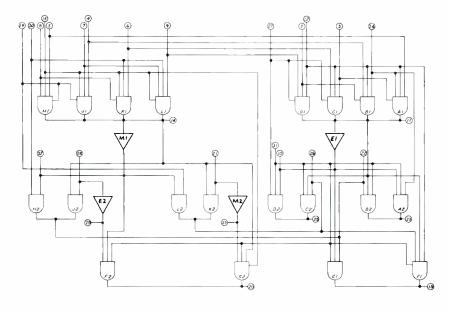

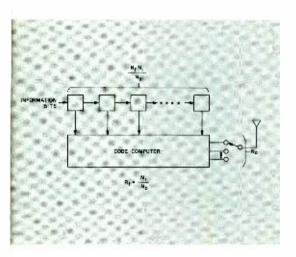

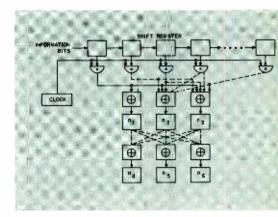

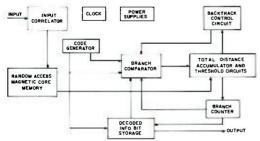

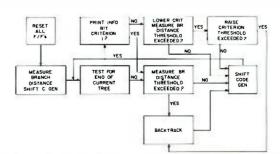

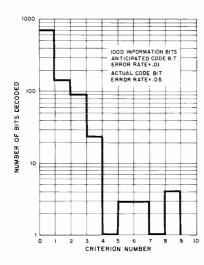

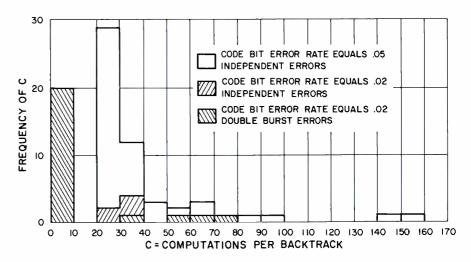

| A Special Purpose Digital Computer for Sequential Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40       |

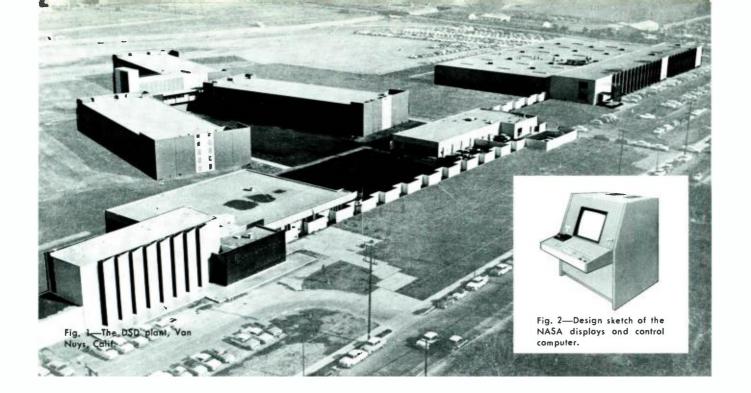

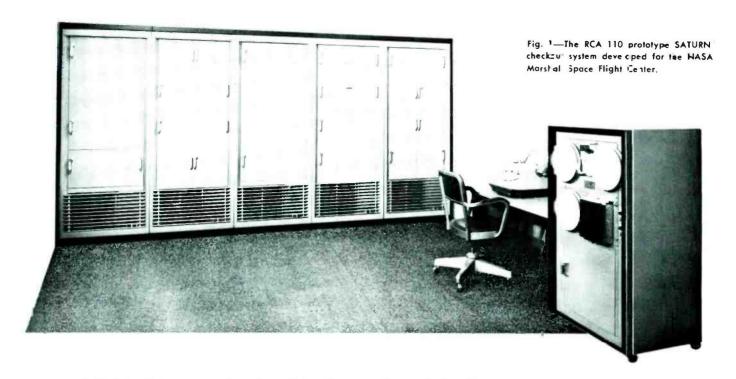

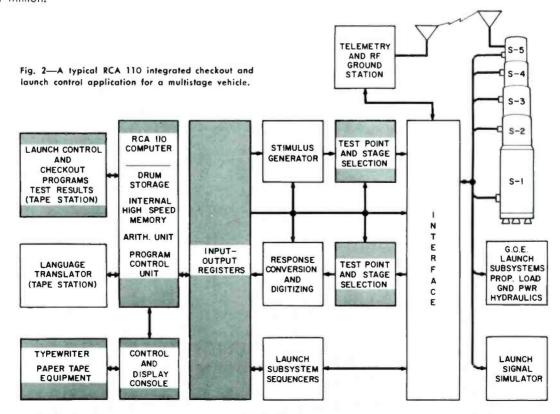

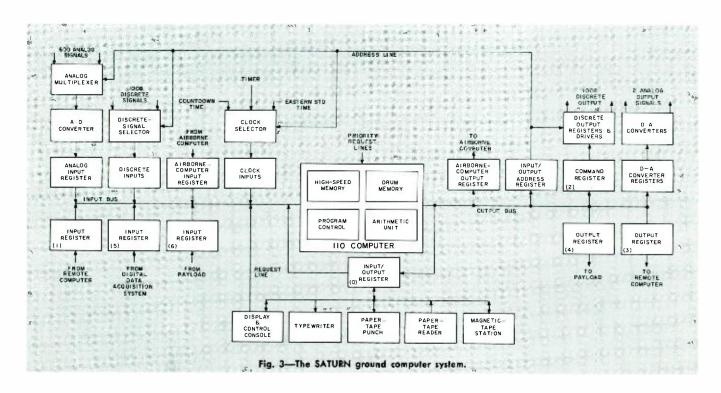

| High-Speed Computer-Controlled Checkout System for Saturn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50       |

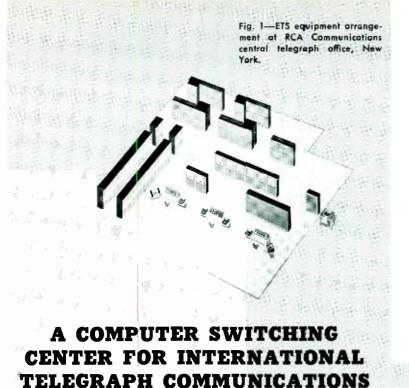

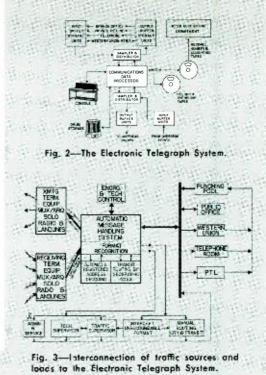

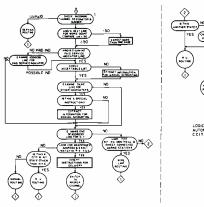

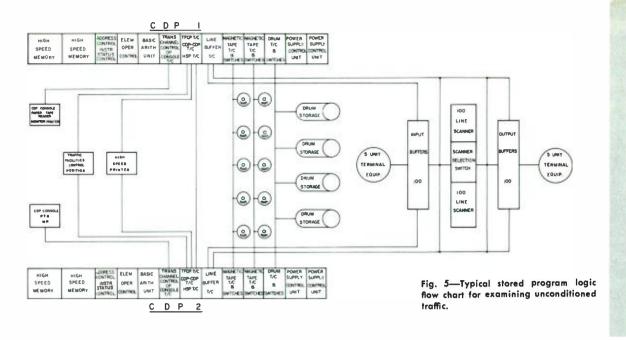

| A Computer Switching Center for International Telegraph Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53       |

| Ensuring Successful Computer Installations—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00       |

| The Training of RCA Computer Service RepresentativesM. H. MacDougall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56       |

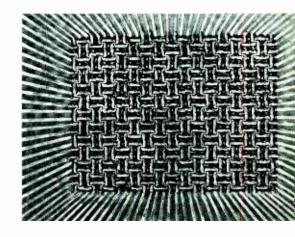

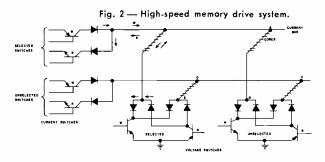

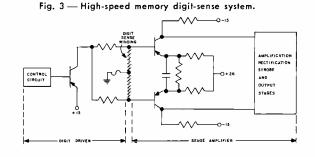

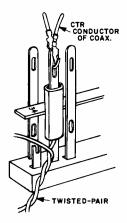

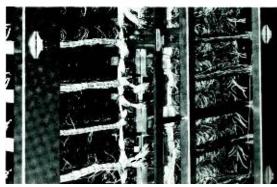

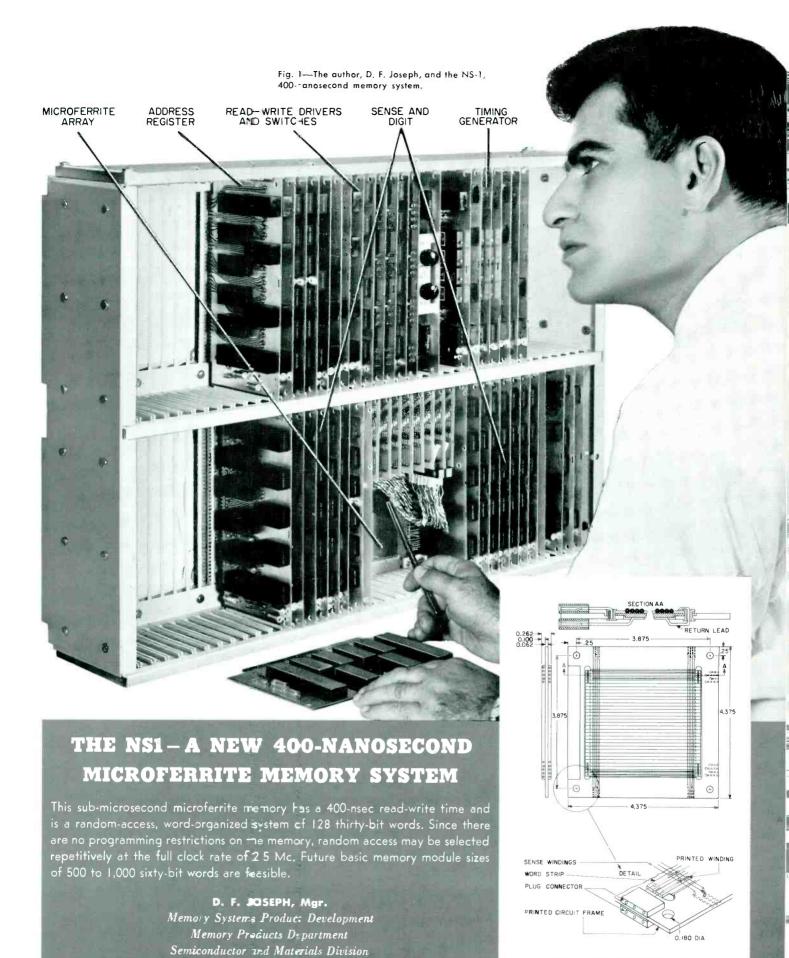

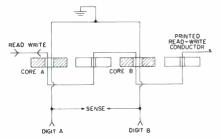

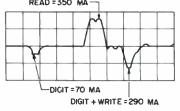

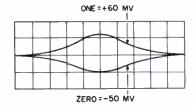

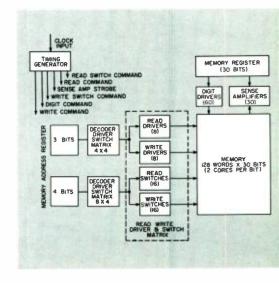

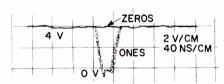

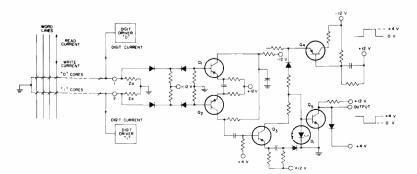

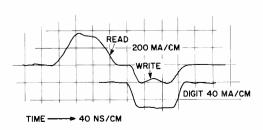

| The NS1-A New 400-nsec Microferrite Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58       |

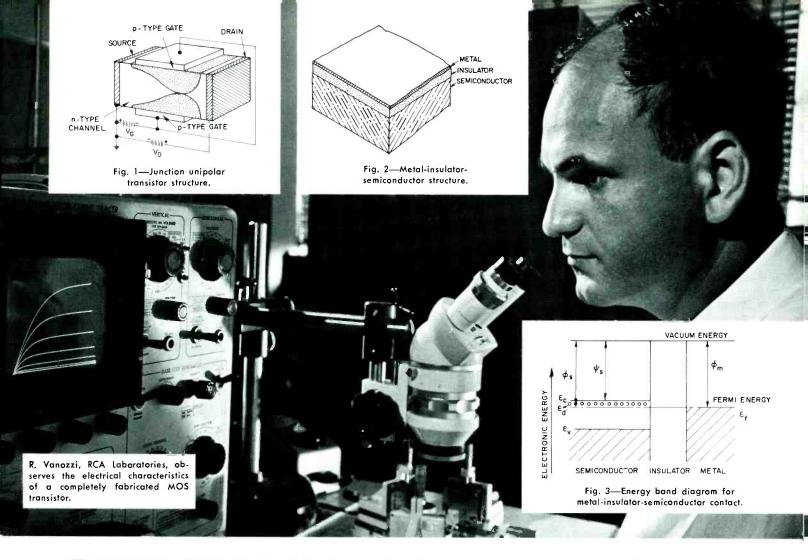

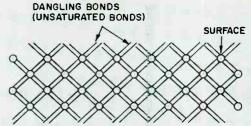

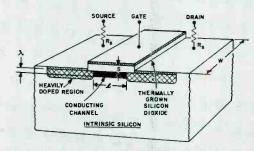

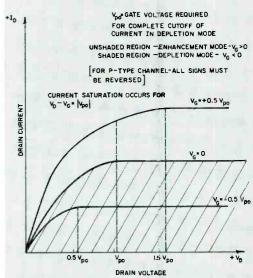

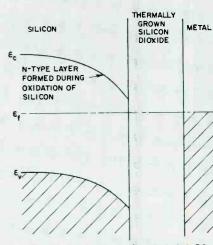

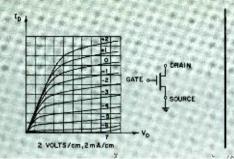

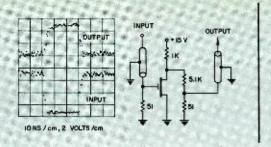

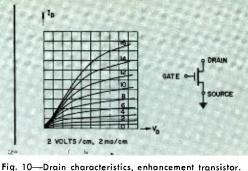

| The MOS (Insulated-Gate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| Field-Effect TransistorF. P. Heiman and S. R. Hofstein                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62       |

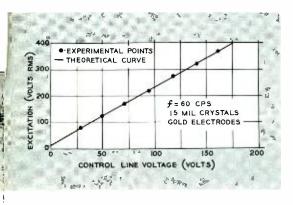

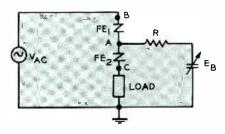

| Ferroelectric Decoding and Addressing for Solid-State DisplaysH. T. Gnuse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| A Geometrical Method to Investigate Dispersion Relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>.</b> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68       |

| A New GaAs Laser That Can Be Pumped ElectricallyDr. J. I. Pankove                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68       |

| Dynagroove—Electronic Compensation of Distortion in Stereo Disk Recordings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69       |

| Scopes New UHF CapabilityF. M. Carlson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69       |

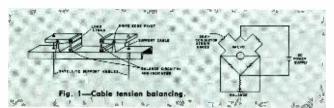

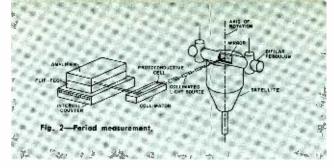

| A Precise Technique for Measuring Satellite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -        |

| Moments of Inertia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70       |

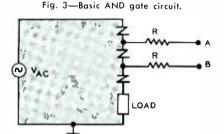

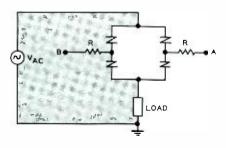

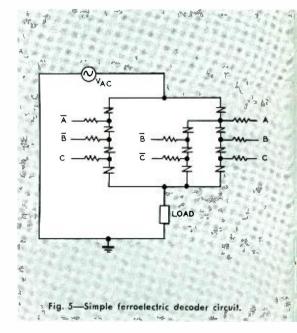

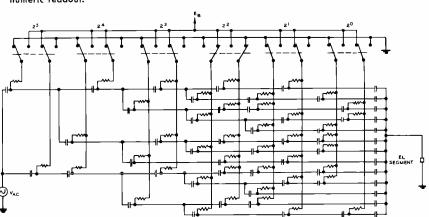

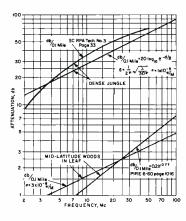

| HF and VHF Radio-Wave Attenuation Through Jungle and WoodsS. Krevsky                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7]       |