SPECIAL REPORT: AI BOOSTS THE IQ OF SILICON COMPILERS/54

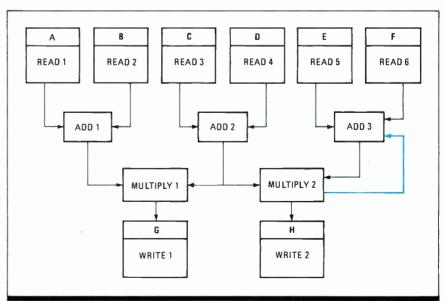

DATA-FLOW DESIGN OUTRUNS VECTORIZING MINISUPERS/64

## EECTO 1 CS

## While others talked "industry standard" only Mentor Graphics became one.

Just what *is* an "industry standard"?

Ask any three people and you'll likely get three very non-standard answers.

In the end, what matters most is that an industry standard be one that's widely accepted and used in the marketplace.

By this common sense definition, only Mentor Graphics can claim the industry standard in electronic design automation.

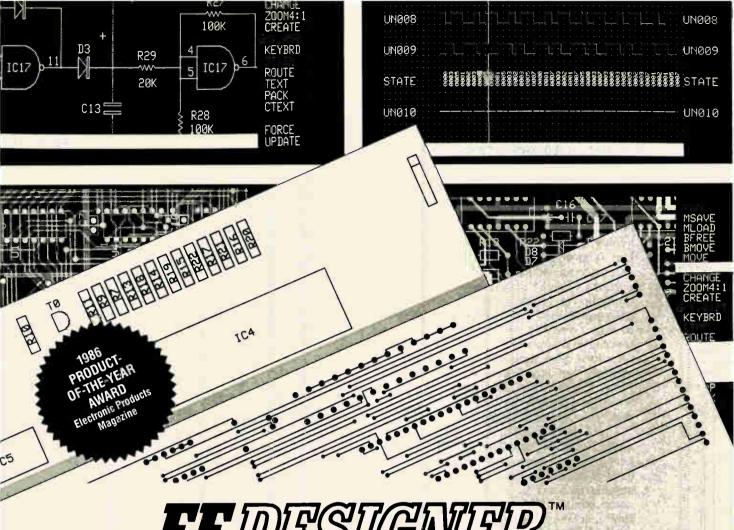

With over 6,000 installations throughout the world, the Mentor Graphics IDEA Series<sup>™</sup> is by far the most widely accepted of all electronic design automation systems.

More engineers use more IDEA Series design tools to develop more IC and PCB products than any other system. In fact, more than two thirds of our business comes from existing customers who are committed to the Mentor Graphics standard and are aggressively expanding their IDEA Series networks.

And our Apollo-based Series 3000 workstation is itself rapidly becoming a standard. With true 32-bit desktop processing, high-speed networking and a very

impressive cost per MIP, the Series 3000 has gained instant and enthusiastic acceptance throughout the engineering world.

Any true standard must embrace other existing standards to survive. And the Series 3000 workstation does just that. UNIX and an optional DOS card provide immediate access to a vast array of engineering tools. And an Ethernet option links you to the largest of network communications standards.

Best of all, we're an open standard. For instance, we give you an open database architecture, so you can easily integrate your applications with ours. The same goes for our Compute Engine global accelerator, which includes a complete set of software development tools.

In electronic design automation, only Mentor Graphics has become the standard that's more than just talk. Call us toll-free for an overview brochure and the number of vour nearest sales office.

Phone 1-800-547-7390 (in Oregon call 284-7357).

UNIX is a trademark of Bell Labs. Ethernet is a trademark of Xerox Corporation

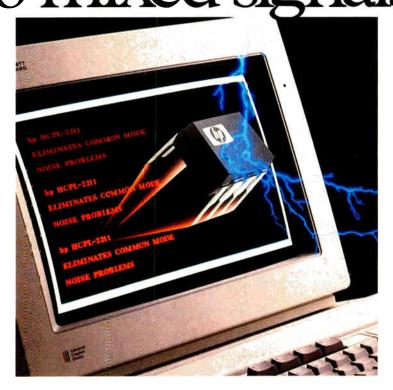

# SURPRISE! w you can put an end to mixed signals.

Put an end to erroneous data, false control signals and damaged circuits.

Introducing Hewlett-Packard's HCPL-2211 Very High Common Mode Rejection (CMR) Optocoupler. Its 5000V/µsec dv/dt rating allows the device to reject a 300 V spike, providing your expensive equipment and vital data 100 times the protection offered by our 6N137 coupler.

It's the smart way to buffer against lightning, cross-talk, inductive load switching, commutation

voltage spikes and other environmental voltage transients. The companion HCPL-2232 optocoupler offers dual channel protection in the same 8-pin package. Both are CMOS-compatible.

To order, call your authorized Hewlett-Packard components distributor. In the U.S.: Almac Electronics, Hall-Mark, Hamilton/Avnet, or Schweber. In Canada: Hamilton/ Avnet or Zentronics, Ltd. ■ Noisy environment (left)? Clean it up with HP's new HCPL-2211 Optocoupler (right).

| Try it! For a free sample HCPL-2211<br>Optocoupler, mail this coupon to:<br>Hewlett-Packard, Components Group,<br>1820 Embarcadero Rd.<br>Palo Alto, CA 94303. |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name                                                                                                                                                           |  |  |  |  |  |

| Title                                                                                                                                                          |  |  |  |  |  |

| Company                                                                                                                                                        |  |  |  |  |  |

| Address                                                                                                                                                        |  |  |  |  |  |

| City/State/Zip                                                                                                                                                 |  |  |  |  |  |

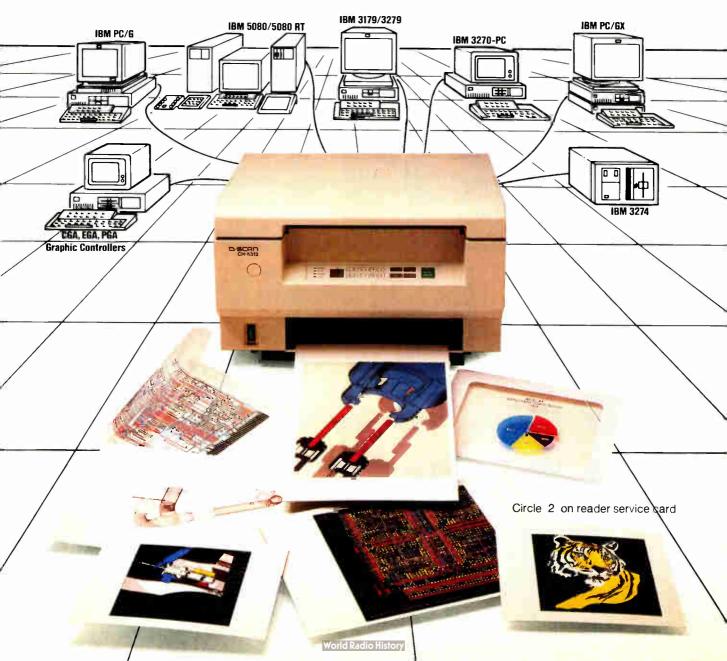

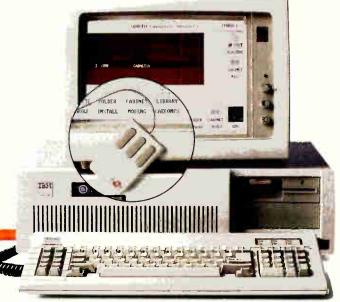

## IBM COPIES. 25¢ EACH.

For the first time, you can get high quality color hardcopy from all your IBM graphics systems. In a matter of seconds. For just a few pennies each.

For just a few pennies each.

The CH-5300 color hardcopier connects directly to your IBM hardware via our video interface. So you don't have to write any software. Plus you can connect up to four sources at one time.

Or network the CH-5300 on a 3274-controlled system.

controlled system.

With the CH-5300, you'll work with up to 4,912 colors (not just 8). And

you can count on seeing crisp, clean lines and smoothly shaded solids. So your screen images are accurately reproduced on every copy.

What's more, you'll get all this on paper or film. A or B size. In as little as

45 seconds.

So look into the Seiko CH-5300. You'll see the best IBM copies to come your way for just a quarter.

Call Martin Nelson at (408) 943-9100 today.

## **Electronics**

## **EDITOR-IN-CHIEF**

Robert W. Henkel

### **EXECUTIVE EDITORS**

Samuel Weber (technical), Arthur Erikson (news)

### MANAGING EDITORS GROUP

Bernard C. Cole, Lawrence Curran, Tom Manuel, Benjamin A. Mason, Jonah McLeod. Howard Wolff, Jeremy Young

## ART DIRECTOR

Fred Sklenar

### DEPARTMENT EDITORS

CAD/CAE: Jonah McLeod (San Mateo) Communications: Tom Manuel Components: Samuel Weber Computers & Peripherals: Tom Manuel Jonah McLeod (San Mateo) Lawrence Curran (Boston)

Industrial & Consumer: Wesley R. Iversen (Chicago)

Military/Aerospace: Ron Schneiderman Packaging & Production: Jerry Lyman Semiconductors: Bernard C. Cole (San Mateo) Software & Microprocessors:

Alexander Wolfe Test Instruments: George Sideris (San Mateo)

### NEWS DEPARTMENT

Features Editor: Jeremy Young Front of the Book: Howard Wolff New Products: Jack Shandle

## **EDITORIAL PRODUCTION & COPY DESK**

Benjamin A. Mason (Director)

### Production Charles D. Ciatto (Mgr.), Kathy O'Neill

## Copy Editors

Larry King (Chief), George Ellis, Nancy J. Erickson

## ART

Karla Tonning (Associate Director)

## **NEWS BUREAUS**

Boston: Lawrence Curran (Mgr.), Paul Angiolillo Chicago: Wesley R. Iversen (Mgr.) Dallas: J. Robert Lineback (Mgr.)

Los Angeles: Larry Waller (Mgr.), Ellie Aguilar New York: Tobias Naegele (Mgr.) San Mateo: Clifford Barney (Mgr.)

> Frankfurt: John Gosch (Mgr.) London: Steve Rogerson

### Paris

Tokyo: Charles L. Cohen (Mgr.), Ayako Hayashihara

### **EDITORIAL ADMINISTRATION**

Laura Aspery (Administrative Assistant), Lisa Costenbader, Ina Gruber

## PUBLISHER

Laurence Altman

Director of Operations: Thomas E. Vachon Director of Circulation: Daniel McLaughlin Production Director: Thomas Egan Manager of Sales Administration:

Evelyn Schmidt Promotion Associate: Diane Breder

f you want to get a fix on just how times have changed in the electronics industry, think back to a decade ago and try to remember how many articles about software appeared in any issue of Electronics. The answer is: not very many.

Now take a look at the contents page of this issue. There are no less than three Technologies to port based on software can stick to engineering. developments that will

The four articles come from CAD/ CAE editor Jonah McLeod. He observes that their common thread, and the dominating trend in the entire field of IC design, is that the mundane, clericaltype work now is handled by the work station.

"The software is taking over a lot of the routine functions that the designer of hardware used to have to do manually. Before, you had the designer working on Mylar plots of an IC with strips of rubylith to create masks—that is, to produce the chip. This work literally required months, and in some cases years for a complex chip," says Jonah.

"But the funny thing is that none of that stuff had anything to do with engineering; it was drafting. Now all of those jobs are done automatically, and the engineer can do engineering. He's

Watch and a Special Re- McLEOD: Now the engineers work. Back in the old

back to doing the things that he really enjoys, the things that led him into engineering in the first place."

Then there's the other half of the chip-design story in which software has wrought such massive change: the test function. Says Jonah, "On the test side, the story is equally interesting. Say you produce a chip and it doesn't days-which were really just a few years ago-it

meant pulling out the paper versions of those good old Mylar plots and laboriously looking for points on the plot.

"I recall seeing it many times when I visited companies and was being taken through the design and test labs. There would be this poor engineer with a microscope tediously and laboriously staring at a chip that was perhaps 100 mils on a side, and behind him on the floor would be a 6-ft exploded view on paper of that chip.

'All he wanted to do was find a polygon in that morass to pinpoint the error," says Jonah. "But he was forced to spend hours and days bent over the chip and searching the paper plot looking for his clues.

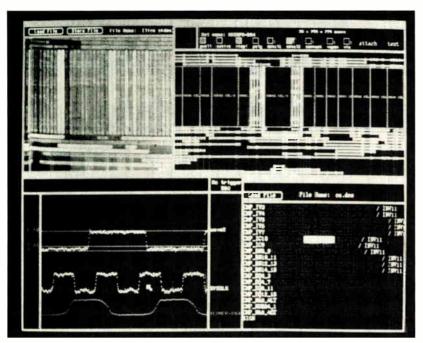

"Then along came the Sentry machine [described in this issue's cover story]. Now all the designer has to do is tell the computer where he wants to probe on the chip, and the system does the rest."

Where is all this leading? In Jonah's view, "We're really just starting out in this area of design software. There's a lot more still to be done, which in my view makes it one of the most exciting frontiers in electronics.'

April 30, 1987 Volume 60, Number 9 138,668 copies of this issue printed

April 30. 1981 - volume 64. number 9

138.682 copie so this issue printed

Electronics (ISSN 0883-4899). Published biweekly by McGraw-Hill Inc.

Publication office: 1221 Avenue of the Americas, N.Y. N.Y. 10020; second class postage paid at New York, New York and additional maling offices. Postage paid at Montreal, P.O. Registration Number 9034.

Executive, editorial, circulation, and advertising addressess: Electronics, McGraw-Hill Building, 1221 Avenue of the Americas, New York, N.Y. 10020 Telephone (212) 512-2000. Telephone 127960 TWX 710-581-4879. Cable address: M.C.G. A.W. H.I.L. N. E.W. Y.O. R. Freildent: Richards McGraw-Hill Information Systems Company; "Frederick P. Jannol, Construction Information Group, Informas Pyain, Markeling and International. Senior Vice Presidents: Publishers: Laurence Altman, Electronics, Harry I. Brown, BYTE; David J.McGrath, Engineering News-Record Group Vice President: Peter B. McCuen, Communications information Group Communications information Group Communications information Vice Presidents: Robert D Daleo, Controller, Fired O. Jensen, Planning and Developmant, Michael J. Koeller, Human Resources; Talat M. Sadig, Systems Planning and Technology.

Officers of McGraw-Hill Inc.: Harold W. McGraw Jr., Charman; Joseph L Dionne. President and Chief Executive Officer; Robert N Landes, Executive Vice President and Secretary, Watter D Serwatka, Executive Vice President and Chief Financial Officer; Shel F Asen, Senior Vice President, Manufacturing; Robert J. Bahash, Senior Vice President, Editorial, George R Elsinger, Vice President, Circulation, Ralph J. Webb, Vice President and Treasurer.

Title registered in U.S. Patent Office, Copyright 1987 by McGraw-Hill Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of copyright owner. Where necessary, permission is granted by the copyright owner for libraries and others registered with the Copyright Clearance Center (CCC), 21 Congress Street, Salem, Mass. 01970, to photocopy any article herein for the base fee of \$0.50 per copy of the article plus \$0.25 per page Payment should be sent directly to the CCC. Copying done for other than personal or internal reference use without the express permission of Uniform Vice President Programment Should be sent directly to the CCC. Copying done for other than personal or internal reference use without the express permission of Uniform Vice President Programment Should be sent directly to the CCC. Sopying done for other than personal or internal reference use without the express permission of Uniform Vice President Programment Should be sent directly to the CCC.

Editorial department phones: Administration (212) 512-2645, News and New Products (212) 512-2685, Technology (212) 512-2666. Bureaus: Boston (617) 262-1160, Chicago (312) 751-3811, Dallas (214) 458-2400, Los Angeles (213) 480-5234, New York (212) 512-3322, San Francisco/San Maleo (415) 349-4100, Washington (202) 463-1650, Frankfurt 72-5566, London 493-1451, Paris 42-89-03-80, Tokyo 581-9816. Business departments: (212) 512-6435 (Business departments follow the Advertisers' Index).

## Electronics

## **NEWS**

### **Newsletters**

## Electronics, 21

- Trade-war fears and computermarket recovery boost chip sales

- GE/RCA is about to jump into digital signal processing

- National slices turnaround time to two weeks for prototype ROMs

## International, 49

- Will U. S. tariffs prompt Japan to flood European markets?

- The EC is investigating charges that Japan is dumping EPROMS

- S-VHS—latest entry in the VCR wars—hits the Japanese market

## Memories, 31

SRAM makers crowd into the cache-tag memory niche

## Careers, 32

Inflation continues to cut into the pay gains of EEs

## Manufacturing, 32

The chemical-vapor-deposition market gets an explosive new entry from Applied Materials

## Communications, 33

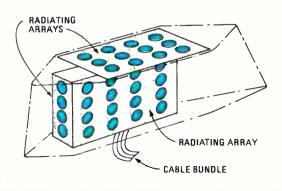

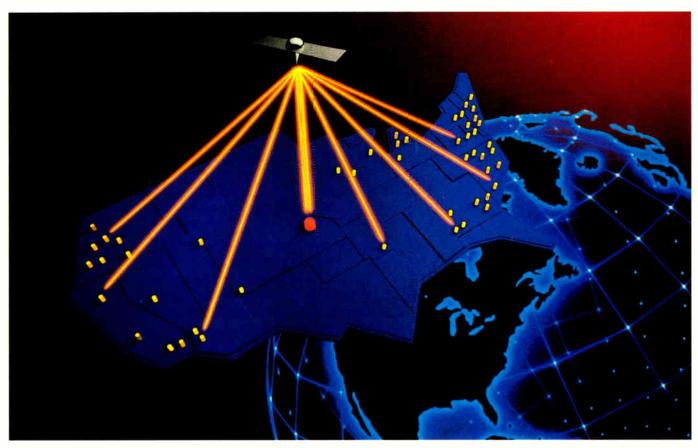

Jetliners soon will get satellite antennas

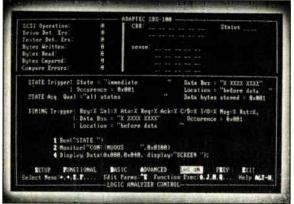

## **Development systems, 34**

Emulation system makes it easy to debug SCSI systems

## Power supplies, 34

Look out, Yanks! Here come the British power-supply makers

## Speech processing, 38

Coming from Europe: a system for real-time dialog

## Displays, 39

How Britain's STC is boosting LCD resolution and sharpness

## INSIDE TECHNOLOGY

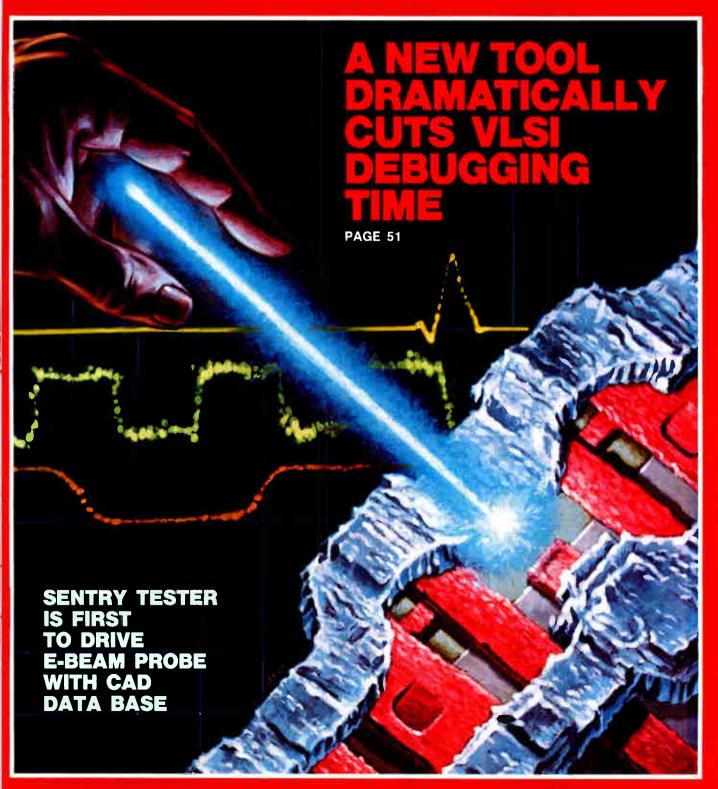

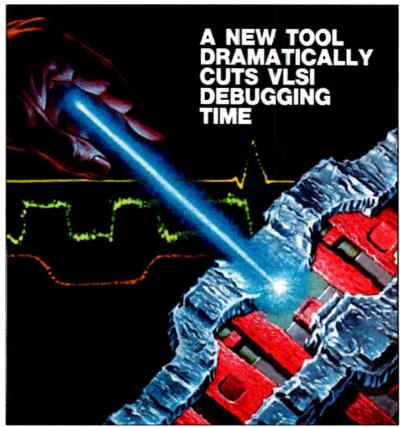

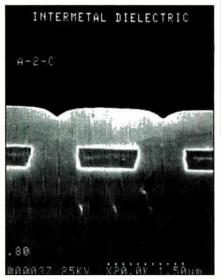

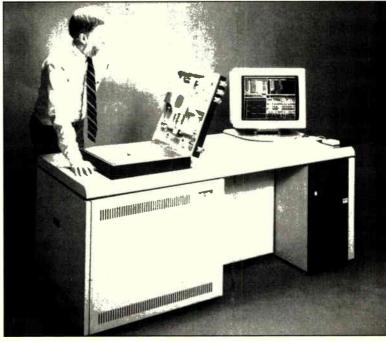

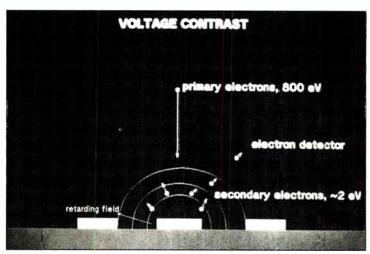

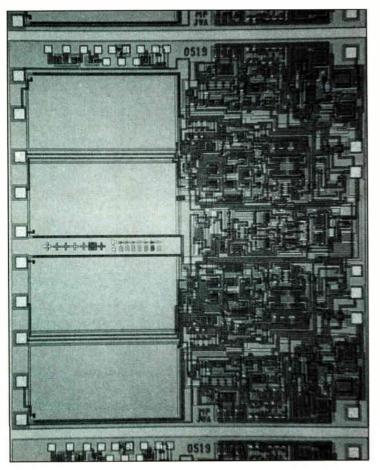

## COVER: A new tool dramatically cuts VLSI debugging time, 51

Sentry Schlumberger's IDS 5000 integrates E-beam probing with CAD/CAE tools. It marries netlists, layout, and oscilloscope with a 'live' microscopic image of the chip

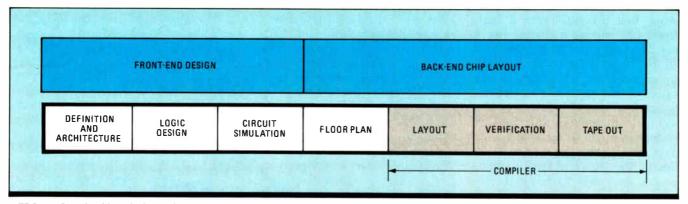

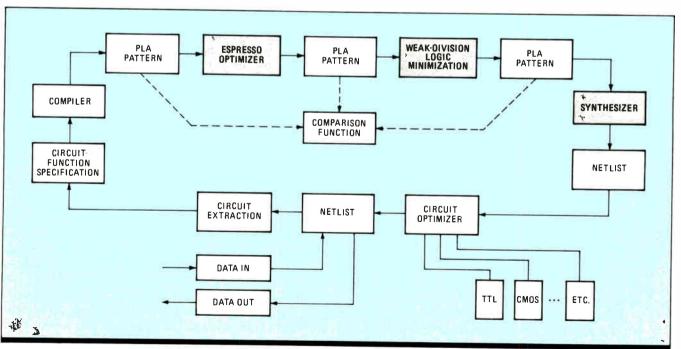

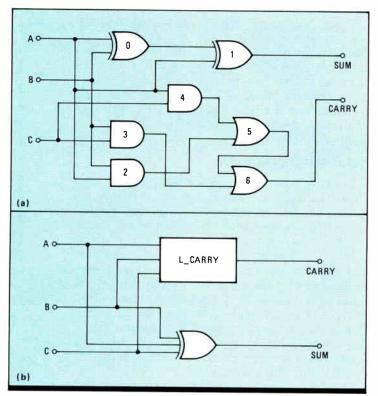

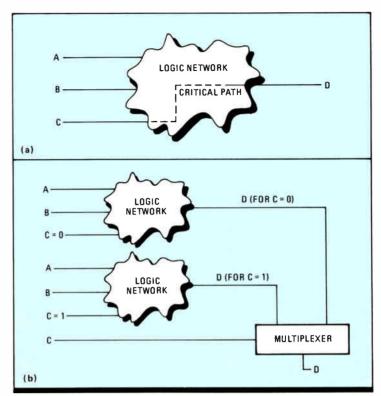

## SPECIAL REPORT: Al boosts the IQ of silicon compilers, 54

With artificial-intelligence techniques, silicon compilers are about to deliver the promise of automating most of the chip-design process

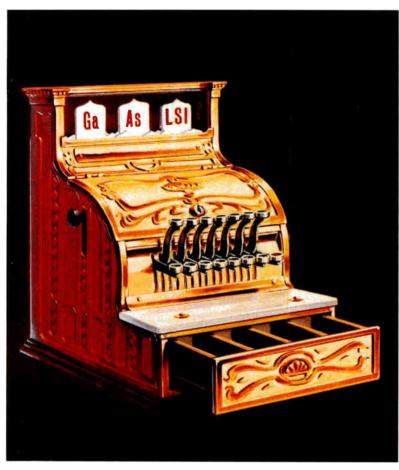

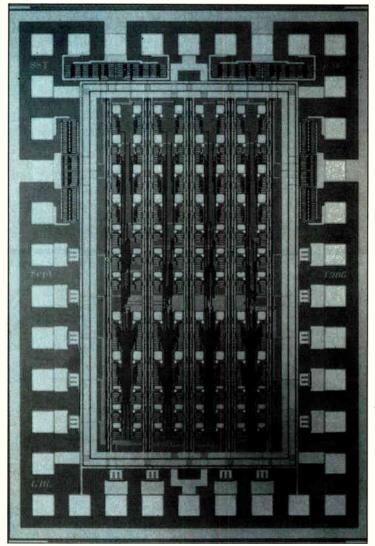

## The first GaAs compiler is already producing chips, 58

Seattle Silicon and Gigabit Logic team up to produce a compiler that can handle different logic types and can migrate to future geometries

## Now designers can skip floor-planning details, 61

A new tool from VLSI Technology automates the back-end IC design task of placement and routing of macro cells and standard cells

## This new design outruns vectorizing minisupercomputers, 64

Cydrome's Cydra 5 modified data-flow architecture can achieve three to four times the sustained performance of a vector-processing minisuper

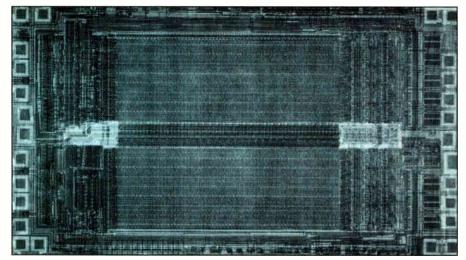

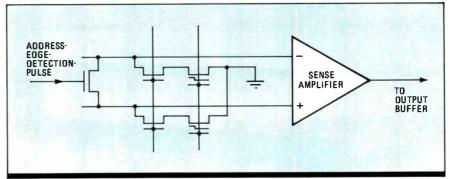

## Fast control stores can now use EEPROMs, 66

With 25-to-35-ns access times, Seeq's CMOS 16- and 32-Kbit EEPROMs rival bipolar PROMs and outspeed EPROMs in writable control stores

## Pyramid adds RISC to parallel processing, 68

Fast RISC processors in a shared-memory multiprocessing architecture boost Pyramid's 9800 series up to 25 mips

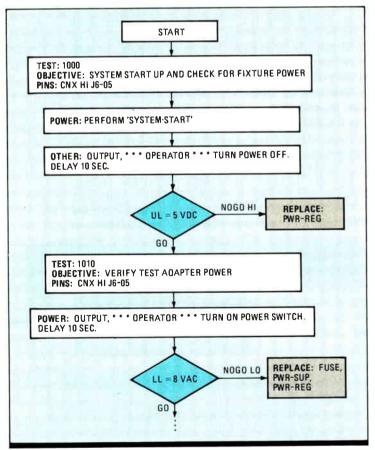

## PC AT-based tester cuts cost of military ATE, 69

Summation's hardware and TYX's software meet in the IBM PC AT-based Summation Atlas Test System for military ATE

## Summation bets on PC-based testers, 71

Now the three-year-old company is going for the military market

## Technology update, 72

Tandem VLX racks up nonstop sales . . . Now Lasarray is set for a brisk year

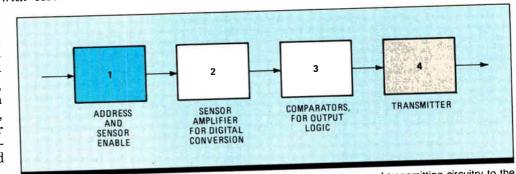

## Smart sensors will help cut wiring that clogs systems, 73

Micro Switch's application-specific sensors interface with any bus protocol and help reduce the maze of wiring in cars, buildings, and aircraft

## PROBING THE NEWS

## Intellectual property turns into high-priced real estate, 43

Chip makers are getting aggressive about raising the return on their patents—and they're more reluctant to sign second-source pacts

## Custom IC Conference looks like a real winner, 45

It will unveil a wide range of denser, speedier gate arrays and tools that promote faster design turnaround

COVER: JOEL NAPRSTEK

PAGE 51

## **NEW PRODUCTS**

## Newsletter, 25

- Telebit designs a 2,400-baud modem from off-the-shelf parts

- Standard Microsystem's controller cuts chip count on interface boards for IBM minis

- Software cuts test-development time for processor boards by 80%

## Semiconductors, 80

- A single NCR chip supports three IBM Personal Computer graphics formats and integrates a CRT controller

- GE/RCA's operational amplifiers provide guaranteed 5-V specifications over the full military temperature range

## Computers & Peripherals, 82

- Data Translation's frame grabber for the IBM PC/AT costs only \$1,600 and handles 30 frames a second

- Two new Tandem computers one running Unix—target the low end of the on-line transactionprocessing market

- Wang's new desktop image processing systems integrate text and graphics

## Military/Aerospace Newsletter, 77

- Avionics work for the new Air Force fighter will cost \$900 million over five years

- GTE now wants to sell its Arizona semiconductor facility

- The Pentagon is jumping on the superconductor bandwagon

## **DEPARTMENTS**

## Publisher's letter, 3

Here's one magazine that moves with the times: 10 years ago, any software article was a rare bird; this issue has three Technologies to Watch and a Special Report based on software developments

### FYI, 8

Americans usually don't have a good understanding of the way that the Japanese do business; partly because of this, only 1 in 25 U.S.-Japanese negotiations ever succeeds

## People, 12

Why Data General's Robert Miller went to MIPS Computer Systems

## **Electronics Week, 90**

- Two Fairchild fabs go on the block

- Norway will install a huge fiberoptic net, based on components from a U. S. company

- Apollo takes on Inference's expert-system development tool

- TI sees 14% growth this year for worldwide semiconductor market

## GE/RCA HC: Your clear path

## into the world of CMOS.

## Only GE/RCA has the broad line, unique parts and 25 years of CMOS experience to support you every step of the way.

Your venture into the world of high-speed CMOS can be very rewarding—if you travel with the right CMOS partner.

## A logical first step.

We have been the leader in CMOS logic for more than two decades.

We pioneered with the 4000 series and followed with high-speed CMOS and ACL.

Today, we have more than 270 highspeed CMOS devices. And that number is growing fast, because every time we make a new HC device (and we have the industry's broadest line), we make the corresponding part in HCT, too.

## A design engineer's dream.

This broad line includes quite a few unique parts (for a sample, see the box below). And we have extensive experience in High-Rel, ASICs, memories and microprocessors, so we can help you get the most possible from this outstanding technology.

## And a purchasing agent's, too.

There's more to good CMOS than good design. We have a track record of delivering competitively-priced parts on time. And we've invested millions of dollars to provide the production capacity and leading-edge technology you need.

Add to this a record for reliability that has truly withstood the test of time (after all, we invented CMOS), and you'll see why so many people have started successful journeys into CMOS with GE/RCA at their side.

Take a big step in the right direction, and call toll-free 800-443-7364, ext. 15. Or contact your local sales office or distributor.

## Our unique high-speed CMOS analog switches are among the highest frequency, lowest distortion devices available today.

## HC/HCT4016, 4066, 4316

- Low Ron, 125 ohm typically (4016, 4316),

25 ohm typically (4066), Vcc=4.5V.

Frequency response of -3db down @ 180 MHz (4016, 4316), -3db down @ 200 MHz (4066), both driving a 75 ohm load.

- Low distortion

- Maximum control switching frequency to 35 MHz.

- Low "OFF" leakage current.

- Applications: Instrumentation, Direct Current to 50 MHz Switching Systems, Cable TV, Workstations.

## HC/HCT4051, 4052, 4053, 4351, 4352, 4353

- Wide analog input voltage range: ±5.5V max.

Low "ON" resistance: 70 ohm typ (Vcc-Vee = 4.5V),

- 40 ohm typ (Vcc-Vee = 9V)

- Low crosstalk between switches.

- Fast switching and propagation speeds.

- "Break-before-make" switching.

- Applications: Audio and Video Switches, Synch. Detection, Video Mixing, RF Frequency Switching, Data Multiplexing, Data Conversion, Data Transmission.

## Our Phase-Locked Loop devices offer greater speed and linearity than any other CMOS PLL's...plus low power consumption.

## HC/HCT4046A

- Operating frequency range up to 17 MHz (fc) at

- Built-in op amps for excellent linearity.

- Op-amp buffered demodulated output. 3 phase comparators to choose from.

- Applications: FM Modulation/Demodulation, Frequency Synthesis, Frequency Multiplexing, Voltage to Frequency/Frequency to Voltage Conversion, Servo Control Systems, Data Synchronization, Manchester Coding/Decoding.

## **HC/HCT7046**

- Operating frequency range up to 17 MHz (fc) at Vcc=4.5V

- Built-in op amps for excellent linearity.

- Op-amp buffered demodulated output.

- A pin which indicates lock detect.

- 2 phase comparators to choose from.

- Applications: FM Modulation/Demodulation, Frequency Synthesis, Frequency Multiplexing, Voltage to Frequency/Frequency to Voltage Conversion, Servo Control Systems, Data Synchronization, Manchester Coding/Decoding.

WHEN YOU CAN TAKE ADVANTAGE OF OUR HIGH PERFORMANCE. NO RISK 8000 SERIES, ENHANCED FOR THE DEMANDS OF MODERN TECHNOLOGY

## FEATURING:

- BLAZING SPEED 6 MHz CA80C85B CPU 10 MHz Peripherals

- VERY LOW POWER CMOS

- PIN AND FUNCTIONAL REPLACEMENT FOR NMOS

- FULL TTL COMPATIBLE

## No RISC

## BENEFITS IN:

- SHORTER DESIGN CYCLES

- REDUCED PROJECT COST

- EXTENSIVE HARDWARE AND SOFTWARE SUPPORT

- APPLICATIONS FLEXIBLITY

**CA80C85B**

CA82C37A CA82C54

CA82C59A CA82C52

CA82C55A CA81C55

CA82C84A CA82C88

CA82C12 CA01C50

FROM:

Calmos Systems Inc.

USA: Call 1-800-267-7231 Europe: UK (0272) 277332 Canada: (613) 836-1014

Tlx: 053-4501 Tlx: 449731

TIx: 053-4501

Americans usually don't have a good understanding of the way the Japanese do business; partly because of this, only 1 in 25 U.S. - Japanese negotiations ever succeeds

s the one-world electronics industry Agets closer and making it depends on a company picking the right strategic alliance or partner, more and more U.S. managers will have to deal with their Japanese counterparts. Yet most Americans are often at a distinct disadvantage in negotiating such deals. While the Japanese have been "U.S.watching" for decades, Americans usually don't have a good understanding of the Japanese way of doing business. In fact, Eugene L. Mendonsa, senior vice president at Red Bluff, Calif.'s, Interna-

tional & Domestic Negotiating Institute, estimates only 1 in 25 American-Japanese negotiations ever succeeds. Even though the Japanese may like a business proposition, they won't sign if they don't like the way the U.S. negotiator talks or behaves. Certain core values rule Japanese perception, thought, and behavior, Mendonsa says, and four key concepts form the foundation of their manners and ethics in business:

1. Amae (pronounced ah-my) means "indulgent love" and is most important. All relationships are based on it; concern for another pervades most Japanese relationships: one should do nothing to cause the other to lose face. This makes negotiating difficult for the Japanese, and a U.S. businessman should do everything he can to establish a personal, trusting relationship. Without Amae, the Japanese will not feel comfortable or "right" and will move more slowly than usual.

2. Shinyo (sheen-yoe) is "gut level" trust, a necessary faith that the other person won't cause any harm. The Japanese are hesitant to enter into any relationship without this trust. In the early stages of any negotiation, the U.S. executive should try to convey shinyo. The Japanese will be far more impressed by the good feeling than by sterling logic and data.

3. Enryo (in-ree-oh) is a feeling of distrust leading to interpersonal distancing. When the Japanese don't feel close to another person, they practice enryo to avoid conflict. Conveving a good feeling is all the more important for foreigners because the Japanese automatically practice enryo with them.

4. Giseisha (ghee-say-e-sha) means "victim syndrome;" the Japanese seem easily insulted. When they are thwarted from having their way, they take it as a personal insult and take revenge. Even an inadvertent insult can damage a long-term business relationship. And it can go beyond that. An insulted Japanese manager could even blacklist an American and make it difficult for him to do business in Japan. ROBERT W. HENKEL

Lightning speed, pin-point accuracy

## INTEGRATED CHIPS - INCREASED PERFORMANCE LESS COMPONENTS - LOWER COSTS

Design IBM PC XT/AT or IBM compatible systems with a higher speed, increased reliability and improved performance while at the same time reducing board size, lower power consumption and reducing costs. Reach this goal by using UMC integrated chip sets UM82C286, UM82C287 and UM82C086 and fully compatible offering many advantages over comparable products.

As a fully integrated chips, the UM82C286 performs the functions of 19 components; the UM82C086 those of 31, and the UM82C287 those of 35 components. These Integrated chips allow production costs to be cut. A reduced board size

gives structural latitude, less power consumption means longer life; advantages that make systems incorporating them extremely competitive.

These savings combine with increased speed, reliability and performance to make this family of UMC integrated chips most attractive to system designers. Thus, the 82C286/7 allows 100 ns of DRAM in a chip set that permits a selection between a one-wait system (12 MHz) or a zero-walt system (10 MHz). the 82C086, on the other hand provides a flexibility that permits the governing of a 4.77 MHz system for the PC-XT, or an 8 MHz system for the PC-TURBO.

For your IBM PC XT/AT requirements choose UMC. For all other system requirements also choose UMC.

For details, please call us today.

U.S.A. HEADQUARTERS:

NMC CORPORATION

3350 SCOTT BLVD, BUILDING #57 SANTA CLARA, CA. 95054 U.S. TEL: 408-727-9239 TLX: 172730 NMC SNTA FAX: 408-9700548

Circle 9 on reader service card

Other ASIC companies brag about how many gates they can pack into an array. Or how much logic they can cram on a PLD.

They think it's a big deal if they can shrink 3 boards down to 3 chips.

Let's get serious.

VLSI nails the competition to the wall.

Our tools let you build a chip

so far ahead of anybody else's they won't know what hit them.

A single chip with logic, memory, processors, and peripherals.

And you'll do it faster than you ever thought possible.

Wang, Tandy, and over seventy other leading companies have already used our tools to build hundreds of chips.

Everything from gate arrays to

megacells to compiled silicon.

NCUBE developed a chip with over 160,000 transistors that requires no glue logic because the processor, communication logic, and all interface logic are integrated on one chip.

What good is a tool set without nuts and bolts?

Our cell libraries are compatible since they're produced in the

same  $2\mu$  CMOS. So you can even combine standard cells, megacells, and compiled cells on a single chip.

You can expect chips designed with our tools to work the first time in your system.

You can use them with Apollo, DEC VAX™ and MicroVAX, Elxsi, HP 9000 Series 300, Mentor, Ridge, Sun, you name it.

And whether you buy them, lease them, or use them at our design centers, our ASIC team will support you all the way.

If you want the right ASIC solution to your problem, talk to the only place that has them all: Tools. Programmable logic. Gate arrays. Standard cells. Megacells. Compiled silicon. And a complete fabrication facility.

Call VLSI at 408-434-3100. Or write to us at 1109 McKay Drive, San Jose, CA 95131.

And start hammering away at your competition.

Looking

for

Career

Advancement

Turn

to

Electronics'

Career

**Opportunities**

Section.

See the

index

for

location.

**PEOPLE**

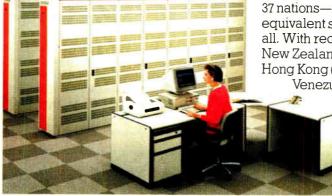

## WHY DG'S MILLER WENT TO MIPS COMPUTER

BOSTON

senior vice president at Data General Corp. who also has 15 years of experience at IBM Corp. under his belt is the kind of quarry that computer-industry headhunters love to bag. Little wonder, then, that Robert C. Miller, who fits that description, had several "career opportunities" dangled before him during his six years at the Westboro, Mass., computer maker. But only one seemed worth taking—the chance to become president, chief executive officer, and chairman of MIPS Computer Systems Inc. of Sunnyvale, Calif.

"It's always been a dream of mine to run my own company," says the 43year-old Miller. He headed Data General's Information Systems Group, which accounted for revenues of \$1.2 billion in 1986, until he signed on with MIPS in mid-April. "To find one that played to my interests like MIPS is truly a rare opportunity."

MIPS, a private company formed in 1984, was the first firm to specialize in reduced-instruction-set-computer technology [Electronics, April 29, 1985, p. 36]. It remains as perhaps the only company dedicated to a pure RISC approach. Its product line includes commercial versions of a RISC chip originally developed at Stanford University, plus board-level products, a component kit, optimizing compilers, and a development system built around that chip.

The RISC technology was one reason Miller accepted the MIPS offer. The company's location, in Palo Alto, Calif., also played a role, as did the opportunity to head "a team that has real class." He also likes MIPS' use of Unix.

**DONE RIGHT.**' Miller earned a master's degree in thermodynamics from Stanford, which is in Palo Alto. "When I left there 20 years ago, I promised myself I'd go back. And when the people at MIPS took me through the architecture of the RISC processor, I could see that these fellows had done it right. They've moved the state of the art quite a bit forward," he contends. "These fellows" include John Hennessey, who pioneered in RISC when he designed the experimental chip at Stanford that MIPS is now selling. He remains at MIPS as chief scientist and now heads a Stanford research project aimed at developing an advanced version of the chip for the Defense Advanced Research Projects Agency.

Miller declines to discuss that effort until he's more familiar with it, but he's quite vocal about Unix and RISC. He's

**MILLER.** MIPS gave him an opportunity he says he simply couldn't overlook.

convinced that RISC processors will be the dominant Unix platform for the 1990s. "Forecasts for the Unix market in the next decade are in the billions of dollars, and I believe this processor [and Unix] will be to the '90s what PC/DOS is to the '80s," Miller predicts.

"I was convinced a few years ago that Unix was going to be an exciting part of the business," he continues. "To think about a processor board that runs at 8 mips at no cost premium versus a 68020-based board is especially exciting. We'll need to keep driving the performance up to realize high-function work stations and servers."

For now, Miller sees MIPS' current CMOS as the most cost-effective implementation for RISC architectures. But he anticipates opportunities for emitter-coupled logic in applications where users will pay a premium for speed.

Miller is joining a company that acting chairman Donald Muller says is aimed at becoming the dominant supplier of RISC-based products. MIPS has backing from some of Silicon Valley's top venture firms, including the Mayfield Fund and Kleiner Perkins Caufield and Byers, San Francisco. The company has already sold Unix-based RISC platforms to several original-equipment manufacturers, including Prime Computer, Silicon Graphics Computer Systems, and Racal-Redac. All in all, Miller concludes, "I couldn't overleok this opportunity."

-Lawrence Curran

## TOSHIBA. NOW, 1 MB DRAMS

AREA SALES OFFICES: CENTRAL AREA, Toshiba America, Inc., (312) 945-1500; EASTERN AREA, Toshiba America, Inc., (417) 272-4352; NORTHWESTERN AREA, Toshiba America, Inc., (408) 244-4070; SOUTHWESTERN REGION, Toshiba America, Inc., (714) 752-0373; SOUTH CENTRAL REGION, Toshiba America, Inc., (214) 480-0470; SOUTHEASTERN REGION, Toshiba America, Inc., (404) 493-4401; MAJDR ACCOUNT OFFICE, PDUGH-KEEPSIE, NEW YORK, Toshiba America, Inc., (415) 952-0363; SOUTH CENTRAL REGION, Toshiba America, Inc., (305) 394-3004 REPRESENTATIVE OFFICES: ALABAMA, Montgomerry Marketing, Inc., (205) 830-0498; ARIZONA, Summit Sales, (602) 998-4850, ARKANSAS, MIL-REP Associates, (512) 459-8682; CALIFORNIA (Northern) Elrepco, Inc., (415) 962-0660; CALIFORNIA (A & Orange County) Bager Electronics, Inc., (818) 712-0011, (714) 957-3367. (San Diego County) Eagle Techrica: Sales, (519) 743-3555, COLORADO, Straube Associates Mountain States, Inc., (303) 426-0890; CONNECTICUT, Datacom, Inc., (203) 288-7005, DISTRICT OF COLUMBIA, Arborek (301) 825-0775, FLORIDA, Sales Engineering Concepts (305) 426-4601, (305) 682-4800; GEDRGIA, Montgomerry Marketing, Inc., (404) 447-6124, IDAHD, Components West, (509) 922-2412; ILLINDIS, Carlson Electronics, (316) 744-1229; KENTUCKY, Lesie M. DeVoc Company, (317) 842-3245; IDWA, C.H. Horn, (319) 338-3703; KANSAS, D.L. E. Electronics, (316) 744-1229; KENTUCKY, Lesie M. DeVoc Components Sales, (313) 349-3940; MINNESOTA, Electric Component Sales, (612) 933-2594; MISSISSIPPI, Montgomerry Marketing, Inc., (205) 830-0498; MISSOURI, D.L.E. Electronics, (316) 744-1229;

## FIRST AGAIN. AND 256 K CRAMS.

Toshiba technology leads the way again with the development of Ultra Large Scale memory devices that feature high speed access times.

## **1 MB CMOS DRAMS**

TOSHIBA is delivering now . . . all the 1Mb product you can use. In three different access modes. With speeds of 85, 100 and 120 ns. You have a choice of fast page mode,

static column or nibble mode. And you can get production quantities now.

| TOSHIBA 1 Mb DRAMs |              |         |        |               |         |  |

|--------------------|--------------|---------|--------|---------------|---------|--|

| Part Number        | Organization | Process | Speed  | Mode          | Package |  |

| TC511000 - 85      | 1 Mb x 1     | CMOS    | 85 ns  | Fast Page     | 18 pin  |  |

| TC511000 - 10      | 1 Mb x 1     | CMOS    | 100 ns | Fast Page     | 18 pin  |  |

| TC511000 - 12      | 1 Mb x 1     | CMOS    | 120 ns | Fast Page     | 18 pin  |  |

| TC511001 - 10      | 1 Mb x 1     | CMOS    | 100 ns | Nibble        | 18 pin  |  |

| TC511001 - 12      | 1 Mb x 1     | CMOS    | 120 ns | Nibble        | 18 pin  |  |

| TC511002 · 10      | 1 Mb x 1     | CMOS    | 100 ns | Static Column | 18 pin  |  |

| TC511002 · 12      | 1 Mb x 1     | CMOS    | 120 ns | Static Column | 18 pin  |  |

| TC514256 · 10      | 256K x 4     | CMOS    | 100 ns | Fast Page     | 20 pin  |  |

| TC514256 - 12      | 256K x 4     | CMOS    | 120 ns | Fast Page     | 20 pin  |  |

| TC514258 - 10      | 256K x 4     | CMOS    | 100 ns | Static Column | 20 pin  |  |

| TC514258 · 12      | 256K x 4     | CMOS    | 120 ns | Static Column | 20 pin  |  |

## **256K CMOS STATIC RAM**

Toshiba's product development leadership continues. We were first with 16K CMOS RAMs.

First with 64K CMOS RAMs. And now first again—with 256K CMOS static RAMs. This 32K x 8 device features the lowest power consumption available today—only 5mA/MHz. Lower than any competitive product. And we offer speeds to 100 ns.

| TOSHIBA 256K CRAMs |              |         |        |               |         |  |  |

|--------------------|--------------|---------|--------|---------------|---------|--|--|

| Part Number        | Organization | Process | Speed  | Standby Power | Package |  |  |

| TC55257A - 10      | 32K x 8      | CMOS    | 100 ns | 1mA MAX       | 28 pin  |  |  |

| TC55257A - 12      | 32K x 8      | CMOS    | 120 ns | 1mA MAX       | 28 pin  |  |  |

| TC55257AL - 10     | 32K x 8      | CMOS    | 100 ns | 100%A MAX     | 28 pin  |  |  |

| TC55257AL - 12     | 32K x 8      | CMOS    | 120 ns | 100%A MAX     | 28 pin  |  |  |

(Now available in Plastic Flat Pack.)

## **ULTRA LEADERSHIP**

Again Toshiba leads the way. With high speed access times. Now with Ultra Large Scale products. With ultra high quality. With ultra fast deliveries. Toshiba. The power in memories.

TOSHIBA. THE POWER IN MEMORIES.

TOSHIBA AMERICA, INC.

1986 Toshiba America, Inc

MONTANA, Components West, (206) 885-5880; NEVADA, Eirepco, Inc., (415) 962-0660; NEW ENGLAND, Datcom, Inc., (617) 891-4600; NEW HAMPSHIRE, Datcom, Inc., (617) 891-4600; NEW JERSEY, Nexus-Technology, (201) 947-0151; NEW MEXICO, Summit Sales, (602) 998-4850; NEW YORK, Nexus Technology, (201) 947-0151; Pi-tronics, (315) 455-7346; MORTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/SOUTH CAROLINA/MIL-REP Associates, (212) 646-6731; NORTH OAKOTA/SOUTH OAKOTA/SOUTH CAROLINA/MIL-REP Associates, (412) 675-686; RHOGE ISLAND, Datcom, Inc., (617) 891-4600; TENRESSEE, MORTHSSEE, MORTHSS

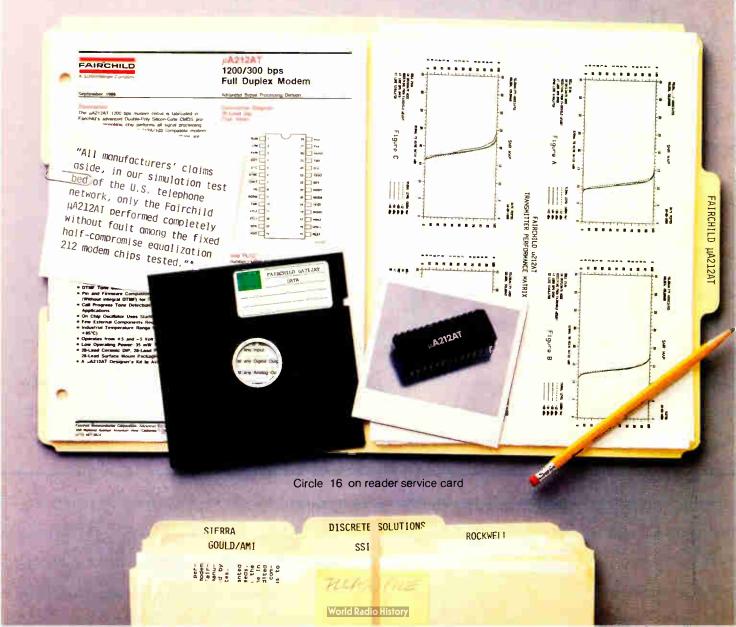

## It's hard to compete when you have no competition.

When we looked for a single-chip modem system to compare to our Surelink™ family, we couldn't find one. Simply because nothing else comes close.

We realize this may sound a bit boastful. But we have every reason to be.

According to TeleQuality Associates' Modem Performance Analysis, the Fairchild  $\mu$ A212AT has the best performance of any single-chip modem IC in existence, and better performance than the leading 2-chip sets.

When they tested us against Gould/ AMI, SSI, Sierra, Rockwell, and a handful of others, only our modem performed completely without fault. And scored the group's lowest BER (Bit Error Rate). Maybe that's why we're the largest supplier of single-chip modems. With over 80 design wins and parts available right now. In quantity.

The Surelink family includes the Bell 212A-compatible  $\mu$ A212AT, and the CCITT V.22-compliant  $\mu$ AV22. Both offering 1200 bps, on-chip tone-dialers, and the lowest power consumption of any modem chip or chip set – just 35 mW. And since Surelink is a constantly growing family, we offer an evolutionary migration path for the future. Along with comprehensive design aids and support.

For a copy of the Surelink Informa-

tion Package, call The Fairchild Customer Information Center at 1-800-554-4443.

We'd also

like to suggest

like to suggest SINGLE-CHIP MODEMS comparing us to the competition. But there doesn't seem to be any.

© 1987 Fairchild Semiconductor Corporation. Surelink is a trademark of Fairchild Semiconductor Corporation.

\*Reprinted with the permission of TeleQuality Associates.

We're taking the high ground.

FAIRCHILD

A Schlumberger Company

## IMPROVE YOUR MEMORY

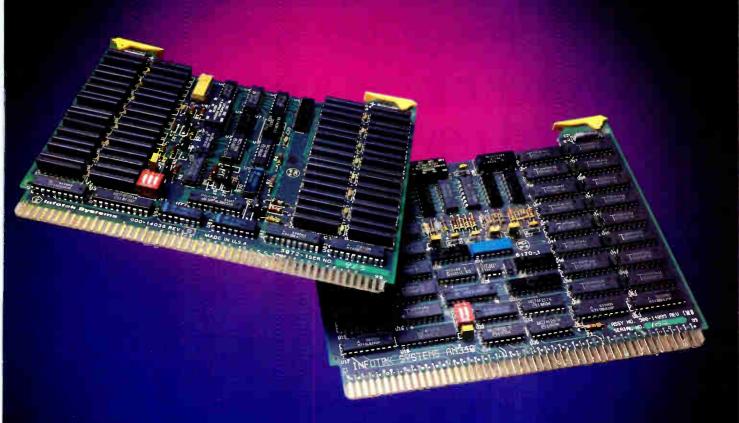

New Infotek 8 and 4 MByte Memory Cards Give Lowest Cost per Byte for HP 200/300.

Now, get all the memory you need for the most complex programs—CAD, CAE—all on a single, compact card. And, at the same time, get the lowest cost per megabyte of memory on the market.

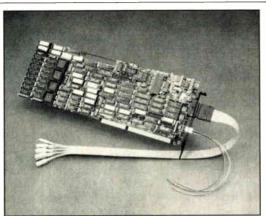

Infotek's new AM380 is the first 8 megabyte single-card memory available for HP 200/300 computers. It allows you to take advantage of the full storage capacity of your HP workstation without wasting valuable backplane space. ZIP packaging of 1 MByte monolithic DRAMs makes the low cost per byte possible.

For the many applications requiring 4 MBytes of memory, Infotek again uses 1 MByte DRAMs in single in-line packages to reduce costs. That means you

can now have Infotek quality in the lowest-cost 4 MByte board available! Of course, Infotek's

Memory for even the most complex CAD and CAE programs on a single board. popular 1 MByte and 2 MByte memories are also available.

The literally famous reliability of Infotek memories is evidenced by our full two-year warranty. So improve your memory with state-of-the-art DRAM boards from Infotek. Call today to Infotek Systems, 1400 North Baxter Street, Anaheim, California 92806-1201, (714) 956-9300, (800) 227-0218, in California (800) 523-1682, TELEX: 182283.

While you're at it, ask to receive our Infotek newsletter.

Your Second Right Decision

Circle 19 on reader service card

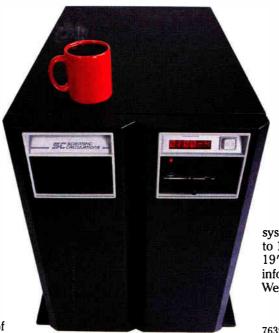

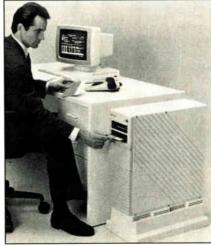

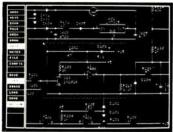

# The ARX20 Automatic Router never goes home, never takes a break, never gets sick, never makes a mistake, and never leaves any routing incomplete

The ARX20™ automatic router from Scientific Calculations is a high performance processor driving powerful multiple algorithms for total routing of large. complex, high density printed circuit boards. The off-line server can queue and route any number of designs from any number of workstations through a Local Area Network (LAN). It performs unattended, day and night, freeing your users and CAD systems for other work. Unlike other systems, it handles clearances, trace widths and vias of any size. And it won't compromise your design rules. It "sees through" up to 32 board layers at once, determining instantly

where there are congested areas and where the best trace paths are. You can query the system anytime to determine route status. Automatic cleanup routines reduce the number of vias, shorten trace lengths and eliminate loops and hooks. The ARX20 system CPU is the full 32-bit MC68020 microprocessor hosting the UNIX V operating

system. Physical memory ranges to 12MB. The unit is 29" high, 19" wide and 31" deep. For more information, write or give us a call. We'll give you a demonstration.

7635 Main Street, Fishers, NY 14453 1-800-4-HARRIS Ext. 4362 1-800-344-2444 (Canada)

ARX20 is a trademark of Scientific Calculations. MC68020 is a trademark of Motorola. UNIX V is a trademark of AT&T Bell Laboratories.

## **ELECTRONICS NEWSLETTER**

## TRADE-WAR FEARS AND COMPUTER-MARKET RECOVERY BOOST CHIP SALES

burst of panicky buying spurred by fears of a trade war between the U. S. and Japan added a fillip to the chip business, but that's not the only reason behind the rise in March semiconductor bookings. Analysts say solid improvement in the computer market—as much as 9% growth—could lead to a double-digit rise for the semiconductor industry for 1987. The Reagan Administration imposed 100% punitive tariffs April 17 on some Japanese instruments, color TVs, and laptop computers, maintaining the Japanese had failed to live up to last summer's semiconductor trade accord. Industry insiders had worried that the move would prompt quick retaliation—and possible chip shortages-from Japan, but so far the Japanese have been slow to react. In the U.S., the strong yen and fears of price hikes for memory parts has fueled a chip-industry comeback, according to Integrated Circuit Engineering Corp., of Scottsdale, Ariz. With the Semiconductor Industry Association reporting March billings of \$912.1 million and bookings of more than \$1 billion, ICE now says its 1987 forecast for 9% growth might be on the low side, and Jack Beedle, the traditionally bearish analyst at In-Stat Corp., has boosted his 1987 sales estimates by about 6%, to 15%.

## GE/RCA IS ABOUT TO JUMP INTO DIGITAL SIGNAL PROCESSORS

Seeking to cash in on the rapidly expanding market for digital signal processors, the GE/RCA Solid State Division is making a late but significant entry. GE/RCA, of Somerville, N.J., has not previously marketed DSP chips, but the company hopes to make a splash this summer when it offers samples of a trio of commercial DSPs that will become part of GE/RCA's Advanced CMOS Logic family. Military versions will follow later this year, and the devices will also be added to the company's standard-cell library for application-specific integrated circuits. The new products include a 20-MHz programmable digital finite-impulse-response filter, a least-mean-square adaptive FIR filter, and a programmable-length first-in, first-out circuit.

## NATIONAL SLICES TURNAROUND TO TWO WEEKS FOR PROTOTYPE ROMS

ational Semiconductor Corp. has found a way to program read-only memories after the final metallization layer has been deposited, cutting turnaround time for new designs to as little as two weeks for prototypes and four weeks for production parts. Normal turnaround time is generally three to four times longer. National found that implanting the chip with phosphorus ions at high energy could change the dopant of a buried layer to turn an enhancement device, which is always off, into a depletion device, which is always on. National has applied the process first to relatively slow devices, called stacked ROMs, in its high-volume COP 400 4-bit microcontroller line and may use it in high-speed ROMs or even programmable logic in the future.

## TELESOFT AND READY SYSTEMS WILL PRODUCE A RUN-TIME VERSION OF ADA

Seeking a way to produce a runtime version of Ada fast enough to operate in time-critical embedded avionics systems, Telesoft of San Diego is trying to mate its validated compiler with VRTX, a real-time operating system from Ready Systems of Palo Alto. The result should be a run-time Ada capable of context switching in as little as 125  $\mu$ s, versus 600 to 900  $\mu$ s for current Ada compilers. Avionics systems need fast context switching to check through a battery of sensors in a given cycle. Ready Systems expects to have an interim product out by midsummer, called AVX, that will provide an alternate tasking mechanism for Ada systems.

## **ELECTRONICS NEWSLETTER**

## PHOTONICS' 5-FT GAS-DISCHARGE FLAT PANEL IS THE BIGGEST EVER

The largest-ever gas-discharge dot-matrix flat-panel display, measuring 59 in. diagonally, will be shown for the first time at the Society of Information Display conference in New Orleans in May. The ac display developed by Photonics Technology Inc., Northwood, Ohio, and Magnavox Electronics Systems Co., Fort Wayne, Ind., features 2,048-by-2,048-pixel monochrome resolution. It packs more than 4 million pixels into a 12.5-ft² viewing area. Photonics has shipped six of the 4-in.-thick, wall-size units, which have a refresh rate of 30 frames/s, to military contractors for command and control applications. Complete with a power supply, electromagnetic interference protection, software, and 68020-based electronics, a military version sells for about \$400,000; the commercial version costs about \$200,000.

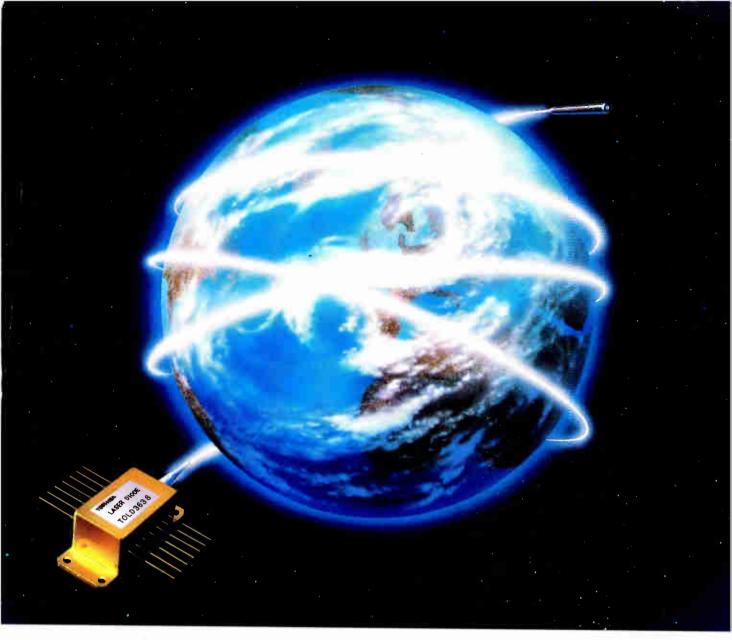

## BELL LABS BUILDS WORLD'S FASTEST LASER

T&T Co.'s Bell Laboratories has set a new standard for the world's fastest laser, shattering a record thought to be unbreakable just six months ago. Bell Lab researchers have built a device capable of emitting pulses every 6 fs, 25% faster than the previous high, and they are already using the laser experimentally. Chuck Shank, director of AT&T's Electronics Research Laboratory in Holmdel, N. J., says he once believed 8 fs was the technological limit, because the two optical gradings the laser relied on distorted results at higher repetition rates. But by bringing a pair of prisms into the picture, researchers in his group discovered that they could counteract the distortion by distorting the signal in an equal, but opposite, manner. The laser "gives us the ability to track an electron through a solid [object], step by step," Shank says. "We're witnessing the fundamental processes of how carriers act inside a material."

## NOW PCs CAN ACT AS WORK STATIONS ON SUPERCOMPUTER NETWORKS

inking popular personal computers to a supercomputer is becoming a lot easier, thanks to software packages developed at the National Center for Supercomputing Applications at the University of Illinois. The center is distributing a communications package called NCSA Telnet, which allows an Apple Macintosh or an IBM PC to serve as a front-end work station to Cray X-MP or other scientific and engineering computers. Designed for the TCP/IP (for Transmission Control Protocol/Internet Protocol) environment used on Arpanet and the National Science Foundation's NSFnet, NCSA Telnet is the first package to allow multiple simultaneous communications between a Mac or PC and a Cray XM/P on a network. Both versions include VT 100 emulation for file editing, and the Mac version incorporates Tektronix 4010 terminal emulation for line-drawing graphics.

## DG BLAMES \$9.6 MILLION OPERATING LOSS ON AGING 16-BIT COMPUTER LINE

ata General Corp. posted a \$42.6 million loss, including an operating loss of \$9.6 million, for its second quarter, which ended March 28, and DG president Edson de Castro is blaming the poor showing on "the rapid deterioration in sales of our older 16-bit product line." Sales of the company's MV line of 32-bit computers are increasing, but not enough to make up the difference. "We don't know when revenues will improve," a spokesman says. "We can't predict the rest of the year." The total quarterly loss was augmented by a one-time charge of \$18.2 million the Westboro, Mass., company took for the early redemption of \$150 million worth of debentures due in 2015, and a \$14.8 million write-down from readjustments in market value for an unconsolidated affilliate, Dama Telecommunications Corp. of Rockville, Md.

## Burr-Brown came to Livingston for the workforce.

For Burr-Brown, the requirements for their European location were relatively straightforward.

A clean environment, modern facilities and direct transport and communication links with continental Europe.

They found all this in Livingston, Scotland.

A town purpose-built for new industries situated at the heart of one of the greatest concentrations of electronic companies in Europe.

And they found much more.

They found investment grants of up to 35%, rent-free periods plus European Community assistance. They found Kirkton Campus, a high-technology park ready-made to receive them.

And they found us.

A Development Corporation that could help them develop at

every turn and a workforce that was both skilful and conscientious.

In Burr-Brown's words, one whose productivity was 'second to none in the world'.

Within a 40 mile radius of Livingston they found the support and research facilities of six Scottish universities and numerous technical colleges.

Today, Burr-Brown is one of a long list of blue chip Livingston residents with firm plans for expansion.

A list that we can offer you every incentive to join.

| IN THE US, send to: C Anne Robins, PO Box 345, Old Greenwich, CT 06870 Tel: (203) 629 3496.  IN THE UK and EUROPE, send to: David Balfour, Commercial Director, Livingston Development Corporation, West Lothian EH54 6QA, Scotland. Tel: 0506 414177.  Prove that Livingston is the most logical location for my company. BLOCK LETTERS PLEASE |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                                                                                                                                                                                                                                                                                            |

| Position                                                                                                                                                                                                                                                                                                                                        |

| Company                                                                                                                                                                                                                                                                                                                                         |

| Address                                                                                                                                                                                                                                                                                                                                         |

| Post Code                                                                                                                                                                                                                                                                                                                                       |

| Telephone MAKEITIN E14                                                                                                                                                                                                                                                                                                                          |

| LIVINGSTON                                                                                                                                                                                                                                                                                                                                      |

| Europe's most logical location.                                                                                                                                                                                                                                                                                                                 |

## Overnight delivery is only half our legend.

The other half is quality. At Data Translation, we ride herd over the quality of everything we make. All Image Processing, Array Processing, and Data Acquisition boards

|                            | Image Pr                                             | ocessing                                                                                  |                                      |                                                |

|----------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------|

| Resolution                 | Real-Time<br>Frame Grab                              | Real-Time<br>Processing                                                                   | Software                             | Price                                          |

|                            |                                                      |                                                                                           |                                      | \$2995                                         |

| 512x512x8                  |                                                      |                                                                                           |                                      | \$1695                                         |

| 256×256×6                  | ~                                                    |                                                                                           | ~                                    | \$1495                                         |

|                            | Array Pr                                             | ocessing                                                                                  |                                      |                                                |

| FFT*<br>1024 Point<br>Real | FFT*<br>1024 Point<br>Complex                        | FFT*<br>256x256<br>Image                                                                  | Software                             | Price                                          |

| 23ms                       | 41ms                                                 | 3.9s                                                                                      | ~                                    | \$4995                                         |

|                            | 512x512x8<br>256x256x6<br>FFT*<br>1024 Point<br>Real | Resolution Real-Time Frame Grab  512x512x8  256x256x6  Array Pri 1024 Point Real  Complex | Resolution   Frame Grab   Processing | Resolution   Real-Time   Processing   Software |

| Data Acquisition (24 Boards Total) |               |                |                    |              |          |               |  |

|------------------------------------|---------------|----------------|--------------------|--------------|----------|---------------|--|

| Series                             | Analog<br>I/O | Digital<br>I/O | 12-bit &<br>16-bit | Throughput   | Software | Price         |  |

| DT2801                             | <b>1</b> /    | 10             | 10                 | 13.7-27.5kHz | ~        | \$295-\$2070  |  |

| DT2821                             | -             | ~              | ~                  | 45-250kHz    | ~        | \$1345-\$2995 |  |

| DT2811                             | <b>1</b>      | ~              | 12-bit             | 20kHz        | <b>1</b> | \$199-\$745   |  |

and software for the IBM PC are pre-tested and pre-burned in. We deliver products that meet our tough quality control standards, making our return rate the lowest in the industry.

So phone us by mid-day for overnight delivery.

After all, why should you wait weeks to start important projects when Data Translation

can have you sitting tall in the saddle tomorrow?

CALL (617) 481-3700.

To learn more, see us in Gold Book 1987, or call to receive our first-ever 1987 3-Book Set, including 1987 Catalog, Product Summary Price List, and Applications Handbook.

## DATA TRANSLATION

World Headquarters: Data Translation, Inc., 100 Locke Dr., Mariboro, MA 01752 (617) 481-3700 Tix 951 646 European Headquarters: Data Translation Ltd., 13 The Business Centre, Molly Millars Lane, Wokingham, Berks, RG11 2QZ, England Tix 849862 (#D) International Sales Office: Australia (61) 2-662-4295; Belgium (32) 2-7352135; Canada (416) 625-1907; Chile (2) 2-253699; Chima (408) 727-8222, (36) 8-721-4017; Denmark (45) (02) 187188; England (44) 734-79383; Finland (358)-90-372144; France (33) (1) 69-28-01-73; Greece (30) (3) 152-7039, (30) (1) 361-4300; Hong Kong (352) 3 318585; India (91) 2-231040; Israel (972) 3-324298; Italy (39) 2-81821; Japan (81) (3) 502-5550, (81) (3) 375-1551, (81) (3) 355-1111; Korea (82) 778-0721; Malaysia (60) 3-36299; Morocco (21) 9-30-6949; Netherlands (31) 70996360; New Zealand (61) 2-662-4295; Norway (47) (02) 559050; Peru (51) (14) 8060; Phillipines (63) 818-0103; Portugal (351) 1545313; Singapore (65) 271-3163; South Africa (27) 12469221; Spain (34) 14558112; Sweden (46) 8-7617820; Switzerland (41) 17231410, (41) 22360830; Taiwan (86) 2-709-1394; West Cermany (49) 89809020.

## PRODUCTS NEWSLETTER

## TELEBIT DESIGNS A 2,400-BAUD MODEM FROM OFF-THE-SHELF PARTS

Telebit Corp., which threw a fastball at the dial-up modem market with its 18-Kbaud Trailblazer modem two years ago, is now following up with a curve: a design for a 2,400-baud modem that can be built from off-the-shelf, second-sourced parts. At the modem's heart is the Texas Instruments Inc. 320CM10 digital signal processor, programmed in read-only memory with basic modem functions from Telebit's Trailblazer architecture. The modem supports CCITT V.22bis, 2,400-baud transmission as well as Bell 212A and Bell 103 (1,200- and 300-baud) operation. The other two chips are an Intel Corp. 80C51 microcontroller with source code for mask programming and an Oki Semiconductor 6950B analog front end. Together the three chips cost about \$27, says the Cupertino, Calif., company. The Telebit licensing fee is either a \$200,000 one-time payment, which includes engineering support; or a \$25,000 technology-transfer fee plus a \$5/unit royalty. □

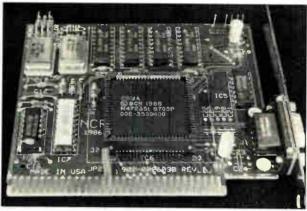

## SMC CONTROLLER CUTS CHIP COUNT ON INTERFACE BOARDS FOR IBM MINIS

Chip counts on boards that link IBM Corp. System/3X minicomputers with terminals, peripherals, and networks can be reduced from as many as 100 to just 12 using Standard Microsystems Corp.'s single-chip controller to implement IBM's 5250 Standard. The COM52C50 is fabricated in 3-μm CMOS standard cells from the company's application-specific integrated-circuit library. All its high-speed-related functions are concentrated on-chip, so board designers can substitute a \$2 chip for a high-speed input-output processor costing 10 times as much, says the Hauppauge, N. Y., company. Samples are available now. In 100-unit quantities, the device costs \$19.50 in plastic dual in-line packages.

## SOFTWARE CUTS TEST-DEVELOPMENT TIME FOR PROCESSOR BOARDS BY 80%

new high-level language, combined with utilities that automate fault-isolation programming, promises to trim the time it takes to develop test and trouble-shooting programs for typical microprocessor boards from the usual 20 to 30 man-weeks down to four to six man-weeks. The software comes with John Fluke Mfg. Co.'s new 9100 series of low-cost digital testers. The testers also handle functional testing up to 10 MHz and guided fault isolation up to 40 MHz. To reduce manual probing during fault isolation, up to 160 10-MHz lines can be employed with dual-in-line-package clips to stimulate and check circuit nodes automatically. Prices range from \$21,500 for a stand-alone system with a programmer's work station to \$9,000 for a test station, says the Everett, Wash., company.

## DEC BOOSTS SPEED AND RESOLUTION ON ITS VAX TERMINALS

esides offering five times the speed and twice the resolution of older DEC terminals, the newest monochrome and color VAX terminals from Digital Equipment Corp. can manage and display two computing sessions simultaneously. What's more, they're priced substantially below their predecessors. The new text-and-graphics terminals are the monochrome VT330 and the full-color VT340. A proprietary VAX layered software utility, called SSU and priced at \$200, allows dual sessions on a single wire with a VAX and an IBM Corp. mainframe, for example—a capability DEC claims is unique. The new terminals, which are completely compatible with all earlier DEC hardware and software, offer either six screens of text memory or two screens of graphics memory to offload the host computer. The VT330 sells for \$1,895, which is \$300 less than its predecessor, the VT240. At \$2,795, the VT340 is \$400 less than the older VT241. Both will be available in volume in May.

## **PRODUCTS NEWSLETTER**

## PRIME SUPERMICRO RUNS UNIX AND MS-DOS SIMULTANEOUSLY

Prime Computer Inc. has tapped into the Unix environment with a supermicrocomputer that can run character-mode MS-DOS and Unix applications at the same time. The EXL 316 turns the trick with Merge 386, a software package from Locus Computing Corp., Santa Monica, Calif. Based on Intel Corp.'s 80386 microprocessor, the EXL 316 also has an Intel 80186 in its asynchronous controller, which means the 80386's 4 million-instructions-persecond performance at 16 MHz is degraded only slightly—to 3.2 mips—in executing Prime's implementation of AT&T Co.'s Unix V.3. With prices starting at \$23,900, the EXL 316 is price-competitive with other multiuser supermicros, but none of them can run MS-DOS and Unix programs simultaneously, says the Natick, Mass., company. The EXL 316 will be available in June. Merge 386 software is separately priced at \$1,800. Prime's other computers—with the exception of a recently introduced Unix-based graphics work station—use the company's Primos operating system.

□

## AMIABLE 100-Mbyte WINCHESTER FROM CONNER GETS ALONG WITH ANY PC

By interfacing a custom gate array with drive logic, Conner Peripherals has built a 100-Mbyte (formatted)  $3\frac{1}{2}$ -in. Winchester disk drive that can be tailored to a specific host bus interface. The CP3100 normally uses the Small Computer Systems Interface and is fully compatible with the SCSI Common Command Set. It is also available with the IBM Corp. PC/AT interface, which means the AT needs no interface card. Other interfaces can be designed with the custom gate array. The San Jose, Calif., company's new drive is voice-coil actuated and employs 2,7 run-length-limited encoding. The half-height drive has a 25-ms access time and weighs 2 lb. Priced at \$995 in OEM quantities (\$1,595 for single units), evaluation units are available now. Volume shipments begin in the fourth quarter.

## CHOICES: \$595 PER NODE FOR A NETBIOS 1-MBIT/S LAN...

Telegence Corp.'s Tokenstar 3301 plug-in card turns IBM Corp. Personal Computers or compatibles into networked work stations on Telegence's 1-Mbit/s Tokenstar local-area network using the IBM Netbios industry-standard interface. For \$595 per node, users can chain together PCs with 3301s by interconnecting them with standard twisted-pair telephone cables with modular plugs. Or, they can plug the PCs into a Tokenstar network installed on a building's telephone wiring. The network transmits data over phone lines without interfering with voice calls [*Electronics*, Jan. 8, 1987, p. 31]. The 3301 boards are available now from the Westlake Village, Calif., company.

## ...OR A NONSTANDARD COAXIAL NETWORK THAT'S 3.6 TIMES FASTER

3.6-Mbit/s local-area network called Grapevine connects IBM Corp. Personal Computers or compatibles for \$595 per node—compared with \$1,600 to \$2,600 per node for competing systems that share 11- to 16-disk dedicated file servers. The LAN, from Computer Pathways Inc., eliminates file servers. Data resident in the PCs is shared instead by means of a proprietary real-time multitasking system. The total system—which consists of an adapter board, software, and coaxial cable—provides extensive user functions for electronic mailboxes, peripheral assignments, and file transfers. Although up to 50 PCs can be linked with the system, the Bothell, Wash., company says Grapevine is best suited for small, eight-member work groups—the majority of network users. Ethernet and IBM Token Ring gateways to larger systems can be purchased if needed. Grapevine's range is 4,000 ft using 14¢/ft RG-59 television coaxial cable. The product is available now.

# For workstations that thrive in a multivendor

HP's powerful family of technical workstations fits right in with your present computing resources, as well as those added in the future. With industry standard networking, operating systems, and languages. *Plus* hundreds of advanced application packages, and performance extras to give you the competitive edge in all of your engineering and technical activities.

Our solutions are implemented on one of the industry's largest technical computer and workstation families. It consists of the HP Technical Vectra PC, the HP 9000 series 200/300/500, and the new model 840 Precision Architecture Computer.

## Full UNIX System V compatibility.

HP's technical workstations use AT&T's System V UNIX operating system with Berkeley 4.2 enhancements and HP improvements. The result is a standard tuned to the workstation environment with windowing, real-time I/O extensions, graphics, six languages and other extras.

## The networking you need.

HP offers the networking to unify design, test, manufacturing, and technical office automation in your company. You'll have ARPA and Berkeley services and TCP/IP on Ethernet\*\* and IEEE 802.3 to provide connectivity with IBM, DEC, and other vendors' products.

## AI power without special AI machines.

You get everything you expect in a multipurpose workstation, plus the ability to run Artificial Intelligence on the same machine. Based on Common Lisp, it lets you harness AI power for accelerated software development. You can also get premier expert system tools from companies such as Intellicorp and Teknowledge.

## Wide range of graphics solutions.

The choice is yours...from low-cost monochrome to high-resolution color monitors...from simple report

# run UNIX systems and environment, talk to HP.

graphics to 3D solids modeling. There are industry standards like GKS and ANSI Computer Graphics Virtual

Device Interface (CG-VDI), to protect your investment by making your existing software portable. HP's accelerated graphics solutions are highly modular, so you can upgrade whenever you choose.

## Hundreds of application packages.

Specialized technical applications? No problem. HP's application packages include logic and analog CAE, PCB CAD, microprocessor software development, 2D design and drafting, 3D solids modeling and finite element analysis, documentation and report generation, and database management. New software packages are constantly being added for an even larger selection.

## HP—protecting your investment.

Buying HP's solutions is not only a smart decision initially, but it provides the added benefit of lower cost of ownership that reflects our commitment to quality and service. For more information, call your local HP sales office listed in the telephone directory white pages.

## Tap HP's DATA-LINE for complete facts...instantly!

For on-line information 24 hours a day, use your computer, modem, and HP's DATA-LINE. Dial 1-800-367-7646 (300 or 1200 baud, 7 bits even parity, 1 stop bit). In Colorado call 1-800-523-1724.

\*UNIX is a trademark of AT&T.

\*\*Ethernet is a trademark of Xerox Corporation.

DS15603B

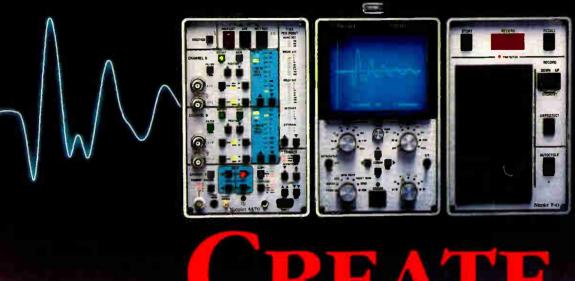

## CAPTURE.

# Record of the second of the se

Stimulate experiments with real-time analog waveforms reproduced from your actual captured data!

Connected via the GPIB interface, the Nicolet Model 4094 digital oscilloscope teamed up with the Nicolet Model 42 arbitrary function generator provides instantaneous waveform storage and generation.

800/356-3090 or 608/273-5008

Nicolet Test Instruments Division P.O. Box 4288 5225-2 Verona Road Madison, WI 53711-0288

## Nicolet Digital Oscilloscopes

Incoming signals digitized by Nicolet's high accuracy 12-bit, 10 MHz digitizers or high speed 8-bit digitizers allow you to see things you've never seen before. Zoom expansion to X256 allows you to see the details in waveforms composed of up to 16k points. Cursor readout of measurement values, continuously variable pretrigger positioning, and built-in disk drives all contribute to Nicolet's tradition of measurement power and ease of use.

## Nicolet Programmable Function Generators

Outgoing signals are accurately generated from the 12-bit by 2k arbitrary waveform memory in the Model 42. Real-time duplication of the captured signal can be produced at speeds up to 1 µSec per data point.

Continuous, triggered, gated, and burst output modes are possible. A unique feature, arbitrary sweep, allows you to accurately program the output frequency. Standard waveforms (sine, triangle, square, sawtooth, pulse),  $10~\text{mV}_{\text{p-p}}$  to  $20\text{V}_{\text{p-p}}$  amplitudes, are all available at speeds up to 4~MHz.

**NEWS** APRIL 30, 1987

## **Electronics**

## SRAM MAKERS CROWD INTO THE **CACHE-TAG MEMORY NICHE**

## THE BIG QUESTION: CHIP SETS OR ONE-CHIP SOLUTIONS?

**DALLAS**

he cache-tag chip race has suddenly picked up speed. With nearly 20 manufacturers competing hard in static random-access-memories, most of them are looking for profitable niches. Right now, cache-tag is the most popular one: at least 10 of them have chips or are planning them.

"Cache is just now coming into its own," says Robert Bailey of Texas Instruments Inc., which originated cachetag integrated circuits in 1980. "With microprocessor speeds increasing, memory is becoming the major bottleneck," says Bailey, U.S. logic strategy manager for standard logic circuits at the Dallas company. That is the design problem TI set out to overcome when it combined a static memory array and the logic of a comparator in the first cache-tag circuit.

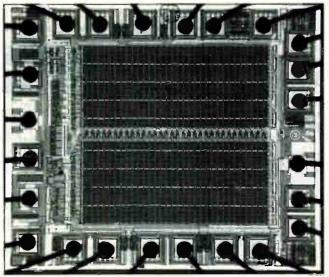

Now the company is launching a new series of 1-µm CMOS cache-tag chips (see p. 81) as part of a VLSI logic portfolio. Others are hot on TI's heels, with a significant portion of chip sales at stake: cache storage represents about a third of fast-SRAM shipments.

"We knew this thing was too good to last," says Bailey, reflecting on TI's fastvanishing position as the sole producer of cache-tag ICs. TI must fend off not

only the onslaught of new competitors, but also the advent of highly integrated cache controllers, which incorporate addressmatching functions with tightly coupled interfaces to specific 32-bit microprocessors.

The cache-tag function acts as a self-initiating directory of what data is being held in SRAM-based cache storage. It automatically checks incoming addresses from host processors against the data copied in cache from slower dynamic random-access main memory. These specialized addressmatching memories can boost system throughput by offloading overhead from a busy host.

Silicon integrators now must

be squeezed onto a single IC. Products planned for later this year run the gamut of possibilities, as chip merchants anticipate cache's move into high-volume personal computers, thanks to 32-bit microprocessors that rev at more than 20 MHz.

The result is a strategic jumble. Solutions range from relatively simple cachetag devices to chip sets and highly integrated cache controllers. Some companies favor what TI's Bailey terms "generic" chips, those not tightly tied to a microprocessor or system-bus architecture. Others are designing around Intel Corp.'s popular 32-bit 80386 microprocessor.

These diverse system-cache architectures are making it difficult for chip makers to clearly identify high-volume configurations, notes Curt Wyman, Motorola Inc.'s SRAM marketing manager. "We are expecting a shakeout in the features area, and standards will evolve," he says.

GETTING FASTER. So chip makers are hustling to get a leg up. For example, TI is redoing its widely used n-channel cache-tag design (512 by 9 bits) in 1-µm CMOS, speeding up the part to 20 ns from 35 ns. The result is the TACT2150, priced at \$16.20 each in 10,000-piece orders. Bailey expects to see 15-ns speeds by year's end.

By June, TI will also offer samples of new 1-Kbit-by-12-bit and 2-Kbit-by-9-bit CMOS cache-tag chips. Like other companies, TI is planning system-specific cache controllers, and it is likely to place cache-tag functions into its 1-µm CMOS standard-cell library.

At Motorola in Austin, Texas, MOSmemory managers are planning a new line of cache-tag SRAMs by the beginning of next year, one matching the 22pin MK41H68 4-Kbit-by-4-bit design introduced by Thomson Components-Mostek Corp. [Electronics, Jan. 22, 1987, p. 102]. Motorola's 24-pin design will contain a bit-set/bit-clear write feature that will allow individual bit manipulation without the need for a complete readmodify-write operation.

But other companies are not willing to wait patiently. They are hoping to get a head start, especially in playing off the popularity of the Intel 80386 processor. Intel itself plans to ship in the second half of the year a high-performance 32-bit cache controller tightly coupled to its microprocessor. The 132-pin 82385 contains not only the cache-tag function but a "posted write-through" feature that uses on-board buffers to make information immediately available to an 80386 system bus.

Intel's plans have led Inmos Corp. to tightly couple the 80386 to a cache-storage chip set now in the works. "We were working on a cache chip set before Intel made its plans known," says Don Carrigan, director of memory marketing at Inmos, Colorado Springs. "Intel's move certainly influenced us in the area of whether or not to go generic, or [to design] one for the Motorola 68020 or the Intel 80386." Inmos plans to roll out early next year a 68-pin controller that will have an 8-bit-wide cache-tag function on-chip and support for a four-way associative organization.

The firm is also designing a cache-oriented data RAM that will have extra interface logic to

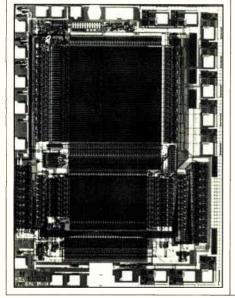

decide how much, and how PATRIARCH. Texas Instruments' TACT2150 is the first of a family quickly, cache circuitry should fabricated in its 1-µm CMOS technology.

work quickly with the Inmos controller or others, such as the Intel chip. Carrigan expects the company's next step will be integration of data array onto the controller for a monolithic cache chip.